- The set introduces the new chassis Nordmende F11B but made by THOMSON as Chassis ICC3000. The set is indeed made entirely by THOMSON in Germany, as NORDMENDE was aquired by the French firm before. The THOMSON Chassis ICC3000 was also shared in SABA TV, HITACHI (Some Models), TELEFUNKEN (Some Models) sets and B&O TV sets.

- Right

side a red led display shows programs and channels numbers with the

"Pr x " and after the "Ch xx" for 2 seconds after, this during use of

the set and a remote which controls the set. Such kind of displaying was

also featured in future sets with other equipment chassis's.

- Also a stereo headphone jack of a din type is present.

- SCART connector Is also present backside and first time it will feature all sets fabricated by the THOMSON firm from then to future.

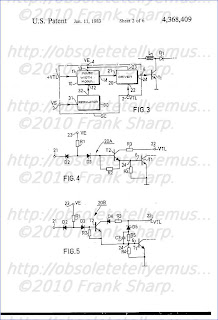

- Integration in the new IC TEA 2026:The vertical and horizontal frequencies are derived from a 500 kHz

crystal oscillator and divider. Adjustment of the vertical and

horizontal frequency is not required. vertical generator up to the control function of the vertical output thyristor, including automatic switching of the 50/60 Hz / horizontal generator up to the control of the horizontal output stage / switch mode power supply up to the control of the step-up transistor, including ‘soft- start’ and protection circuit

- Stereo Sound and Bi Language sound channnel .

- Switched-mode frame-scan control circuit for vertical deflection as featured earlier in F11 (1983) /Switched mode vertical deflection systems derive power from horizontal deflection energy, by storing a portion of a horizontal trace or retrace energy each horizontal deflection cycle. The energy is supplied to a vertical deflection winding in order to provide the desired vertical deflection current in the deflection winding. The amount of horizontal rate energy stored each horizontal interval is closely controlled in order to provide the correct amount of vertical deflection current.

- First introduction of a a single case enclosing a device comprises inside a tuner, an intermediate frequency amplifier connected to the tuner, a demodulator connected to the intermediate frequency amplifier and sound IF, and a phase locked loop provision connected to the tuner.

- High integration chassis featuring all functions of the receiver.

- Additionally an optional teletext feature.

A SCART Connector (which stands for Syndicat des Constructeurs d'Appareils

Radiorécepteurs et Téléviseurs) is a standard for connecting

audio-visual equipment together. The official standard for SCART is

CENELEC document number EN 50049-1. SCART is also known as Péritel

(especially in France) and Euroconnector but the name SCART will be used

exclusively herein. The standard defines a 21-pin connector (herein

after a SCART connector) for carrying analog television signals. Various

pieces of equipment may be connected by cables having a plug fitting

the SCART connectors. Television apparatuses commonly include one or

more SCART connectors.Although a SCART connector is bidirectional, the present invention is concerned with the use of a SCART connector as an input connector for receiving signals into a television apparatus. A SCART connector can receive input television signals either in an RGB format in which the red, green and blue signals are received on Pins 15, 11 and 7, respectively, or alternatively in an S-Video format in which the luminance (Y) and chroma (C) signals are received on Pins 20 and 15. As a result of the common usage of Pin 15 in accordance with the SCART standard, a SCART connector cannot receive input television signals in an RGB format and in an S-Video format at the same time.This kind of connector is todays obsoleted !

A SCART Connector (which stands for Syndicat des Constructeurs d'Appareils

Radiorécepteurs et Téléviseurs) is a standard for connecting

audio-visual equipment together. The official standard for SCART is

CENELEC document number EN 50049-1. SCART is also known as Péritel

(especially in France) and Euroconnector but the name SCART will be used

exclusively herein. The standard defines a 21-pin connector (herein

after a SCART connector) for carrying analog television signals. Various

pieces of equipment may be connected by cables having a plug fitting

the SCART connectors. Television apparatuses commonly include one or

more SCART connectors.Although a SCART connector is bidirectional, the present invention is concerned with the use of a SCART connector as an input connector for receiving signals into a television apparatus. A SCART connector can receive input television signals either in an RGB format in which the red, green and blue signals are received on Pins 15, 11 and 7, respectively, or alternatively in an S-Video format in which the luminance (Y) and chroma (C) signals are received on Pins 20 and 15. As a result of the common usage of Pin 15 in accordance with the SCART standard, a SCART connector cannot receive input television signals in an RGB format and in an S-Video format at the same time.This kind of connector is todays obsoleted ! Consequently many commercially available

television apparatuses include a separate SCART connectors each

dedicated to receive input television signals in one of an RGB format

and an S-Video format. This limits the functionality of the SCART

connectors. In practical terms, the number of SCART connectors which can

be provided on a television apparatus is limited by cost and space

considerations. However, different users wish the input a wide range of

different combinations of formats of television signals, depending on

the equipment they personally own and use. However, the provision of

SCART connectors dedicated to input television signals in one of an RGB

format and an S-Video format limits the overall connectivity of the

television apparatus. Furthermore, for many users the different RGB

format and S-Video format are confusing. Some users may not understand

or may mistake the format of a television signal being supplied on a

given cable from a given piece of equipment. This can result in the

supply of input television signals of an inappropriate format for the

SCART connector concerned.

Consequently many commercially available

television apparatuses include a separate SCART connectors each

dedicated to receive input television signals in one of an RGB format

and an S-Video format. This limits the functionality of the SCART

connectors. In practical terms, the number of SCART connectors which can

be provided on a television apparatus is limited by cost and space

considerations. However, different users wish the input a wide range of

different combinations of formats of television signals, depending on

the equipment they personally own and use. However, the provision of

SCART connectors dedicated to input television signals in one of an RGB

format and an S-Video format limits the overall connectivity of the

television apparatus. Furthermore, for many users the different RGB

format and S-Video format are confusing. Some users may not understand

or may mistake the format of a television signal being supplied on a

given cable from a given piece of equipment. This can result in the

supply of input television signals of an inappropriate format for the

SCART connector concerned.

PLL SYNTHESIZED TUNING System Concepts:

INTRODUCTION Digital tuning systems are fast replacing the conventional mechanical systems in AM FM and television receivers The desirability of the digital approach is mainly due to the following features * Precise tuning of station frequencies

* Exact digital frequency display

* Keyboard entry of desired frequency

* Virtually unlimited station memory

* Up down scanning through the band

* Station ‘‘search’’ (stop on next active station)

* Power on to the last station

* Easy option for time-of-day clock In addition

" recent "developments in large scale integrated circuit technology and new varactor diodes for the AM band have made the cost-benefit picture for digital tuning very attractive System partitioning is extremely important in optimizing this cost-benefit picture as will be discussed.

SYSTEM DESCRIPTION

A simplified block diagram of a typical digitally tuned receiver is shown in Figure 1 Notice this receiver could be one for AM FM marine radio or television it makes no difference The frequency synthesizer block generates the local oscillator frequency for the receiver just as a conventional mechanical tuner would However the phase-locked-loop (PLL) acts as an integral frequency multiplier of an accurate crystal controlled reference frequency while the mechanical type provides a continuously variable frequency output with no reference Some method of controlling the value of the multiplier for channel tuning must be provided The other RF IF and audio video circuitry will be the same as in the mechanical tuning method There are many different ways to partition the frequency synthesizer system to perform the digital tuning function................

The tuning is for this capable of 99 channels PLL synthesized tuner .

The chassis used in this series was only produced for a year or little more.

(To see the Internal Chassis Just click on Older Post Button on bottom page, that's simple !)

NORDMENDE HISTORYNordmende was a manufacturer of entertainment electronics based in Bremen, Germany.

The original company, Radio H. Mende & Co, was founded in 1923 by Otto Hermann Mende (1885-1940) in Dresden. Following the destruction of the plant during the bombing raids in 1945, Martin Mende (the founder's son) created a new company in Bremen in 1947, in a former Focke-Wulf plant, under the name North German Mende Broadcast GmbH.

The name was subsequently changed to Nordmende: subsequently the

company became one of the prominent German manufacturers of radios,

televisions, tape recorders and record players in the 1950s and 1960s.

(1885-1940) in Dresden. Following the destruction of the plant during the bombing raids in 1945, Martin Mende (the founder's son) created a new company in Bremen in 1947, in a former Focke-Wulf plant, under the name North German Mende Broadcast GmbH.

The name was subsequently changed to Nordmende: subsequently the

company became one of the prominent German manufacturers of radios,

televisions, tape recorders and record players in the 1950s and 1960s.

In the 1970s, Nordmende televisions were renowned for their innovative chassis, and for the rigorous testing and quality control of their finished products. Both created high costs, however, which soon proved a competitive disadvantage when the price of colour televisions began to plunge.In 1969, Mende's sons took over the company, and in 1977 a majority shareholding was sold to the French Thomson Brandt company and the chassis remains the original NordMende until CHASSIS F9. The following year, the family sold their remaining shares to Thomson. In the 1980s, the factories in Bremen were closed, Nordmende becoming purely a Thomson trademark (Starting from chassis F10 F11 they're all THOMSON).

In the 1990s, the name Nordmende was used with decreasing frequency, and it eventually disappeared in favour of the Thomson name. In 2005 Videocon Group acquired all cathode ray tube activities from Thomson. This led to the creation of VDC Technologies, which manufactures TV sets using the Nordmende brand under licence from Thomson.

The Nordmende brand name was relaunched in Ireland in September 2008 by the KAL Group. Although Nordmende

was well known for its televisions throughout Ireland during the

1970s and 1980s, the company bought the rights to the name and

launched a range of white goods including fridges, freezers, washing machines, and dishwashers, alongside a revamped range of flat-screen TVs and stereos.

Nordmende

was well known for its televisions throughout Ireland during the

1970s and 1980s, the company bought the rights to the name and

launched a range of white goods including fridges, freezers, washing machines, and dishwashers, alongside a revamped range of flat-screen TVs and stereos.

The pre-war history can be found under Mende. After the total loss in Dresden, Martin Mende (Dec. 30, 1898-1982) founds Norddeutsche Mende-Rundfunk GmbH in Bremen-Hemelingen on August 26, 1947, with the assistance of Hermann Weber.

The pre-war history can be found under Mende. After the total loss in Dresden, Martin Mende (Dec. 30, 1898-1982) founds Norddeutsche Mende-Rundfunk GmbH in Bremen-Hemelingen on August 26, 1947, with the assistance of Hermann Weber.- The first housings are supplied by a carpenter in Achim in exchange for five housings to make one radio set. The former Mende designer, Obering. Heer is again responsible for the equipment.

- From July 27, 1948, the new company, first 18 and soon 60 people, supplies the new radio production on the basis of currency reform, loans and subcontracts.

- The regime in East Germany does not allow the name Mende, so Martin Mende continues his pre-war success with graphic designs in connection with "Nord".

- The hangars of the former Focke-Wulf AG near Seebaldsbrück station serve as workshops. In 1950, the company employs 700 people, in 1959 already 3500 and at its zenith 6300.

- In 1950, the company starts with VHF, in 1953 with television and in 1954 with measuring and testing equipment. Towards the end of the 1950s, the company is called Norddeutsche Mende Rundfunk KG .

Having not previously been involved with magnetic sound equipment, Nordmende launches the first German home tape recorder with three motors in 1958. However, other companies such as AEG/Telefunken and Grundig clearly dominate this sector. From Nordmende, only one or two devices (none in 1960) appear in the catalogs. But the company is successful with another new entry:

In 1958, Nordmende introduces its first travel set, "Mambo" - but not "the first German, mass-produced and fully transistorized portable set," according to one source. After that, Nordmende becomes particularly strong in Germany in the travel set sector, although they did not build tube suitcases. After all, the 8 semiconductors used in "Mambo" then cost DM 98.70 at retail, while for the four D-tubes of the 90 series - even at the catalog price - about DM 35 would have to be spent. Price of the whole unit: DM 189.- plus two flat batteries of 4.5 V.

Until 1969, there are about 92 models of portable radios (suitcase radios or "hand held radios"). For example, in the 1961/62 catalog, there are 11 table radios and radio furniture as well as 8 models of travel radios. 17 different television models, on the other hand, show where success was to be found in those days.

According to ], Nordmende was even technically ahead for a short time with the so-called "Tippomatik operation". See also Philips etc.

Also concert cabinets seem to be a mainstay for Nordmende in the late 50s to early 60s. The company repeatedly uses the same names like "Cabinet", "Caruso", "Casino", "Cosima" as well as "Arabella" and "Isobella" with changing additional numbers or the addition "Stereo", e.g. in 1959 and 1960/61.- In March 1967, the plant started production of color TV sets. For the company's anniversary, a series of sets called 'Golden 20' is published. In 1969, the Mende sons Karl and Hermann take over the management.

- In 1977, increased competition leads to the sale of a majority stake to the French group Thomson-Brandt; the Mende family then withdraws completely from the company. Martin Mende dies in 1982.

- In 1977, shares in the company were sold to the French Thomson-Brandt Group. A year later, the family also sold its remaining share in Thomson-Brandt.

- During

Thomson's control, the production company changed its name several

times: Norddeutsche AG für Unterhaltungselektronik & Co. oHG

(NAGFU), later Deutsche AG für Unterhaltungselektronik & Co. oHG

(DAGFU). DAGFU became the holding company for the German Thomson

companies.

- Production was transferred to Deutsche Elektronik-Werke GmbH (DEWEK), which was formed from Süddeutsche Elektronikwerke GmbH (SEWEK), the former SABA production company. In the late 1980s, DEWEK was merged with Norddeutsche Elektronikwerke GmbH (NEWEK), the Telefunken production company, to form Elektronik-Werke Deutschland GmbH (EWD). EWD later operated under the name Thomson Television Germany GmbH (TTG).

- The sales company (oHG) was dissolved in the mid-1980s. Distribution in Germany was continued by Nordmende Vertriebs GmbH, which changed its name to Nordmende GmbH. Nordmende GmbH was merged with Telefunken Fernseh und Rundfunk GmbH with plants in Hanover and Celle, SABA GmbH, TTG and other companies in the mid-1990s to form Thomson Multimedia Sales GmbH.

The other company involved in Nordmende Vertriebs GmbH & Co. oHG, Nordmende Verkaufs GmbH, changed its name to Nordmende International GmbH and, under the umbrella of European Consumer Electronics GmbH (ECE), held the trademark rights to Nordmende for the export business, while the export business itself was handled by ECE. Nordmende International GmbH was sold to Thomson Consumer Electronics S.A. in Paris in the mid-1990s, changed its name to Thomson Consumer Electronics GmbH and acquired a share in DAGFU, as a result of which DAGFU changed its name to Thomson Consumer Electronics GmbH & Co. oHG.

Thomson's acquisition of Telefunken Fernseh und Rundfunk GmbH in Hanover in 1983 meant that all German Thomson production facilities now continued to operate under the name Elektronik Werke Deutschland (EWD).

While at the Villingen-Schwenningen site of SABA (SEWEK), Thomson's complete television set development and chassis production (printed circuit boards) were combined and television production was discontinued, the Bremen plant advanced to become the headquarters of color television set assembly for Thomson's German and European subsidiary brands. Only Telefunken was still allowed to build its own sets with its own chassis at the Celle plant (closed in 1997) because of its strong position in the German market.

Originally, Thomson had planned to close the Bremen site and abandon it completely. However, the company had not counted on the resistance of the employees and the support of the Bremen Senate and the great media response. Since Thomson already had a reputation in Germany as a "job killer" and did not want to put itself in a bad light again, the company backed down. Instead, production in Villingen-Schwenningen was closed and relocated to Bremen.

Then, in the mid-1980s, the Bremen Thomson plant was also on the verge of going out of business. In 1987, the managing directors took over the company in a management buy-out. With the social plan funds from Thomson, an investment from the state-owned Hanseatische Industrie-Beteiligungen GmbH (HIBEG) and loans from leading Bremen banks, the television set and plastic parts production was continued with a greatly reduced workforce under the name Europart (the planned name was initially Eurotec).

End of production

At the end of the 1980s, after Thomson had stopped purchasing plastic parts from Europart for its television set production, which had been relocated in the meantime, the company plunged into a crisis from which it never recovered. The company's own developments were unable to establish themselves on the market in parallel with supplier production, so that despite rescue attempts by the Bremen Senate and a plant occupation lasting several weeks, the company went into insolvency because the banks had cancelled their credit lines.

Nordmende brand under Thomson

Immediately after acquiring the company, Thomson separated production and sales into two companies. While production was controlled directly from the headquarters in Paris, sales initially remained independent. The production of audio equipment was discontinued in Germany and relocated to France. After the closure of several factories in the Bremen area, the television production in Bremen and the Kit Center in Bremerhaven remained. At the Kit Center, kits were assembled for countries that required a domestic production content (local content).

The main markets for Nordmende were Germany and Italy. Qualified specialist retailers were used as the sales channel in Germany and general importers for the export markets. After the export activities of the group brands Nordmende, Telefunken and SABA were combined under the umbrella of ECE GmbH in Hanover in 1987, domestic sales continued to operate independently from Bremen for several years.

In the early 1990s, Thomson was forced to reorganize its domestic sales operations as a result of the cut-throat competition from low-cost large-scale sales organizations. The distribution of the Nordmende, Telefunken and SABA brands was centralized in Hanover. Brand families were established: SABA and Brandt (France) as price-oriented brands for the large-scale distribution forms, Telefunken as a quality brand for the retail trade, and Nordmende and Thomson (France) as design-oriented brands for the upper price segment.

When the Thomson Group became involved in Germany, it avoided using the Thomson name for a long time, which was also expressed in company names such as SEWEK, EWD or DAGFU. In the 1990s, a change occurred. Various companies were rebranded with the Thomson name. As a final consequence, the Nordmende brand was also taken off the market and replaced by Thomson, which led to an even faster decline in Germany.

Nordmende today

Since the end of 2007, the Nordmende brand name has again appeared sporadically in connection with LCD televisions. The Indian consumer electronics group Videocon took over a television tube factory in Anagni, Italy, from the French Thomson Group, acquiring the trademark rights of the formerly traditional German brand Nordmende. The Phillar Group has been using the Nordmende name since 2008.

In Italy in particular, design-oriented flat-screen televisions are sold under the Nordmende brand. Since 2014, the Nordmende brand name has also been used in connection with electronic hearing aid-like devices.

In April 2017, TechniSat acquired the license to use the Nordmende brand for Germany, Austria, Switzerland as well as Poland from the brand owner Technicolor S.A.. The first Nordmende devices from the TV sets and DAB+ digital radios segments were presented at IFA 2017.

NORDMENDE HISTORY IN GERMAN:

Die Vorkriegsgeschichte findet sich unter Mende. Nach dem Totalverlust in Dresden gründet Martin Mende (30.12.1898-1982) unter Mitwirkung von Hermann Weber am 26. August 1947 in Bremen-Hemelingen die Norddeutsche Mende-Rundfunk GmbH.

Die ersten Gehäuse liefert ein Tischler in Achim gegen Kompensation von fünf Gehäusen zu einem Rundfunkgerät. Der frühere Mende-Konstrukteur, Obering. Heer zeichnet wieder für die Geräte verantwortlich .

Ab 27. Juli 1948 liefert die neue, zuerst 18 und bald 60 Personen umfassende Firma auf Grund von Währungsreform, Krediten und Zulieferverträgen die neue Radioproduktion.

Das Regime in Ostdeutschland lässt den Namen Mende nicht zu, so dass Martin Mende mit grafischen Konstruktionen im Zusammenhang mit «Nord» an seinen Vorkriegserfolg anschliesst.

Die Hallen der ehemaligen Focke-Wulf AG beim Bahnhof Seebaldsbrück dienen als Werkstätten. 1950 beschäftigt das Unternehmen 700, 1959 schon 3500 und im Zenit 6300 Personen.

1950 beginnt die Firma mit UKW-, 1953 mit Fernseh- und 1954 mit Mess- und Prüfgeräten. Gegen Ende der 50er Jahre heisst die Firma Norddeutsche Mende Rundfunk KG .

Nachdem sich Nordmende bislang nicht mit Magnettongeräten befasst hat, bringt das Werk 1958 das erste deutsche Heim-Tonbandgerät mit drei Motoren auf den Markt. Allerdings dominieren auf diesem Sektor eindeutig andere Firmen wie AEG/Telefunken und Grundig. Von Nordmende kommen jeweils nur ein bis zwei Geräte (1960 keines) in die Kataloge. Dafür hat die Firma Erfolg mit einem anderen Neueinstieg:

1958 stellt Nordmende mit «Mambo» ihr erstes Reisegerät vor - aber nicht «das erste deutsche, serienmässig hergestellte und volltransistorisierte Koffergerät», wie man aus einer Quelle nachlesen kann. Danach wird Nordmende in Deutschland auf dem Sektor Reisegeräte besonders stark, obwohl sie keine Röhren-Koffer baute. Immerhin kosten die in «Mambo» verwendeten 8 Halbleiter dann im Einzelhandel DM 98.70, während für die vier D-Röhren der 90er-Serie - auch zum Katalogpreis - etwa DM 35.- auszugeben wären. Preis des ganzen Gerätes: DM 189.- plus zwei Flachbatterien von 4,5 V.

Bis 1969 gibt es ca. 92 Modelle der tragbaren Radios (Koffer- bzw. «Handradios», d.h. «Hand held radios»). Beispielsweise finden sich im Katalog 1961/62 je 11 Tischradios und Radiomöbel sowie 8 Modelle von Reiseradios. 17 verschiedene Fernsehmodelle zeigen dagegen, wo in jener Zeit der Erfolg zu holen war.

Gemäss ] liegt Nordmende während kurzer Zeit mit der sogenannten «Tippomatik-Bedienung» sogar technisch vorne. Siehe auch Philips etc.

Auch Konzertschränke scheinen Ende der 50er bis Anfang 60er Jahre eine tragende Säule für Nordmende zu sein. Dabei verwendet die Firma immer wieder gleiche Namen wie «Cabinet», «Caruso», «Casino», «Cosima» sowie «Arabella» und «Isobella» mit wechselnden Zusatz-Nummern oder den Zusatz «Stereo», z.B. in den Jahren 1959 und 1960/61.

Im März 1967 nimmt das Werk die Produktion von Farbfernsehgeräten auf. Zum Firmenjubiläum erscheint eine Gerätereihe mit der Bezeichnung 'Goldene 20'. 1969 übernehmen die Mende-Söhne Karl und Hermann die Geschäftsführung.

1977 führt der verschärfte Wettbewerb zum Verkauf der Mehrheit an den französischen Konzern Thomson-Brandt; die Familie Mende zieht sich anschliessend ganz aus dem Unternehmen zurück. Martin Mende stirbt 1982.

1977 wurden Anteile des Unternehmens an den französischen Thomson-Brandt-Konzern verkauft. Ein Jahr später veräußerte die Familie auch ihren verbliebenen Anteil an Thomson-Brandt.

Das Bremer Unternehmen bestand stets aus zwei Gesellschaften. Die Produktion erfolgte bei der Norddeutsche Mende Rundfunk KG; den Vertrieb und die Werbung übernahm die Nordmende Vertriebs GmbH & Co. oHG.

Während der Beherrschung durch Thomson änderte die Produktionsgesellschaft mehrfach ihren Namen: Norddeutsche AG für Unterhaltungselektronik & Co. oHG (NAGFU), später Deutsche AG für Unterhaltungselektronik & Co. oHG (DAGFU). Die DAGFU wurde zur Holding der deutschen Thomson-Gesellschaften.

Die Produktion ging auf die Deutschen Elektronik-Werke GmbH (DEWEK) über, die aus der Süddeutschen Elektronikwerke GmbH (SEWEK), der ehemaligen SABA-Produktionsgesellschaft, entstanden ist. Ende der 1980er Jahre wurde die DEWEK mit der Norddeutschen Elektronikwerke GmbH (NEWEK), der Telefunken-Produktionsgesellschaft, zur Elektronik-Werke Deutschland GmbH (EWD) fusioniert. Die EWD firmierte später als Thomson Television Germany GmbH (TTG).

Die Vertriebsgesellschaft (oHG) wurde Mitte der 1980er Jahre aufgelöst. Der Vertrieb in Deutschland wurde von der Nordmende Vertriebs GmbH fortgeführt, die sich in Nordmende GmbH umbenannte. Die Nordmende GmbH wurde Mitte der 1990er Jahre zusammen mit der Telefunken Fernseh und Rundfunk GmbH mit Werken in Hannover und Celle, der SABA GmbH, der TTG und anderen Gesellschaften zur Thomson Multimedia Sales GmbH verschmolzen.

Die andere, an der Nordmende Vertriebs GmbH & Co. oHG beteiligte Gesellschaft, die Nordmende Verkaufs GmbH, firmierte in Nordmende International GmbH um und hielt unter dem Dach der European Consumer Electronics GmbH (ECE) die Markenrechte an Nordmende für das Export-Geschäft, während das Export-Geschäft an sich von der ECE wahrgenommen wurde. Die Nordmende International GmbH wurde Mitte der 1990er Jahre an die Thomson Consumer Electronics S.A. in Paris verkauft, firmierte in Thomson Consumer Electronics GmbH um und erwarb einen Anteil an der DAGFU, wodurch die DAGFU in Thomson Consumer Electronics GmbH & Co. oHG umfirmierte.

Durch Thomsons Übernahme der Telefunken Fernseh und Rundfunk GmbH in Hannover im Jahr 1983 wurden nunmehr alle deutschen Thomson-Produktionsstätten unter dem Namen Elektronik Werke Deutschland (EWD) weitergeführt.

Während am Standort Villingen-Schwenningen bei SABA (SEWEK) die komplette Fernsehgeräte-Entwicklung und Chassis-Produktion (Leiterplatten) von Thomson zusammengefasst und die Fernseher-Produktion aufgegeben wurde, avancierte das Bremer Werk zur Zentrale der Farbfernsehgerätemontage der deutschen und europäischen Thomson-Tochtermarken. Lediglich Telefunken durfte im Werk Celle (1997 geschlossen) wegen seiner starken Position am deutschen Markt noch eigene Geräte mit eigenem Chassis bauen.

Ursprünglich hatte Thomson geplant, den Standort Bremen zu schließen und komplett aufzugeben. Der Konzern hatte jedoch nicht mit dem Widerstand der Beschäftigten und der Unterstützung durch den Bremer Senat und dem großen Medienecho gerechnet. Da Thomson in Deutschland bereits einen Ruf als „Jobkiller“ hatte und sich nicht erneut ins schlechte Licht rücken wollte, machte das Unternehmen einen Rückzieher. Stattdessen wurde die Produktion in Villingen-Schwenningen geschlossen und nach Bremen verlagert.

Mitte der 1980er Jahre stand dann auch das Bremer Thomson-Werk vor dem Aus. 1987 übernahmen die Geschäftsführer im Zuge eines Management Buy Outs das Unternehmen. Mit den Sozialplan - Geldern von Thomson, einer Beteiligung der landeseigenen Hanseatischen Industrie-Beteiligungen GmbH (HIBEG) und Krediten führender Bremer Banken wurden die Fernsehgeräte- und Kunststoff teile produktion, mit einer stark reduzierten Belegschaft, unter dem Namen Europart (geplanter Name war zunächst Eurotec) fortgeführt.

Ende der Produktion

Nachdem Thomson Ende der 1980er Jahre seine Kunststoffteile für die inzwischen verlagerte Fernsehgeräte produktion nicht mehr von Europart bezog, stürzte das Unternehmen in eine Krise, von der es sich nicht mehr erholte. Eigene Entwicklungen konnten sich parallel zur Zulieferproduktion am Markt nicht etablieren, so dass das Unternehmen trotz der Rettungsversuche durch den Bremer Senat und einer mehrwöchigen Werksbesetzung in die Insolvenz ging, da die Banken ihre Kreditlinien gekündigt hatten.

Marke Nordmende unter Thomson

Unverzüglich nach Erwerb des Unternehmens trennte Thomson Produktion und Vertrieb in zwei Gesellschaften auf. Während die Produktion direkt von der Zentrale in Paris gesteuert wurde, blieb der Vertrieb zunächst eigenständig. Die Produktion von Audio-Geräten wurde in Deutschland eingestellt und nach Frankreich verlagert. Nach Schließung mehrerer Fabriken im Bremer Umland blieben die Fernsehproduktion in Bremen und das Kit Center in Bremerhaven übrig. Im Kit Center wurden Bausätze für Länder zusammengestellt, die einen inländischen Produktionsanteil (local content) forderten.

Die Hauptmärkte für Nordmende waren Deutschland und Italien. Als Vertriebskanal in Deutschland wurde der qualifizierte Facheinzelhandel und für die Exportmärkte Generalimporteure genutzt. Nachdem die Exportaktivitäten der Konzernmarken Nordmende, Telefunken und SABA im Jahr 1987 unter dem Dach der ECE GmbH in Hannover zusammengefasst worden waren, agierte der Inlandsvertrieb noch einige Jahre eigenständig von Bremen aus.

Durch den Verdrängungswettbewerb der preisgünstigen Großvertriebsformen sah sich Thomson Anfang der neunziger Jahre gezwungen, den Inlandsvertrieb neuzuordnen. Die Vertriebe der Marken Nordmende, Telefunken und SABA wurden in Hannover zentralisiert. Es wurden Markenfamilien gegründet: SABA und Brandt (Frankreich) als preisorientierte Marken für die Großvertriebsformen, Telefunken als Qualitätsmarke für den Einzelfachhandel sowie Nordmende und Thomson (Frankreich) als designorientierte Marken für das gehobene Preissegment.

Als der Thomson-Konzern sich in Deutschland engagierte, wurde es lange Zeit vermieden, unter dem Namen Thomson aufzutreten, was sich auch in Gesellschaftsbezeichnungen wie SEWEK, EWD oder DAGFU ausdrückte. In den 1990er Jahren trat ein Wandel ein. Verschiedene Gesellschaften wurden mit dem Namensbestandteil Thomson umfirmiert. Als letzte Konsequenz wurde auch die Marke Nordmende vom Markt genommen und durch Thomson ersetzt, was zu einem noch schnelleren Niedergang in Deutschland führte.

Nordmende heute

Seit Ende 2007 taucht wieder vereinzelt der Markenname Nordmende in Zusammenhang mit LCD-Fernsehgeräten auf. Der indische Unterhaltungselektronik-Konzern Videocon hat von der französischen Thomson-Gruppe ein Fernsehröhrenwerk im italienischen Anagni übernommen und dabei die Markenrechte der ehemals deutschen Traditionsmarke Nordmende erworben. Seit 2008 verwendet die Phillar Group die Bezeichnung Nordmende.

Besonders in Italien werden unter der Marke Nordmende gestaltungsorientierte Flachbild-Fernsehgeräte vertrieben. Seit 2014 wird der Markenname Nordmende auch im Zusammenhang mit elektronischen hörgeräteähnlichen Geräten verwendet.

Im April 2017 erwarb TechniSat vom Markeninhaber Technicolor S.A. die Lizenz zur Nutzung der Marke Nordmende für Deutschland, Österreich, Schweiz sowie Polen. Zur IFA 2017 wurden die ersten Nordmende-Geräte aus den Segmenten TV-Geräte und DAB+-Digitalradios präsentiert.

In 1879 Elihu Thomson and Edwin Houston formed the Thomson-Houston Electric Company in the United States.

On April 15, 1892 Thomson-Houston and the Edison General Electric Company merged to form General Electric (GE). Also in 1892 the company formed a French subsidiary, Thomson Houston International.

In 1893 Compagnie Française Thomson-Houston (CFTH) was set up as a partner to GE. It is from this company that the modern Thomson companies would evolve.

In 1966 CFTH merged with Hotchkiss-Brandt to form Thomson-Houston-Hotchkiss-Brandt (soon renamed Thomson-Brandt). In 1968 the electronics business of Thomson-Brandt merged with Compagnie Générale de Télégraphie Sans Fil (CSF) to form Thomson-CSF. Thomson Brandt maintained a significant shareholding in this company (approximately 40%).

In 1982 both Thomson-Brandt and Thomson-CSF were nationalized by François Mitterrand. Thomson-Brandt was renamed Thomson SA (Société Anonyme) and merged with Thomson-CSF.

From 1983 to 1987 a major reorganisation of Thomson-CSF was undertaken, with divestitures to refocus the group on its core activities (electronics and defence). Thomson-CSF Téléphone and the medical division were sold to Alcatel and GE respectively. The semiconductor businesses of Thomson CSF was merged with Finmeccanica. Thomson acquired General Electric’s RCA and GE consumer electronics business in 1987.

In 1988 Thomson Consumer Electronics was formed, renamed Thomson Multimedia in 1995. The French government split the consumer electronics and defence businesses prior to privatisation in 1999, those companies being Thomson Multimedia (today Technicolor SA) and Thomson-CSF (today Thales Group).

Thomson-CSF was a major electronics and defence contractor. In December 2000 it was renamed Thales Group.

...........1996............there are no stranger foreigners than the first ones you come across, the French. This is borne out by the 1996 Thomson situation. Thomson, was a vast company by any reckoning, is a strange beast. It's state controlled, which means that the government owns most but not quite all of it. and consists of two distinct arms, the defence group Thomson-CFS which is quite profitable, and the consumer electronics group Thomson Multimedia which loses a packet. The government wanted rid of it, but won't sell the bits separately. It doesn't want to be left with the problem of what to do with Thomson Multimedia. You might think that no one would be interested in helping the French government. But in fact there are two contenders to take over Thomson, the telecommunications and power group Alcatel Alsthom and the defence and media group Lagardere. They have been engaging in quite a battle over the ownership, and as we go to press the French government is due to decide whose bid to accept. Whoever wins will end up with the profitable defence company and the problem of Thomson Multimedia (TMM).

Lagardere has stated that it would sell TMM to Daewoo of Korea. Alcatel Alsthom has not been quite so specific, but has announced that it would take immediate action to reduce TMM's losses and seek an "Asian partner" that "specialises in consumer electronics". The partner would be expected to take over management of TMM, but Alcatel would like to remain a "minority partner" - it sees prospects in the move to digital TV technology that will occur during the next decade. All this gives one a strange feeling of déjà vu. At the time when Thomson took over Ferguson, in June 1987, it was noticed that Thomson is "now on the government's privatisation list". It's taken almost a decade to happen.

It's also said that "Thomson may be big, but has not been all that successful in the past in the consumer electronics field". Right on! What has happened to Ferguson in the UK illustrates the dismal Thomson effect. From being the local brand leader, with over ten per cent of the market, Ferguson has ended up being an also ran. It's only fair however to mention that Ferguson was making substantial losses when Thorn EMI was glad to get £90m for it from Thomson. Thomson has been able to survive in the consumer electronics field because it is part of a larger organisation, with those defence profits. It has nevertheless over the years attempted to play a a major role in the international consumer electronics field, keeping up with Philips and the Japanese corporations. From its French origins, it first expanded by picking up various German companies such as NordMende an SABA. It added Telefunken, a venerable name if ever there was one in this industry, in the early eighties, then took what was to be a big move into the UK market when it bought Ferguson.

It used six brand names in Europe. The largest step however occurred when TMM became a major force in the North American market by taking over General Electric's consumer electronics interests. This also gave it the RCA operation. The idea behind all this seems to have been to achieve success simply by getting bigger. There was always government finance to back the policy, which in the event has not been a success. The TMM debacle is a sad one, since Thomson's research and engineering has had many successes.

It has not stinted on R and D work, with laboratories in Los Angeles, Indianapolis, Strasbourg, Hanover, Villingen, Tokyo and Singapore. Much work has been done on HD -TV, digital signal processing and other developments that have kept it in the forefront of the technology. Now, it seems, TMM is likely to be swallowed up by one of the Oriental corporate giants.

If there are any lessons to be drawn, they would seem to be that expansion by itself is no guarantee of success, that to spread ones activities and their control across the globe makes management extremely difficult, and that costs are very hard to control in such a context. Alcatel Alsthom's plans to reduce TMM's losses bear this out. It would close down TMM's US factories, transferring production to the company's modern facilities in Mexico, where wages are much lower.

It would rationalise the large collection of brands, possibly adopting RCA as the main one worldwide. And there is a suggestion that the company should be run from the USA, since this is its largest market. But all this would be just initial steps towards ceding majority control. Venerable brand names such as Telefunken, GE and RCA would pass to oriental ownership. This will happen whoever wins, Alcatel Alsthom or Lagardere, which would leave just Philips to carry on Europe's traditions in the consumer electronics field............. but we all know how it ended.................

Thomson-CSF independence

Following the privatisation of the Thomson Group Thomson-CSF explored the possibility of merging with Marconi Electronic Systems, however British Aerospace was successful in that aim, forming BAE Systems.

In 2000 Thomson-CSF went through a series of transactions, including with Marconi plc. The major acquisition at this time was the £1.3 billion purchase of the British defence electronics firm, Racal. This made Thomson-CSF the second largest participant in the UK defence industry after BAE. Racal was renamed Thomson-CSF Racal plc.

On December 6, 2000 the group was renamed Thales.

------------------------------------------------------------------------------------------------------------

Further reading

- Jean-Pierre, Thierry (16 October 2003). Taïwan Connection : Scandales et meurtres au cœur de la République [Taiwan Connection – Scandals and Murders at the Heart of the Republic] (in French). Robert Laffont. ISBN 978-2221100820.

- L'entreprise partagée ? Une pratique différente des relations sociales : l'expérience Thomson-CSF, Robert Thomas (pseudonym for a team-work with Pierre Beretti and Jean-Pierre Thiollet), Paris, Maxima-Laurent du Mesnil Ed., 1999

- Ein neues Programm. Artikel in der Zeit

Fernseher: Inder produzieren neue Nordmende. Artikel bei itespresso.de

Videocon produziert Plasmaschirme für Nordmende. Artikel im pressetext.de

Mende/Nordmende-Prospekte von 1938 bis 1985, auf hifi-archiv.info

Nordmende | Ikonische Produkte

Einzelnachweise:

- Spectra Color Studio und Spectra SK2 Color de Luxe Studio auf radiomuseum.org

- Michael Gassmann: Die Marke Nordmende kommt zurück. In: DIE WELT. 28. August 2017 (welt.de [abgerufen am 4. April 2020]). Company profile. Phillar, archiviert vom Original am 6. März 2008; abgerufen am 26. April 2013 (englisch).

- Broschüre – Sprachmanager24. Abgerufen am 5. Januar 2015.

- Marke Nordmende mit Digital- und Internetradios zurück, teltarif.de, Artikel vom 2. September 2017.

«Annual Report 2010». STMicroelectronics. Consultado el 17 de noviembre de 2011.

Castelletto en ST

http://www.st.com/content/st_com/en/contact-us.html#EUROPE

«SGS-Thomson Microelectronics Becomes STMicroelectronics | EE Times». EETimes. Consultado el 6 de julio de 2017.

Peter Robin Morris (1990). A History of the World Semiconductor Industry. The Institution of Engineering and Technology. ISBN 9780863412271.

Okada, Yoshitaka (2006). Struggles for Survival. Institutional and Organizational Changes in Japan's High-Tech Industries. Springer. ISBN 9784431288749.

Franco Malerba (1985). The Semiconductor Business: The Economics of Rapid Growth and Decline (Economics of Technological Change). Madison, University of Wisconsin Press. ISBN 9780299104603.

- Eintrag im Handelsregister des Kantons Genf

- Volker Briegleb: Chiphersteller STMicroelectronics baut 1400 Jobs ab. In: Heise online. 28. Januar 2016. Abgerufen am 28. Januar 2016.

- st.com: Company Information, abgerufen 24. Januar 2020 (englisch)

- Who We Are. STMicroelectronics, Januar 2017, abgerufen am 14. Oktober 2017 (englisch).

- STMicroelectronics Outlines Next Steps to Improve Cost Structure. (Nicht mehr online verfügbar.) 10. Juli 2007, archiviert vom Original am 13. Juli 2007; abgerufen am 29. Dezember 2015 (Pressemitteilung).

- Intel, STMicroelectronics, and Francisco Partners Establish a new leader in Flash memories. (Nicht mehr online verfügbar.) 22. Mai 2007, archiviert vom Original am 6. März 2008; abgerufen am 22. Mai 2007 (Pressemitteilung).

- STMicroelectronics Completes Acquisition of Genesis Microchip. (Nicht mehr online verfügbar.) 25. Januar 2008, archiviert vom Original am 10. März 2008; abgerufen am 9. Juni 2010 (englisch, Pressemitteilung).

- Gescheiterte Kooperation: Ericsson und STMicro lösen Joint Venture auf. In: www.handelsblatt.com. 18. März 2013, abgerufen am 24. Januar 2020.