The BS465 Is the brother of the BS400 for the 90° degree CRT tubes family and was first ZANUSSI chassis with power supply developed around SIEMENS TDA4600.

It runs almost cool and is an example of absolute everlasting tv chassis pratically bugless with highly over sized components in almost all sections (see the BU208A in Line deflection and in Power supply), further you can see the Line Deflection EHT Transformer which can serve easyly a 37 Inches without

problems !!!!!

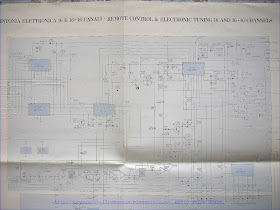

UNITS FUNCTION DESCRIPTION CHASSIS BS465.2

- POWER SUPPLY WITH BU208A It converts the mains voltage in DC voltage available at five outputs with values of: +2OOV; +12OV; +27V (two outputs); +12.6V. These voltages are stabilized and separated from the mains.

Switched Mode Power supply Description based on TDA4601d (SIEMENS)

TDA4601 Operation. * The TDA4601 device is a single in line, 9 pin chip. Its predecessor was the TDA4600 device, the TDA4601 however has improved switching, better protection and cooler running. The (SIEMENS) TDA4601 power supply is a fairly standard parallel chopper switch mode type, which operates on the same basic principle as a line output stage. It is turned on and off by a square wave drive pulse, when switched on energy is stored in the chopper transformer primary winding in the form of a magnetic flux; when the chopper is turned off the magnetic flux collapses, causing a large back emf to be produced. At the secondary side of the chopper transformer this is rectified and smoothed for H.T. supply purposes. The advantage of this type of supply is that the high chopping frequency (20 to 70 KHz according to load) allows the use of relatively small H.T. smoothing capacitors making smoothing easier. Also should the chopper device go short circuit there is no H.T. output. In order to start up the TDA4601 I.C. an initial supply of 9v is required at pin 9, this voltage is sourced via R818 and D805 from the AC side of the bridge rectifier D801, also pin 5 requires a +Ve bias for the internal logic block. (On some sets pin 5 is used for standby switching). Once the power supply is up and running, the voltage on pin 9 is increased to 16v and maintained at this level by D807 and C820 acting as a half wave rectifier and smoothing circuit. PIN DESCRIPTIONS Pin 1 This is a 4v reference produced within the I.C. Pin 2 This pin detects the exact point at which energy stored in the chopper transformer collapses to zero via R824 and R825, and allows Q1 to deliver drive volts to the chopper transistor. It also opens the switch at pin 4 allowing the external capacitor C813 to charge from its external feed resistor R810. Pin 3 H.T. control/feedback via photo coupler D830. The voltage at this pin controls the on time of the chopper transistor and hence the output voltage. Normally it runs at Approximately 2v and regulates H.T. by sensing a proportion of the +4v reference at pin 1, offset by conduction of the photo coupler D830 which acts like a variable resistor. An increase in the conduction of transistor D830 and therefor a reduction of its resistance will cause a corresponding reduction of the positive voltage at Pin 3. A decrease in this voltage will result in a shorter on time for the chopper transistor and therefor a lowering of the output voltage and vice versa, oscillation frequency also varies according to load, the higher the load the lower the frequency etc. should the voltage at pin 3 exceed 2.3v an internal flip flop is triggered causing the chopper drive mark space ratio to extend to 244 (off time) to 1 (on time), the chip is now in over volts trip condition. Pin 4 At this pin a sawtooth waveform is generated which simulates chopper current, it is produced by a time constant network R810 and C813

. C813 charges when the chopper is on and is discharged when the chopper is off, by an internal switch strapping pin 4 to the internal +2v reference, see Fig 2. The amplitude of the ramp is proportional to chopper drive. In an overload condition it reaches 4v amplitude at which point chopper drive is reduced to a mark-space ratio of 13 to 1, the chip is then in over current trip. The I.C. can easily withstand a short circuit on the H.T. rail and in such a case the power supply simply squegs quietly. Pin 4 is protected by internal protection components which limit the maximum voltage at this pin to 6.5v. Should a fault occur in either of the time constant components, then the chopper transistor will probably be destroyed. Pin 5 This pin can be used for remote control on/off switching of the power supply, it is normally held at about +7v and will cause the chip to enter standby mode if it falls below 2v. Pin 6 Ground. Pin 7 Chopper switch off pin. This pin clamps the chopper drive voltage to 1.6v in order to switch off the chopper. Pin 8 Chopper base current output drive pin. Pin 9 L.T. pin, approximately 9v under start-up conditions and 16v during normal running, Current consumption of the I.C. is typically 135mA. The voltage at this pin must reach 6.7v in order for the chip to start-up.

. C813 charges when the chopper is on and is discharged when the chopper is off, by an internal switch strapping pin 4 to the internal +2v reference, see Fig 2. The amplitude of the ramp is proportional to chopper drive. In an overload condition it reaches 4v amplitude at which point chopper drive is reduced to a mark-space ratio of 13 to 1, the chip is then in over current trip. The I.C. can easily withstand a short circuit on the H.T. rail and in such a case the power supply simply squegs quietly. Pin 4 is protected by internal protection components which limit the maximum voltage at this pin to 6.5v. Should a fault occur in either of the time constant components, then the chopper transistor will probably be destroyed. Pin 5 This pin can be used for remote control on/off switching of the power supply, it is normally held at about +7v and will cause the chip to enter standby mode if it falls below 2v. Pin 6 Ground. Pin 7 Chopper switch off pin. This pin clamps the chopper drive voltage to 1.6v in order to switch off the chopper. Pin 8 Chopper base current output drive pin. Pin 9 L.T. pin, approximately 9v under start-up conditions and 16v during normal running, Current consumption of the I.C. is typically 135mA. The voltage at this pin must reach 6.7v in order for the chip to start-up.Semiconductor circuit for supplying pow

er to electrical equipment, comprising a transformer having a primary winding connected, via a parallel connection of a collector-emitter path of a transistor with a first capacitor, to both outputs of a rectifier circuit supplied, in turn, by a line a-c voltage; said transistor having a base controlled via a second capacitor by an output of a control circuit acted upon, in turn by the rectified a-c line voltage as actual value and by a reference voltage; said transformer having a first secondary winding to which the electrical equipment to be supplied is connected; said transformer having a second secondary winding with one terminal thereof connected to the emitter of said transistor and the other terminal thereof connected to an anode of a first diode leading to said control circuit; said transformer having a third secondary winding with one terminal thereof connected, on the one hand, via a series connection of a third capacitor with a first resistance, to the other terminal of said third secondary winding and connected, on the other hand, to the emitter of said transistor, the collector of which is connected to said primary winding; a point between said third capacitor and said first resistance being connected to the cathode of a second diode; said control circuit having nine terminals including a first terminal delivering a reference voltage and connected, via a voltage divider formed of a third and fourth series-connected resistances, to the anode of said second diode; a second terminal of said control circuit serving for zero-crossing identification being connected via a fifth resista

er to electrical equipment, comprising a transformer having a primary winding connected, via a parallel connection of a collector-emitter path of a transistor with a first capacitor, to both outputs of a rectifier circuit supplied, in turn, by a line a-c voltage; said transistor having a base controlled via a second capacitor by an output of a control circuit acted upon, in turn by the rectified a-c line voltage as actual value and by a reference voltage; said transformer having a first secondary winding to which the electrical equipment to be supplied is connected; said transformer having a second secondary winding with one terminal thereof connected to the emitter of said transistor and the other terminal thereof connected to an anode of a first diode leading to said control circuit; said transformer having a third secondary winding with one terminal thereof connected, on the one hand, via a series connection of a third capacitor with a first resistance, to the other terminal of said third secondary winding and connected, on the other hand, to the emitter of said transistor, the collector of which is connected to said primary winding; a point between said third capacitor and said first resistance being connected to the cathode of a second diode; said control circuit having nine terminals including a first terminal delivering a reference voltage and connected, via a voltage divider formed of a third and fourth series-connected resistances, to the anode of said second diode; a second terminal of said control circuit serving for zero-crossing identification being connected via a fifth resista nce to said cathode of said second diode; a third terminal of said control-circuit serving as actual value input being directly connected to a divider point of said voltage divider forming said connection of said first terminal of said control circuit to said anode of said second diode; a fourth terminal of said control circuit delivering a sawtooth voltage being connected via a sixth resistance to a terminal of said primary winding of said transformer facing away from said transistor; a fifth terminal of said control circuit serving as a protective input being connected, via a seventh resistance to the cathode of said first diode and, through the intermediary of said seventh resistance and an eighth resistance, to the cathode of a third diode having an anode connected to an input of said rectifier circuit; a sixth terminal of said control circuit carrying said reference potential and being connected via a fourth capacitor to said fourth terminal of said control circuit and via a fifth capacitor to the anode of said second diode; a seventh terminal of said control circuit establishing a potential for pulses controlling said transistor being connected directly and an eighth terminal of said control circuit effecting pulse control of the base of said transistor being connected through the intermediary of a ninth resistance to said first capacitor leading to the base of said transistor; and a ninth terminal of said control circuit serving as a power supply input of said control circuit being connected both to the cathode of said first diode as well as via the intermediary of a sixth capacitor to a terminal of said second secondary winding as well as to a terminal of said third secondary winding.

nce to said cathode of said second diode; a third terminal of said control-circuit serving as actual value input being directly connected to a divider point of said voltage divider forming said connection of said first terminal of said control circuit to said anode of said second diode; a fourth terminal of said control circuit delivering a sawtooth voltage being connected via a sixth resistance to a terminal of said primary winding of said transformer facing away from said transistor; a fifth terminal of said control circuit serving as a protective input being connected, via a seventh resistance to the cathode of said first diode and, through the intermediary of said seventh resistance and an eighth resistance, to the cathode of a third diode having an anode connected to an input of said rectifier circuit; a sixth terminal of said control circuit carrying said reference potential and being connected via a fourth capacitor to said fourth terminal of said control circuit and via a fifth capacitor to the anode of said second diode; a seventh terminal of said control circuit establishing a potential for pulses controlling said transistor being connected directly and an eighth terminal of said control circuit effecting pulse control of the base of said transistor being connected through the intermediary of a ninth resistance to said first capacitor leading to the base of said transistor; and a ninth terminal of said control circuit serving as a power supply input of said control circuit being connected both to the cathode of said first diode as well as via the intermediary of a sixth capacitor to a terminal of said second secondary winding as well as to a terminal of said third secondary winding.

Description:

The invention relates to a blocking oscillator type switching power supply for supplying power to electrical equipment, wherein the primary winding of a transformer, in series with the emitter-collector path of a first bipolar transistor, is connected to a d-c voltage obtained by rectification of a line a-c voltage fed-in via two external supply terminals, and a secondary winding of the transformer is provided for supplying power to the electrical equipment, wherein, furthermore, the first bipolar transistor has a base controlled by the output of a control circuit which is acted upon in turn by the rectified a-c line voltage as actual value and by a set-point transmitter, and wherein a starting circuit for further control of the base of the first bipolar transistor is provided.

The invention relates to a blocking oscillator type switching power supply for supplying power to electrical equipment, wherein the primary winding of a transformer, in series with the emitter-collector path of a first bipolar transistor, is connected to a d-c voltage obtained by rectification of a line a-c voltage fed-in via two external supply terminals, and a secondary winding of the transformer is provided for supplying power to the electrical equipment, wherein, furthermore, the first bipolar transistor has a base controlled by the output of a control circuit which is acted upon in turn by the rectified a-c line voltage as actual value and by a set-point transmitter, and wherein a starting circuit for further control of the base of the first bipolar transistor is provided. Such a blocking oscillator switching power supply is described in the German periodical, "Funkschau" (1975) No. 5, pages 40 to 44. It is well known that the purpose of such a circuit is to supply electronic equipment, for example, a television set, with stabilized and controlled supply voltages. Essential for such switching power supply is a power switching transistor i.e. a bipolar transistor with high switching speed and high reverse voltage. This transistor therefore constitutes an important component of the control element of the control circuit. Furthermore, a high operating frequency and a transformer intended for a high operating frequency are provided, because generally, a thorough separation of the equipment to be supplied from the supply naturally is desired. Such switching power supplies may be constructed either for synchronized or externally controlled operation or for non-synchronized or free-running operation. A blocking converter is understood to be a switching power supply in which power is delivered to the equipment to be supplied only if the switching transistor establishing the connection between the primary coil of the transformer and the rectified a-c voltage is cut off. The power delivered by the line rectifier to the primary coil of the transformer while the switching transistor is open, is interim-stored in the transformer and then delivered to the consumer on the secondary side of the transformer with the switching transistor cut off.

In the blocking converter described in the aforementioned reference in the literature, "Funkschau" (1975), No. 5, Pages 40 to 44, the power switching transistor is connected in the manner defined in the introduction to this application. In addition, a so-called starting circuit is provided. Because several diodes are generally provided in the overall circuit of a blocking oscillator according to the definition provided in the introduction hereto, it is necessary, in order not to damage these diodes, that due to the collector peak current in the case of a short circuit, no excessive stress of these diodes and possibly existing further sensitive circuit parts can occur.

Considering the operation of a blocking oscillator, this means that, in the event of a short circuit, the number of collector current pulses per unit time must be reduced. For this purpose, a control and regulating circuit is provided. Simultaneously, a starting circuit must bring the blocking converter back to normal operation when the equipment is switched on, and after disturbances, for example, in the event of a short circuit. The starting circuit shown in the literature reference "Funkschau" on Page 42 thereof, differs to some extent already from the conventional d-c starting circuits. It is commonly known for all heretofore known blocking oscillator circuits, however, that a thyristor or an equivalent circuit replacing the thyristor is essential for the operation of the control circuit.

Considering the operation of a blocking oscillator, this means that, in the event of a short circuit, the number of collector current pulses per unit time must be reduced. For this purpose, a control and regulating circuit is provided. Simultaneously, a starting circuit must bring the blocking converter back to normal operation when the equipment is switched on, and after disturbances, for example, in the event of a short circuit. The starting circuit shown in the literature reference "Funkschau" on Page 42 thereof, differs to some extent already from the conventional d-c starting circuits. It is commonly known for all heretofore known blocking oscillator circuits, however, that a thyristor or an equivalent circuit replacing the thyristor is essential for the operation of the control circuit. It is accordingly an object of the invention to provide another starting circuit. It is a further object of the invention to provide a possible circuit for the control circuit which is particularly well suited for this purpose. It is yet another object of the invention to provide such a power supply which is assured of operation over the entire range of line voltages from 90 to 270 V a-c, while the secondary voltages and secondary load variations between no-load and short circuit are largely constant.

With the foregoing and other objects in view, there is provided, in accordance with the invention, a blocking oscillator-type

switching power supply for supplying power to electrical equipment wherein a primary winding of a transformer, in series with an emitter-collector path of a first bipolar transistor, is connected to a d-c voltage obtained by rectification of a line a-c voltage fed-in via two external supply terminals, a secondary winding of the transformer being connectible to the electrical equipment for supplying power thereto, the first bipolar transistor having a base controlled by the output of a control circuit acted upon, in turn, by the rectified a-c line voltage as actual value and by a set-point transmitter, and including a starting circuit for further control of the base of the first bipolar transistor, including a first diode in the starting circuit having an anode directly connected to one of the supply terminals supplied by the a-c line voltage and a cathode connected via a resistor to an input serving to supply power to the control circuit, the input being directly connected to a cathode of a second diode, the second diode having an anode connected to one terminal of another secondary winding of the transformer, the other secondary winding having another terminal connected to the emitter of the first bipolar transmitter.

switching power supply for supplying power to electrical equipment wherein a primary winding of a transformer, in series with an emitter-collector path of a first bipolar transistor, is connected to a d-c voltage obtained by rectification of a line a-c voltage fed-in via two external supply terminals, a secondary winding of the transformer being connectible to the electrical equipment for supplying power thereto, the first bipolar transistor having a base controlled by the output of a control circuit acted upon, in turn, by the rectified a-c line voltage as actual value and by a set-point transmitter, and including a starting circuit for further control of the base of the first bipolar transistor, including a first diode in the starting circuit having an anode directly connected to one of the supply terminals supplied by the a-c line voltage and a cathode connected via a resistor to an input serving to supply power to the control circuit, the input being directly connected to a cathode of a second diode, the second diode having an anode connected to one terminal of another secondary winding of the transformer, the other secondary winding having another terminal connected to the emitter of the first bipolar transmitter.  In accordance with another feature of the invention, there is provided a second bipolar transistor having the same conduction type as that of the first bipolar transistor and connected in the starting circuit with the base thereof connected to a cathode of a semiconductor diode, the semiconductor diode having an anode connected to the emitter of the first bipolar transistor, the second bipolar transistor having a collector connected via a resistor to a cathode of the first diode in the starting circuit, and having an emitter connected to the input serving to supply power to the control circuit and also connected to the cathode of the second diode which is connected to the other secondary winding of the transformer.

In accordance with another feature of the invention, there is provided a second bipolar transistor having the same conduction type as that of the first bipolar transistor and connected in the starting circuit with the base thereof connected to a cathode of a semiconductor diode, the semiconductor diode having an anode connected to the emitter of the first bipolar transistor, the second bipolar transistor having a collector connected via a resistor to a cathode of the first diode in the starting circuit, and having an emitter connected to the input serving to supply power to the control circuit and also connected to the cathode of the second diode which is connected to the other secondary winding of the transformer. In accordance with a further feature of the invention, the base of the second bipolar transistor is connected to a resistor and via the latter to one pole of a first capacitor, the anode of the first diode being connected to the other pole of the first capacitor.

In accordance with an added feature of the invention, the input serving to supply power to the control circuit is connected via a second capacitor to an output of a line rectifier, the output of the line rectifier being directly connected to the emitter of the first bipolar transistor.

In accordance with an additional feature of the invention, the other secondary winding is connected at one end to the emitter of the first bipolar transistor and to a pole of a third capacitor, the third capacitor having another pole connected, on the one hand, via a resistor, to the other end of the other secondary winding and, on the other hand, to a cathode of a third diode, the third diode having an anode connected via a potentiometer to an actual value input of the control circuit and, via a fourth capacitor, to the emitter of the first bipolar transistor.

In accordance with yet another feature of the invention, the control circuit has a control output connected via a fifth capacitor to the base of the first bipolar transistor for conducting to the latter control pulses generated in the control circuit.

In accordance with a concomitant feature of the invention, there is provided a sixth capacitor shunting the emitter-collector path of the first transistor.

Other features which are considered as characteristic for the invention are set forth in the appended claim.

Although the invention is illustrated and described herein as embodied in a blocking oscillator type switching power supply, it is nevertheless not intended to be limited to the details shown, since various modifications and structural changes may be made therein without departing from the spirit of the invention and within the scope and range of equivalents of the claims.

The construction and method of operation of the invention, however, together with additional objects and advantages thereof will be best understood from the following description of specific embodiments when read in connection with the accompanying drawings, in which:

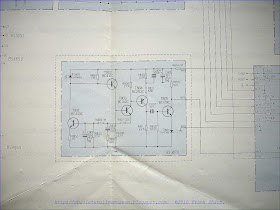

FIGS. 1 and 2 are circuit diagrams of the blocking oscillator type switching power supply according to the invention; and

FIG. 3 is a circuit diagram of the control unit RS of FIGS. 1 and 2.

Referring now to the drawing and, first, particularly to FIG. 1 thereof, there is shown a rectifier circuit G in the form of a bridge current, which is acted upon by a line input represented by two supply terminals 1' and 2'. Rectifier outputs 3' and 4' are shunted by an emitter-collector path of an NPN power transistor T1 i.e. t

he

series connection of the so-called first bipolar transistor referred to

hereinbefore with a primary winding I of a transformer Tr. Together

with the inductance of the transformer Tr, the capacitance C1 determines

the frequency and limits the opening voltages of the switch embodied by

the first transistor T1. A capacitance C2, provided between the base of

the first transistor T1 and the control output 7,8 of a control circuit

RS, separates the d-c potentials of the control or regulating circuit

RS and the switching transistor T1 and serves for addressing this

switching transistor T1 with pulses. A resistor R1 provided at the

control output 7,8 of the control circuit RS is the negative-feedback

resistor of both output stages of the control circuit RS. It determines

the maximally possible output pulse current of the control circuit RS. A

secondary winding II of the transformer Tr takes over the power supply

of the control circuit, in steady state operation, via the diode D1. To

this end, the cathode of this diode D1 is directly connected to a power

supply input 9 of the control circuit RS, while the anode thereof is

connected to one terminal of the secondary winding II. The other

terminal of the secondary winding II is connected to the emitter of the

power switching transistor T1.

he

series connection of the so-called first bipolar transistor referred to

hereinbefore with a primary winding I of a transformer Tr. Together

with the inductance of the transformer Tr, the capacitance C1 determines

the frequency and limits the opening voltages of the switch embodied by

the first transistor T1. A capacitance C2, provided between the base of

the first transistor T1 and the control output 7,8 of a control circuit

RS, separates the d-c potentials of the control or regulating circuit

RS and the switching transistor T1 and serves for addressing this

switching transistor T1 with pulses. A resistor R1 provided at the

control output 7,8 of the control circuit RS is the negative-feedback

resistor of both output stages of the control circuit RS. It determines

the maximally possible output pulse current of the control circuit RS. A

secondary winding II of the transformer Tr takes over the power supply

of the control circuit, in steady state operation, via the diode D1. To

this end, the cathode of this diode D1 is directly connected to a power

supply input 9 of the control circuit RS, while the anode thereof is

connected to one terminal of the secondary winding II. The other

terminal of the secondary winding II is connected to the emitter of the

power switching transistor T1.The cathode of the diode D1 and, therewith, the power supply terminal 9 of the control circuits RS are furthermore connected to one pole of a capacitor C3, the other pole of which is connected to the output 3' of the rectifier G. The capacitance of this capacitor C3 thereby smoothes the positive half-wave pulses and serves simultaneously as an energy storage device during the starting period. Another secondary windi

ng

III of the transformer Tr is connected by one of the leads thereof

likewise to the emitter of the first transistor T1, and by the other

lead thereof via a resistor R2, to one of the poles of a further

capacitor C4, the other pole of which is connected to the

first-mentioned lead of the other secondary winding III. This second

pole of the capacitor C4 is simultaneously connected to the output 3' of

the rectifier circuit G and, thereby, via the capacitor C3, to the

cathode of the diode D1 driven by the secondary winding II of the

transformer Tr as well as to the power supply input 9 of the control

circuit RS and, via a resistor R9, to the cathode of a second diode D4.

The second pole of the capacitor C4 is simultaneously connected directly

to the terminal 6 of the control circuit RS and, via a further

capacitor C 6, to the terminal 4 of the control circuit RS as well as,

additionally, via the resistor R6, to the other output 4' of the

rectifier circuit G. The other of the poles of the capacitor C4 acted

upon by the secondary winding II is connected via a further capacitor C5

to a node, which is connected on one side thereof, via a variable

resistor R4, to the terminals 1 and 3 of the control circuit RS, with

the intermediary of a fixed resistor R5 in the case of the terminal 1.

On the other side of the node, the latter and, therefore, the capacitor

C5 are connected to the anode of a third diode D2, the cathode of which

is connected on the one hand, to the resistor R2 mentioned hereinbefore

and leads to the secondary winding III of the transformer Tr and, on the

other hand, via a resistor R3 to the terminal 2 of the control circuit

RS.

ng

III of the transformer Tr is connected by one of the leads thereof

likewise to the emitter of the first transistor T1, and by the other

lead thereof via a resistor R2, to one of the poles of a further

capacitor C4, the other pole of which is connected to the

first-mentioned lead of the other secondary winding III. This second

pole of the capacitor C4 is simultaneously connected to the output 3' of

the rectifier circuit G and, thereby, via the capacitor C3, to the

cathode of the diode D1 driven by the secondary winding II of the

transformer Tr as well as to the power supply input 9 of the control

circuit RS and, via a resistor R9, to the cathode of a second diode D4.

The second pole of the capacitor C4 is simultaneously connected directly

to the terminal 6 of the control circuit RS and, via a further

capacitor C 6, to the terminal 4 of the control circuit RS as well as,

additionally, via the resistor R6, to the other output 4' of the

rectifier circuit G. The other of the poles of the capacitor C4 acted

upon by the secondary winding II is connected via a further capacitor C5

to a node, which is connected on one side thereof, via a variable

resistor R4, to the terminals 1 and 3 of the control circuit RS, with

the intermediary of a fixed resistor R5 in the case of the terminal 1.

On the other side of the node, the latter and, therefore, the capacitor

C5 are connected to the anode of a third diode D2, the cathode of which

is connected on the one hand, to the resistor R2 mentioned hereinbefore

and leads to the secondary winding III of the transformer Tr and, on the

other hand, via a resistor R3 to the terminal 2 of the control circuit

RS.The nine terminals of the control circuit RS have the following purposes or functions:

Terminal 1 supplies the internally generated reference voltage to ground i.e. the nominal or reference value required for the control or regulating process;

Terminal 2 serves as input for the oscillations provided by the secondary winding III, at the zero point of which, the pulse start of the driving pulse takes place;

Terminal 3 is the control input, at which the existing actual value is communicated to the control circuit RS, that actual value being generated by the rectified oscillations at the secondary winding III;

Terminal 4 is responsive to the occurrence of a maximum excursion i.e. when the largest current flows through the first transistor T1 ;

Terminal 5 is a protective input which responds if the rectified line voltage drops too sharply; Terminal 6 serves for the power supply of the control process and, indeed, as ground terminal;

Terminal 7 supplies the d-c component required for charging the coupling capacitor C2 leading to the base of the first transistor T1 ;

Terminal 8 supplies the control pulse required for the base of the first transistor T1 ; and

Terminal 9 serves as the first terminal of the power supply of the control circuit RS.

Further details of the control circuit RS are described hereinbelow.

The capacity C3 smoothes the positive half-wave pulses which are provided by the secondary winding II, and simultaneously serves as an energy storage device during the starting time. The secondary winding III generates the control voltage and is simultaneously used

as

feedback. The time delay stage R2 /C4 keeps harmonics and fast

interference spikes away from the control circuit RS. The resistor R3 is

provided as a voltage divider for the second terminal of the control

circuit RS. The diode D2 rectifies the control pulses delivered by the

secondary winding III. The capacity C5 smoothes the control voltage. A

reference voltage Uref, which is referred to ground i.e. the potential

of terminal 6 is present at the terminal 1 of the control circuit RS.

The resistors R4 and R5 form a voltage divider of the input-difference

control amplifier at the terminal 3. The desired secondary voltage can

be set manually via the variable resistor R4. A time-delay stage R6 /C6

forms a sawtooth rise which corresponds to the collector current rise of

the first bipolar transistor T1 via the primary winding I of the

transformer Tr. The sawtooth present at the terminal 4 of the control

circuit RS is limited there between the reference voltage 2 V and 4 V.

The voltage divider R7 /R8 (FIG. 2), brings to the terminal 5 of the

control circuit RS the enabling voltage for the drive pulse at the

output 8 of the control circuit RS.

as

feedback. The time delay stage R2 /C4 keeps harmonics and fast

interference spikes away from the control circuit RS. The resistor R3 is

provided as a voltage divider for the second terminal of the control

circuit RS. The diode D2 rectifies the control pulses delivered by the

secondary winding III. The capacity C5 smoothes the control voltage. A

reference voltage Uref, which is referred to ground i.e. the potential

of terminal 6 is present at the terminal 1 of the control circuit RS.

The resistors R4 and R5 form a voltage divider of the input-difference

control amplifier at the terminal 3. The desired secondary voltage can

be set manually via the variable resistor R4. A time-delay stage R6 /C6

forms a sawtooth rise which corresponds to the collector current rise of

the first bipolar transistor T1 via the primary winding I of the

transformer Tr. The sawtooth present at the terminal 4 of the control

circuit RS is limited there between the reference voltage 2 V and 4 V.

The voltage divider R7 /R8 (FIG. 2), brings to the terminal 5 of the

control circuit RS the enabling voltage for the drive pulse at the

output 8 of the control circuit RS.The diode D4, together with the resistor R9 in cooperation with the diode D1 and the secondary winding II, forms the starting circuit provided, in accordance with the invention. The operation thereof is as follows:

After the switching power supply is switched on, d-c voltages build up at the collector of the switching transistor T1 and at the input 4 of the control circuit RS, as a function in time of the predetermined time constants. The positive sinusoidal half-waves charge the capacitor C3 via the starting diode D4 and the starting resistor R9 in dependence upon the time constant R9.C3. Via the protective input terminal 5 and the resisto

r

R11 not previously mentioned and forming the connection between the

resistor R9 and the diode D1, on the one hand, and the terminal 5 of the

control circuit RS, on the other hand, the control circuit RS is biased

ready for switching-on, and the capacitor C2 is charged via the output

7. When a predetermined voltage value at the capacitor C3 or the power

supply input 9 of the control circuit RS, respectively, is reached, the

reference voltage i.e. the nominal value for the operation of the

control voltage RS, is abruptly formed, which supplies all stages of the

control circuit and appears at the output 1 thereof. Simultaneously,

the switching transistor T1 is switched into conduction via the output

8. The switching of the transistor T1 at the primary winding T of the

transformer Tr is transformed to the second secondary winding II, the

capacity C3 being thereby charged up again via the diode D1. If

sufficient energy is stored in the capacitor C3 and if the re-charge via

the diode D1 is sufficient so that the voltage at a supply input 9 does

not fall below the given minimum operating voltage, the switching power

supply then remains connected, so that the starting process is

completed. Otherwise, the starting process described is repeated several

times.

r

R11 not previously mentioned and forming the connection between the

resistor R9 and the diode D1, on the one hand, and the terminal 5 of the

control circuit RS, on the other hand, the control circuit RS is biased

ready for switching-on, and the capacitor C2 is charged via the output

7. When a predetermined voltage value at the capacitor C3 or the power

supply input 9 of the control circuit RS, respectively, is reached, the

reference voltage i.e. the nominal value for the operation of the

control voltage RS, is abruptly formed, which supplies all stages of the

control circuit and appears at the output 1 thereof. Simultaneously,

the switching transistor T1 is switched into conduction via the output

8. The switching of the transistor T1 at the primary winding T of the

transformer Tr is transformed to the second secondary winding II, the

capacity C3 being thereby charged up again via the diode D1. If

sufficient energy is stored in the capacitor C3 and if the re-charge via

the diode D1 is sufficient so that the voltage at a supply input 9 does

not fall below the given minimum operating voltage, the switching power

supply then remains connected, so that the starting process is

completed. Otherwise, the starting process described is repeated several

times.In FIG. 2, there is shown a further embodiment of the circuit for a blocking oscillator type switching power supply, according to the invention, as shown in FIG. 1. Essential for this circuit of FIG. 2 is the presence of a second bipolar transistor T2 of the type of the first bipolar transistor T1 (i.e. in the embodiments of the invention, an npn-transistor), which forms a further component of the starting circuit and is connected with the collector-emitter path thereof between the resistor R9 of the starting circuit and the current supply input 9 of the control circuit RS. The base of this second transistor T2 is connected to a node which leads, on the one hand, via a resistor R10 to one electrode of a capacitor C7, the other electrode of which is connected to the anode of the diode D4 of the starting circuit and, accordingl

y,

to the terminal 1' of the supply input of the switching power supply G.

On the other hand, the last-mentioned node and, therefore, the base of

the second transistor T2 are connected to the cathode of a Zener diode

D3, the anode of which is connected to the output 3' of the rectifier G

and, whereby, to one pole of the capacitor C3, the second pole of which

is connected to the power supply input 9 of the control circuit RS as

well as to the cathode of the diode D1 and to the emitter of the second

transistor T2. In other respects, the circuit according to FIG. 2

corresponds to the circuit according to FIG. 1 except for the resistor

R11 which is not necessary in the embodiment of FIG. 2, and the missing

connection between the resistor R9 and the cathode of the diode D1,

respectively, and the protective input 5 of the control circuit RS.

y,

to the terminal 1' of the supply input of the switching power supply G.

On the other hand, the last-mentioned node and, therefore, the base of

the second transistor T2 are connected to the cathode of a Zener diode

D3, the anode of which is connected to the output 3' of the rectifier G

and, whereby, to one pole of the capacitor C3, the second pole of which

is connected to the power supply input 9 of the control circuit RS as

well as to the cathode of the diode D1 and to the emitter of the second

transistor T2. In other respects, the circuit according to FIG. 2

corresponds to the circuit according to FIG. 1 except for the resistor

R11 which is not necessary in the embodiment of FIG. 2, and the missing

connection between the resistor R9 and the cathode of the diode D1,

respectively, and the protective input 5 of the control circuit RS.Regarding the operation of the starting circuit according to FIG. 2,

it can be stated that the positive sinusoidal half-wave of the line

voltage, delayed by the time delay stage C7, R10 drives the base of the

transistor T2 in the starting circuit. The amplitude is limited by the

diode D3 which is provided for overvoltage protection of the control

circuit RS and which is preferably incorporated as a Zener diode. The

second transistor T2 is switched into conduction. The capacity C3 is

charged, via the serially connected diode D4 and the resistor R9 and the

collector-emitter path of the transistor T2, as soon as the voltage

between the terminal 9 and the terminal 6 of the control circuit RS i.e.

the voltage U9, meets the condition U9 <[UDs -UBE (T2)].

it can be stated that the positive sinusoidal half-wave of the line

voltage, delayed by the time delay stage C7, R10 drives the base of the

transistor T2 in the starting circuit. The amplitude is limited by the

diode D3 which is provided for overvoltage protection of the control

circuit RS and which is preferably incorporated as a Zener diode. The

second transistor T2 is switched into conduction. The capacity C3 is

charged, via the serially connected diode D4 and the resistor R9 and the

collector-emitter path of the transistor T2, as soon as the voltage

between the terminal 9 and the terminal 6 of the control circuit RS i.e.

the voltage U9, meets the condition U9 <[UDs -UBE (T2)].Because of the time constant R9.C3, several positive half-waves are necessary in order to increase the voltage U9 at the supply terminal 9 of the control circuit RS to such an extent that the control circuit RS is energized. During the negative sine half-wave, a partial energy chargeback takes place from the capacitor C3 via the emitter-base path of the transistor T2 of the starting circuit and via the resistor R10 and the capacitor C7, respectively, into the supply network. At approximately 2/3 of the voltage U9, which is limited by the diode D3, the control circuit RS is switched on. At the terminal 1 thereof, the reference voltage Uref then appears. In addition, the voltage divider R5 /R4 becomes effective. At the terminal 3, the control amplifier receives the voltage forming the actual value, while the first bipolar transistor T1 of the blocking-oscillator type switching power supply is addressed pulsewise via the terminal 8.

Because the capacitor C6 is charged via the resistor R6, a higher voltage than Uref is present at the terminal 4 if the control circuit RS is activated. The control voltage then discharges the capacitor C6 via the terminal 4 to half the value of the reference voltage Uref, and immediately cuts off the addressing input 8 of the control circuit RS. The first driving pulse of the switching transistor T1 is thereby limited to a minimum of time. The power for switching-on the control circuit RS and for driving the transistor T1 is supplied by the capacitor C3. The voltage U9 at the capacitor C3 then drops. If the voltage U9 drops below the switching-off voltage value of the control circuit RS, the latter is then inactivated. The next positive sine half-wave would initiate the starting process again.

By switching the transistor T1, a voltage is transformed in the secondary winding II of the transformer Tr. The positive component is rectified by the diode D1, recharing of the capacitor C3 being thereby provided. The voltage U9 at the output 9 does not, therefore, drop below the minimum value required for the operation of the control circuit RS, so that the control circuit RS remains activated. The power supply continues to operate in the rhythm of the existing conditions. In operation, the voltage U9 at the supply terminal 9 of the control circuit RS has a value which meets the condition U9 >[UDs -UBE (T2)], so that the transistor T2 of the starting circuit remains cut off.

For the internal layout of the control circuit RS, the construction shown, in particular, from FIG. 3 is advisable. This construction is realized, for example, in the commercially available type TDA 4600 (Siemens AG).

The block diagram of the control circuit according to FIG. 3

shows

the power supply thereof via the terminal 9, the output stage being

supplied directly whereas all other stages are supplied via Uref. In the

starting circuit, the individual subassemblies are supplied with power

sequentially. The d-c output voltage potential of the base current gain

i.e. the voltage for the terminal 8 of the control circuit RS, and the

charging of the capacitor C2 via the terminal 7 are formed even before

the reference voltage Uref appears. Variations of the supply voltage U9

at terminal 9 and the power fluctuations at the terminal 8/terminal 7

and at the terminal 1 of the control circuit RS are leveled or smoothed

out by the voltage control. The temperature sensitivity of the control

circuit RS and, in particular, the uneven heating of the output and

input stages and input stages on the semiconductor chip containing the

control circuit in monolithically integrated form are intercepted by the

temperature compensation provided. The output values are constant in a

specific temperature range. The message for blocking the output stage,

if the supply voltage at the terminal 9 is too low, is given also by

this subassembly to a provided control logic.

shows

the power supply thereof via the terminal 9, the output stage being

supplied directly whereas all other stages are supplied via Uref. In the

starting circuit, the individual subassemblies are supplied with power

sequentially. The d-c output voltage potential of the base current gain

i.e. the voltage for the terminal 8 of the control circuit RS, and the

charging of the capacitor C2 via the terminal 7 are formed even before

the reference voltage Uref appears. Variations of the supply voltage U9

at terminal 9 and the power fluctuations at the terminal 8/terminal 7

and at the terminal 1 of the control circuit RS are leveled or smoothed

out by the voltage control. The temperature sensitivity of the control

circuit RS and, in particular, the uneven heating of the output and

input stages and input stages on the semiconductor chip containing the

control circuit in monolithically integrated form are intercepted by the

temperature compensation provided. The output values are constant in a

specific temperature range. The message for blocking the output stage,

if the supply voltage at the terminal 9 is too low, is given also by

this subassembly to a provided control logic.The outer voltage divider of the terminal 1 via the r

esistors

R5 and R4 to the control tap U forms, via terminal 3, the variable side

of the bridge for the control amplifier formed as a differential

amplifier. The fixed bridge side is formed by the reference voltage Uref

via an internal voltage divider. Similarly formed are circuit portions

serving for the detection of an overload short circuit and circuit

portions serving for the "standby" no-load detection, which can be

operated likewise via terminal 3.

esistors

R5 and R4 to the control tap U forms, via terminal 3, the variable side

of the bridge for the control amplifier formed as a differential

amplifier. The fixed bridge side is formed by the reference voltage Uref

via an internal voltage divider. Similarly formed are circuit portions

serving for the detection of an overload short circuit and circuit

portions serving for the "standby" no-load detection, which can be

operated likewise via terminal 3.Within a provided trigger circuit, the driving pulse length is determined as a function of the sawtooth rise at the terminal 4, and is transmitted to the control logic. In the control logic, the commands of the trigger circuit are processed. Through the zero-crossing identification at input 2 in the control circuit RS, the control logic is enabled to start the control input only at the zero point of the frequency oscillation. If the voltages at the terminal 5 and at the terminal 9 are too low, the control logic blocks the output amplifier at the terminal 8. The output amplifier at the terminal 7 which is responsible for the base charge in the capacitor C2, is not touched thereby.

The base current gain for the transistor T1 i.e. for the first transistor in accordance with the definition of the invention, is formed by two amplifiers which mutually operate on the capacitor C2. The roof inclination of the base driving current for the transistor T1 is impressed by the collector current simulation at the terminal 4 to the amplifier at the terminal 8. The control pulse for the transistor T1 at the terminal 8 is always built up to the potential present at the terminal 7. The amplifier working into the terminal 7 ensures that each new switching pulse at the terminal 8 finds the required base level at terminal 7.

Supplementing the comments regarding FIG. 1, it should also be mentioned that the cathode of the diode D1 connected by the anode thereof to the one end of the secondary winding II of the transformer Tr is connected via a resistor R11 to the protective input 5 of the control circuit RS whereas, in the circuit according to FIG. 2, the protective input 5 of the control circuit RS is supplied via a voltage divider R8, R7 directly from the output 3', 4' of the rectifier G delivering the rectified line a-c voltage, and which obtains the voltage required for executing its function. It is evident that the first possible manner of driving the protective input 5 can be used also in the circuit according to FIG. 2, and the second possibility also in a circuit in accordance with FIG. 1.

The control circuit RS which is shown in FIG. 3 and is realized in detail by the building block TDA 4600 and which is particularly well suited in conjunction with the blocking oscillator type switching power supply according to the invention has 9 terminals 1-9, which have the following characteristics, as has been explained in essence hereinabove:

Terminal 1 delivers a reference voltage Uref which serves as the constant-current source of a voltage divider R5.R4 which supplies the required d-c voltages for the differential amplifiers provided for the functions control, overload detection, short-circuit detection and "standby"-no load detection. The dividing point of the voltage divider R5 -R4 is connected to the terminal 3 of the control circuit RS. The terminal 3 provided as the control input of RS is controlled in the manner described hereinabove as input for the actual value of the voltage to be controlled or regulated by the secondary winding III of the transformer Tr. With this input, the lengths of the control pulses for the switching transistor T1 are determined.

Via the input provided by the terminal 2 of the control circuit RS, the zero-point identification in the control circuit is addressed for detecting the zero-point o

f

the oscillations respectively applied to the terminal 2. If this

oscillation changes over to the positive part, then the addressing pulse

controlling the switching transistor T1 via the terminal 8 is released

in the control logic provided in the control circuit.

f

the oscillations respectively applied to the terminal 2. If this

oscillation changes over to the positive part, then the addressing pulse

controlling the switching transistor T1 via the terminal 8 is released

in the control logic provided in the control circuit.A sawtooth-shaped voltage, the rise of which corresponds to the collector current of the switching transistor T1, is present at the terminal 4 and is minimally and maximally limited by two reference voltages. The sawtooth voltage serves, on the one hand as a comparator for the pulse length while, on the other hand, the slope or rise thereof is used to obtain in the base current amplification for the switching transistor T1, via the terminal 8, a base drive of this switching transistor T1 which is proportional to the collector current.

The terminal 7 of the control circuit RS as explained hereinbefore, determines the voltage potential for the addressing pulses of the transistor T2. The base of the switching transistor T1 is pulse-controlled via the terminal 8, as described hereinbefore. Terminal 9 is connected as the power supply input of the control circuit RS. If a voltage level falls below a given value, the terminal 8 is blocked. If a given positive value of the voltage level is exceeded, the control circuit is activated. The terminal 5 releases the terminal 8 only if a given voltage potential is present.

Forei

gn References:

gn References:DE2417628A1 1975-10-23 363/37

DE2638225A1 1978-03-02 363/49

Other References:

Grundig Tech. Info. (Germany), vol. 28, No. 4, (1981).

IBM Technical Disclosure Bulletin, vol. 19, No. 3, pp. 978, 979, Aug. 1976.

German Periodical, "Funkschau", (1975), No. 5, pp. 40 to 44.

Inventors:

Peruth, Gunther (Munich, DE) Siemens Aktiengesellschaft (Berlin and Munich, DE)- FRAME DEFLECTION WITH TDA1170 This p.c.b. generates a sawtooth

voltage at frame frequency which is used for driving the vertical deflection yoke. It supplies a

similar voltage to the "pincushion" section of the synchro. separator p.c.b. to obtain the E/W pincushion correction. It supplies a frame frequency pulse which is used for the luminance, chrominance and video amplifier p.c.b. blankings. It receives the vertical synchro.

from the synchro. separator p.c.b. and receives from the chassis a voltage proportional to the beam current.

- BS399.0 LUMINANCE AND CHROMINANCE + RGB AMPLIFIER This p.c.b. processes the

- BS399.0 LUMINANCE AND CHROMINANCE + RGB AMPLIFIER This p.c.b. processes thecomplete composite video signal coming from the IF p.c.b. andsupplies the R-G-B signals to

the picture tube.

- BS398 TUNER

+ AFC + IF Conversion of the RF signal into an IF signal

+ AFC + IF Conversion of the RF signal into an IF signal(video carrier:39.5 M z; audio carrier:33.5 MHZ).

Detection of the IF signal into low frequency video and audio signals.

TDA2541 IF AMPLIFIER WITH DEMODULATOR AND AFC

DESCRIPTION

The TDA2540 and 2541 are IF amplifier and A.M.

demodulator circuits for colour and black and white

television receivers using PNP or NPN tuners. They

are intended for reception of negative or positive

modulation CCIR standard.

They incorporate the following functions : .Gain controlled amplifier .Synchronous demodulator .White spot inverter .Video preamplifier with noise protection .Switchable AFC .AGC with noise gating .Tuner AGC output (NPN tuner for 2540)-(PNP

tuner for 2541) .VCR switch for video output inhibition (VCR

play back).

- BS389 REMOTE CONTROL

DECODER WITH ITT SAA1251 This p.c.b. enables remote

DECODER WITH ITT SAA1251 This p.c.b. enables remotecontrol of the following functions: selection of 16 programmes; "+" or "-" adjustment; brightness

saturation adjustment; silencing; TV receiver switching.

- BS388.2 TUNING MEMORY AND SEARC

H Remote control p.c.b. The display indicates the programme selected. Furthermore,this p.c.b. includes all pushbuttons for clock

H Remote control p.c.b. The display indicates the programme selected. Furthermore,this p.c.b. includes all pushbuttons for clockadjustment.No adjustments needed. Automatic searching of a TV station through a start command. Manual searching of a TV station through two commands (increment and decrement).

Inclusion-exclusion of the AFC circuit with LED display. Band indication displayed on

three LEDs. Tuning level indication with five LEDs. Memorization of 16 selected

programmes manually or remote control.

Features The MOTOROLA Memotronic with MC14429P-A, MC14426P, UAA1008A-DP,

- BS392.2 ST-BY SUPPLY AND OPTOCOUPLER START STOP FEATURE. The p.c.b. includes circuits relevant to: mains filter, degaussing, remote control

supply, start remote control.

supply, start remote control.No adjustments needed. It includes circuits for clock supply and for switch-ON programming. It has the phototransistor + infrared emitter joined in a plastic tube to obtain power on off separate from mains

- BS401 This p.c.b. receives the audio signal (not adjusted in volume) coming from p.c.b. BS 398, it adjusts it in amplitude and tone, it amplifies it and sends it to drive the two receiver’s loudspeakers (tweeter and woofer).

TDA1170 vertical deflection FRAME DEFLECTION INTEGRATED CIRCUITGENERAL DESCRIPTION f The TDA1170 and TDA1270 are monolithic integrated

circuits designed for use in TV vertical deflection systems. They are manufactured using

the Fairchild Planar* process.

Both devices are supplied in the 12-pin plastic power package with the heat sink fins bent

for insertion into the printed circuit board.

The TDA1170 is designed primarily for large and small screen black and white TV

receivers and industrial TV monitors. The TDA1270 is designed primarily for driving

complementary vertical deflection output stages in color TV receivers and industrial

monitors.

APPLICATION INFORMATION (TDA1170)

The vertical oscillator is directly synchronized by the sync pulses (positive or negative); therefore its free

running frequency must be lower than the sync frequency. The use of current feedback causes the yoke

current to be independent of yoke resistance variations due to thermal effects, Therefore no thermistor is

required in series with the yoke. The flyback generator applies a voltage, about twice the supply voltage, to

the yoke. This produces a short flyback time together with a high useful power to dissipated power

ratio.

BU208(A)

Silic on NPN

on NPNnpn transistors,pnp transistors,transistors

Category: NPN Transistor, Transistor

MHz: <1 MHz

Amps: 5A

Volts: 1500V

HIGH VOLTAGE CAPABILITY

JEDEC TO-3 METAL CASE.

DESCRIPTION

The BU208A, BU508A and BU508AFI are

manufactured using Multiepitaxial Mesa

technology for cost-effective high performance

and use a Hollow Emitter structure to enhance

switching speeds.

APPLICATIONS:

* HORIZONTAL DEFLECTION FOR COLOUR TV With 110° or even 90° degree of deflection angle.

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

VCES Collector-Emit ter Voltage (VBE = 0) 1500 V

VCEO Collector-Emit ter Voltage (IB = 0) 700 V

VEBO Emitter-Base Voltage (IC = 0) 10 V

IC Collector Current 8 A

ICM Collector Peak Current (tp < 5 ms) 15 A

TO - 3 TO - 218 ISOWATT218

Ptot Total Dissipation at Tc = 25 oC 150 125 50 W

Tstg Storage Temperature -65 to 175 -65 to 150 -65 to 150 oC

Tj Max. Operating Junction Temperature 175 150 150 °C

SELECO (ZANUSSI) 20ST211 BRAVO 20" CHASSIS BS465.2 Television receiver with an automatic station finding arrangement:

The present invention relates to a television tuning device, comprising a circuit for continuously scanning at least one band of receivable frequencies, and having control means for starting and stopping the said scanning procedure and a terminal for applying a switch signal for switching from a first band-scanning speed to a second band-scanning speed slower than the first.

The name usually applied to a unit consisting of circuits of this type for selecting and memorising a given number of preferred channels is "station memory".

Many types of station memories are already being sold on the market which can be divided into two main groups: those with automatic and those with manual television channel searching.

The automatic types are fitted with electronic searching circuits which locate television channels automatically when started by the user. This is done by scanning a given band (VHF or UHF, for example) and stopping on the located channel. Data relative to the located channel can then be memorised by the user in a memory circuit and the same channel recalled whenever required by simply pressing a button which recalls the said data from the memory and supplies it to the channel selection circuit.

This type of circuit is also fitted with components which sense, during search, if a television channel has been tuned into and disable automatic searching to prevent television band scanning from continuing. Most of these circuits are fitted with a phase detector which senses the coincidence between the sync signals received and those regenerated in the receiver (in particular, the flyback signal).

Manual station memories, on the other hand, are fitted with controls which, when activated by the user, start a device for scanning a given television band. These controls also stop the said device when required by the user. When the user sees the required channel appear on the screen, the device is stopped to disable search and enable the channel to be memorised in the appropriate circuit.

In these cases, the simplest way of starting and stopping the search is to fit the circuits with a button which, when pressed, supplies a search-start signal and, when released, stops the searching operation. For best tuning, two buttons are usually provided for band scanning in both directions.

Both the types discussed up to now present drawbacks. In the case of automatic station memories, for example, tuning quality depends on correct operation of all the search-stop circuits and the automatic tuning circuit (AFC=automatic frequency control). Even in cases where these circuits are operating correctly, tuning could still be impaired by noise or amplitude distortion on the received signal.

Tuning

quality on manual station memories, on the other hand, depends on the

tuning ability of the user. Television receivers can be manipulated by

anybody not all of whom are gifted with this ability. A further drawback

of manual station memories is that the user has very little time in

which to decide whether the received channel is the right one and to

estimate tuning quality. If the whole television band is to be scanned

in a reasonable length of time (let us say, the UHF band in one minute)

band-scanning speed needs to be fairly high. Consequently, if the user

is not quick enough in sending out the search-stop control signal, it is

more than likely that the control will be sent when the required

television channel has been overshot. If, by chance, there are two

channels close to one another, the searching device may even stop on the

second of the two, thus confusing the user who will not know which of

the two channels he has tuned into.

Tuning

quality on manual station memories, on the other hand, depends on the

tuning ability of the user. Television receivers can be manipulated by

anybody not all of whom are gifted with this ability. A further drawback

of manual station memories is that the user has very little time in

which to decide whether the received channel is the right one and to

estimate tuning quality. If the whole television band is to be scanned

in a reasonable length of time (let us say, the UHF band in one minute)

band-scanning speed needs to be fairly high. Consequently, if the user

is not quick enough in sending out the search-stop control signal, it is

more than likely that the control will be sent when the required

television channel has been overshot. If, by chance, there are two

channels close to one another, the searching device may even stop on the

second of the two, thus confusing the user who will not know which of

the two channels he has tuned into. The aim of the present invention is to provide a tuning device to overcome these problems.

With this aim in view, the present invention provides a television tuning device comprising a circuit for continuously scanning at least one band of receivable frequencies, manual control means for starting and stopping the said scanning procedure, a terminal for applying a switch signal for switching from a first band-scanning speed to a second band-scanning speed lower than the first, and detection means for detecting the presence of a television channel by comparing the received sync signals with local signals generated in the television receiver, and applying a switch signal to the said terminal for switching from the said first scanning speed to the said second scanning speed in the presence of the said switch signal, so that the band scanning continues at said lower speed until the manual control means produce the stopping scanning procedure.

MOTOROLA TUNING MEMORY / MEMOTRONIC SYSTEM TECHNOLOGY.In a radio or television receiver containing an automatic station finder with a digital counter, a clock generator, and a digital-to-analog converter forming the tuning voltage for the varactors, a recall memory consisting of two series-connected parallel memories is connected in parallel with the digital counter. At a stop signal from the

automatic station finder the first parallel memory records the instantaneous count of the digital counter; at an automatic-station-finding start signal the second parallel memory, to which the parallel input of the digital counter is connected, records the contents of the first parallel memory.

1. A receiver having automatic station finding capability, comprising:

means for tuning said receiver in response to an applied voltage;

a controllable pulse generator;

means for starting said pulse generator;

circulating counter means having parallel inputs and outputs, a stepping input and a set input, said stepping input connected to and responsive to pulses from said pulse generator for providing a variable digital output;

digital-to-analog convert

ing means for converting the variable digital output from said counter means to a variable analog voltage, said voltage being applied to said tuning means, so that the receiver is tuned to a frequency corresponding to the analog voltage;

means for sensing a received signal and for providing a stop signal to the pulse generator in response thereto, whereby said generator stops providing pulses and the analog voltage remains constant keeping the receiver tuned to the received signal;

memory means having parallel inputs connected to the parallel outputs of said counter means and parallel outputs connected to the parallel inputs of said counter means;

means associated with said memory means for causing the memory means to store a particular digital output from said counter means; and

means associated with the set input of said counter means for selectively causing the digital signal at the counter input to be transferred to the counter output.

2. A receiver as described in claim 1, wherein the memory means comprises: two series connected parallel memories each having a transfer input, a first of said parallel memories having parallel inputs c

onnected to the parallel outputs of the counter means and having the transfer input connected to the stop signal means, a second of said parallel memories having parallel outputs connected to the parallel inputs of the counter means and having the transfer input connected to the means for starting said pulse generator.

onnected to the parallel outputs of the counter means and having the transfer input connected to the stop signal means, a second of said parallel memories having parallel outputs connected to the parallel inputs of the counter means and having the transfer input connected to the means for starting said pulse generator.3. A receiver as described in claim 2, wherein each of said parallel memories comprises a plurality of semiconductor voltage flip-flops.

4. A receiver as described in claim 2, wherein the two series connected parallel memories are incorporated in an integrated circuit module with the counter means.

5. A receiver as described in claim 2, wherein the transfer input of the first parallel memory is also connected to the means associated with the set input of the counter means.

6. A receiver as described in claim 1, additionally comprising:

an additional memory means having parallel inputs and outputs;

means for connecting the inputs of said additional memory means to the counter means output and the outputs of said additional memory means to the counter inputs;

means for causing said additional memory means to store a digital output; and

means for transferring the stored digital output to the counter means input through the connecting means.

7. A receiver as described in claim 6, additionally comprising gate means disposed at the outputs of the memory means and the additional memory means for selectively connecting either the additional memory means or the memory means to the input of the counter.

8. A receiver as described in claim 6, wherein the additional memory means comprises a plurality of memories and the connecting means comprises a plurality of station switches corresponding in number to the number of additional memories.

9. A receiver as described in claim 1, wherein each memory means comprises a number of flip-flops corresponding to the number of digits to be stored.

Description:

The p

resent invention relates to a radio or television receiver with an automatic station finding arrangement which contains a pulse generator, a circulating counter formed from semiconductor counting flip-flops and having parallel inputs, a digital-to-analog converter converting the count of the counter to a tuning voltage, and a start-stop circuit acting on the flow of counting pulses and controlled over a start and at least one stop line, and with a parallel memory connected between the parallel outputs and parallel inputs of the counter.

Such a radio receiver is known from, e.g., the journal "Funkschau 1971", pp. 535 to 538 and 587 to 589. With the aid of the free-running pulse generator, the up-counter, and the digital-to-analog converter, the automatic station finding arrangement generates a sawtoothlike tuning voltage for the varactors contained as frequency-setting tuning elements in the resonant circuits of the receiver's radio-frequency portion. If a transmitter is received which meets the receiving criteria set in the receiver, the pulse generator is stopped so that the tuning voltage now remains constant until the operator continues the automatic station finding operation by actuating a start switch.

It is frequently desirable to tune in once again the station at which the start switch for automatic station finding was actuated last - either for comparison or because of the more interestin g program. To do this in the case of a receiver with provision for unidirectional automatic station search, the entire search range must be scanned once or several times by repeatedly actuating the start switch, depending on whether the desired station is detected immediately or not.

g program. To do this in the case of a receiver with provision for unidirectional automatic station search, the entire search range must be scanned once or several times by repeatedly actuating the start switch, depending on whether the desired station is detected immediately or not.

It is the object of the invention to provide measures for a receiver of the kind referred to by way of introduction which permit the transmitter received before the actuation of the start switch to be found again with a high degree of safety by simple manipulation.

The invention is characterized in that the parallel memory consists of two series-connected parallel memories having one transfer input each, that the transfer input of the (first) parallel memory, whose parallel inputs are connected to the parallel outputs of the counter, are connected directly or indirectly to the stop line, that the transfer input of the (second) parallel memory, whose parallel outputs are connected to the parallel inputs of the counter, is connected directly or indirectly to the start line, that the counter has a set input for through-connecting the parallel inputs of the counter to the flip-flops of the counter, and that a recall switch is connected to the set input of the counter.

Particularly advantageously, the memory locations of the two series-connected parallel memories are storage flip-flops using semiconductor technology. In that case it is possible to arrange the counter and the parallel memories on a common chip of an integrated-circuit module. Such a module has only two terminals more than a module formed by the counter only.

The measures chara cterized by the invention thus require, aside from an additional recall switch, no additional space and involve nearly no additional expense. To recall the station previously tuned in it is only necessary to depress a button, for example, whereby the receiver is safely tuned to the station's carrier wave even if at the instant of the depression the local received field strength is temporarily too low for sufficient reception.

cterized by the invention thus require, aside from an additional recall switch, no additional space and involve nearly no additional expense. To recall the station previously tuned in it is only necessary to depress a button, for example, whereby the receiver is safely tuned to the station's carrier wave even if at the instant of the depression the local received field strength is temporarily too low for sufficient reception.

The invention will now be described in more detail with reference to the accompanying drawing, showing, by way of example, two embodiments of the invention, and wherein:

FIG. 1 is a block diagram showing the radio- and intermediate-frequency portions of a receiver with an automatic station finding arrangement and a recall arrangement;

FIG. 2 shows diagrams a to g explaining the operation of the recall storage, and

FIG. 3 shows a receiver similar to the one of FIG. 1 in which the automatic station finding counter and the recall memories are arranged together on the chip of an integrated-circuit module.

The receivers shown in the block diagrams of FIGS. 1 and 3 have a radio-frequency-receiving section 1, an intermediate-frequency amplif ier 2, and a demodulator section 3, to whose output 4 are connected the arrangements processing the modulation frequency. The tunable resonant circuits of the radio-frequency section contain varactors as tuning elements. Connected to the radio-frequency section is an automatic station finding arrangement in which a digital-to-analog converter 5 generates from the count of a digital counter 7, which receives signals at a stepping input T and advances at the rate of a pulse generator 6, a nearly sawtooth-shaped tuning voltage for the varactors. With a sufficient received field strength at the antenna 8 of the receiver a signal is formed in the demodulator section 3 which signal can be used as stop signal 9 to change the state of a start-stop circuit 10 which may be a flip flop. In the "stop" state the start-stop circuit interrupts the pulse generation or the pulse flow in the pulse generator so that the receiver remains tuned to the station being received. By operating a start-button switch 11 a start signal 12 is generated in the receiver which signal places the start-stop circuit in the "automatic station finding" state and thus continues the automatic station finding operation until next station meeting the receiver's receiving requirements is received.