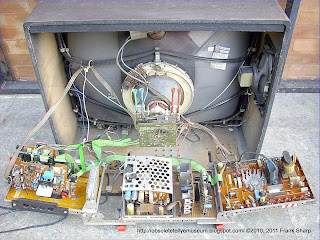

This Line of television set was called the STUDIO LINE and was introducing the CHASSIS 714A with the already introduced 30AX CRT TUBE one year earlyer, this was the last OPEN BOOK chassis type technology with his unique modularity (see pictures) and with some add on capability never officially marketed because TELEFUNKEN after 1981 ceased to produce tellyes in this way.

The 714A Is introducing the use of the TDA3560 as PAL MonoChip for chroma-luminance section, to integrate in one unit Video and RGB stages.

The successor chassis type was the CHASSIS 415/615 and related types.

LAST TELEFUNKEN CHASSIS DEVELOPED IN THIS WAY FOREVER !!!!!!!!

TELEFUNKEN CHASSIS 714A (AT349354097) Switching power supply, especially for a T.V. receiving apparatus:

1. Switch mode power supply means, especially for a television receiver, having a working winding (5), a switching transistor (6), a back-coupling winding (7) and a control switch (11) on the primary side of a divided transformer (1), and also having rectifiers (15, 16, 20) for the production of the drive voltages (U1, U2, U3) on the secondary side of the transformer (1), characterized by the following features : (a) Connected to a winding (19) there is a thyristor (24) which is poled in the permitted direction for the voltage at the winding (19) arising during the current conducting phase of the switching transistor (6). (b) One of the drive voltages (U2) is applied to the control electrode of the thyristor (24) with such magnitude that the thyristor (24) remains blocked in the normal working state and fires on the occurrence of an inadmissible rise of the drive voltage (U3).

TELEFUNKEN PALCOLOR CHASSIS 714A Schaltnetzteil AT349354097

(AT 349354097), IN GERMAN:

1. Schaltnetzteil, insbesondere f·ur einen Fernsehempf·anger, mit einer Arbeitswicklung (5), einem Schalttransistor (6), einer R·uckkopplungswicklung (7) und einer Regelschaltung (ii) auf der Prim·arseite sowie mit Gleichrichtern (15,16, 20) zur Erzeugung von Betriebsspannungen (U11U2#U3) auf der Sekund·arseite eines Trenntransformators (1) gekenn zeichnet durch folgende Merkmale: a) An eine Wicklung (19) ist ein Thyristor (24) angeschlos sen, der f·ur die w·ahrend der siromf·uhrenden Phase der Schalttransistoren (6) an der Wicklung (19) auftreten de Spannung in Durchlassrichtung gepolt ist. b) An die Steuerelektrode des Thyristors (24) ist eine der Betriebsspannungen (U2) in solcher H·ohe angelegt, dass der Thyristor (24) im Normalbetrieb gesperrt bleibt und bei einem unzul·assigen Anstieg der Betriebs spannung (U3) z·undet.

2. Netzteil nach Anspruch 1, dadurch gekennzeichnet, dass die Betriebsspannung (U3) ·uber einen Spannungsteiler (25,26) an die Steuerelektrode des Thyristors (24) angelegt ist.

3. Netzteil nach Anspruch 1, dadurch gekennzeichnet, dass die Wicklung (19) eine Sekund·arwicklung des Trenntransforma tors (1) ist.

Description:

Schaltnetzteil, insbesondere f·ur einen Fernsehempf·anger

Bei Ger·aten der Nachrichtentechnik wie z.B. einem Fernsehempf·anger ist es bekannt, die f·ur die einzelnen Stufen notwendigen Betriebsspannungen mit einem Schaltnetzteil aus der Netzspannung zu erzeugen (Funkschau 1975, Heft 5, Seite 40-43). Ein Schaltnetzteil erm·oglicht die f·ur den Anschluss ·ausserer Ger·ate und f·ur die Massnahmen zur Schutzisolierung vorteilhafte galvanische Trennung der Empf·angerschaltung vom Netz. Da ein Schaltnetzteil mit einer gegen·uber der Netzfrequenz hohen Frequenz von ca. 30 kHz arbeitet, kann der zur galvanischen Trennung dienende Trenntransformator gegen·uber einem Netztrafo f·ur 50 Hz wesentlich kleiner und leichter ausgebildet sein. Durch mehrere Wicklungen oder Wicklungsabgriffe und angeschlossene Gleichrichter k·onnen auf der Sekund·arseite des Trenntransformators Betriebs~ spannungen unterschiedlicher Gr·osse und Polarit·at erzeugt werden.

Ein solches Schaltnetzteil enth·alt eine Regelschaltung zur Stabilisierung der Amplitude der auf der Sekund·arseite erzeugten Betriebsspannungen. In dieser Regelschaltung wird eine durch Gleichrichtung der Impulsspannung am Trafo gewonnene Stellgr·osse erzeugt und mit einer Bezugsspannung verglichen. In Abh·angigkeit von der Abweichung wird der Schaltzeitpunkt des auf der Prim·arseite vorgesehenen elektronischen Schalters so gesteuert, dass die Amplitude der erzeugten Betriebsspannungen konstant bleibt.

Bei einem solchen Schaltnetzteil kann die genannte Regelschaltung z.B. durch ein fehlerhaftes Bauteil ausfallen. Die Regelung der Amplitude der erzeugten Betriebsspannungen ist dann unkontrolliert. Die Betriebsspannungen k·onnen dann auf den doppelten oder dreifachen Wert ansteigen. Dadurch besteht die Gefahr, dass das Schaltnetzteil oder die an die Betriebsspannungen angeschlossenen Verbraucher wie z.B. der Heizfaden der Bildr·ohre oder der Zeilenendstufentransistor zerst·ort werden. Der Anstieg der Betriebsspannungen kann dar·uberhinaus einen Anstieg der im Fernsehempf·anger erzeugten Hochspannung und dadurch eine R·ontgenstrahlung ausl·osen.

Es ist auch ein Schaltnetzteil bekannt (DE-OS 27 27 332), bei dem zum Schutz gegen einen zu starken Anstieg der erzeugten Betriebsspannungen aus der Impulsspannung an der Prim·arseite des Trafos eine Stellgr·osse gewonnen wird, die beim ·Uberschreiten eines Schwellwertes den R·uckkopplungsweg unwirksam steuert. Durch die Unterbrechung des R·uckkopplungsweges kann das Schaltnetzteil nicht mehr schwingen, so dass in erw·unschter Weise auch keine Betriebsspannungen mehr erzeugt werden. Diese Schaltung erfordert jedoch eine Vielzahl von Bauteilen und ist daher relativ teuer.

Der Erfindung liegt die Aufgabe zugrunde, eine sicher wirkende Schutzschaltung mit verringertem Schaltungsaufwand gegen die oben

beschriebenen Gefahren zu schaffen.

die oben

beschriebenen Gefahren zu schaffen.

Diese Aufgabe wird durch die im Anspruch 1 beschriebene Erfindung gel·ost. Vorteilhafte Weiterbildungen der Erfindung sind in den Unteranspr·uchen beschrieben.

Die Erfindung beruht auf folgender ·Uberlegung: Der Schalttransistor auf der Prim·arseite wird von der prim·arseitigen R·uckkopplungswicklung w·ahrend seiner stromleitenden Phase mit einem Basisstrom angesteuert. Wenn jetzt eine Sekund·arwicklung w·ahrend dieser stromleitenden Phase stark belastet, z.B. ·uber den Thyristor kurzgeschlossen wird, bricht auch die Spannung an der prim·arseitigen R·uckkopplungswicklung zusammen. Diese Wicklung kann dann f·ur den Schalttransistor nicht mehr einen f·ur den leitenden Betrieb ausreichenden Basis strom liefern. Das Schaltnetzteil schwingt dann nicht mehr, so dass die sekund·arseitigen Betriebsspannungen in erw·unschter Weise zusammenbrechen. Der schaltungstechni- sche Aufwand ist gering. Er besteht vorzugsweise aus einem Thyristor und zwei Widerst·anden.

Ein Ausf·uhrungsbeispiel der Erfindung wird anhand der Zeichnung erl·autert. Darin zeigen Figur 1 ein erfindungsgem·ass ausgebildetes Schaltnetzteil und Figur 2 Kurven zur Erl·auterung der Wirkungsweise. Dabei zeigen die kleinen Buchstaben, an welchen Punkten in Figur 1 die Spannungen gem·ass Figur 2 stehen.

Das Schaltnetzteil gem·ass Figur 1 enth·alt auf der Prim·arseite des Trenntransformators 1 den Netzgleichrichter 2, den Ladekondensator 3, den Strom-Messwiderstand 4, die Prim·arwicklung 5 den Schalttransistor 6, die zur Schwingungserzeugung dienende R·uckkopplungswicklung 7, den zur Steuerung des Schalttransistors 6 dienenden Thyristor 8, die Regelwicklung 9, den zur Erzeugung der Regelspannung dienenden Gleichrichter 10 sowie die zur Stabilisierung der Betriebsspannungen dienende Regelschaltung 11 mit dem Transistor 12 und der eine Referenzspannung lieferndenZenerdiode 13. Die Sekund·arwicklung 14 liefert ·uber den Gleichrichter 15 eine erste Betriebsspannung U1 von 150 V. Ein Abgriff der Wicklung 14 liefert ·uber den Gleichrichter 16 eine zweite Betriebsspannung U2 von 12 V f·ur einen Fernbedienungsempf·anger.

Eine weitere Sekund·arwicklung 19 liefert ·uber den Gleichrichter 20 eine dritte Betriebsspannung U3 von 12 V. Die Polung der Wicklungen 14,19 und der Gleichrichter 15,16,20 ist derart, dass die Gleichrichter 15,16,20 w·ahrend der Sperrphase des Schalttransistors 6 durch die sekund·arseitig auftretenden Impulsspannungen leitend gesteuert sind und die angeschlossenen Ladekondensatoren aufladen.

An das untere Ende der Wicklung 19 ist zus·atzlich der Thyristor 24 angeschlossen. An die Steuerelektrode b des Thyristors 24 ist die Betriebs spannung U2 ·uber den Spannungsteiler 25,26 angelegt.

Die Wirkungsweise der Schaltung wird anhand der Figur 2 erl·autert. Es sei angenommen, dass das Schaltnetzteil im Zeitpunkt tl in Betrieb genommen wird. Mit der Diode 21 wird aus der Netzspannung am Punkt d ein positiver Impuls erzeugt. Dieser gelangt ·uber den Kondensator 23 auf die Basis des Schalttransistors 6 und steuert diesen leitend. Dadurch beginnt das Schaltnetzteil zu schwingen, wobei die Schwingung durch die R·uckk opplungswicklung 7

aufrechterhalten wird. Am Punkt a entsteht dann eine m·aanderf·ormige

Wechselspannung mit einer Frequenz von etwa 25-30 kHz.

opplungswicklung 7

aufrechterhalten wird. Am Punkt a entsteht dann eine m·aanderf·ormige

Wechselspannung mit einer Frequenz von etwa 25-30 kHz.

Die daraufhin in den Sekund·arwicklungen 14,19 erzeugten Impulse erzeugen in der beschriebenen Weise die Betriebsspannungen U1,U2,U3. Der Spannungsteiler 25,26 ist so bemessen, dass der Thyristor 24 gesperrt bleibt, d.h. die Spannung am Punkt 6 jst kleiner als 0,7 V. Der Thyristor 24 hat dann keine Wirkung. Dir Amplitude der Spannungen Ui,U2,U3 wird ·uber die Regelschaltung 11 stabilisiert.

Es sei jetzt angenommen, dass durch einen Fehler in der Regelschaltung 11, z.B. durch Ausfall eines Bauteiles, die Regelung zur Stabilisierung der Betriebsspannungen U1,U2,U3 nicht mehr wirkt und diese Betriebsspannungen stark ansteigen. Dadurch steigt auch die Spannung am Punkt b an.

Im Zeitpunkt t2 erreicht diese Spannung den Wert von 0,7 V, so dass der Thyristor 24 z·undet. Der untere Teil der Wicklung 19 ist jetzt praktisch kurzgeschlossen. Das Netzteil ist dadurch sekund·arseitig so stark belastet, dass die R·uck kopplungswicklung 7 keinen ausreichenden Basisstrom zur Steuerung des Schalttransistors 6 in seine stromleitende Phase mehr liefert. Im Zeitpunkt t2 bricht die Schwingung des Schaltnetzteiles ab, so dass auch die Wechselspannung am Punkt a auf null abf·allt. Den Ladekondensatoren der Gleichrichter 15,16,20 wird kein Strom mehr zugef·uhrt, so dass die Betriebspannungen U1,U2,U3 nicht weiter ansteigen k·onnen, sondern entsprechend den wirksamen Entladezeitkonstanten abfallen. Das Schaltnetzteil w·urde auf diese Weise an sich beliebig lange ausgeschaltet bleiben.

Im Zeitpunkt t3 erscheint am Punkt b der n·achste aus der Netzspannung gewonnene Startimpuls, der den Schalttransistor 6 wieder leitend steuert, so dass die Wechselspannung am Punkt a wieder auftritt. Das Schaltnetzteil geht also in einen getakteten Betrieb ·uber, bei dem die ·ubertragene Leistung entsprechend dem Zeitverh·altnis zwischen Einschaltphase und Ausschaltphase der Spannung am Punkt a betr·achtlich verringert ist. Die Betriebsspannungen U11U2,U3 k·onnen nicht mehr unzul·assig hohe Werte annehmen.

Bei Ger·aten der Nachrichtentechnik wie z.B. einem Fernsehempf·anger ist es bekannt, die f·ur die einzelnen Stufen notwendigen Betriebsspannungen mit einem Schaltnetzteil aus der Netzspannung zu erzeugen (Funkschau 1975, Heft 5, Seite 40-43). Ein Schaltnetzteil erm·oglicht die f·ur den Anschluss ·ausserer Ger·ate und f·ur die Massnahmen zur Schutzisolierung vorteilhafte galvanische Trennung der Empf·angerschaltung vom Netz. Da ein Schaltnetzteil mit einer gegen·uber der Netzfrequenz hohen Frequenz von ca. 30 kHz arbeitet, kann der zur galvanischen Trennung dienende Trenntransformator gegen·uber einem Netztrafo f·ur 50 Hz wesentlich kleiner und leichter ausgebildet sein. Durch mehrere Wicklungen oder Wicklungsabgriffe und angeschlossene Gleichrichter k·onnen auf der Sekund·arseite des Trenntransformators Betriebs~ spannungen unterschiedlicher Gr·osse und Polarit·at erzeugt werden.

Ein solches Schaltnetzteil enth·alt eine Regelschaltung zur Stabilisierung der Amplitude der auf der Sekund·arseite erzeugten Betriebsspannungen. In dieser Regelschaltung wird eine durch Gleichrichtung der Impulsspannung am Trafo gewonnene Stellgr·osse erzeugt und mit einer Bezugsspannung verglichen. In Abh·angigkeit von der Abweichung wird der Schaltzeitpunkt des auf der Prim·arseite vorgesehenen elektronischen Schalters so gesteuert, dass die Amplitude der erzeugten Betriebsspannungen konstant bleibt.

Bei einem solchen Schaltnetzteil kann die genannte Regelschaltung z.B. durch ein fehlerhaftes Bauteil ausfallen. Die Regelung der Amplitude der erzeugten Betriebsspannungen ist dann unkontrolliert. Die Betriebsspannungen k·onnen dann auf den doppelten oder dreifachen Wert ansteigen. Dadurch besteht die Gefahr, dass das Schaltnetzteil oder die an die Betriebsspannungen angeschlossenen Verbraucher wie z.B. der Heizfaden der Bildr·ohre oder der Zeilenendstufentransistor zerst·ort werden. Der Anstieg der Betriebsspannungen kann dar·uberhinaus einen Anstieg der im Fernsehempf·anger erzeugten Hochspannung und dadurch eine R·ontgenstrahlung ausl·osen.

Es ist auch ein Schaltnetzteil bekannt (DE-OS 27 27 332), bei dem zum Schutz gegen einen zu starken Anstieg der erzeugten Betriebsspannungen aus der Impulsspannung an der Prim·arseite des Trafos eine Stellgr·osse gewonnen wird, die beim ·Uberschreiten eines Schwellwertes den R·uckkopplungsweg unwirksam steuert. Durch die Unterbrechung des R·uckkopplungsweges kann das Schaltnetzteil nicht mehr schwingen, so dass in erw·unschter Weise auch keine Betriebsspannungen mehr erzeugt werden. Diese Schaltung erfordert jedoch eine Vielzahl von Bauteilen und ist daher relativ teuer.

Der Erfindung liegt die Aufgabe zugrunde, eine sicher wirkende Schutzschaltung mit verringertem Schaltungsaufwand gegen

die oben

beschriebenen Gefahren zu schaffen.

die oben

beschriebenen Gefahren zu schaffen.Diese Aufgabe wird durch die im Anspruch 1 beschriebene Erfindung gel·ost. Vorteilhafte Weiterbildungen der Erfindung sind in den Unteranspr·uchen beschrieben.

Die Erfindung beruht auf folgender ·Uberlegung: Der Schalttransistor auf der Prim·arseite wird von der prim·arseitigen R·uckkopplungswicklung w·ahrend seiner stromleitenden Phase mit einem Basisstrom angesteuert. Wenn jetzt eine Sekund·arwicklung w·ahrend dieser stromleitenden Phase stark belastet, z.B. ·uber den Thyristor kurzgeschlossen wird, bricht auch die Spannung an der prim·arseitigen R·uckkopplungswicklung zusammen. Diese Wicklung kann dann f·ur den Schalttransistor nicht mehr einen f·ur den leitenden Betrieb ausreichenden Basis strom liefern. Das Schaltnetzteil schwingt dann nicht mehr, so dass die sekund·arseitigen Betriebsspannungen in erw·unschter Weise zusammenbrechen. Der schaltungstechni- sche Aufwand ist gering. Er besteht vorzugsweise aus einem Thyristor und zwei Widerst·anden.

Ein Ausf·uhrungsbeispiel der Erfindung wird anhand der Zeichnung erl·autert. Darin zeigen Figur 1 ein erfindungsgem·ass ausgebildetes Schaltnetzteil und Figur 2 Kurven zur Erl·auterung der Wirkungsweise. Dabei zeigen die kleinen Buchstaben, an welchen Punkten in Figur 1 die Spannungen gem·ass Figur 2 stehen.

Das Schaltnetzteil gem·ass Figur 1 enth·alt auf der Prim·arseite des Trenntransformators 1 den Netzgleichrichter 2, den Ladekondensator 3, den Strom-Messwiderstand 4, die Prim·arwicklung 5 den Schalttransistor 6, die zur Schwingungserzeugung dienende R·uckkopplungswicklung 7, den zur Steuerung des Schalttransistors 6 dienenden Thyristor 8, die Regelwicklung 9, den zur Erzeugung der Regelspannung dienenden Gleichrichter 10 sowie die zur Stabilisierung der Betriebsspannungen dienende Regelschaltung 11 mit dem Transistor 12 und der eine Referenzspannung lieferndenZenerdiode 13. Die Sekund·arwicklung 14 liefert ·uber den Gleichrichter 15 eine erste Betriebsspannung U1 von 150 V. Ein Abgriff der Wicklung 14 liefert ·uber den Gleichrichter 16 eine zweite Betriebsspannung U2 von 12 V f·ur einen Fernbedienungsempf·anger.

Eine weitere Sekund·arwicklung 19 liefert ·uber den Gleichrichter 20 eine dritte Betriebsspannung U3 von 12 V. Die Polung der Wicklungen 14,19 und der Gleichrichter 15,16,20 ist derart, dass die Gleichrichter 15,16,20 w·ahrend der Sperrphase des Schalttransistors 6 durch die sekund·arseitig auftretenden Impulsspannungen leitend gesteuert sind und die angeschlossenen Ladekondensatoren aufladen.

An das untere Ende der Wicklung 19 ist zus·atzlich der Thyristor 24 angeschlossen. An die Steuerelektrode b des Thyristors 24 ist die Betriebs spannung U2 ·uber den Spannungsteiler 25,26 angelegt.

Die Wirkungsweise der Schaltung wird anhand der Figur 2 erl·autert. Es sei angenommen, dass das Schaltnetzteil im Zeitpunkt tl in Betrieb genommen wird. Mit der Diode 21 wird aus der Netzspannung am Punkt d ein positiver Impuls erzeugt. Dieser gelangt ·uber den Kondensator 23 auf die Basis des Schalttransistors 6 und steuert diesen leitend. Dadurch beginnt das Schaltnetzteil zu schwingen, wobei die Schwingung durch die R·uckk

opplungswicklung 7

aufrechterhalten wird. Am Punkt a entsteht dann eine m·aanderf·ormige

Wechselspannung mit einer Frequenz von etwa 25-30 kHz.

opplungswicklung 7

aufrechterhalten wird. Am Punkt a entsteht dann eine m·aanderf·ormige

Wechselspannung mit einer Frequenz von etwa 25-30 kHz.Die daraufhin in den Sekund·arwicklungen 14,19 erzeugten Impulse erzeugen in der beschriebenen Weise die Betriebsspannungen U1,U2,U3. Der Spannungsteiler 25,26 ist so bemessen, dass der Thyristor 24 gesperrt bleibt, d.h. die Spannung am Punkt 6 jst kleiner als 0,7 V. Der Thyristor 24 hat dann keine Wirkung. Dir Amplitude der Spannungen Ui,U2,U3 wird ·uber die Regelschaltung 11 stabilisiert.

Es sei jetzt angenommen, dass durch einen Fehler in der Regelschaltung 11, z.B. durch Ausfall eines Bauteiles, die Regelung zur Stabilisierung der Betriebsspannungen U1,U2,U3 nicht mehr wirkt und diese Betriebsspannungen stark ansteigen. Dadurch steigt auch die Spannung am Punkt b an.

Im Zeitpunkt t2 erreicht diese Spannung den Wert von 0,7 V, so dass der Thyristor 24 z·undet. Der untere Teil der Wicklung 19 ist jetzt praktisch kurzgeschlossen. Das Netzteil ist dadurch sekund·arseitig so stark belastet, dass die R·uck kopplungswicklung 7 keinen ausreichenden Basisstrom zur Steuerung des Schalttransistors 6 in seine stromleitende Phase mehr liefert. Im Zeitpunkt t2 bricht die Schwingung des Schaltnetzteiles ab, so dass auch die Wechselspannung am Punkt a auf null abf·allt. Den Ladekondensatoren der Gleichrichter 15,16,20 wird kein Strom mehr zugef·uhrt, so dass die Betriebspannungen U1,U2,U3 nicht weiter ansteigen k·onnen, sondern entsprechend den wirksamen Entladezeitkonstanten abfallen. Das Schaltnetzteil w·urde auf diese Weise an sich beliebig lange ausgeschaltet bleiben.

Im Zeitpunkt t3 erscheint am Punkt b der n·achste aus der Netzspannung gewonnene Startimpuls, der den Schalttransistor 6 wieder leitend steuert, so dass die Wechselspannung am Punkt a wieder auftritt. Das Schaltnetzteil geht also in einen getakteten Betrieb ·uber, bei dem die ·ubertragene Leistung entsprechend dem Zeitverh·altnis zwischen Einschaltphase und Ausschaltphase der Spannung am Punkt a betr·achtlich verringert ist. Die Betriebsspannungen U11U2,U3 k·onnen nicht mehr unzul·assig hohe Werte annehmen.

A power supply voltage stabiliz

er comprising a transformer, of which the primary winding is connected to a switching means for controlling power supply to the primary winding. An oscillator circuit is associated with the switching means in order to control on/off operation of the switching means. An abnormal overvoltage and/or overcurrent detection circuit is provided for terminating the oscillation operation of the oscillator circuit when impending overvoltage and/or overcurrent is detected.

er comprising a transformer, of which the primary winding is connected to a switching means for controlling power supply to the primary winding. An oscillator circuit is associated with the switching means in order to control on/off operation of the switching means. An abnormal overvoltage and/or overcurrent detection circuit is provided for terminating the oscillation operation of the oscillator circuit when impending overvoltage and/or overcurrent is detected. 1. A power supply voltage stabilizer comprising:

a transformer including a primary winding connected to a power source and a secondary winding for output purposes;

switching means connected to said primary winding for controlling power supply to said primary winding;

an oscillator circuit for controlling on/off operation of said switching means; and

abnormal condition detection means for developing a control signal for terminating oscillation operation of said oscillator circuit when an abnormal condition is detected;

said oscillator circuit including an astable multivibrator, and variable impedance means for varying an oscillation frequency of said astable multivibrator.

2. A power supply voltage stabilizer comprising:

a transformer including a primary winding connected to a power source and a secondary winding for output purposes;

switching means connected to said primary winding for controlling power supply to said primary winding;

an oscillator circuit for controlling on/off operation of said switching means; and

abnormal condition detection means for developing a control signal for terminating oscillation operation of said oscillator circuit when an abnormal condition is detected;

said transformer further including an auxiliary winding for developing a voltage proportional to that developed through said secondary winding, said voltage developed through said auxiliary winding being applied to said oscillator circuit for driving said oscillator circuit;

said abnormal condition detection means including an overvoltage detection circuit connected to said auxiliary winding for developing said control signal when an overvoltage is developed through said auxilliary winding;

said oscillator circuit comprising an astable multivibrator, and variable impedance means for varying an oscillation frequency of said astable multivibrator.

3. A power supply voltage stabilizer comprising:

a transformer including a primary winding connected to a power source and a secondary winding for output purposes;

switchi

ng means connected to said primary winding for controlling power supply to said primary winding;

ng means connected to said primary winding for controlling power supply to said primary winding;an oscillator circuit for controlling on/off operation of said switching means; and

abnormal condition detection means for developing a control signal for terminating oscillation operation of said oscillator circuit when an abnormal condition is detected;

said transformer further including an auxiliary winding for developing a voltage proportional to that developed through said secondary winding, said voltage developed through said auxiliary winding being applied to said oscillator circuit for driving said oscillator circuit;

said abnormal condition detec

tion means including an overvoltage detection circuit connected to said auxiliary winding for developing said control signal when an overvoltage is developed through said auxiliary winding;

said overvoltage detection circuit including a latching means for continuously developing said control signal.

4. A power supply voltage stabilizer comprising:

a transformer including a primary winding connected to a power source and a secondary winding for output purposes;

switching means connected to said primary winding for controlling power supply to said primary winding;

an oscillator circuit for controlling on/off operation of said switching means;

abnormal condition detection means for developing a control signal for terminating oscillation operation of said oscillator circuit when an abnormal condition is detected;

said transformer further including an auxiliary winding for developing a voltage proportional to that developed through said secondary winding, said voltage developed through said auxiliary winding being applied to said oscillator circuit for driving said oscillator circuit;

said abnormal condition detection means including an overvoltage detection circuit connected to said auxiliary winding for developing said control signal when an overvoltage is developed through said auxiliary winding;

said overvoltage detection circui

t further includes,

t further includes,a reference voltage generation means for developing a reference voltage proportional to a voltage applied from said power source; and

comparing means for comparing said voltage developed through said auxiliary winding with said reference voltage in order to develop said control signal when said voltage developed through said auxiliary winding exceeds said reference voltage.

5. A power supply voltage stabilizer comprising:

a transformer including a primary winding connected to a power source and a secondary winding for output purposes;

switching means connected to said primary winding for controlling power supply to said primary winding;

an oscillator circuit for controlling on/off operation of said switching means; and

abnormal condition detection means for developing a control signal for terminating oscillation operation of said oscillator circuit when an abnormal condition is detected;

said abnormal condition detection means including an overcurrent detection circuit connected to said primary winding for developing said control signal when an overcurrent flows through said primary winding;

wherein said oscillator circuit includes an astable multivibrator, and variable impedance means for varying an oscillation frequency of said astable multivibrator.

6. A power supply voltage stabilizer comprising:

a transformer including a primary winding connected to a power source and a secondary winding for output purposes;

switching means connected to said primary winding for controlling power supply to said primary winding;

an oscillator circuit for controlling on/off operation of said switching means; and

abnormal condition detection means for developing a control signal for terminating oscillation operation of said oscillator circuit when an abnormal condition is detected;

said abnormal condition detection means including an overcurrent detection circuit connected to said primary winding for developing said control signal when an overcurrent flows through said primary winding;

said overcurrent detection circuit including a latching means for continuously developing said control signal;

said oscillator circuit including an astable multivibrator, and variable impedance means for varying an oscillation frequency of said astable multivibrator.

7. The power supply voltage stabilizer of claim 1, 2, 5, or 6, wherein said variable impedance means comprise a photo transistor, and wherein a light emitting diode is connected to said secondary wind

ing for emitting a light of which amount is proportional to a voltage developed through said secondary winding, said light emitted from said light emitting diode being applied to said photo transistor. 8. The power supply voltage stabilizer of claim 7, wherein said light emitting diode and said photo transistor are incorporated in a single photo coupler. 9. A power supply voltage stabilizer comprising:

ing for emitting a light of which amount is proportional to a voltage developed through said secondary winding, said light emitted from said light emitting diode being applied to said photo transistor. 8. The power supply voltage stabilizer of claim 7, wherein said light emitting diode and said photo transistor are incorporated in a single photo coupler. 9. A power supply voltage stabilizer comprising: a transformer including a primary winding connected to a power source and a secondary winding for output purposes;

switching means connected to said primary winding for controlling power supply to said primary winding;

an oscillator circuit for controlling on/off operation of said switching means; and

abnormal condition detection means for developing a control signal for terminating oscillation operation of said oscillator circuit when an abnormal condition is detected;

said transformer further including an auxiliary winding for developing a voltage proportional to that developed through said secondary winding, said voltage developed through said auxiliary winding being applied to said oscillator circuit for driving said oscillator circuit;

said abnormal condition detection means including an overvoltage detection circuit connected to said auxiliary winding for developing said control signal when an overvoltage is developed through said auxilliary winding;

said overvoltage detection circuit including a latching means for continuously developing said control signal;

said oscillator circuit including an astable multivibrator, and variable impedance means for varying an oscillation frequency of said astable multivibrator.

10. A power supply voltage stabilizer comprising:

a transformer including a primary winding connected to a power source and a secondary winding for output purposes;

switching means connected to said primary winding for controlling power supply to said primary winding;

an oscillator circuit for controlling on/off operation of said switching means;

abnormal condition detection means for developing a control signal for terminating oscillation operation of said oscillator circuit when an abnormal condition is detected;

said transformer further including an auxiliary winding for developing a voltage proportional to that developed th

rough said secondary winding, said voltage developed through said auxiliary winding being applied to said oscillator circuit for driving said oscillator circuit;

rough said secondary winding, said voltage developed through said auxiliary winding being applied to said oscillator circuit for driving said oscillator circuit;said abnormal condition detection means including an overvoltage detection circuit connected to said auxiliary winding for developing said control signal when an overvoltage is developed through said auxiliary winding;

said overvoltage detection circuit including,

a reference voltage generation means for developing a reference voltage proportional to a voltage applied from said power source; and

comparing means for comparing said voltage developed through said auxiliary winding with said reference voltage in order to develop said control signal when said voltage developed through said auxiliary winding exceeds said reference voltage;

said oscillator circuit including an astable multivibrator, and a variable impedance means for varying an oscillation frequency of said astable multivibrator.

11. A power supply voltage stabilizer comprising:

transformer means including a primary winding connected to a power source, a secondary winding for producing an output voltage, and an auxiliary winding for developing a voltage proportional to said output voltage produced by said secondary winding;

switching means connected to said primary winding for controlling the power supply from said power source to said primary winding;

oscillator circuit means for controlling the on/off operation of said switching means;

overvoltage detection circuit means connected to said auxiliary winding for developing a control signal to terminate the oscillation operation of said oscillator circuit means when an overvoltage condition is detected, said overvoltage detection circuit means including,

means for developing a reference potential, and

comparing means responsive to said voltage developed at said auxiliary winding and to said reference potential for comparing said reference potential with said voltage developed at said auxiliary winding and for generating said control signal to terminate the oscillation operation of said oscillator circuit means when said voltage developed at said auxiliary winding exceeds said reference potential.

12. A power supply voltage stabilizer comprising:

transformer means including a primary winding connected to a power source and having a voltage supplied thereto, a secondary winding for producing an output voltage, and an auxiliary winding for developing a voltage proportional to said output voltage produced by said secondary winding;

switching means connected to said primary winding for controlling the power supply from said power source to said primary winding;

oscillator circuit means for controlling the on/off operation of said switching means;

overcurrent detection circuit means connected to said primary winding for developing a control signal to terminate the oscillation operation of said oscillator circuit means when an overcurrent condition is detected, said overcurrent detection circuit means including,

means for monitoring said voltage supplied to said primary winding of said transformer means,

means for measuring the amount of current passing through said primary winding of said transformer means by translating said amount of current into a corresponding amount of voltage potential,

switching means responsive to said corresponding amount of voltage potential for switching to a first switched condition when the corresponding voltage potential exceeds a predetermined voltage potential and for switching to a second switched condition when said voltage potential does not exceed said predetermined voltage potential, and

comparing means responsive to said voltage supplied to said primary winding and connected to an output of said switching means for generating said control signal to terminate oscillation operation of said oscillator circuit means when said switching means switches to said first switched condition in response to the exceeding of said predetermined voltage potential by said corresponding voltage potential.

13. A power supply voltage stabilizer in accordance with claim 11 or 12 wherein said comparing means comprises a double base diode.

Description:

BACKGROUND AND SUMMARY OF THE INVENTION

The present invention relates to a power supply voltage stabilizer and, more particularly, to a power supply voltage stabilizer employing a switching system for controlling power supply to a transformer included in the power supply voltage stabilizer.

In the conventional power supply voltage stabilizer employing a switching system for controlling power supply to a transformer included in the power supply voltage stabilizer, there is a possibility that an abnormal overvoltage will be developed from an output terminal thereof and/or an abnormal overcurrent may flow through the primary winding of the transformer.

Accordingly, an object of the present invention is to provide a protection means for protecting the power supply voltage stabilizer from an abnormal overvoltage and/or overcurrent.

Another object of the present invention is to provide a detection means for detecting an impending overvoltage and/or overcurrent occurring within the power supply voltage stabilizer.

Other objects and further scope of applicability of the present invention will become apparent from the detailed description given hereinafter. It should be understood, however, that the detailed description and specific examples, while indicating preferred embodiments of the invention, are given by way of illustration only, since various changes and modifications within the spirit and scope of the invention will become apparent to those skilled in the art from this detailed description.

The

power supply voltage stabilizer of the present invention mainly comprises a transformer including a primary winding connected to a commercial power source through a rectifying circuit, a secondary winding for output purposes, and an auxiliary winding. A driver circuit including a switching means is connected to the primary winding for controlling the power supply to the primary winding. An oscillator circuit is associated with the switching means to control ON/OFF operation of the switching means, thereby controlling the power supply to the primary winding.

To achieve the above objects, pursuant to an embodiment of the present invention, an overvoltage detection circuit is connected to the auxiliary winding. The overvoltage detection circuit functions to compare a voltage created in the auxiliary winding with the rectified power supply voltage, and develop a control signal, when an impending overvoltage is detected, for terminating operation of the oscillator circuit, thereby precluding power supply to the primary winding.

In another embodiment of the present invention, an overcurrent detection circuit is provided for detecting an impending overcurrent flowing through the primary winding to develop a control signal for terminating operation of the oscillator circuit.

BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will become more fully understood from the detailed description given hereinbelow and the accompanying drawings, which are given by way of illustration only, and thus are not limitative of the present invention and wherein:

FIG. 1 is a circuit diagram of a basic construction of a power supply voltage stabilizer of the present invention;

FIG. 2 is a block diagram of an embodiment of a power supply voltage stabilizer of the present invention, which includes an oscillator circuit and an over voltage detection circuit;

FIG. 3 is a circuit diagram of an embodiment of the overvoltage detection circuit included in the power supply voltage stabilizer of FIG. 2;

FIG. 4 is a circuit diagram of an embodiment of the oscillator circuit included in the power supply voltage stabilizer of FIG. 2;

FIG. 5 is a waveform chart for explaining operation of the oscillator circuit of FIG. 4;

FIG. 6 is a block diagram of another embodiment of a power supply voltage stabilizer of the present invention, which includes an oscillator circuit and an overcurrent detection circuit; and

FIG. 7 is a circuit diagram of an embodiment of the overcurrent detection circuit included in the power supply voltage stabilizer of FIG. 6.

DESCRIPTION OF THE PREFERRED EMBODIMENTS

R eferring now in detail to the drawings, and to facilitate a more complete understanding of the present invention, a basic construction of a power supply voltage stabilizer of the present invention will be first described with reference to FIG. 1.

eferring now in detail to the drawings, and to facilitate a more complete understanding of the present invention, a basic construction of a power supply voltage stabilizer of the present invention will be first described with reference to FIG. 1.

The power supply voltage stabillizer mainly comprises a transformer T including a primary winding N 1 connected to a commercial power source V, a secondary winding N 2 connected to an output terminal V 0 , and an auxiliary winding N 3 . An oscillator circuit OSC is associated with the primary winding N 1 and the auxiliary winding N 3 to control the power supply from the commercial power source V to the primary winding N 1 .

A rectifying circuit E is connected to the commercial power source V for applying a rectified voltage to a capacitor C 1 . A negative terminal of the capacitor C 1 is grounded, and a positive terminal of the capacitor C 1 is connected to the collector electrode of a switching transistor Q 5 through the primary winding N 1 of the transformer T. The oscillator circuit OSC performs the oscillating operation when receiving a predetermined voltage, and develops a control signal toward the base electrode of the switching transistor Q 5 to control the switching operation of the switching transistor Q 5 . The switching transistor Q 5 functions to control the power supply to the primary winding N 1 , thereby controlling the power transfer to the secondary winding N 2 and the auxiliary winding N 3 .

The auxiliary winding N 3 is connected to a capacitor C 3 in a parallel fashion via a diode D 1 . A positive terminal of the capacitor C 3 is connected to the oscillator circuit OSC to supply a drive voltage Vc 3 . A negative terminal of the capacitor C 3 is connected to the emitter electrode of the switching transistor Q 5 and grounded. The positive terminal of the capacitor C 3 is connected to the primary winding N 1 via a diode D 2 and a capacitor C 2 in order to stabilize the initial condition of the oscillator circuit OSC.

The secondary winding N 2 functions to develop a predetermined voltage through the output terminal V 0 . A smoothing capacitor C 0 is connected to the secondary winding N 2 via a diode D 0 , and a series circuit of a resistor R 0 and a light emitting diode D i is connected to the smoothing capacitor C 0 in a parallel fashion. The light emitted from the light emitting diode D i is applied to a photo transistor Q 8 employed in the oscillator circuit OSC. The light emitting diode D i and the photo transistor Q 8 are preferably incorporated in a single package as a photo coupler.

The light amount emitted from the light emitting diode D i is proportional to the output voltage developed from the output terminal V 0 . The photo transistor Q 8 exhibits the impedance corresponding to the applied light amount. The oscillator circuit OSC is so constructed that the oscillation frequency is varied in response to variation of the impedance of the photo transistor Q 8 . Accordingly, the ON/OFF operation of the switching transistor Q 5 is controlled in response to the output voltage level, thereby stabilizing the output voltage level.

In the above constructed power supply voltage stabilizer, there is a possibility that an abnormal overvoltage is developed through the secondary winding N 2 and the auxiliary winding N 3 when the oscillator circuit OSC or the light emitting diode D i is placed in the fault condition.

FIG. 2 show s an embodiment of the power supply voltage stabilizer of the present invention, which includes means for precluding occurrence of the above-mentioned overvoltage. Like elements corresponding to those of FIG. 1 are indicated by like numerals.

s an embodiment of the power supply voltage stabilizer of the present invention, which includes means for precluding occurrence of the above-mentioned overvoltage. Like elements corresponding to those of FIG. 1 are indicated by like numerals.

The power supply voltage stabilizer of FIG. 2 mainly comprises the transformer T, the oscillator circuit OSC, a driver circuit 1 including the switching transistor Q 5 , and an overvoltage detection circuit 3.

The positive terminal of the capacitor C 3 is connected to the driver circuit 1 and the oscillator circuit OSC to apply the driving voltage thereto. The positive terminal of the capacitor C 3 is also connected to the primary winding N 1 through the diode D 2 and a parallel circuit of the capacitor C 2 and a resistor R 2 in order to stabilize the initial start operation of the oscillator circuit OSC. The secondary winding N 2 is connected to an output level detector 2, which comprises the light emitting diode D i as shown in FIG. 1. The ON/OFF control of the switching transistor Q 5 is similar to that is achieved in the power supply voltage stabilizer of FIG. 1.

The secondary winding N 2 and the auxiliary winding N 3 are wound in the same polarity fashion and, therefore, the voltage generated through the auxiliary winding N 3 is proportional to that voltage generated through the secondary winding N 2 . The overvoltage detection circuit 3 is connected to receive the voltage at a point a as a power source voltage, and the voltage at a point b which is connected to the positive terminal of the capacitor C 3 . When the voltage level at the point b exceeds a reference level, the overvoltage detection circuit 3 develops a control signal for terminating the operation of the oscillator circuit OSC.

FIG. 3 shows a typical construction of the overvoltage detection circuit 3.

The voltage at the point a is applied to a series circuit of resistors R 3 and R 4 , and grounded. The voltage at the point b is applied to the connection point of the resistors R 3 and R 4 via a diode D 3 . The connection point of the resistors R 3 and R 4 is grounded through resistors R 5 and R 6 and a Zener diode Z 1 . A double-base diode (Trade Name Programmable Unijunction Transistor) P 1 is provided for developing the control signal to be applied to the oscillator circuit OSC. The anode electrode of the programmable unijunction transistor P 1 is connected to the connection point of the resistors R 3 and R 4 , the gate electrode of the programmable unijunction transistor P 1 is connected to the connection point of the resistors R 5 and R 6 , and the cathode electrode is connected to the oscillator circuit OSC.

When the voltage level of the point b exceeds a reference level VZ 1 , the programmable unijunction transistor P 1 is turned on to develop the control signal for terminating the oscillation operation of the oscillator OSC. In this way, the impending abnormal overvoltage is detected to protect the circuit elements. The ON condition of the programmable unijunction transistor P 1 is maintained as long as the main power switch is closed, because the overvoltage detection circuit 3 is connected to receive the voltage from the point a.

The voltage detection circuit 3 does not necessarily employ the programmable unijunction transistor. Another element showing the latching characteristics such as a negative resistance element can be employed instead of the programmable unijunction transistor.

FIG. 4 shows a typical construction of the oscillator circuit OSC.

The oscillation circuit OSC mainly comprises an astable multivibrator including transistors Q 1 , Q 2 and Q 3 , and an o utput stage including a transistor Q 4 . The astable multivibrator is connected to receive the voltage appearing across the capacitor C 3 , and develops an output signal of which frequency is determined by the circuit condition as long as the multivibrator receives a voltage greater than a predetermined level.

utput stage including a transistor Q 4 . The astable multivibrator is connected to receive the voltage appearing across the capacitor C 3 , and develops an output signal of which frequency is determined by the circuit condition as long as the multivibrator receives a voltage greater than a predetermined level.

The output signal of the output stage is applied to the base electrode of the switching transistor Q 5 included in the driver circuit 1 in order to switch the switching transistor Q 5 with a predetermined frequency. A transistor Q 9 is interposed between the base electrode of the transistor Q 3 and the grounded terminal. The transistor Q 9 is controlled by the control signal derived from the overvoltage detection circuit 3. Accordingly, the transistor Q 3 is turned off to terminate the oscillation operation when the abnormal overvoltage is detected by the overvoltage detection circuit 3.

Now assume that a voltage Vc 3 is developed across the capacitor C 3 . When main power supply switch is closed, the voltage Vc 3 varies in a manner shown by a curve X in FIG. 5. When the voltage Vc 3 reaches a predetermined level, the astable multivibrator begins the oscillation operation. More specifically, the transistor Q 1 is first turned on because the base electrode of the transistor Q 1 is connected to a capacitor C 4 of which the capacitance value is relatively small. At this moment, the transistor Q 2 is held off.

Because of turning on of the transistor Q 1 , the capacitor C 4 is gradually charged through a resistor R 4 and the transistor Q 1 . Accordingly, the base electrode voltage of the transistor Q 1 is gradually increased and, hence, the emitter electrode voltage of the transistor Q 1 is also increased to turn on the transistor Q 2 . When the transistor Q 2 is turned on, the transistor Q 3 is also turned on. The base electrode voltage of the transistor Q 2 which is bypassed by a resistor R 1 is reduced and, therefore, the transistor Q 2 is stably on. At this moment, the transistor Q 1 is turned off.

When the transistor Q 3 is turned on, the transistor Q 4 is turned on to develop a signal to turn on the switching transistor Q 5 . Upon turning on of the transistor Q 3 , the charge stored in the capacitor C 4 is gradually discharged through paths shown by arrows in FIG. 4. Therefore, the base electrode voltage of the transistor Q 1 is gradually reduced. When the base electrode voltage of the transistor Q 1 becomes less than a predetermined level, the transistor Q 1 is turned on, and the transistor Q 2 , Q 3 and Q 4 are turned off. Accordingly, the transistor Q 5 is turned off. After passing the initial start condition, the driving voltage Vc 3 is held at a predetermined level as shown by a curve Y in FIG. 5 to maintain the above-mentioned oscillation operation.

The photo transistor Q 8 is disposed in the discharge path of the capacitor C 4 in order to control the discharge period in response to the impedance of the photo transistor Q 8 . That is, the oscillation frequency is controlled in response to the light amount emitted from the light emitting diode included in the output level detector 2.

FIG. 6 shows another em bodiment of the power supply voltage stabilizer of the present invention, which includes means for precluding occurrence of an abnormal overcurrent. Like elements corresponding to those of FIG. 2 are indicated by like numerals.

bodiment of the power supply voltage stabilizer of the present invention, which includes means for precluding occurrence of an abnormal overcurrent. Like elements corresponding to those of FIG. 2 are indicated by like numerals.

In the power supply voltage stabilizer of FIG. 1, there is a possibility that an abnormally large current flows through the primary winding N 1 when the magnetic flux is saturated due to requirement of large current at the secondary winding side. The power supply voltage stabilizer of FIG. 6 includes an overcurrent detection circuit 4 for detecting an impending abnormally large current.

A resistor R 9 is interposed between the emitter electrode of the switching transistor Q 5 included in the driver circuit 1 and the grounded terminal. The overcurrent detection circuit 4 is connected to receive a signal from the connection point of the resistor R 9 and the emitter electrode of the switching transistor Q 5 , thereby developing a control signal for terminating the oscillation operation of the oscillation circuit OSC.

FIG. 7 shows a typical construction of the overcurrent detection circuit 4.

The voltage at the point a is applied to a series circuit of resistors R 10 and R 11 , and grounded. The collector electrode of a transistor Q 10 is connected to the connection point of the resistors R 10 and R 11 through resistors R 12 and R 13 . The emitter electrode of the transistor Q 10 is grounded. The base electrode of the transistor Q 10 is connected to the connection point of the resistor R 9 and the emitter electrode of the switching transistor Q 5 via a resistor R 14 .

When the switching transistor Q 5 is turned on, a current flows through the resistor R 9 . When the voltage drop across the resistor R 9 exceeds a predetermined value due to a large current, the transistor Q 10 is turned on to turn on the programmable unijunction transistor P 1 . That is, when a large current flows through the primary winding N 1 , the programmable unijunction transistor P 1 develops the control signal to terminate the oscillation operation of the oscillator circuit OSC.

The invention being thus described, it will be obvious that the same may be varied in many ways. Such variations are not to be regarded as a departure from the spirit and scope of the invention, and all such modifications are intended to be included within the scope of the following claims.

BU2

Silicon NPN

npn transistors,pnp transistors,transistors

Category: NPN Transistor, Transistor

MHz: <1 MHz

Amps: 5A

Volts: 1500V

HIGH VOLTAGE CAPABILITY

JEDEC TO-3 METAL CASE.

DESCRIPTION

The BU208A, BU508A and BU508AFI are

manufactured using Multiepitaxial Mesa

technology for cost-effective high performance

and use a Hollow Emitter structure to enhance

switching speeds.

APPLICATIONS:

* HORIZONTAL DEFLECTION FOR COLOUR TV With 110° or even 90° degree of deflection angle.

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

VCES Collector-Emit ter Voltage (VBE = 0) 1500 V

VCEO Collector-Emit ter Voltage (IB = 0) 700 V

VEBO Emitter-Base Voltage (IC = 0) 10 V

IC Collector Current 8 A

ICM Collector Peak Current (tp < 5 ms) 15 A

TO - 3 TO - 218 ISOWATT218

Ptot Total Dissipation at Tc = 25 oC 150 125 50 W

Tstg Storage Temperature -65 to 175 -65 to 150 -65 to 150 oC

Tj Max. Operating Junction Temperature 175 150 150 °C

GENERAL BASIC TRANSISTOR LINE OUTPUT STAGE OPERATION:

The basic essentials of a transistor line output stage are shown in Fig. 1(a). They comprise: a line output transformer which provides the d.c. feed to the line output transistor and serves mainly to generate the high -voltage pulse from which the e.h.t. is derived, and also in practice other supplies for various sections of the receiver; the line output transistor and its parallel efficiency diode which form a bidirectional switch; a tuning capacitor which resonates with the line output transformer primary winding and the scan coils to determine the flyback time; and the scan coils, with a series capacitor which provides a d.c. block and also serves to provide slight integration of the deflection current to compensate for the scan distortion that would otherwise be present due to the use of flat screen, wide deflection angle c.r.t.s. This basic circuit is widely used in small -screen portable receivers with little elaboration - some use a pnp output transistor however, with its collector connected to chassis.

Circuit Variations:

Variations to the basic circuit commonly found include: transposition of the scan coils and the correction capacitor; connection of the line output transformer primary winding and its e.h.t. overwinding in series; connection of the deflection components to a tap on the transformer to obtain correct matching of the components and conditions in the stage; use of a boost diode which operates in identical manner to the arrangement used in valve line output stages, thereby increasing the effective supply to the stage; omission of the efficiency diode where the stage is operated from an h.t. line, the collector -base junction of the line output transistor then providing the efficiency diode action without, in doing so, producing scan distortion; addition of inductors to provide linearity and width adjustment; use of a pair of series -connected line output transistors in some large -screen colour chassis; and in colour sets the addition of line convergence circuitry which is normally connected in series between the line scan coils and chassis. These variations on the basic circuit do not alter the basic mode of operation however.

Resonance

The most important fact to appreciate about the circuit is that when the transistor and diode are cut off during the flyback period - when the beam is being rapidly returned from the right-hand side of the screen to the left-hand side the tuning capacitor together with the scan coils and the primary winding of the line output transformer form a parallel resonant circuit: the equivalent circuit is shown in Fig. 1(b). The line output transformer primary winding and the tuning capacitor as drawn in Fig. 1(a) may look like a series tuned circuit, but from the signal point of view the end of the transformer primary winding connected to the power supply is earthy, giving the equivalent arrangement shown in Fig. 1(b).

The Flyback Period:

Since the operation of the circuit depends mainly upon what happens during the line flyback period, the simplest point at which to break into the scanning cycle is at the end of the forward scan, i.e. with the beam deflected to the right-hand side of the screen, see Fig. 2. At

this point the line output transistor is suddenly switched off by the

squarewave drive applied to its base. Prior to this action a linearly

increasing current has been flowing in the line output transformer

primary winding and the scan coils, and as a result magnetic fields have

been built up around these components. When the transistor is switched

off these fields collapse, maintaining a flow of current which rapidly

decays to zero and returns the beam to the centre of the screen. This

flow of current charges the tuning capacitor, and the voltage at A rises

to a high positive value - of the order of 1- 2k V in large -screen

sets, 200V in the case of mains/battery portable sets. The e

beam deflected to the right-hand side of the screen, see Fig. 2. At

this point the line output transistor is suddenly switched off by the

squarewave drive applied to its base. Prior to this action a linearly

increasing current has been flowing in the line output transformer

primary winding and the scan coils, and as a result magnetic fields have

been built up around these components. When the transistor is switched

off these fields collapse, maintaining a flow of current which rapidly

decays to zero and returns the beam to the centre of the screen. This

flow of current charges the tuning capacitor, and the voltage at A rises

to a high positive value - of the order of 1- 2k V in large -screen

sets, 200V in the case of mains/battery portable sets. The e nergy

in the circuit is now stored in the tuning capacitor which next

discharges, reversing the flow of current in the circuit with the result

that the beam is rapidly deflected to the left-hand side of the screen -

see Fig. 3. When the tuning capacitor has discharged, the voltage at A

has fallen to zero and the circuit energy is once more stored in the

form of magnetic fields around the inductive components. One half -cycle

of oscillation has occurred, and the flyback is complete.

nergy

in the circuit is now stored in the tuning capacitor which next

discharges, reversing the flow of current in the circuit with the result

that the beam is rapidly deflected to the left-hand side of the screen -

see Fig. 3. When the tuning capacitor has discharged, the voltage at A

has fallen to zero and the circuit energy is once more stored in the

form of magnetic fields around the inductive components. One half -cycle

of oscillation has occurred, and the flyback is complete.

Energy Recovery:

First Part of Forward Scan The circuit then tries to continue the cycle of oscillation, i.e. the magnetic fields again collapse, maintaining a current flow which this time would charge the tuning capacitor negatively (upper plate). When the voltage at A reaches about -0.6V however the efficiency diode becomes forward biased and switches on. This damps the circuit, preventing further oscillation, but the magnetic fields continue to collapse and in doing so produce a linearly decaying current flow which provides the first part of the forward s can,

the beam returning towards the centre of the screen - see Fig. 4. The

diode shorts out the tuning capacitor but the scan correction capacitor

charges during this period, its right-hand plate becoming positive with

respect to its left-hand plate, i.e. point A. Completion of Forward Scan

When the current falls to zero, the diode will switch off. Shortly

before this state of affairs is reached however the transistor is

switched on. In practice this is usually about a third of the way

through the scan. The squarewave applied to its base drives it rapidly

to saturation, clamping the vol

can,

the beam returning towards the centre of the screen - see Fig. 4. The

diode shorts out the tuning capacitor but the scan correction capacitor

charges during this period, its right-hand plate becoming positive with

respect to its left-hand plate, i.e. point A. Completion of Forward Scan

When the current falls to zero, the diode will switch off. Shortly

before this state of affairs is reached however the transistor is

switched on. In practice this is usually about a third of the way

through the scan. The squarewave applied to its base drives it rapidly

to saturation, clamping the vol tage

at point A at a small positive value - the collector emitter saturation

voltage of the transistor. Current now flows via the transistor and the

primary winding of the line output transformer, the scan correction

capacitor discharges, and the resultant flow of current in the line scan

coils drives the beam to the right-hand side of the screen see Fig. 5.

tage

at point A at a small positive value - the collector emitter saturation

voltage of the transistor. Current now flows via the transistor and the

primary winding of the line output transformer, the scan correction

capacitor discharges, and the resultant flow of current in the line scan

coils drives the beam to the right-hand side of the screen see Fig. 5.

Efficiency:

The transistor is then cut off again, to give the flyback, and the cycle of events recurs. The efficiency of the circuit is high since there is negligible resistance present. Energy is fed into the circuit in the form of the magnetic fields that build up when the output transistor is switched on. This action connects the line output transformer primary winding across the supply, and as a result a linearly increasing current flows through it. Since the width is

dependent on the supply voltage, this must be stabilised.

Harmonic Tuning:

There is another oscillatory action in the circuit during the flyback period. The considerable leakage inductance between the primary and the e.h.t. windings of the line output transformer, and the appreciable self -capacitance present, form a tuned circuit which is shocked into oscillation by the flyback pulse. Unless this oscillation is controlled, it will continue into and modulate the scan. The technique used to overcome this effect is to tune the leakage inductance and the associated capacitance to an odd harmonic of the line flyback oscillation frequency. By doing this the oscillatory actions present at the beginning of the scan cancel. Either third or fifth harmonic tuning is used. Third harmonic tuning also has the effect of increasing the amplitude of the e.h.t. pulse, and is generally used where a half -wave e.h.t. rectifier is employed. Fifth harmonic tuning results in a flat-topped e.h.t. pulse, giving improved e.h.t. regulation, and is generally used where an e.h.t. tripler is employed to produce the e.h.t. The tuning is mainly built into the line output transformer, though an external variable inductance is commonly found in colour chassis so that the tuning can be adjusted. With a following post I will go into the subject of modern TV line timebases in greater detail with other models and technology shown here at Obsolete Technology Tellye !

TELEFUNKEN CHASSIS 714A AMBIENT LIGHT RESPONSIVE CONTROL OF BRIGHTNESS, CONTRAST AND COLOR SATURATION

1. In a color television apparatus, a circuit for varying color display characteristics in accordance with variations in ambient light comprising: 2. In a color picture display system having a display device comprising: 3. The display system of claim 2 with kinescope means having a first set of electrodes and a second set of electrodes, 4. The display system of claim 2 with said light sensing means being responsive to the intensity of the ambient light and said parameter varying in accordance with the intensity of ambient light. 5. The display system of claim 4 with said modifying means increasing the gain of said luminance amplifying means at a greater rate than the gain of said chroma amplifying means as said ambient light intensity is increased. 6. A color television apparatus comprising: 7. In a color television receiver: 8. The receiver of claim 7 with said modifying means comprising a light dependent resistor means, 9. The receiver of claim 8 with second impedance means coupling said light dependent resistor means to said luminance gain means to control the gain of said luminance gain means. 10. The receiver of claim 9 with said second impedance means comprising a parallel combination of capacitance and resistance. 11. The receiver of claim 7 with said modifying means varying the gain of the luminance gain means at a greater rate than the gain of the chroma gain means as ambient light is varied. 12. The receiver of claim 7 with said modifying means being responsive to the intensity of ambient light and said parameter being varied as the intensity of the ambient light is varied. 13. The receiver of claim 7 with said modifying means attenuating the gain of said luminance amplifying means approximately fifty percent more than the gain of said chroma amplifying means, when the attenuation is measured in decibels, as said ambient light intensity is decreased. 14. In a color television receiver:

TELEFUNKEN CHASSIS 714A AMBIENT LIGHT RESPONSIVE CONTROL OF BRIGHTNESS, CONTRAST AND COLOR SATURATION Gain control arrangement useful in a television signal processing systemIn a color television receiver, first and second amplifiers are respectively included in the luminance and chrominance channels to permit control of contrast and saturation. The amplifiers have gain versus contr ol voltage characteristics including linear portions extrapolated to cut off at predetermined voltages which may or may not be the same. A first potentiometer is coupled between a source of fixed voltage equal to the extrapolated cut off voltage of the first amplifier and a gain controlling voltage source. The gain controlling voltage may be produced by a circuit including an element responsive to ambient light. The wiper of the first potentiometer is coupled to the first amplifier to couple a voltage developed at a predetermined point of the first potentiometer to the first amplifier to control its gain. A second potentiometer is coupled between a source of voltage equal to the extrapolated cut off voltage of the second amplifier and the gain controlling voltage source to receive a portion of the gain controlling voltage in accordance with the ratio of the extrapolated cut off voltages of the first and second amplifiers. The wiper of the second potentiometer is coupled to the second amplifier to couple a voltage developed at a predetermined point of the second potentiometer to the second amplifier to control its gain. In this manner, the contrast of the receiver may be varied over a relatively wide range while saturation is maintained substantially constant.

ol voltage characteristics including linear portions extrapolated to cut off at predetermined voltages which may or may not be the same. A first potentiometer is coupled between a source of fixed voltage equal to the extrapolated cut off voltage of the first amplifier and a gain controlling voltage source. The gain controlling voltage may be produced by a circuit including an element responsive to ambient light. The wiper of the first potentiometer is coupled to the first amplifier to couple a voltage developed at a predetermined point of the first potentiometer to the first amplifier to control its gain. A second potentiometer is coupled between a source of voltage equal to the extrapolated cut off voltage of the second amplifier and the gain controlling voltage source to receive a portion of the gain controlling voltage in accordance with the ratio of the extrapolated cut off voltages of the first and second amplifiers. The wiper of the second potentiometer is coupled to the second amplifier to couple a voltage developed at a predetermined point of the second potentiometer to the second amplifier to control its gain. In this manner, the contrast of the receiver may be varied over a relatively wide range while saturation is maintained substantially constant.

1. In a color television signal processing system of the type including luminance and chrominance signal processing channels, apparatus comprising:

first and second amplifiers respectively included in said luminance and chrominance channels, said amplifiers having gain versus control voltage characteristics including linear portions extrapolated to cut-off at predetermined voltages which may or may not be the same voltage;

a gain controlling voltage source;

means for coupling said gain controlling voltage to said first amplifier to control its gain;

potentiometer means coupled between a fixed voltage substantially equal to the extrapolated cut-off voltage of said second amplifier and to said gain controlling voltage source to recieve a portion of said gain controlling voltage in accordance with the ratio of the extrapolated cut-off voltages of said first and second amplifiers; and

means for coupling a voltage developed at a predetermined point on said potentiometer means to said second amplifier to control its gain.

2. The apparatus recited in claim 1 wherein said means for coupling said gain controlling voltage to said first amplifier includes another potentiometer coupled between a source of fixed voltage substantially equal to the extrapolated cut-off voltage of said first amplifier and said gain controlling voltage source. 3. In a color television signal processing system of the type including luminance and chrominance signal processing channels, apparatus comprising:

first and second amplifiers respectively included in said luminance and chrominance channels, said amplifiers having gain control voltage characteristics including linear portions extrapolated to cut-off at substantially the same predetermined voltage;

a source of gain controlling voltage; and

means for coupling said gain controlling voltage to said first and second amplifiers.

4 . Apparatus comprising:

. Apparatus comprising:

first variable gain amplifying means for amplifying a first signal in response to a first DC control signal, said first amplifying means having a first gain versus DC control voltage characteristic including a linear region, said linear region having a gain substantially equal to 0 at a DC control voltage equal to VO ;

second variable gain amplifying means for amplifying a second signal in response to a second DC control signal, said second amplifying means having a second gain versus DC control voltage characteristic including a linear region, said linear region having a gain substantially equal to 0 at a DC control voltage equal to AVO, where A is a number greater than 0;

a first source of fixed voltage substantially equal to VO ;

a second source of fixed voltage substantially equal to AVO ;

means for developing a third DC control voltage v;

means for developing a portion Av of said third control voltage v;

first means for deriving said first control voltage including means for providing the difference between said third control voltage v and said fixed voltage VO and means for adding a predetermined portion of the difference between said third control voltage v and said fixed voltage VO to said DC control voltage v; and

second means for deriving said second control voltage including means for providing the difference between a portion Av of said third control voltage v and said fixed voltage AVO and means for adding a predetermined portion of the difference between said portion Av and said fixed voltage AVO to said DC control voltage v.

5. The apparatus recited in claim 4 wherein A is equal to 1. 6. The apparatus recited in claim 4 wherein said first amplifying means is included in a luminance channel of a televeision signal processing system and said second amplifying means is included in a chrominance channel of said television signal processing system. 7. The apparatus recited in claim 6 wherein means for developing said third control voltage includes means responsive to ambient light. 8. The apparatus recited in claim 4 wherein said first means includes first voltage divider means coupled between said fixed voltage VO and said third DC control voltage v; and wherein said second means includes second voltage divider means coupled between said fixed voltage AVO and said portion Av. 9. The apparatus recited in claim 8 wherein said first voltage divider means includes a first potentiometer, said first potentiometer having a wiper coupled to said first amplifying means; and wherein said second voltage divider means includes a second potentiometer, said second potentiometer having a wiper coupled to said amplifying means. 10. The apparatus recited in claim 4 wherein said second gain versus DC control voltage characteristic includes a region between said voltage AVO and a voltage VB where the gain is greater than 0, said voltage VB being substantially equal to the voltage at which said second amplifying means has a gain substantially equal to 0; and wherein said second source of fixed voltage includes means for coupling said voltage VB to said second amplifying means. 11. The apparatus recited in claim 10 wherein said second source of said voltage AVO includes a third source of fixed voltage VB ; potentiometer means coupled between said third source of fixed voltage VB and said means for developing said third DC control voltage; and means coupled to said potentiometer means for developing said voltage AVO at a point along said potentiometer means; said potentiometer means including a wiper coupled to said second amplifier means, said wiper being adjustable to couple a DC voltage VFB and said third control voltage to said second amplifying means.

The present invention relates to a power supply voltage stabilizer and, more particularly, to a power supply voltage stabilizer employing a switching system for controlling power supply to a transformer included in the power supply voltage stabilizer.

In the conventional power supply voltage stabilizer employing a switching system for controlling power supply to a transformer included in the power supply voltage stabilizer, there is a possibility that an abnormal overvoltage will be developed from an output terminal thereof and/or an abnormal overcurrent may flow through the primary winding of the transformer.

Accordingly, an object of the present invention is to provide a protection means for protecting the power supply voltage stabilizer from an abnormal overvoltage and/or overcurrent.

Another object of the present invention is to provide a detection means for detecting an impending overvoltage and/or overcurrent occurring within the power supply voltage stabilizer.

Other objects and further scope of applicability of the present invention will become apparent from the detailed description given hereinafter. It should be understood, however, that the detailed description and specific examples, while indicating preferred embodiments of the invention, are given by way of illustration only, since various changes and modifications within the spirit and scope of the invention will become apparent to those skilled in the art from this detailed description.

The

power supply voltage stabilizer of the present invention mainly comprises a transformer including a primary winding connected to a commercial power source through a rectifying circuit, a secondary winding for output purposes, and an auxiliary winding. A driver circuit including a switching means is connected to the primary winding for controlling the power supply to the primary winding. An oscillator circuit is associated with the switching means to control ON/OFF operation of the switching means, thereby controlling the power supply to the primary winding.

To achieve the above objects, pursuant to an embodiment of the present invention, an overvoltage detection circuit is connected to the auxiliary winding. The overvoltage detection circuit functions to compare a voltage created in the auxiliary winding with the rectified power supply voltage, and develop a control signal, when an impending overvoltage is detected, for terminating operation of the oscillator circuit, thereby precluding power supply to the primary winding.

In another embodiment of the present invention, an overcurrent detection circuit is provided for detecting an impending overcurrent flowing through the primary winding to develop a control signal for terminating operation of the oscillator circuit.

BRIEF DESCRIPTION OF THE DRAWINGS

The present invention will become more fully understood from the detailed description given hereinbelow and the accompanying drawings, which are given by way of illustration only, and thus are not limitative of the present invention and wherein:

FIG. 1 is a circuit diagram of a basic construction of a power supply voltage stabilizer of the present invention;

FIG. 2 is a block diagram of an embodiment of a power supply voltage stabilizer of the present invention, which includes an oscillator circuit and an over voltage detection circuit;

FIG. 3 is a circuit diagram of an embodiment of the overvoltage detection circuit included in the power supply voltage stabilizer of FIG. 2;

FIG. 4 is a circuit diagram of an embodiment of the oscillator circuit included in the power supply voltage stabilizer of FIG. 2;

FIG. 5 is a waveform chart for explaining operation of the oscillator circuit of FIG. 4;

FIG. 6 is a block diagram of another embodiment of a power supply voltage stabilizer of the present invention, which includes an oscillator circuit and an overcurrent detection circuit; and

FIG. 7 is a circuit diagram of an embodiment of the overcurrent detection circuit included in the power supply voltage stabilizer of FIG. 6.

DESCRIPTION OF THE PREFERRED EMBODIMENTS

R

eferring now in detail to the drawings, and to facilitate a more complete understanding of the present invention, a basic construction of a power supply voltage stabilizer of the present invention will be first described with reference to FIG. 1.