The PANASONIC CHASSIS Z5 is a monocarrier based mainly around the PHILIPS TDA8361.

Aside the classic number of dry joint around the chassis it was reliable and durable offering great features for an analog 21 Inches color set.

Sometimes the power supply which is sligtly complex was difficult to repair unless getting original parts from PANASONIC.

Panasonic Z5 chassis was introduced in 1993 as a lower - cost replacement for the Z4 chassis in small -screen, monophonic sound sets. Whereas the Z4 had been designed to drive the more expensive Invar-mask FST picture tubes, the Z5 can drive cheaper iron -mask non-FST displays. The chassis was mainly developed by Panasonic's Cardiff design team. It employs a significant feature that's new for a non -Japanese Panasonic chassis, a 'hot' line output stage. This, in conjunction with a 'cold' field deflection circuit, means that an isolation split is required in the yoke. In fact the chopper, line driver and output transformers and the scan coils all have to provide mains isolation. Thus while the line scan circuit is hot, the EHT system and the field scan circuit remain cold. Obviously the picture tube, or at least the deflection coils, can't be replaced with a conventional non -isolated type. Other innovations include a linear transformerless remote -control standby circuit and a simple teletext option mounted on a small subpanel. This features four -page text storage with both FLOF and TOP text. Initially only 21in. models were equipped with CATS (Contrast Auto Tracking System), an automatic contrast control system that employs a light -dependent resistor to sense the ambient light level. This feature was subsequently added to all UK models. The rather exotic on -screen calendar/calculator/`mood light' used in the Z4 chassis was dropped however. A single AV input is provided, via both scart and phono sockets, with no S video connector. Unlike the Z4, NTSC playback is not possible, though continental variants have Secam and modified NTSC facilities. The scart connector does allow for external RGB signal display however, and has a tuner AV output. The non -text TC14S1R and TC21S1R and the text TX14S1T and TX21S1T are amongst the more popular models fitted with the chassis. Some models with cosmetic variations have been added - the S2R and S2T versions. There are also cabinet colour variants. Some sets are fitted with Philips tubes (suffix /B) while others have Thomson types (suffix /BH). Layout and Access From the servicing point of view the most obvious improvement in the Z5 compared with the Z4 is the reduced number of PCBs. There are usually only two, the main panel E and the CRT base panel Y. When added, the text board T is a daughter board that's soldered directly into panel E. This is the first Panasonic chassis to have so few interconnecting leads! The circuitry is arranged as follows: Panel E contains the power supply, the tuner, the IF, vision and sound processing stages, the sync and timebase circuitry, the audio output chip, the microcontroller chip and its associated devices and the AV connectors. Panel Y contains the RGB output stages and CRT base. Option panel T contains the teletext decoder and an RGB switch. Option panel A contains a Secam L decoder (for French models only).

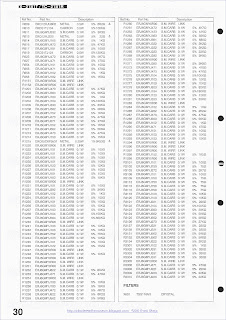

Fig. 1 shows the general layout. Service access is very good. Simply remove the back cover screws and a front panel retaining screw near the AV connector. Panel E can then be gently pulled up and back. As usual with Panasonic models a 'service position' is provided: panel E can be clipped to the inside vertical side of the cabinet. The set can be operated normally in this condition, with access to both sides of the main PCB. IC Complement The accompanying table lists the ICs used in the chassis. The mixture of European and Japanese devices reflects the origins of different parts of the design. There are various differences with continental models, as follows. The TDA3843 in position IC201 is an additional sound IF chip for Secam L and L' sets (French models), which also have a 4053 CMOS switch (IC202). IC601 is type TDA8362 and IC602 type TDA4662 to provide multistandard operation.

Fig. 1 shows the general layout. Service access is very good. Simply remove the back cover screws and a front panel retaining screw near the AV connector. Panel E can then be gently pulled up and back. As usual with Panasonic models a 'service position' is provided: panel E can be clipped to the inside vertical side of the cabinet. The set can be operated normally in this condition, with access to both sides of the main PCB. IC Complement The accompanying table lists the ICs used in the chassis. The mixture of European and Japanese devices reflects the origins of different parts of the design. There are various differences with continental models, as follows. The TDA3843 in position IC201 is an additional sound IF chip for Secam L and L' sets (French models), which also have a 4053 CMOS switch (IC202). IC601 is type TDA8362 and IC602 type TDA4662 to provide multistandard operation.On panel E IC251 IC451 IC601 AN5265 TDA3653C TDA8361 IC602 TDA4661V2 IC801 STR5 1 203M STR51224M IC851 AN78M05LB I IC852 AN78M12LB1 IC1202 MN152811XXX IC1203 MN128OR IC 1204 RPM637CBRS IC1205 ST24CO2CB I On panel T IC3501 IC3502 IC3504 IC3505 CF72306 CF70205ANW LA7222TV AN5862K Audio amplifier Field driver and output IF, colour decoder, RGB switching, timebase generators Chroma delay line Chopper (14in. models) Chopper (21 in. models) 5V regulator 12V regulator Microcontroller (suffix depends on model) Reset Remote control receiver EEROM Video data slicer Text decoder AV switch RGB switch.

IC603, type TDA8395, is a Secam chroma delay line used in French models. The text decoder 1C3502 is type CF70204NW for Central and Eastern Europe, type CF70209NW for Russian and type CF70210NW for Hebrew.

CIRCUITS DESCRIPTIONS:

The CHASSIS Z5 Power Supply The chopper power supply, which operates in synchronism with the line timebase, uses a new Sanken chip. Fig. 2 shows the circuitry on the primary side. A feature of the design is that when the microcontroller chip switches the set to standby the power supply doesn't stop, as with many designs. Instead, its duty cycle is reduced until the output is just sufficient to run the control system but not the other parts of the set. There is thus no need for an extra standby power supply transformer. This has two advantages, reduced cost and lower power consumption in the standby mode. The power supply has two distinct operating modes therefore, standby and full operation. We'll look at each in turn. Standby Mode After passing via the usual fuse, filter and on/off switch the AC mains input is presented to the bridge rectifier D801-4 which charges its reservoir capacitor C807. Approximately 300V DC is developed across this capacitor and is fed via the primary winding (P1-2) on the chopper transformer T801 to the collector of transistor Q1 in the chopper chip IC801 (pin 3). Q1 's base (pin 2) receives a small start-up bias via R818, R802 and L804. As a result it conducts and a voltage appears at pin 4 of the chip. This is fed to the +B2 line via R828. It appears at the collector of the standby switching transistor Q803 via D810 and R812. The standby command optocoupler D813 is off, and Q803' s base is forward biased via R813 and R821. Q803 is thus switched on, and the +B2 voltage is held at typically 1V. The current flowing in T801's primary winding produces a reverse current in winding B1-2. D811 rectifies the voltage at pin B1, charging C813 whose positive terminal is connected to the +B2 link C813's negative terminal will be at approximately -2V. As a result Q804 and in turn zener diode D817 conduct, clamping the DC voltage at pin 2 of IC801 ataround 1V. Chopper transistor Q1 is therefore prevented from being switched to full on. Because of the feedback via D816 and R803, the circuit oscillates. This is the stable standby state. In the standby mode T801 produces, via rectifier D851 with its reservoir capacitor C852, about 12V on the +B4 rail. The 5V regulator IC851 produces the +B10 supply for the microcontroller chip IC1202. Fig. 3 shows, somewhat simplified, the secondary side of the chopper power supply circuit. Note that in standby the microcontroller's power on/off output signal is also used to switch off Q851 so that there's no voltage on the +B9 rail. Otherwise the +B4 and +B9 rails would be linked. This prevents the IF/colour decoder/timebase generator chip IC601 being powered. Operating Mode When the microcontroller issues a power on command, Q851 and the optocoupler D813 switch on. With D813 conductive, the voltage at the base of Q803 falls to zero and it switches off. The rise in its collector voltage triggers thyristor D820, which switches on. C814 is now able to charge from the 300V supply via R811, R819 and R810. In addition, with D820 conductive the charge (around 90V) developed across C818 in the standby mode is available on the +B2 rail, which is used to power the line output tranistor - both are on the hot side of the circuitry. With Q851 switched on IC601, which contains the line generator, can come into operation. The line timebase starts up, producing flyback pulses. These are coupled via R806 and D809 to pin 2 of IC801, i.e. the base of the chopper transistor Q 1. This pulse feed does not require isolation, as it comes from the hot side of the line output transformer. As the +B2 voltage rises, so the voltage at the negative low terminal of C813 becomes positive and Q804 switches off. Q2 in IC801 is also switched off, enab

The CHASSIS Z5 Power Supply The chopper power supply, which operates in synchronism with the line timebase, uses a new Sanken chip. Fig. 2 shows the circuitry on the primary side. A feature of the design is that when the microcontroller chip switches the set to standby the power supply doesn't stop, as with many designs. Instead, its duty cycle is reduced until the output is just sufficient to run the control system but not the other parts of the set. There is thus no need for an extra standby power supply transformer. This has two advantages, reduced cost and lower power consumption in the standby mode. The power supply has two distinct operating modes therefore, standby and full operation. We'll look at each in turn. Standby Mode After passing via the usual fuse, filter and on/off switch the AC mains input is presented to the bridge rectifier D801-4 which charges its reservoir capacitor C807. Approximately 300V DC is developed across this capacitor and is fed via the primary winding (P1-2) on the chopper transformer T801 to the collector of transistor Q1 in the chopper chip IC801 (pin 3). Q1 's base (pin 2) receives a small start-up bias via R818, R802 and L804. As a result it conducts and a voltage appears at pin 4 of the chip. This is fed to the +B2 line via R828. It appears at the collector of the standby switching transistor Q803 via D810 and R812. The standby command optocoupler D813 is off, and Q803' s base is forward biased via R813 and R821. Q803 is thus switched on, and the +B2 voltage is held at typically 1V. The current flowing in T801's primary winding produces a reverse current in winding B1-2. D811 rectifies the voltage at pin B1, charging C813 whose positive terminal is connected to the +B2 link C813's negative terminal will be at approximately -2V. As a result Q804 and in turn zener diode D817 conduct, clamping the DC voltage at pin 2 of IC801 ataround 1V. Chopper transistor Q1 is therefore prevented from being switched to full on. Because of the feedback via D816 and R803, the circuit oscillates. This is the stable standby state. In the standby mode T801 produces, via rectifier D851 with its reservoir capacitor C852, about 12V on the +B4 rail. The 5V regulator IC851 produces the +B10 supply for the microcontroller chip IC1202. Fig. 3 shows, somewhat simplified, the secondary side of the chopper power supply circuit. Note that in standby the microcontroller's power on/off output signal is also used to switch off Q851 so that there's no voltage on the +B9 rail. Otherwise the +B4 and +B9 rails would be linked. This prevents the IF/colour decoder/timebase generator chip IC601 being powered. Operating Mode When the microcontroller issues a power on command, Q851 and the optocoupler D813 switch on. With D813 conductive, the voltage at the base of Q803 falls to zero and it switches off. The rise in its collector voltage triggers thyristor D820, which switches on. C814 is now able to charge from the 300V supply via R811, R819 and R810. In addition, with D820 conductive the charge (around 90V) developed across C818 in the standby mode is available on the +B2 rail, which is used to power the line output tranistor - both are on the hot side of the circuitry. With Q851 switched on IC601, which contains the line generator, can come into operation. The line timebase starts up, producing flyback pulses. These are coupled via R806 and D809 to pin 2 of IC801, i.e. the base of the chopper transistor Q 1. This pulse feed does not require isolation, as it comes from the hot side of the line output transformer. As the +B2 voltage rises, so the voltage at the negative low terminal of C813 becomes positive and Q804 switches off. Q2 in IC801 is also switched off, enab ling Q1 to be triggered by the line pulses at its base. It is now able to switch on fully, driven by the feedback to its base via D816, R803 and L804. When it saturates, the voltage across winding B1-2 falls and Q1 then switches off until the next line pulse appears. The power supply and the line timebase thus operate synchronously. The efficiency of the power supply is increased by charging C814 via D806 and D820 when Q1 switches off. Q3 adjusts the DC conditions at the base of Q1 to provide regulation. Q805 provides excess current protection by sensing the voltage developed across R828. It switches on under excess -current conditions to remove the drive to Q 1 . D808 provides overvoltage protection. The chopper power supply provides several outputs. Others are derived from the line output transformer. Most vary depending on whether the set is in the standby or operational condition. They are listed in the accompanying table.

ling Q1 to be triggered by the line pulses at its base. It is now able to switch on fully, driven by the feedback to its base via D816, R803 and L804. When it saturates, the voltage across winding B1-2 falls and Q1 then switches off until the next line pulse appears. The power supply and the line timebase thus operate synchronously. The efficiency of the power supply is increased by charging C814 via D806 and D820 when Q1 switches off. Q3 adjusts the DC conditions at the base of Q1 to provide regulation. Q805 provides excess current protection by sensing the voltage developed across R828. It switches on under excess -current conditions to remove the drive to Q 1 . D808 provides overvoltage protection. The chopper power supply provides several outputs. Others are derived from the line output transformer. Most vary depending on whether the set is in the standby or operational condition. They are listed in the accompanying table. The CHASSIS Z5 Microcontroller As in all current Panasonic models the microcontroller chip IC1202 is a Matsushita device. It has 42 pins and contains 8K of ROM. Other features include frequency - synthesis tuning, two resistive keyboard scan inputs, a contrast sensor input, 50/60Hz detection and switching, an on -screen display character generator, AV switch control, seven pulse -width modulated control outputs, a self -test mode and I2C bus operation.The use of presettable option pins enables the chip to be set up for text/non-text or UK/continental operation. Associated devices in the control system are as follows: IC1205, a serial EEROM for storage of the customer settings; the reset generator IC1203; and the remote control receiver IC1204. Fig. 4 shows the basic arrangement. IC1202' s pin functions are listed in the accompanying table. Note that several functions, particularly those related to multi -standard operation, are not used in UK sets. Most of the pins have a 470pF capacitor connected to chassis to provide antistatic protection. These are not shown in the accompanying diagrams. Some pins may or may not be connected to external circuitry depending on the options in use. Even when connected, some operations function with only certain models. Pins 2 and 12 for example are used with French sets, while pin 41 was initially used with 21in. models only. Pins 3 and 40 are always connected to chassis, as the Z5 chassis does not provide NTSC colour reception or S video operation. Pins 29 and 33 are left open -circuit, as only green OSD charact

ers are displayed. All models now use the scart slow -switch feature (pin 39). Pins 20 and 21 have dual functions. They operate as keyscan inputs able to sense the value of a resistor or a push-button selected resistor ladder. The residual resistance, when no button is depressed, sets the option mode. As these models have only five user control buttons (TV/AV, up, down, function and store), only keyscan 1 is used. Use is made of both option 1 and 2 however. The on -board keys are all connected to the resistor ladder. When a button is pressed, a different resistance value and thus voltage at pin 21 is selected. The last resistor in the chain (R1215) is fitted only in teletext models, its presence confirming that a text decoder is fitted (option 1). The keyscan 2/option 2 input is used to tell IC1202 in which area the set is to be used. This enables the micro to set the correct channel numbers and select the required frequency bands. The values of R1212/3 set the voltage at pin 20: 5V is the UK mode, 2.7V indicates French use and less than 1V continental use. Self Test and the EEROM A useful feature is the microcontroller chip's self -test mode. Access to this is obtained by reducing the colour and sharpness settings to minimum then simultaneously

ers are displayed. All models now use the scart slow -switch feature (pin 39). Pins 20 and 21 have dual functions. They operate as keyscan inputs able to sense the value of a resistor or a push-button selected resistor ladder. The residual resistance, when no button is depressed, sets the option mode. As these models have only five user control buttons (TV/AV, up, down, function and store), only keyscan 1 is used. Use is made of both option 1 and 2 however. The on -board keys are all connected to the resistor ladder. When a button is pressed, a different resistance value and thus voltage at pin 21 is selected. The last resistor in the chain (R1215) is fitted only in teletext models, its presence confirming that a text decoder is fitted (option 1). The keyscan 2/option 2 input is used to tell IC1202 in which area the set is to be used. This enables the micro to set the correct channel numbers and select the required frequency bands. The values of R1212/3 set the voltage at pin 20: 5V is the UK mode, 2.7V indicates French use and less than 1V continental use. Self Test and the EEROM A useful feature is the microcontroller chip's self -test mode. Access to this is obtained by reducing the colour and sharpness settings to minimum then simultaneously pressing the set's function button and the remote control unit's off -timer button. This should produce the result CHECK 1+ 2- 3+, representing the tuner, the text processor and the EEROM respectively. If any check fails, there will be a minus instead of a plus symbol. Non- text models will of course show 1+ 2- 3+ when operating correctly. A second row of self -test display digits indicates the settings of options 1-6. A typical display is 11 47 46. Options 1 and 2 are, as previously mentioned,set by hardware. Options 3-6 can be selected from the self-test screen. Most of these options will not operate if the respective hardware is not fitted. They enable the text, tuning and audio options to be changed, as wellas turning the CATS system on or off. The numbers displayedare decimal values that correspond with six data bits which define each option, including some extra option 1 and 2 bits that are not accessible by means of hardware changes. These values are stored in the EEROM. Further information can be found in the Panasonic Z5 Technical Guide. The EEROM also stores user information, defining the 50 -channel programme memory, AFC offset and, with non -UK models, the colour system and subcarrier settings. It also retains a 'last memory' of theuser control settings. This includes the programme number, all the DAC settings and the last CATS eye value. Analogue Controls The analogue control outputs are all provided by 64-step pulse -width modulated output drivers within IC1202. A large mark -space ratio output represents the maximum level, a small mark -space ratio the minimum level. Digital to analogue conversion is achieved by filtering the outputs. As each output is a DC control level, preset levels (such as the factory sub -colour setting) can be obtained by adding a preset potentiometer across the output. The contrast PWM output at pin 13 is mixed with a control voltage obtained from the CATS circuit. A potential divider network is used to add voltages, a light - dependent resistor forming the bottom section. This item is fitted just behind the set's front panel. Variations in the ambient light level and the CATS sensitivity setting (pin 41, IC1202) alter the voltage at the base of Q1210 and thus its conduction. As the conduction of Q1210 increases, the contrast control voltage falls. There is also a small effect on the brightness, via R1254 and R321. Pin 41 of IC1202 can be set at chassis potential,open - circuit or high. This changes the CATS sensitivity to off, medium and high respectively. On -screen Display and RGB Switching The Z5 chassis uses a simplified on -screen display system. Green OSD signals from pin 32 of IC1202 and composite blanking from pin 31 are buffered by emitter- followers and then mixed directly with the RGB outputs from IC601 as they pass to the output stages on the tube's base panel. In text sets the external RGB inputs from the scart socket go to panel T, where IC3505 carries out text/AV RGB selection. Fig. 5 shows this. The selected signals go to IC601 on panel E, where they or the video/OSD RGB signals are selected. Jumper leads to bypass panel T are used for the external RGB inputs in non -text models. AV Switching Pin 10 of IC1202 sets the mode to TV or AV while pin 9 sets to text or normal. In text equipped sets, external video SIP from T201 5 6 SIF External audio AV TV 15 13 Part IC501 Audio Video Video polarity select from the scart connector or the phono socket and demodulated video from IC601 leave the E panel andpass to the video switching chip IC3504 on panel T. Pin 4 of this device receives the mode select signal from IC1202, low for TV (normal) or high for external AV. A further switch in IC3504 is used to select either the output from the first switch or teletext sync pulses from the text processor chip. The selected signals are buffered on panel T after which they return to panel E where theyare fed to pins 13 and 15 of IC601. These pins are the inputs ofan internal video mode switch which is not used in text equipped models. Audio signals are switched within IC601, also under the control of IC1202. IC601 has an internal sound IF filter, so it can accept either the audio from the W circuit or external (baseband) audio. Fig. 6 shows the AV switching arrangement. Innon -text models without panel T the external and internal videogo straight to IC601 for selection, via jumper links JEK and JEL respectively. Audio selection remains as in the text models. French models have an additional control signal from pin 12 of IC1202. This is used to invert the video polarity when system L signals with positive video modulationare received. Standby Control IC1202 sets the receiver to standby by producing a low level output at pin 24 - see Fig. 3. This switches off Q1203, preventing current flow in optocoupler D813. Q803 is thus able to conduct, as previously described. Q1203 also switches Q851 off, via Q853, isolating the 8V line - again as described earlier. The standby status is indicated by D1203, which is driven by pin 5 of IC1202 via Q1202 and the optocoupler D822. In the standby mode pin 5 is high so D1203, Q1202 and D822 are all conductive. In normal operation pin 5 of IC1202 is low and the standby LED D1203 is off. When a remote control command is received, the output from pin 5 is modulated. The standby LED thus flickers. If the mains power is disconnected or the set is switched off, the microcontroller's 5V supply continues for a few seconds. Optocoupler D822 is in thiscase used to break the circuit to the LED so that it goes out immediately.

Microcontroller Pin Functions Pin Function 1 5V supply 22 Field pulse for OSD sync 2 Mute 2 input (from sync) 23 Volume control output (PWM) 3 Tint mode select (NTSC only) 24 On/standby output 4 Mute 1 input (from VIF) 25 Factory test pin 5 Standby/remote LED drive 26 50/60Hz detect (field pulse input) 6 50/60Hz select 27 Video mute output 7 Reset input 28 NTSC tint control output (PWM) 8 Subcarrier select (Secam/Zwietone) 29 OSD blue output 9 TV/text select 30 Line sync pulse input 10 AV1 select 31 OSD blanking output 11 AV2 select 32 OSD green output 12 Video polarity select (Secam) 33 OSD red output 13 Contrast control output (PWM) 34 Remote control data input 14 Sharpness control output (PWM) 35 Crystal osc. 2 15 Colour control output (PWM) 36 Crystal osc. 1 16 Brightness control output (PWM) 37 I2C bus clock in/out 17 RGB, mode select 38 I2C data bus in/out 18 AFC input 39 Scarf slow switch input 19 Mute 1 input 40 S video select output 20 Keyscan 2/option 2 41 CATS sensitivity 21 Keyscan 1/option 1 42 Chassis

TDA8361 Integrated PAL and PAL/NTSC TV processor

FEATURES

Available in TDA8360, TDA8361

and TDA8362

· Vision IF amplifier with high

sensitivity and good differential

gain and phase

· Multistandard FM sound

demodulator (4.5 MHz to 6.5 MHz)

· Integrated chrominance trap and

bandpass filters (automatically

calibrated)

· Integrated luminance delay line

· RGB control circuit with linear RGB

inputs and fast blanking

· Horizontal synchronization with two

control loops and alignment-free

horizontal oscillator without

external components

· Vertical count-down circuit

(50/60 Hz) and vertical preamplifier

· Low dissipation (700 mW)

· Small amount of peripheral

components compared with

competition ICs

· Only one adjustment (vision IF

demodulator)

· The supply voltage for the ICs is

8 V. They are mounted in a shrink

DIL envelope with 52 pins and are

pin compatible.

Additional features

TDA8360

· Alignment-free PAL colour decoder

for all PAL standards, including

PAL-N and PAL-M.

TDA8361

· PAL/NTSC colour decoder with

automatic search system

· Source selection for external

audio/video (A/V) inputs (separate

Y/C signals can also be applied).

TDA8362

· Multistandard vision IF circuit

(positive and negative modulation)

· PAL/NTSC colour decoder with

automatic search system

· Source selection for external

A/V inputs (separate Y/C signals

can also be applied)

· Easy interfacing with the TDA8395

(SECAM decoder) for

multistandard applications.

GENERAL DESCR

IPTION

IPTIONThe TDA8360, TDA8361 and

TDA8362 are single-chip TV

processors which contain nearly all

small signal functions that are

required for a colour television

receiver. For a complete receiver the

following circuits need to be added:

a base-band delay line (TDA4661),

a tuner and output stages for audio,

video and horizontal and vertical

deflection.

Because of the different functional

contents of the ICs the set maker can

make the optimum choice depending

on the requirements for the receiver.

The TDA8360 is intended for simple

PAL receivers (all PAL standards,

including PAL-N and PAL-M are

possible).

The TDA8361 contains a PAL/NTSC

decoder and has an A/V switch.

For real multistandard applications

the TDA8362 is available. In addition

to the extra functions which are

available in the TDA8361, the

TDA8362 can handle signals with

positive modulation and it supplies

the signals which are required for the

SECAM decoder TDA8395.

TDA8361

The TDA8361 has the following

differences to the pinning:

Pin 1: only audio de-emphasis

Pin 27: only hue control

Pin 32: 4.43 MHz output for TDA8395

is not connected.

FUNCTIONAL DESCRIPTION

Video IF amplifier

The IF amplifier contains

3 AC-coupled control stages with a

total gain control range of greater

than 60 dB. The sensitivity of the

circuit is comparable with that of

modern IF ICs.

The reference carrier for the video

demodulator is obtained by means of

passive regeneration of the picture

carrier. The external reference tuned

circuit is the only remaining

adjustment of the IC.

In the TDA8362 the polarity of the

demodulator can be switched so that

the circuit is suitable for both positive

and negative modulated signals.

The AFC circuit is driven with the

same reference signal as the video

demodulator. To ensure that the

video content does not disturb the

AFC operation a sample-and-hold

circuit is incorporated; the capacitor

for this function is internal. The AFC

output voltage is 6 V.

The AGC detector operates on levels,

top sync for negative modulated and

top white for positive modulated

signals.The AGC detector time

constant capacitor is connected

externally. This is mainly because of

the flexibility of the application.

The time constant of the AGC system

during positive modulation

(TDA8362) is slow, this is to avoid any

visible picture variations. This,

however, causes the system to react

very slowly to sudden changes in the

input signal amplitude.

To overcome this problem a speed-up

circuit has been included which

detects whether the AGC detector is

activated every frame period. If,

during a 3-frame period, no action is

detected the speed of the system is

increased. When the incoming signal

has no peak white information (e.g.

test lines in the vertical retrace period)

the gain would be video signal

dependent. To avoid this effect the

circuit also contains a black level

AGC detector which is activated when

the black level of the video signal

exceeds a certain level.

The TDA8361 and TDA8362 contain

a video identification circuit which is

independent of the synchronization

circuit. Therefore search tuning is

possible when the display section of

the receiver is used as a monitor. In

the TDA8360 this circuit is only used

for stable OSD at no signal input. In

the normal television mode the

identification output is connected to

the coincidence detector, this applies

to all three devices. The identification

output voltage is LOW when no

transmitter is identified. In this

condition the sound demodulator is

switched off (mute function). When a

transmitter is identified the output

voltage is HIGH. The voltage level is

dependen

t on the frequency of the

t on the frequency of theincoming chrominance signal.

Sound circuit

The sound bandpass and trap filters

have to be connected externally. The

filtered intercarrier signal is fed to a

limiter circuit and is demodulated by

means of a PLL demodulator. The

PLL circuit tunes itself automatically

to the incoming signal, consequently,

no adjustment is required.

The volume is DC controlled. The

composite audio output signal has an

amplitude of 700 mV RMS at a

volume control setting of -6 dB. The

de-emphasis capacitor has to be

connected externally. The

non-controlled audio signal can be

obtained from this pin via a buffer

stage. The amplitude of this signal is

350 mV RMS.

The TDA8361 and TDA8362 external

audio input signal must have an

amplitude of 350 mV RMS. The

audio/video switch is controlled via

the chrominance input pin.

Synchronization circuit

The sync separator is preceded by a

voltage controlled amplifier which

adjusts the sync pulse amplitude to a

fixed level. The sync pulses are then

fed to the slicing stage (separator)

which operates at 50% of the

amplitude.

The separated sync pulses are fed to

the first phase detector and to the

coincidence detector. The

coincidence detector is used for

transmitter identification and to detect

whether the line oscillator is

synchronized. When the circuit is not

synchronized the voltage on the

peaking control pin (pin 14) is LOW

so that this condition can be detected

externally. The first PLL has a very

high static steepness, this ensures

that the phase of the picture is

independent of the line frequency.

The line oscillator operates at twice

the line frequency.

The oscillator network is internal.

Because of the spread of internal

components an automatic adjustment

circuit has been added to the IC.

The circuit compares the oscillator

frequency with that of the crystal

oscillator in the colour decoder. This

results in a free-running frequency

which deviates less than 2% from the

typical value.

The circuit employs a second control

loop to generate the drive pulses for

the horizontal driver stage.

X-ray protection can be realised by

switching the pin of the second

control loop to the positive supply line.

The detection circuit must be

connected externally. When the X-ray

protection is active the horizontal

output voltage is switched to a high

level. When the voltage on this pin

returns to its normal level the

horizontal output is released again.

The IC contains a start-up circuit for

the horizontal oscillator. When this

feature is required a current of 6.5 mA

has to be supplied to pin 36. For an

application without start-up both

supply pins (10 and 36) must be

connected to the 8

V supply line.

V supply line.The drive signal for the vertical ramp

generator is generated by means of a

divider circuit. The RC network for the

ramp generator is external.

Integrated video filters

The circuit contains a chrominance

bandpass and trap circuit. The filters

are realised by means of gyrator

circuits and are automatically tuned

by comparing the tuning frequency

with the crystal frequency of the

decoder.

In the TDA8361 and TDA8362 the

chrominance trap is active only when

the separate chrominance input pin is

connected to ground or to the positive

supply voltage and when a colour

signal is recognized.

When the pin is left open-circuit the

trap is switched off so that the circuit

can also be used for S-VHS

applications.

The luminance delay line and the

delay for the peaking circuit are also

realised by means of gyrator circuits.

Colour decoder

The colour decoder in the various ICs

contains an alignment-free crystal

oscillator, a colour killer circuit and

colour difference demodulators.

The 90° phase shift for the reference

signal is achieved internally. Because

the main differences of the 3 ICs are

found in the colour decoder the

various types will be discussed.

TDA8360

This IC contains only a PAL decoder.

Depending on the frequency of the

crystals which are connected to the IC

the decoder can demodulate all PAL

standards. Because the horizontal

oscillator is calibrated by using the

crystal frequency as a reference the

4.4 MHz crystal must be connected to

pin 35 and the 3.5 MHz crystal to

pin 34. When only one crystal is

connected to the IC the other crystal

pin must be connected to the positive

supply rail via a 47 kW resistor. For

applications with two 3.5 MHz

crystals both must be connected to

pin 34 and the switching between the

crystals must be made externally.

Switching of the crystals is only

allowed directly after the vertical

retrace. The circuit will indicate

whether a PAL signal has been

identified by the colour decoder via

the saturation control pin.

When two crystals are connected to

the IC the output voltage of the video

identification circuit indicates the

frequency of the incoming

chrominance signal.

The conditions are:

· Signal identified at

fosc = 3.6 MHz; VO = 6 V

· Signal identified at

fosc = 4.4 MHz (or no colour);

VO = 8 V.

This information can be used to

switch the sound bandpass filter and

trap filter.

TDA8361

This IC contains an automatic

PAL/NTSC decoder. The conditions

for connecting the reference crystals

are the same as for the TDA8360.

The decoder can be forced to PAL

when the hue control pin is connected

to the positive supply voltage via a

5 kW or 10 kW resistor

(approximately). The decoder cannot

be forced to the NTSC standard. It is

also possible to see if a colour signal

is recognized via the saturation pin.

TDA8362

In addition to the possibilities of the

TDA8361, the TDA8362 can

co-operate with the SECAM add-on

decoder TDA8395.

The communication between the two

ICs is achieved via pin 32. The

TDA8362 supplies the reference

signal (4.43 MHz) for the calibration

system of the TDA8395, identification

of the colour standard is via the same

connection. When a SECAM signal is

detected by the TDA8395 the IC will

draw a current of 150 mA. When

TDA8362 has not identified a colour

signal in this condition it will go into

the SECAM mode, that means it will

switch off the R-Y and B-Y outputs

and increase the voltage level on

pin 32.

This voltage will switch off the

colour-killer in the TDA8395 and

switch on the R-Y and B-Y outputs of

the TDA8395. Forcing the system to

the SECAM standard can be

achieved by loading

pin 32 with a

pin 32 with acurrent of 150 mA. Then the system

manager in the TDA8362 will not

search for PAL or NTSC signals.

Forcing to NTSC is not possible.

For PAL/SECAM applications the

input signal for the TDA8395 can be

obtained from pin 27 (hue control)

when this pin is connected to the

positive supply rail via the 5 kW or

10 kW resistor. An external source

selector is required by the

TDA8395/TDA8362 combination for

PAL/SECAM/NTSC applications.

RGB output circuit

The colour difference signals are

matrixed with the luminance signal to

obtain the RGB signals. Linear

amplifiers have been chosen for the

RGB inputs so that the circuit is

suitable for incoming signals from the

SCART connector. The contrast and

brightness controls operate on

internal and external signals.

The fast blanking pin has a second

detection level at 3.5 V.

When this level is exceeded the

RGB outputs are blanked so that

“On-Screen-Display” signals can be

applied to the outputs.

The output signal has an amplitude of

approximately 4 V, black-to-white,

with nominal input signals and

nominal control settings. The nominal

black level is 1.3 V.

CHASSIS Z5 Synchronized switch-mode power supply:

In a switch mode power supply, a first switching transistor is coupled to a primary winding of an isolation transformer. A second switching transistor periodically applies a low impedance across a second winding of the transformer that is coupled to an oscillator for synchronizing the oscillator to the horizontal frequency. A third winding of the transformer is coupled via a switching diode to a capacitor of a control circuit for developing a DC control voltage in the capacitor that varies in accordance with a supply voltage B+. The control voltage is applied via the transformer to a pulse width modulator that is responsive to the oscillator output signal for producing a pulse-width modulated control signal. The control signal is applied to a mains coupled chopper transistor for generating and regulating the supply voltage B+ in accordance with the pulse width modulation of the control signal.

Description:

The invention relates to switch-mode power supplies.

Some television receivers have signal terminals for receiving, for example, external video input signals such as R, G and B input signals, that are to be developed relative to the common conductor of the receiver. Such signal terminals and the receiver common conductor may be coupled to corresponding signal terminals and common conductors of external devices, such as, for example, a VCR or a teletext decoder.

To simplify the coupling of signals between the external devices and the television receiver, the common conductors of the receiver and of the external devices are connected together so that all are at the same potential. The signal lines of each external device are coupled to the corresponding signal terminals of the receiver. In such an arrangement, the common conductor of each device, such as of the television receiver, may be held "floating", or conductively isolated, relative to the corresponding AC mains supply source that energizes the device. When the common conductor is held floating, a user touching a terminal that is at the potential of the common conductor will not suffer an electrical shock.

To simplify the coupling of signals between the external devices and the television receiver, the common conductors of the receiver and of the external devices are connected together so that all are at the same potential. The signal lines of each external device are coupled to the corresponding signal terminals of the receiver. In such an arrangement, the common conductor of each device, such as of the television receiver, may be held "floating", or conductively isolated, relative to the corresponding AC mains supply source that energizes the device. When the common conductor is held floating, a user touching a terminal that is at the potential of the common conductor will not suffer an electrical shock. Therefore, it may be desirable to isolate the common conductor, or ground, of, for example, the television receiver from the potentials of the terminals of the AC mains supply source that provide power to the television receiver. Such isolation is typically achieved by a transformer. The isolated common conductor is sometimes referred to as a "cold" ground conductor.

In a typical switch mode power supply (SMPS) of a television receiver the AC mains supply voltage is coupled, for example, directly, and without using transformer coupling, to a bridge rectifier. An unregulated direct current (DC) input supply voltage is produced that is, for example, referenced to a common conductor, referred to as "hot" ground, and that is conductively isolated from the cold ground conductor. A pulse width modulator controls the duty cycle of a chopper transistor switch that applies the unregulated supply voltage across a primary winding of an isolating flyback transformer. A flyback voltage at a frequency that is determined by the modulator is developed at a secondary winding of the transformer and is rectified to produce a DC output supply voltage such as a voltage B+ that energizes a horizontal deflection circuit of the television receiver. The primary winding of the flyback transformer is, for example, conductively coupled to the hot ground conductor. The secondary winding of the flyback transformer and voltage B+ may be conductively isolated from the hot ground conductor by the hot-cold barrier formed by the transformer.

It may be desirable to synchronize the operation of the chopper transistor to horizontal scanning frequency for preventing the occurrence of an objectionable visual pattern in an image displayed in a display of the television receiver.

It may be further desirable to couple a horizontal synchronizing signal that is referenced to the cold ground to the pulse-width modulator that is referenced to the hot ground such that isolation is maintained.

A synchronized switch mode power supply, embodying an aspect of the invention, includes a transfromer having first and second windings. A first switching arrangement is coupled to the first winding for generating a first switching current in the first winding to periodically energize the second winding. A source of a synchronizing input signal at a frequency that is related to a deflection frequency is provided. A second switching arrangement responsive to the input signal and coupled to the second winding periodically applies a low impedance across the energized second winding that by transformer action produces a substantial increase in the first switching current. A periodic first control signal is generated. The increase in the first switching current is sensed to synchronize the first control signal to the input signal. An output supply voltage is generated from an input supply voltage in accordance with the first control signal.

A synchronized switch mode power supply, embodying an aspect of the invention, includes a transfromer having first and second windings. A first switching arrangement is coupled to the first winding for generating a first switching current in the first winding to periodically energize the second winding. A source of a synchronizing input signal at a frequency that is related to a deflection frequency is provided. A second switching arrangement responsive to the input signal and coupled to the second winding periodically applies a low impedance across the energized second winding that by transformer action produces a substantial increase in the first switching current. A periodic first control signal is generated. The increase in the first switching current is sensed to synchronize the first control signal to the input signal. An output supply voltage is generated from an input supply voltage in accordance with the first control signal. TDA3654 TDA3654Q Vertical deflection and guard circuit (110°).

GENERAL DESCRIPTION

The TDA3654 is a f

ull performance vertical deflection output circuit for direct drive of the deflection coils and can be used

ull performance vertical deflection output circuit for direct drive of the deflection coils and can be usedfor a wide range of 90° and 110° deflection systems.

A guard circuit is provided which blanks the picture tube screen in the absence of deflection current.

Features

· Direct drive to the deflection coils

· 90° and 110° deflection system

· Internal blanking guard circuit

· Internal voltage stabilizer

QUICK REFERENCE DATA

Output voltage V5-2 max. 60 V

Output current (peak-to-peak) I5(p-p) max. 3 A

Supply voltage V9-2 max. 40 V

Guard circuit output voltage V7-2 max. 5,6 V

Operating ambient temperature range Tamb -25 to +60 °C

Storage temperature Tstg -55 to +150 °C

FUNCTIONAL DESCRIPTION

Output stage and protection circuits

The output stage consists of two Darlington configurations in class B arrangement.

Each output transistor can deliver 1,5 A maximum and the VCEO is 60 V.

Protection of the output stage is such that the operation of the transistors remains well within the SOAR area in all

circumstances at the output pin, (pin 5). This is obtained by the cooperation of the thermal protection circuit, the

current-voltage detector and the short circuit protection.

Special measures in the internal circuit layout give the output transistors extra solidity, this is illustrated in Fig.5 where

typical SOAR curves of the lower output transistor are given. The same curves also apply for the upper output device.

The supply for the output stage is fed to pin 6 and the output stage ground is connected to pin 4.

Driver and switching circuit

Pin 1 is the input for the driver

of the output stage. The signal at pin 1 is also applied to pin 3 which is the input of a

of the output stage. The signal at pin 1 is also applied to pin 3 which is the input of aswitching circuit (pin 1 and 3 are connected via external resistors).

This switching circuit rapidly turns off the lower output stage when the flyback starts and it, therefore, allows a quick start

of the flyback generator. The maximum required input signal for the maximum output current peak-to-peak value of 3 A

is only 3 V, the sum of the currents in pins 1 and 3 is then maximum 1 mA.

Flyback generator

During scan, the capacitor between pins 6 and 8 is charged to a level which is dependent on the value of the resistor at

pin 8 (see Fig.1).

When the flyback starts and the voltage at the output pin (pin 5) exceeds the supply voltage, the flyback generator is

activated.

The supply voltage is then connected in series, via pin 8, with the voltage across the capacitor during the flyback period.

This implies that during scan the supply voltage can be reduced to the required scan voltage plus saturation voltage of

the output transistors.

The amplitude of the flyback voltage can be chosen by changing the value of the external resistor at pin 8.

It should be noted that the application is chosen such that the lowest voltage at pin 8 is > 1,5 V, during normal operation.

Guard circuit

When there is no deflection current, for any reason, the voltage at pin 8 becomes less than 1 V, the guard circuit will

produce a d.c. voltage at pin 7. This voltage can be used to blank the picture tube, so that the screen will not burn in.

Voltage stabilizer

The internal voltage stabilizer provides a stabilized supply of 6 V to drive the output stage, so the drive current is not

affected by supply voltage variations.

No comments:

Post a Comment

The most important thing to remember about the Comment Rules is this:

The determination of whether any comment is in compliance is at the sole discretion of this blog’s owner.

Comments on this blog may be blocked or deleted at any time.

Fair people are getting fair reply. Spam and useless crap and filthy comments / scrapers / observations goes all directly to My Private HELL without even appearing in public !!!

The fact that a comment is permitted in no way constitutes an endorsement of any view expressed, fact alleged, or link provided in that comment by the administrator of this site.

This means that there may be a delay between the submission and the eventual appearance of your comment.

Requiring blog comments to obey well-defined rules does not infringe on the free speech of commenters.

Resisting the tide of post-modernity may be difficult, but I will attempt it anyway.

Your choice.........Live or DIE.

That indeed is where your liberty lies.

Note: Only a member of this blog may post a comment.