This is the PHILIPS 2nd generation 100HZ digital scanrate from PHILIPS.

The invention relates to an arrangement for converting an original picture signal representing a sequence of frames, each of which is composed of two interlaced fields, into a converted picture signal which has a double field frequency with respect to the original picture signal.

When converting a picture signal into such a converted picture signal which, with respect to the original picture signal, has a double field frequency, there is the problem that every second field of the converted picture signal must be newly generated, because no corresponding field of the original picture signal is available with respect to time and also with respect to the picture information.

In simple arrangements for doubling the field frequency, every field is doubled. A moving object in the fields of the converted picture signal is imaged twice in the same position before it jumps to the next position in the two subsequent fields. Since the human eye cannot follow these jumps, it is incident on the average speed of motion and observes a moving object from field to field at different positions. This leads to a double structure and motion blurr.

In other arrangements for field doubling of a picture signal a motion compensation is therefore provided by means of which the motion between two fields of the original picture signal is determined so that the motion can be taken into account in fields of the converted picture signal to be generated therebetween as a function of time and a corresponding interpolation can be performed. However, such arrangements have the further problem that possibly present noise is also to be reduced and that the line flicker, which still occurs in spite of the doubling of the field frequency in picture signals generated by way of interlaced scanning, is to be reduced. In the state of the art arrangements are only known in which a motion compensation is combined either with a noise reduction or with a line flicker reduction.

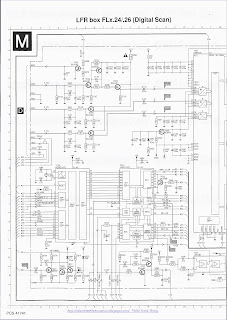

- Right side all Power part and large signal panel

- Left side all signal processing and small signal panel

Description of circuits:

PHILIPS 28PW9608 MATCHLINE IDTV 100HZ CHASSIS FL2.24 AA Switched-mode self oscillating supply voltage circuit:POWER SUPPLY (SOPS - Self Oscillating Power Supply)

A

switched-mode self-oscillating supply voltage circuit for converting an

input voltage into an output d.c. voltage which is substantially

independent of variations of the input voltage and/or a load connected

to the output voltage. The circuit comprises a first controllable switch

connected in series with a transformer winding and a second controllable

switch for turning-off the first switch. The conduction period of the

first switch is controlled by means of a control voltage present on a

control electrode of the second switch. The circuit can be switched-over

to a stand-up state in which the energy supplied to the load is reduced

to zero. A starting network is connected between the input voltage and

the second switch so that the current therein flows through the second

switch during the period of time this switch conducts and does not flow

to the control electode of the first switch in the stand-by state.

A

switched-mode self-oscillating supply voltage circuit for converting an

input voltage into an output d.c. voltage which is substantially

independent of variations of the input voltage and/or a load connected

to the output voltage. The circuit comprises a first controllable switch

connected in series with a transformer winding and a second controllable

switch for turning-off the first switch. The conduction period of the

first switch is controlled by means of a control voltage present on a

control electrode of the second switch. The circuit can be switched-over

to a stand-up state in which the energy supplied to the load is reduced

to zero. A starting network is connected between the input voltage and

the second switch so that the current therein flows through the second

switch during the period of time this switch conducts and does not flow

to the control electode of the first switch in the stand-by state. 1.

A switched-mode self-oscillating supply voltage circuit for converting

an input voltage into an output d.c. voltage which is substantially

independent of variations of the input voltage and/or of a load

connected to the terminals of the output voltage, comprising a

transformer having a primary and a feedback winding, a first

controllable switch connected in series with the primary winding, the

series arrangement thus formed being coupled between terminals for the

input voltage, a second controllable switch coupled via a turn-off

capacitor to the control electrode of the first switch to turn it off,

means coupling the feedback winding to said control electrode, a

transformer winding being coupled via a rectifier to an output capacitor

having terminals which supply the output voltage, an output

voltage-dependent control voltage being present on a control electrode

of the second switch for controlling the conduction period of the first

switch, the circuit being switchable between an operating state and a

stand-by state in which relative to the operating state the supply

energy supplied to the load is considerably reduced, a starting network

connected to a terminal for the input voltage, means for adjusting the

control voltage in the stand-by state to a value at which the first

controllable switch is cut-off, a connection which carries current

during the conduction period for the second controllable switch being

provided between the starting network and said second switch, and means

providing a connection between the starting network and the control

electrode of the

1.

A switched-mode self-oscillating supply voltage circuit for converting

an input voltage into an output d.c. voltage which is substantially

independent of variations of the input voltage and/or of a load

connected to the terminals of the output voltage, comprising a

transformer having a primary and a feedback winding, a first

controllable switch connected in series with the primary winding, the

series arrangement thus formed being coupled between terminals for the

input voltage, a second controllable switch coupled via a turn-off

capacitor to the control electrode of the first switch to turn it off,

means coupling the feedback winding to said control electrode, a

transformer winding being coupled via a rectifier to an output capacitor

having terminals which supply the output voltage, an output

voltage-dependent control voltage being present on a control electrode

of the second switch for controlling the conduction period of the first

switch, the circuit being switchable between an operating state and a

stand-by state in which relative to the operating state the supply

energy supplied to the load is considerably reduced, a starting network

connected to a terminal for the input voltage, means for adjusting the

control voltage in the stand-by state to a value at which the first

controllable switch is cut-off, a connection which carries current

during the conduction period for the second controllable switch being

provided between the starting network and said second switch, and means

providing a connection between the starting network and the control

electrode of the first switch, which connection does not carry current

in the stand-by state.

first switch, which connection does not carry current

in the stand-by state.2. A supply voltage circuit as claimed in claim 1, further comprising a resistor included between the connection of the starting network to the second switch and a turn-off capacitor present in the connection to the control electrode of the first switch.

3. A supply voltage circuit as claimed in claim 2, characterized in that the second controllable switch comprises a thyristor having a main current path included in the control electrode connection of the first controllable switch, said thyristor having a first control gate electrode for adjusting the turn-off instant of the first switch and a second control electrode to which the starting network and the resistor are connected.

4. A

supply voltage circuit as claimed in claim 1, characterized in that a

resistor is included in the connection to the control electrode of the

second controllable switch so that a current flows through said resistor

in the stand-by state of a value sufficient to cut-off the first

controllable switch.

4. A

supply voltage circuit as claimed in claim 1, characterized in that a

resistor is included in the connection to the control electrode of the

second controllable switch so that a current flows through said resistor

in the stand-by state of a value sufficient to cut-off the first

controllable switch.

Description:

The

invention relates to a switched-mode self-oscillating supply voltage

circuit for converting an input voltage into an output d.c. voltage

which is substantially independent of variations of the input voltage

and/or of a load connected to the terminals of the output voltage. This

circuit comprises a transformer having a primary and a feedback winding

and a first controllable switch arranged in series with the primary

winding. The series arrangement thus formed is coupled between the

terminals of the input voltage. A second controllable switch which is

coupled via a turnoff capacitor to the control electrode of the first

switch to turn it off. The feedback winding is coupled to this control

electrode and the primary winding is coupled via a rectifier to an

output capacitor the terminals of which are the terminals for the output

voltage. An output voltage-dependent control voltage is present on a

control electrode of the second switch for controlling the conduction

period of the first switch. The circuit is switchable between an

operating state and a stand-by state in which relative to the operating

state the energy supplied to the load is considerably reduced, and the

circuit further comprises a starting network connected to a terminal for

the input voltage. Such a supply voltage circuit is disclosed in German Patent Application No. 2,651,196. With this prior art circuit supply energy can be applied in the operating state to the different portions of a television receiver. In the stand-by state the majority of the output voltages of the circuit are so low that the receiver is substantially in the switched-off condition. In the prior art circuit the starting network is formed by a resistor connected to the unstabilized input voltage and through which on turn-on of the circuit a current flows via the feedback winding to the control electrode of the first controllable switch, which is a switching transistor, and brings it to and maintains it in the conductive state, as a result of which the circuit can start.

In

the stand-by state the transistor is non-conducting in a large part of

the period of the generated oscillation so that little energy is stored

in the transformer. However, the starting resistor is connected via a

diode to the second controllable switch, which is a thyristor. As the

sum of the voltages across these elements is higher than the

base-emitter threshold voltage of the transistor, the diode and the

thyristor cannot simultaneously carry current. This implies that current

flows through the starting resistor to the base of the transistor via

the feedback winding after a capacitor connected to the feedback winding

has been charged.

In

the stand-by state the transistor is non-conducting in a large part of

the period of the generated oscillation so that little energy is stored

in the transformer. However, the starting resistor is connected via a

diode to the second controllable switch, which is a thyristor. As the

sum of the voltages across these elements is higher than the

base-emitter threshold voltage of the transistor, the diode and the

thyristor cannot simultaneously carry current. This implies that current

flows through the starting resistor to the base of the transistor via

the feedback winding after a capacitor connected to the feedback winding

has been charged. The invention has for its object to provide an improved circuit of the same type in which in the stand-by state the supply energy applied to the load is reduced to zero. The prior art circuit cannot be improved in this respect without the use of mechanical switches, for example relays. According to the invention, the switched-mode self-oscillating supply voltage circuit does not comprise such relays and is characterized in that it further comprises means for adjusting the control voltage in the stand-by state to a value at which the first controllable switch is cut-off. A connection which carries current during the conduction period of the second controllable switch is provided between the starting network and said second switch while a connection present between the starting network and the control electrode of the first switch does not carry current in the stand-by state.

The invention is based on the recognition that the prior art supply voltage circuit cannot oscillate, so that the energy supplied by it is zero, if the control voltage obtains a value as referred to, while the starting network is connected in such a manner that in the stand-by state no current can flow through it to the control electrode of the first controllable switch.

It should be noted that in the said German Patent Application the starting network is in the form of a resistor which is connected to an unstabilized input d.c. voltage. It is, however, known, for example, from German Patent Specification No. 2,417,628 to employ for this purpose a rectifier network connected to an a.c. voltage from which the said input d.c. voltage is derived by rectification.

The invention will now be further described by way of example with reference to the accompanying drawing, which shows a basic circuit diagram of a switched-mode self-oscillating supply voltage circuit.

The self-oscillating supply circuit shown in the FIGURE comprises a npn-switching transistor Tr1 having its collector connected to the primary winding L1 of a transformer T, while the emitter is connected to ground via a small resistor R1, for example 1.5 Ohm. Resistor R1 is decoupled for the high frequencies by means of a 150 nF capacitor C1. One end of winding L1 is connected to a conductor which carries an unstabilized input d.c. voltage V B of, for example, 300 V. Voltage V B has a negative rail connected to ground and is derived from the electric power supply by rectification. One end of a feedback winding L2 is connected to the base of transistor Tr1 via the parallel arrangement of a small inductance L3 and a damping resistor R2. A terminal of a 47 μF capacitor C2 is connected to the junction of the elements L2, L3 and R2. The series arrangement of a diode D1 and a 2.2 Ohm-limiting resistor R3 is arranged between the other terminal of capacitor C2 and the other end of winding L2 and the series arrangement of a resistor R4 of 12 Ohm and a diode D2 is arranged between the same end of winding L2 and the emitter of transistor Tr1. A 150 nF capacitor C3 is connected in parallel with diode D2. The anode of diode D1 is connected to that end of winding L2 which is not connected to capacitor C2, while the anode of diode D2 is connected to the emitter of transistor Tr1. In the FIGURE the winding sense of windings L1 and L2 is indicated by means of dots.

The junction of capacitor C2 and resistor R3 is connected to a 100 Ohm resistor R5 and to the emitter of a pnp-transistor Tr2. The base of transistor Tr2 is connected to the other terminal of resistor R5 and to the collector of an npn-transistor Tr3, whose emitter is connected to ground. The base of Tr3 is connected to the collector of transistor Tr2. Transistors Tr2 and Tr3 form an artificial thyristor, i.e. a controllable diode whose anode is the emitter of transistor Tr2 while the cathode is the emitter of transistor Tr3. The base of transistor Tr2 is the anode gate and the base of transistor Tr3 is the cathode gate of the thyristor formed. Between the last-mentioned base and the emitter of transistor Tr1 there is arranged the series network of a 2.2 kOhm resistor R6 with the parallel arrangement of a 2.2 kOhm resistor R7 and a 100 μF capacitor C4. The series arrangement of a diode D11 and a 220 Ohm limiting resistor R19 is arranged between the junction of components R6, R7 and C4 and the junction of components C2, L2, R2 and L3. The cathode of diode D11 is connected to capacitor C2.

Because

of the feedback the described circuit oscillates independently as soon

as the steady state is achieved. It will be described hereinafter how

this state is obtained. During the time transistor Tr1 conducts the

current flowing through the resistor R1 increases linearly. The resistor

R4 then partly determines the base current of transistor Tr1. Capacitor

C4 and resistor R7 form a voltage source the voltage of which is

subtracted from the voltage drop across resistor R1. As soon as the

voltage on the base of transistor Tr3 is equal to approximately 0.7 V

this transistor becomes conductive, as a result of which the thyristor

formed by transistors Tr2 and Tr3 becomes rapidly conductive and remains

so. Across capacitor C2 there is a negative voltage by means of which

transistor Tr1 is turned off. The inverse base current thereof flows

through thyristor Tr2, Tr3. This causes charge to be withdrawn from

capacitor C2, while the charge carriers stored in transistor Tr1 are

removed with the aid of inductance L3. As soon as the collector current

of transistor Tr1 has been turned off, the voltage across winding L2

reverses its polarity, which current recharges the capacitor. Now the

voltage at the junction of components C2, R3 and R5 is negative, causing

thyristor Tr2, Tr3 to extinguish.

Because

of the feedback the described circuit oscillates independently as soon

as the steady state is achieved. It will be described hereinafter how

this state is obtained. During the time transistor Tr1 conducts the

current flowing through the resistor R1 increases linearly. The resistor

R4 then partly determines the base current of transistor Tr1. Capacitor

C4 and resistor R7 form a voltage source the voltage of which is

subtracted from the voltage drop across resistor R1. As soon as the

voltage on the base of transistor Tr3 is equal to approximately 0.7 V

this transistor becomes conductive, as a result of which the thyristor

formed by transistors Tr2 and Tr3 becomes rapidly conductive and remains

so. Across capacitor C2 there is a negative voltage by means of which

transistor Tr1 is turned off. The inverse base current thereof flows

through thyristor Tr2, Tr3. This causes charge to be withdrawn from

capacitor C2, while the charge carriers stored in transistor Tr1 are

removed with the aid of inductance L3. As soon as the collector current

of transistor Tr1 has been turned off, the voltage across winding L2

reverses its polarity, which current recharges the capacitor. Now the

voltage at the junction of components C2, R3 and R5 is negative, causing

thyristor Tr2, Tr3 to extinguish. Secondary windings L4, L5 and L6 are provided on the core of transformer T with the indicated winding senses. When transistor Tr1 is turned off, a current which recharges a smoothing capacitor C5, C6 or C7 via a rectifier D3, D4 or D5 flows through each of these windings. The voltages across these capacitors are the output voltages of the supply circuit for loads connectable thereto. These loads, which are not sho

wn in the FIGURE, are, for example, portions of a television receiver.

wn in the FIGURE, are, for example, portions of a television receiver. In parallel with winding L1 there is the series network of a 2.2 nF tuning capacitor C8 and a 100 Ohm limiting resistor R8. The anode of a diode D6 is connected to the junction of components R8 and C8, while the cathode is connected to the other terminal of resistor R8. Winding L1 and capacitor C8 form a resonant circuit across which an oscillation is produced after windings L4, L5 and L6 have become currentless. At a later instant the current through circuit L1, C8 reverses its direction. As a result thereof a current is generated in winding L2 which flows via diode D2 and resistor R4 to the base of transistor Tr1 and makes this transistor conductive and maintains it in this state. The dissipation in resistor R8 is reduced by means of diode D6. A clamping network formed by the parallel arrangement of a 22 kOhm resistor R9 and a 120 nF capacitor C9 is arranged in series with a diode D7. This whole assembly is in parallel with winding L1 and cuts-off parasitic oscillations which would be produced during the period of time in which transistor Tr1 is non-conductive. The output voltages of the supply circuit are kept substantially constant in spite of variations of voltage V B and/or the loads, thanks to a control of the turning-on instant of thyrisistor Tr2, Tr3. For this purpose the emitter of a light-sensitive transistor Tr4 is connected to the base of transistor Tr3. The collector of transistor Tr4 is connected via a resistor R10 to the conductor which carries the voltage V B and to a Zener diode Z1 which has a positive voltage of approximately 7.5 V, while the base is unconnected. The other end of diode Z1 is connected to ground. A light-emitting diode D8, whose cathode is connected to the collector of an npn-transistor Tr5, is optically coupled to transistor Tr4. By means of a potentiometer R11 the base of transistor Tr5 can be adjusted to a d.c. voltage which is derived from the voltage V 0 of approximately 130 V across capacitor C6. The anode of diode D8 is connected to a d.c. voltage V 1 of approximately 13 V. A resistor R12 is also connected to voltage V 1 , the other end of the resistor being connected to the emitter of transistor Tr5, to the cathode of a Zener diode Z2 which has a voltage of

approximately 7.5 V and to a smoothing capacitor C10. The other ends

of diode Z2 and capacitor C10 are connected to ground. Voltage V1 can be

generated by means of a transformer connected to the electric AC supply

and a rectifier, which are not shown for the sake of simplicity, more

specifically for a remote control to which constantly supply energy is

always applied, even when the majority of the components of the receiver

in what is referred to as the stand-by state are not supplied with

supply energy.

approximately 7.5 V and to a smoothing capacitor C10. The other ends

of diode Z2 and capacitor C10 are connected to ground. Voltage V1 can be

generated by means of a transformer connected to the electric AC supply

and a rectifier, which are not shown for the sake of simplicity, more

specifically for a remote control to which constantly supply energy is

always applied, even when the majority of the components of the receiver

in what is referred to as the stand-by state are not supplied with

supply energy. A portion of voltage V 0 is compared with the voltage of diode Z2 by means of transistor Tr5. The measured difference determines the collector current of transistor Tr5 and consequently the emitter current of transistor Tr4. This emitter current produces across resistor R6 a voltage drop whose polarity is the opposite of the polarity of the voltage source formed by resistor R7 and capacitor C4. Under the influence of this voltage drop the turn-on instant of thyristor Tr2, Tr3 is controlled as a function of voltage V 0 . If, for example, voltage V 0 tends to decrease owing to an increasing load thereon and/or in response to a decrease in voltage V B , then the collector current of transistor Tr5 decreases and consequently also the said voltage drop. Thyristor Tr2, Tr3 is turned on at a later instant than would otherwise be the case, causing transistor Tr1 to be cut-off at a later instant. The final value of the collector current of this transistor is consequently higher. Consequently, the ratio of the time interval in which transistor

Tr1 is conductive to the entire period, commonly referred to as the duty cycle, increases, while the frequency decreases.

Tr1 is conductive to the entire period, commonly referred to as the duty cycle, increases, while the frequency decreases. The circuit is protected from overvoltage. This is ensured by a thyristor which is formed by a pnp-transistor Tr6 and an npn-transistor Tr7. The anode of a diode D9 is connected to the junction of components R3 and C2 and the cathode to the base of transistor Tr6 and to the collector of transistor Tr7. The base of transistor Tr7, which base is connected to the collector of transistor Tr6, is connected via a zener diode Z3 to a voltage which, by means of a potentiometer R13 is adjusted to a value derived from the voltage across capacitor C7. The emitter of transistor Tr6 also is connected to the voltage of capacitor C7, more specifically via a resistor R14 and a diode D10. If this voltage increases to above a predetermined value then thyristor Tr6, Tr7 becomes conductive. Since the emitter of transistor Tr7 is connected to ground, the voltage at its collector becomes very low, as a result of which diode D9 becomes conductive, which keeps transistor Tr1 in the non-conducting state. This situation is maintained as long as thyristor Tr6, Tr7 continues to conduct. This conduction time is predominantly determined by the values of capacitor C7, resistor R14 and a resistor R15 connected between the base and the emitter of transistor Tr6. A thyristor is advantageously used here to render it possible to switch off a large current even with a low level signal and to obtain the required hysteresis.

The

circuit comprises a 1 MOhm starting resistor R16, one end of which is

connected to the base of transistor Tr2 and the other end to the

conductor which carries the voltage V B . Upon turn-on of the

circuit current flows through resistors R16 and R5 and through

capacitor C2, which has as yet no charge, to the base of transistor Tr1.

The voltage drop thus produced across resistor R5 keeps transistor Tr2,

and consequently also transistor Tr3, in the non-conductive state,

while transistor Tr1 is made conductive and is maintained so by this

current. Current also flows through winding L2. In this manner the

circuit can start as energy is built up in transformer T.

The

circuit comprises a 1 MOhm starting resistor R16, one end of which is

connected to the base of transistor Tr2 and the other end to the

conductor which carries the voltage V B . Upon turn-on of the

circuit current flows through resistors R16 and R5 and through

capacitor C2, which has as yet no charge, to the base of transistor Tr1.

The voltage drop thus produced across resistor R5 keeps transistor Tr2,

and consequently also transistor Tr3, in the non-conductive state,

while transistor Tr1 is made conductive and is maintained so by this

current. Current also flows through winding L2. In this manner the

circuit can start as energy is built up in transformer T. The supply circuit can be brought into the stand-by state by making an npn-transistor Tr8, which is non-conductive in the operating state, conductive. The emitter of transistor Tr8 is connected to ground while the collector is connected to the collector of transistor Tr5 via a 1.8 kOhm resistor R17. A resistor R18 has one end connected to the base of transistor Tr8 and the other end, either in the operating state to ground, or in the stand-by state to a positive voltage of, for example, 5 V. Transistor Tr8 conducts in response to this voltage. An additional, large current flows through diode D8 and consequently also through transistor Tr4, resulting in thyristor Tr2, Tr3 being made conductive and transistor Tr1 being made non-conductive and maintained so. So to all appearances a large control current is obtained causing the duty cycle to be reduced to zero. A condition for a correct operation is that the emitter current of transistor Tr4 be sufficiently large in all circumstances, which implies that the voltage drop produced across resistor R6 by this current is always higher than the sum of the voltage across voltage source R7, C4, of the base-emitter threshold voltage of transistor Tr3 in the conductive state thereof, and of the voltage at the emitter of transistor Tr1. So the said voltage drop must be higher than the sum of the first two voltages, which corresponds to the worst dimensioning case in which the stand-by state is initiated while transistor Tr1 is in the non-conductive state.

If thyristor Tr2,

Tr3 conducts, either in the operating state or in the stand-by state,

current flows through resistor R16 via the collector emitter path of

transistor Tr3 to ground. This current is too small to have any

appreciable influence on the behaviour of the circuit. When thyristor

Tr2, Tr3 does not conduct, the voltage on the left hand terminal of

capacitor C2 is equal to approximately 1 V, while the voltage across the

capacitor is approximately -4 V. So transistor Tr1 remains in the

non-conductive state and a premature turn-on thereof cannot occur. If in

the operating state transistor Tr1 conducts while thyristor Tr2, Tr3 is

cut-off, then the current flows through resistor R16 in the same manner

as it flows during the start to the base of transistor Tr1, but has

relatively little influence as the base current caused by the energy

stored in winding L2 is many times larger. If both transistor Tr1 and

thyristor Tr2, Tr3 are non-conductive, then the current through resistor

R16 flows through components R5, C2, L2, R4, C3 and R1. In this

stand-by state capacitor C2 has indeed substantially no negative charge

any longer but, in spite thereof, transistor Tr1 cannot become

conductive since no current flows to its base. It will furthermore be

noted that the circuit is protected in the event that thyristor Tr2, Tr3

has an interruption. Namely, in such a case the circuit cannot start.

If thyristor Tr2,

Tr3 conducts, either in the operating state or in the stand-by state,

current flows through resistor R16 via the collector emitter path of

transistor Tr3 to ground. This current is too small to have any

appreciable influence on the behaviour of the circuit. When thyristor

Tr2, Tr3 does not conduct, the voltage on the left hand terminal of

capacitor C2 is equal to approximately 1 V, while the voltage across the

capacitor is approximately -4 V. So transistor Tr1 remains in the

non-conductive state and a premature turn-on thereof cannot occur. If in

the operating state transistor Tr1 conducts while thyristor Tr2, Tr3 is

cut-off, then the current flows through resistor R16 in the same manner

as it flows during the start to the base of transistor Tr1, but has

relatively little influence as the base current caused by the energy

stored in winding L2 is many times larger. If both transistor Tr1 and

thyristor Tr2, Tr3 are non-conductive, then the current through resistor

R16 flows through components R5, C2, L2, R4, C3 and R1. In this

stand-by state capacitor C2 has indeed substantially no negative charge

any longer but, in spite thereof, transistor Tr1 cannot become

conductive since no current flows to its base. It will furthermore be

noted that the circuit is protected in the event that thyristor Tr2, Tr3

has an interruption. Namely, in such a case the circuit cannot start. In the foregoing a circuit is described which may be considered to be a switched-mode supply voltage circuit of the parallel ("flyback") type. It will be obvious that the invention may alternatively be used in supply voltage circuits of a different type, for example converters of the type commonly referred to as up-converters. It will also be obvious that transistor Tr1 may be replaced by an equivalent switch, for example a gate-turn-off switch.

TDA8425 Hi-fi stereo audio processor;I2C-bus

GENERAL DESCRIPTION

GENERAL DESCRIPTIONThe TDA8425 is a monolithic bipolar integrated stereo sound circuit with a loudspeaker channel facility, digitally

controlled via the I2C-bus for application in hi-fi audio and television sound.

Feature:

· Source and mode selector for two stereo channels

· Pseudo stereo, spatial stereo, linear stereo and forced mono switch

· Volume and balance control

· Bass, treble and mute control

· Power supply with power-on reset

FUNCTIONAL DESCRIPTION

Source selector

The input to channel 1 (CH1) and channel 2 (CH2) is determined by the source selector. The selection is made from the

following AF input signals:

· IN 1 L (pin 18); IN1 R (pin 20)

or

· IN2 L (pin 1); IN2 R (pin 3)

Mode selector

The mode selector selects between stereo, sound A and sound B (in the event of bilingual transmission) for OUT R and

OUT L.

Volume control and balance

The volume control consists of two stages (left and right). In each part the gain can be adjusted between +6 dB and

-64 dB in steps of 2 dB. An additional step allows an attenuation of ³ 80 dB. Both parts can be controlled independently

over the whole range, which allows the balance to be varied by controlling the volume of left and right output channels.

Linear stereo, pseudo stereo, spatial stereo and forced mono mode(1)

It is possible to select four modes: linear stereo, pseudo stereo, spatial stereo or forced mono. The pseudo stereo mode

handles mono transmissions, the spatial stereo mode handles stereo transmissions and the forced mono can be used

in the event of stereo signals.

Bass control

The bass control stage can be switched from an emphasis of 15 dB to an attenuation of 12 dB for low frequencies in

steps of 3 dB.

Treble control

The treble control stage can be switched from +12 dB to -12 dB in steps of 3 dB.

Bias and power supply

The TDA8425 includes a bias and power supply stage, which generates a voltage of 0.5 ´ VCC with a low output

impedance and injector currents for the logic part.

Power-on reset

The on-chip power-on reset circuit sets the mute bit to active, which mutes both parts of the treble amplifier. The muting

can be switched by transmission of the mute bit.

I2C-bus receiver and data handling

Bus specification

The TDA8425 is controlled via the 2-wire I2C-bus by a microcomputer.

The two wires (SDA - serial data, SCL - serial clock) carry information between the devices connected to the bus. Both

SDA and SCL are bidirectional lines, connected to a positive supply voltage via a pull up resistor.

When the bus is free both lines are HIGH.

The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line

can only change when the clock signal on the SCL line is LOW. The set up and hold times are specified in AC

CHARACTERISTICS.

A HIGH-to-LOW transition of the SDA line while SCL is HIGH is defined as a start condition.

A LOW-to-HIGH transition of the SDA line while SCL is HIGH is defined as a stop condition.

The bus receiver will be reset by the reception of a start condition. The bus is considered to be busy after the start

condition.

The bus is considered to be free again after a stop condition.

Module address

Data transmission to the TDA8425 starts with the module address MAD.

PHILIPS 28PW9608 MATCHLINE IDTV 100HZ CHASSIS FL2.24 AA Rapid access teletext - Videotextx decoder arrangement:A teletext decoder includes a background or buffer memory operating as a first-in, first-out (

FIFO)

memory. The buffer memory is used for storing a large number of

teletext pages. A given video line that contains teletext information

is identified as such by the detection of part of a clock run-in

sequence followed by the framing code. The video line is then stored in

the background memory. After a user page request occurs, the

background memory is read-out by a data processor operating in a full

channel mode of operation for obtaining the information of the

requested page. As long as the read-out operation has not been

terminated, incoming teletext data is stored in the background memory.

This enables teletext data received prior to termination of the read-out

operation to be read out and processed by the data processor.

FIFO)

memory. The buffer memory is used for storing a large number of

teletext pages. A given video line that contains teletext information

is identified as such by the detection of part of a clock run-in

sequence followed by the framing code. The video line is then stored in

the background memory. After a user page request occurs, the

background memory is read-out by a data processor operating in a full

channel mode of operation for obtaining the information of the

requested page. As long as the read-out operation has not been

terminated, incoming teletext data is stored in the background memory.

This enables teletext data received prior to termination of the read-out

operation to be read out and processed by the data processor. 1. A television apparatus responsive to an incoming television signal containing video lines that carry text data, defining corresponding data lines, for generating an output signal that is capable of providing picture information to a display device, comprising:

means for generating a first control signal in order to select one of said data lines to be used in conjunction with the generation of said output signal;

a source of said television signal;

a first-in, first-out background memory having a data input that is coupled to an output of said source;

first

control means coupled to said background memory for controlling

storage therein of corresponding data lines of said television signal,

wherein prior to the time said first control signal is generated, said

background memory already contains a substantial number of stored data

lines of said television signal;

first

control means coupled to said background memory for controlling

storage therein of corresponding data lines of said television signal,

wherein prior to the time said first control signal is generated, said

background memory already contains a substantial number of stored data

lines of said television signal; second control means responsive to said first control signal and coupled to said background memory for controlling during a given interval that follows the generation of said first control signal, read-out from said background memory of a plurality of data lines of said television signal that have been stored before the end of said given interval, said given interval having a duration that is substantially shorter than that of a corresponding interval between the occurrence of an initial data line of said plurality of data lines and the occurrence of a final data line thereof so as to reduce access time to said plurality of data lines, said second control means controlling read-out of said plurality of data lines in a first-in, first-out manner for generating during said given interval a data signal that contains the data of said plurality of data lines including data lines that have been stored in said background memory during said given interval; and

a data processor responsive to said data signal for selecting said one data line to generate in accordance therewith said output signal.

2. An

apparatus according to claim 1 wherein said data lines occur in said

television signal only during, corresponding vertical blanking

intervals, wherein, during said given interval, said data processor

operates in a full channel mode of operation, and wherein, prior to the

time when said first control signal is generated, said data processor

operates in a field flyback mode of operation.

3. An apparatus according to claim 1 further comprising,

means for coupling said data signal and said television signal to said

data processor such that prior to the time said first control signal is

generated said television signal is coupled to said data processor in a

manner that bypasses said background memory.

4. An apparatus according to claim 3 wherein, throughout

said given interval, said coupling means decouples said signal that

bypasses said background memory from said data processor.

5. An apparatus according to claim 1 further

comprising, a switch having a first input that is coupled between said

output of said source of said television signal and said data input of

said background memory, a second input that is coupled to a data output

of said background memory and a switch output that is coupled to an

input of said data processor. 6.

An apparatus according to claim 5 further comprising, means for

generating a second control signal that is coupled to a control input

of said switch, said second control signal having a first state for

enabling said switch to couple the signal that is developed at said

second input of said switch to said data processor following the time

when said first control signal is generated and having a second state,

for enabling said switch to couple the signal that is developed at said

first input thereof to said data processor following the occurrence of

the earlier of (a) a time when all the data stored in said background

memory has been read out, and (b) a time when a first time-out interval

has elapsed from a time when said data processor selects the data of a

Page Header data line. 7. An

apparatus according to claim 5 further comprising, means coupled to

said background memory, for generating, in accordance with the data of

said plurality of data lines, a serial bit data signal that contains

corresponding data lines that are read out of said background memory in

a first-in, first-out manner, said serial bit data signal being

coupled to said second input of said switch, said switch coupling said

serial bit data signal to said input of said data processor, during

said given interval, and coupling the signal that is developed at said

first input of said switch to said input of said data processor, outside

said given interval. 8. An

apparatus according to claim 1 wherein, as a result of reading out t

2. An

apparatus according to claim 1 wherein said data lines occur in said

television signal only during, corresponding vertical blanking

intervals, wherein, during said given interval, said data processor

operates in a full channel mode of operation, and wherein, prior to the

time when said first control signal is generated, said data processor

operates in a field flyback mode of operation.

3. An apparatus according to claim 1 further comprising,

means for coupling said data signal and said television signal to said

data processor such that prior to the time said first control signal is

generated said television signal is coupled to said data processor in a

manner that bypasses said background memory.

4. An apparatus according to claim 3 wherein, throughout

said given interval, said coupling means decouples said signal that

bypasses said background memory from said data processor.

5. An apparatus according to claim 1 further

comprising, a switch having a first input that is coupled between said

output of said source of said television signal and said data input of

said background memory, a second input that is coupled to a data output

of said background memory and a switch output that is coupled to an

input of said data processor. 6.

An apparatus according to claim 5 further comprising, means for

generating a second control signal that is coupled to a control input

of said switch, said second control signal having a first state for

enabling said switch to couple the signal that is developed at said

second input of said switch to said data processor following the time

when said first control signal is generated and having a second state,

for enabling said switch to couple the signal that is developed at said

first input thereof to said data processor following the occurrence of

the earlier of (a) a time when all the data stored in said background

memory has been read out, and (b) a time when a first time-out interval

has elapsed from a time when said data processor selects the data of a

Page Header data line. 7. An

apparatus according to claim 5 further comprising, means coupled to

said background memory, for generating, in accordance with the data of

said plurality of data lines, a serial bit data signal that contains

corresponding data lines that are read out of said background memory in

a first-in, first-out manner, said serial bit data signal being

coupled to said second input of said switch, said switch coupling said

serial bit data signal to said input of said data processor, during

said given interval, and coupling the signal that is developed at said

first input of said switch to said input of said data processor, outside

said given interval. 8. An

apparatus according to claim 1 wherein, as a result of reading out t he

data of said plurality of data lines in the first-in, first-out manner,

memory addresses, where said plurality of data lines are stored in

said background memory are transparent to the operation of said data

processor. 9. An apparatus

according to claim 1 wherein said data processor is included in an

integrated circuit of the same type used in a conventional teletext

decoder such that said background memory provides an add-on feature.

10. An apparatus according to claim 1

wherein said television signal comprises a teletext signal and wherein

said television apparatus comprises a teletext decoder.

11. An apparatus according to claim 10 wherein

said data lines of said television signal define corresponding pages of

teletext data, wherein said background memory is capable of containing

at a given time the data of a substantial number of said pages and

wherein, during said given interval, said data processor selects from

the data that is read out of said background memory the data of a first

page, in accordance with said one of said data lines that is a

Page-Header data line, to generate from the data of said first page

said output signal. 12. An

apparatus according to claim 1 further comprising, a page memory

wherein said output signal is stored in said page memory during said

given interval. 13. An apparatus

according to claim 1 further comprising, a switch for coupling one of

said data signal that is generated at an output of said background

memory and a second data signal, that bypasses said background memory,

to an input of said data processor when a second control signal that is

developed at a control input of said switch is at first state and for

coupling the other one of said to said input of said data processor

when said second control signal is at a second state.

14. An apparatus according to claim 13 further

comprising, means for generating, during said given interval, a first

time-out signal after an interval having a predetermined duration has

elapsed from a time when the data of said one of said data line that is

a Page Header data line has been identified in said data signal and

means responsive to said first time-out signal for generating said

second control signal in accordance with said first time-out signal .

15. An apparatus according to

claim 13 further comprising, means for generating a signal that is

indica

he

data of said plurality of data lines in the first-in, first-out manner,

memory addresses, where said plurality of data lines are stored in

said background memory are transparent to the operation of said data

processor. 9. An apparatus

according to claim 1 wherein said data processor is included in an

integrated circuit of the same type used in a conventional teletext

decoder such that said background memory provides an add-on feature.

10. An apparatus according to claim 1

wherein said television signal comprises a teletext signal and wherein

said television apparatus comprises a teletext decoder.

11. An apparatus according to claim 10 wherein

said data lines of said television signal define corresponding pages of

teletext data, wherein said background memory is capable of containing

at a given time the data of a substantial number of said pages and

wherein, during said given interval, said data processor selects from

the data that is read out of said background memory the data of a first

page, in accordance with said one of said data lines that is a

Page-Header data line, to generate from the data of said first page

said output signal. 12. An

apparatus according to claim 1 further comprising, a page memory

wherein said output signal is stored in said page memory during said

given interval. 13. An apparatus

according to claim 1 further comprising, a switch for coupling one of

said data signal that is generated at an output of said background

memory and a second data signal, that bypasses said background memory,

to an input of said data processor when a second control signal that is

developed at a control input of said switch is at first state and for

coupling the other one of said to said input of said data processor

when said second control signal is at a second state.

14. An apparatus according to claim 13 further

comprising, means for generating, during said given interval, a first

time-out signal after an interval having a predetermined duration has

elapsed from a time when the data of said one of said data line that is

a Page Header data line has been identified in said data signal and

means responsive to said first time-out signal for generating said

second control signal in accordance with said first time-out signal .

15. An apparatus according to

claim 13 further comprising, means for generating a signal that is

indica tive

of when the data of all the da&a lines that are stored in said

background memory have been read out and that is coupled to said

control input of said switch to control the state of said second

control signal. 16. A television

apparatus according to claim 1 wherein said data processor is

responsive, outside said given interval, to data lines of said

television signal that are coupled to said data processor in a manner

that bypasses said background memory.

17. An apparatus according to claim 1 further comprising, a

parallel-to-serial converter that is coupled between an output of said

background memory and an input of said data processor.

18. A television apparatus according to claim 1

wherein said background memory comprises a random access memory,

wherein said first control means comprises first sequencing means that

is coupled to an address input of said random access memory for

generating a write-in address word and wherein said second control

means comprises second sequencing means for generating a read-out

address word that is coupled to said address input.

19. An apparatus according to claim 18 wherein at

least one of said first and second sequencing means comprises a linear

feedback shift register counter.

20. An apparatus according to claim 18 wherein each of said data lines

includes a corresponding plurality of data line portions that are

stored in corresponding locations in said background memory having

corresponding addresses, wherein said first sequencing means changes

states in a cyclical manner each time a given one of said portions of

each data line is stored such that the number of states in each cycle is

equal to an integer multiple of the total number of data lines that

can be stored in said background memory in each cycle.

21. An apparatus according to claim 20 wherein

the number of memory addresses that are required for storing a given

data line is equal to 86. 22. An

apparatus according to claim 20 wherein the number of said states in

each cycle is equal to. 23. A

television apparatus according to claim 1 further comprising, a page

memory responsive to said output signal for storing said output signal

therein. 24. An apparatus

according to claim 1 wherein said data processor operates in a full

channel mode of operation throughout said given interval and wherein

said television signal contains said data lines only during

corresponding vertical blanking intervals thereof.

25. An apparatus according to claim 1 wherein said

first control means identifies, in a given video line signal, data of a

clock run-in portion of said video line signal and stores in said

background memory text data of such video line signal provided that

said data of said clock run-in portion is identified.

26. An apparatus according to claim 25 wherein said

said first control means identifies said given data line also in

accordance with data of a framing code.

27. An apparatus according to claim 1 wherein said first control

signal is indicative of when a user initiated page request has occurred

and causes said data processor to operate in a full channel mode of

operation during said given interval.

28. An apparatus according to claim 27 further comprising, means

for generating a second control signal that is indicative when a

predetermined time-out interval has elapsed from the time said first

control signal is generated, said second control signal being coupled to

said data processor for causing said data processor to start operating

in a field flyback mode of operation following said time-out interval

irrespective of whether said one of said data lines that is a Page

Header of the page requested has been selected.

29. An apparatus according to claim 28 wherein said

second control signal is generated in a microprocessor such that said

time out interval is determined by a program thereof.

30. A television apparatus responsive to an

incoming television signal containing video line signals that carry

text data, defining corresponding data lines, for generating an output

signal that is capable of providing picture information to a display

device, comprising:

tive

of when the data of all the da&a lines that are stored in said

background memory have been read out and that is coupled to said

control input of said switch to control the state of said second

control signal. 16. A television

apparatus according to claim 1 wherein said data processor is

responsive, outside said given interval, to data lines of said

television signal that are coupled to said data processor in a manner

that bypasses said background memory.

17. An apparatus according to claim 1 further comprising, a

parallel-to-serial converter that is coupled between an output of said

background memory and an input of said data processor.

18. A television apparatus according to claim 1

wherein said background memory comprises a random access memory,

wherein said first control means comprises first sequencing means that

is coupled to an address input of said random access memory for

generating a write-in address word and wherein said second control

means comprises second sequencing means for generating a read-out

address word that is coupled to said address input.

19. An apparatus according to claim 18 wherein at

least one of said first and second sequencing means comprises a linear

feedback shift register counter.

20. An apparatus according to claim 18 wherein each of said data lines

includes a corresponding plurality of data line portions that are

stored in corresponding locations in said background memory having

corresponding addresses, wherein said first sequencing means changes

states in a cyclical manner each time a given one of said portions of

each data line is stored such that the number of states in each cycle is

equal to an integer multiple of the total number of data lines that

can be stored in said background memory in each cycle.

21. An apparatus according to claim 20 wherein

the number of memory addresses that are required for storing a given

data line is equal to 86. 22. An

apparatus according to claim 20 wherein the number of said states in

each cycle is equal to. 23. A

television apparatus according to claim 1 further comprising, a page

memory responsive to said output signal for storing said output signal

therein. 24. An apparatus

according to claim 1 wherein said data processor operates in a full

channel mode of operation throughout said given interval and wherein

said television signal contains said data lines only during

corresponding vertical blanking intervals thereof.

25. An apparatus according to claim 1 wherein said

first control means identifies, in a given video line signal, data of a

clock run-in portion of said video line signal and stores in said

background memory text data of such video line signal provided that

said data of said clock run-in portion is identified.

26. An apparatus according to claim 25 wherein said

said first control means identifies said given data line also in

accordance with data of a framing code.

27. An apparatus according to claim 1 wherein said first control

signal is indicative of when a user initiated page request has occurred

and causes said data processor to operate in a full channel mode of

operation during said given interval.

28. An apparatus according to claim 27 further comprising, means

for generating a second control signal that is indicative when a

predetermined time-out interval has elapsed from the time said first

control signal is generated, said second control signal being coupled to

said data processor for causing said data processor to start operating

in a field flyback mode of operation following said time-out interval

irrespective of whether said one of said data lines that is a Page

Header of the page requested has been selected.

29. An apparatus according to claim 28 wherein said

second control signal is generated in a microprocessor such that said

time out interval is determined by a program thereof.

30. A television apparatus responsive to an

incoming television signal containing video line signals that carry

text data, defining corresponding data lines, for generating an output

signal that is capable of providing picture information to a display

device, comprising:  means for generating a first control signal

in order to select one of said data lines to be used in conjunction

with the generation of said output signal;

means for generating a first control signal

in order to select one of said data lines to be used in conjunction

with the generation of said output signal; a source of said television signal;

a first-in, first-out background memory having a data input that is coupled to said source;

first control means coupled to said background memory for controlling storage therein of corresponding data lines of said television signal, wherein prior to the time said first control signal is generated, said background memory already contains a substantial number of stored data lines of said television signal;

second control means responsive to said first control signal and coupled to said background memory for controlling during a given interval that follows the generation of said first control signal, read-out from said background memory of a plurality of stored data lines of said television signal, such that the duration of said given interval is substantially shorter than that of a corresponding interval between the occurrence of an initial data line of said plurality of data lines and the occurrence of a final data line thereof, so as to reduce access time to said plurality of data lines, said second control means controlling read-out of said plurality of data lines in a first-in, first-out manner for generating during said given interval a data signal that contains the data of said plurality of data lines;

a switch having a first input that is coupled to said source of said television signal, having a second input that is coupled to a data output of said background memory and having an output for generating a second data signal;

a data processor responsive to said second data signal for selecting said one data line to generate in accordance therewith said output signal; and

means for generating a second control signal that is coupled to a control input of said switch, said second control signal having a first state for enabling said switch to couple to said data processor after said first control signal is generated the signal that is developed at said switch second input, and having a second state for enabling said switch to couple to said data processor the signal that is developed at said first switch input following the occurrence of the earlier of (a) a time when all the data stored in said background memory has been read out, and (b) a time when a time-out interval has elapsed from a time when said data processor selects said one data line that is a Page Header.

31. A television apparatus responsive to an incoming television signal containing video lines that carry text data, defining corresponding data lines, for generating an output signal that is capable of providing picture information to a display device, comprising:

first means for generating a first control signal in order to select one of said data lines to be used in conjunction with the generation of said output signal;

second means responsive to said television signal for generating a clock signal that is indicative of timings of individual bits of a data sequence of a clock run-in portion of a data line;

a source of said television signal;

a first-in, first-out background memory having a data input that is coupled to said source;

third means coupled to said background memory and responsive to said television signal and to said clock signal for identifying in a given video line, said data sequence of said clock run-in portion of said data line and for storing in said background memory such video lines that are identified as data lines but only when individual bits of said data sequence of said clock run-in portion are correct, said first means storing said data lines such that prior to the generation of said first control signal, said background memory already contains a substantial number of stored data lines of said television signal;

fourth means responsive to said first control signal and coupled to said background memory for controlling during a given interval that follows the generation of said first control signal, read-out from said background memory of a plurality of stored data lines of said television signal, suc

h that the duration of said given interval is substantially

shorter than that of a corresponding interval between the occurrence

of an initial data line of said plurality of data lines and the

occurrence of a final data line thereof, so as to reduce access time to

said plurality of data lines, said fourth means controlling read-out

of said plurality of data lines in a first-in, first-out manner for

generating during said given interval, a data signal that contains the

data of said plurality of data lines; and

h that the duration of said given interval is substantially

shorter than that of a corresponding interval between the occurrence

of an initial data line of said plurality of data lines and the

occurrence of a final data line thereof, so as to reduce access time to

said plurality of data lines, said fourth means controlling read-out

of said plurality of data lines in a first-in, first-out manner for

generating during said given interval, a data signal that contains the

data of said plurality of data lines; and a data processor responsive to said data signal for selecting said one data line to generate in accordance therewith said output signal.

32. An apparatus according to claim 31 wherein said third means identifies said video line as data line when data sequence of a framing code portion immediately follows said data sequence of said clock run-in portion. 33. An apparatus according to claim 31 wherein said third means identifies said video line as data line by identifying a 12 bit sequence (101011100100) in data that are derived from said video line.

Description:

This

invention relates to a teletext decoder employing a so-called

background or buffer memory for storing multipages of teletext incoming

data.

This

invention relates to a teletext decoder employing a so-called

background or buffer memory for storing multipages of teletext incoming

data. Teletext is a television-based communication technique in which a given horizontal video line is utilized for broadcasting textual and graphical information encoded in a digital binary representation. Such horizontal video line signal that contains teletext data is referred to herein as a Data-line. It is assumed herein, for explanation purposes, that teletext is sent by the broadcaster only during the vertical blanking interval (VBI), when no other picture information is sent. The organization of the binary information in the broadcast signal is determined by the standard employed by the broadcaster. By way of an example only, references are made herein to a teletext based on a standard referred to by the British Broadcasting Corporation (BBC) as CEEFAX.

Each Data-line carries data synchronizing and address information and the codes for a Row of 40 characters. The synchronizing information includes a clock run-in sequence followed by an 8-bit framing code sequence. Each Data-line contains a 3 bit code referred to as the Magazine number. A teletext Page includes 24 Rows of 40 characters, including a special top Row called the Page-Header. Each ROW is contained in a corresponding Data-line. A user selected Page is intended to be displayed in place of, or added to a corresponding television picture frame. A Magazine is defined to include Pages having Data-lines containing a corresponding Magazine number. The transmission of a selected Page begins with, and includes its Page Header and ends with and excludes the next Page Header of the selected Magazine number. All intermediate Data lines carrying the selected Magazine number relate to the selected Page.

FIG.

1 illustrates a block diagram of a conventional teletext decoder that

includes an integrated circuit (IC) referred to herein as video input

processor (VIP) such as, for example, of the type SAA5231 made by

Philips Corporation. The VIP receives a baseband composite video signal

VIDEO that contains Data-lines. The VIP performs data slicing, clock

regeneration and timing synchronization functions and generates a serial

data signal DATA and an associated clock signal CLOCK Signals DATA and

CLOCK represent the data contained in the horizontal video lines.

Signals DATA and CLOCK are coupled to a second IC of the decoder,

referred to herein as computer controlled teletext IC (CCT) that

includes a data processor responsive to signals DATA and CLOCK. An

example of such CCT is IC SAA5243 made by Philips Corporation.

FIG.

1 illustrates a block diagram of a conventional teletext decoder that

includes an integrated circuit (IC) referred to herein as video input

processor (VIP) such as, for example, of the type SAA5231 made by

Philips Corporation. The VIP receives a baseband composite video signal

VIDEO that contains Data-lines. The VIP performs data slicing, clock

regeneration and timing synchronization functions and generates a serial

data signal DATA and an associated clock signal CLOCK Signals DATA and

CLOCK represent the data contained in the horizontal video lines.

Signals DATA and CLOCK are coupled to a second IC of the decoder,

referred to herein as computer controlled teletext IC (CCT) that

includes a data processor responsive to signals DATA and CLOCK. An

example of such CCT is IC SAA5243 made by Philips Corporation. The CCT performs data acquisition and interface function with a page memory that is included in the teletext decoder. For example, only a teletext Page requested by the user is derived by the CCT from the serial data and clock signals and stored in the page memory. The CCT also generates video display signals R,G, and B from the teletext data stored in the page memory to provide corresponding drive signals that contain picture information for display in the receiver picture tube (CRT), not shown.

A control microcomputer, not shown in FIG. 1, that is responsive to user initiated commands, generates control and status messages. The messages are coupled via, for example, a standard IIC bus to the CCT, for controlling the operation of the CCT.

A total of, for example, 500 Pages may be periodically transmitted during each interval of 15-45 seconds, depending on the number of Data-lines used for teletext during the VBI. Consequently, if the teletext Page is not already stored in memory when a new user page request occurs, the user may experience a nuisance as a result of waiting a maximum of 15-45 seconds until the requested Page is displayed. It may be desirable to reduce such Page access time. It may also be desirable to utilize in the teletext decoder a standard CCT such that the reduction of the access time is provided as an add-on feature to the teletext decoder.

A teletext decoder, embodying an aspect of the invention, includes a background or buffer memory that is capable of storing multi-Pages of teletext data. The portion of serial data signal DATA generated by the VIP that meets a predetermined identification criteria and, therefore, assumed to represent a Data-line is stored in the buffer memory. At any given time after the operation of the buffer memory is enabled, such as immediately after the user turns on the television receiver, the buffer memory contains, for example, the most recently received teletext Pages. The maximum number of such Pages that can be contained in the buffer memory at any given time is determined by the buffer memory Page storage capacity.

In order to reduce the size of the hardware required to identify each video line that is assumed to be a Data-line, only a limited, rather than a complete identification operation, is initially performed. The complete identification is accomplished in the CCT, during a read-out operation, when the data is read-out of the buffer memory.

In

accordance with a feature of the invention, the limited identification

operation for identifying a given Data-line is accomplished by

identifying in a video line signal data of a sequence of the clock

run-in that is immediately followed by a sequence of the framing code.

When, for example, both sequences are identified it is assumed that a

Data-line is identified. Therefore, a portion of such identified

Data-line that contains relevant data bits is stored in the buffer

memory. Otherwise, the video line information is not stored in the

buffer memory. The inclusion of the test for the data of the clock

run-in sequence, advantageously, reduces the probability that the data

that is stored is, in fact, not a Data-line.

In

accordance with a feature of the invention, the limited identification

operation for identifying a given Data-line is accomplished by

identifying in a video line signal data of a sequence of the clock

run-in that is immediately followed by a sequence of the framing code.

When, for example, both sequences are identified it is assumed that a

Data-line is identified. Therefore, a portion of such identified

Data-line that contains relevant data bits is stored in the buffer

memory. Otherwise, the video line information is not stored in the

buffer memory. The inclusion of the test for the data of the clock

run-in sequence, advantageously, reduces the probability that the data

that is stored is, in fact, not a Data-line. When the user's page request occurs, the data processor of the CCT receives the data that have been stored in the buffer memory and searches for the presence of a Data-line representing a Page Header of the requested Page. The search operation that is included in the read-out operation begins when the first data is read out of the buffer memory following the occurrence of the user's page request.

Memory read-out cycles occur between VBI's, when no teletext data is received. If the Page Header of the user requested teletext Page is found in the buffer memory in the course of such memory scan or search operation, the stored data of the Page Header is transferred to the page memory.

During the search operation, the CCT operates in the full channel operation mode. In the full channel operation mode, the Data-lines in the buffer memory are read out and transferred to the page memory in a first-in, first-out manner and without encountering large time gaps. Such large time gaps occur when teletext information is received by th

e CCT only

during the VBI's. Therefore, the search operation occurs faster than if

the Data lines were received, unbuffered, only during the VBI's. For

example, the access time to a teletext Page that is already contained

in a buffer memory capable of storing 500 teletext Pages may be reduced

to, for example, 0.8 seconds that is, advantageously, substantially

shorter than the 15-45 seconds maximum access time, referred to before.

Furthermore, should more than, for example, 600 pages be transmitted,

the access time for a page which, at the time the user page request

occurs, is not already stored in the memory, is reduced by the time

required to fill the buffer memory with teletext data.

e CCT only

during the VBI's. Therefore, the search operation occurs faster than if

the Data lines were received, unbuffered, only during the VBI's. For

example, the access time to a teletext Page that is already contained

in a buffer memory capable of storing 500 teletext Pages may be reduced

to, for example, 0.8 seconds that is, advantageously, substantially

shorter than the 15-45 seconds maximum access time, referred to before.

Furthermore, should more than, for example, 600 pages be transmitted,

the access time for a page which, at the time the user page request

occurs, is not already stored in the memory, is reduced by the time

required to fill the buffer memory with teletext data. After the Page Header is identified in the CCT, other Data-lines that are associated with the requested Page and that are stored in the buffer memory are read-out. On the other hand, if no Page Header Data-line of the requested teletext Page is found in the buffer memory in the course of the search operation, the unbuffered data received from the VIP will be coupled, after the end of the search operation, directly to the data processor of the CCT such that the buffer memory is bypassed.

When a buffer memory with large storage capacity is utilized, the read-out operation that was explained before may require a longer interval than the interval between consecutive VBI's. It may be desirable to store incoming Data-lines in the buffer memory that occur during the intervening VBI's prior to the completion of the read-out operation. If such incoming Data-lines of the Page requested by the user were not stored, an undesirable situation might have occurred in which only a partial Page is temporarily displayed on the CRT. Such temporary condition may continue until after the time when the same Page is re-transmitted.

In the teletext decoder, embodying an aspect of

the invention, the read-out operation in the buffer memory occurs only

outside the VBI's. Data-lines are stored in the buffer memory during

the VBI's that occur prior to the completion time of the read-out

operation. Therefore, Data-lines that were stored in the buffer memory

after the read-out operation has been initiated and prior to its

termination may be read-out and processed by the CCT. In this way,

advantageously an incoming Data-line that is included in the teletext

Page that is requested may be processed during the read-out operation