Single-Chip Video Processor

ITT VDP3108

Preamble:

The ITT VDP3108 Is the evolution of the DIGIT2000 chipset.

1. Introduction

The entire video processing and controlling for a color

TV has been developed on a single chip in 0.8m CMOS

technology. Modular design and submicron technology

allow the economic integration of features in all classes

of TV sets.

Open architecture is the key word to the new DSP generation.

Flexible standard building blocks have been defined

that offer continuity and transparency of the entire

system.

One IC contains the entire video and deflection processing

and builds the heart of a modern color TV. Its performance

and complexity allow the user to standardize

his product development. Hardware and software applications

can profit from the modularity as well as manufacturing,

system support or maintenance. The main

features are:

– low cost, high performance

– all digital video processing

– multi-standard color decoder PAL/NTSC/SECAM

– 3 composite, 1 S–VHS input

– integrated high-quality AD/DA converters

– sync and deflection processing

– luminance and chrominance features, e.g.

peaking, color transient improvement

– programmable RGB matrix

– various digital interfaces

– embedded RISC controller (80 MIPS)

– one crystal, few external components

– single power supply 5 V

– 0.8m CMOS Technology

– 68-pin PLCC or 64-pin Shrink DIL Package

1.1. System Architecture

Two main modules have been defined:

Video Processor and

Display Processor.

They are designed as silicon building blocks. Their partitioning

permits a variety of IC configurations with the aim

to satisfy the particular requirements of different applications.

Both, analog and digital interfaces, support

state of the art TV receivers as well as other environments.

Fig. 1–1 shows the block diagram of the singlechip

Video Processor which consists of both modules.

2. Functional Description

2.1. Analog Front End

This block provides the analog interfaces to all video inputs

and mainly carries out analog-to digital conversion

for the following digital video processing. A block diagram

is given in figure 2–1.

Most of the functional blocks in the front end are digitally

controlled (clamping, AGC and clock-DCO). The control

loops are closed by the Fast Processor (‘FP’) embedded

in the decoder.

2.1.1. Input Selector

Up to four analog inputs can be connected. Three inputs

are for input of composite video or S–VHS luma signal.

These inputs are clamped to the sync back porch and

are amplified by a variable gain amplifier. One input is

for connection of S–VHS carrier–chrominance signal.

This input is internally biased and has a fixed gain amplifier.

2.1.2. Clamping

The composite video input signals are AC coupled to the

IC. The clamping voltage is stored on the coupling capacitors

and is generated by digitally controlled current

sources. The clamping level is the back porch of the video

signal. S-VHS chroma is also AC coupled. The input

pin is internally biased to the center of the ADC input

range.

2.1.3. Automatic Gain Control

A digitally working automatic gain control adjusts the

magnitude of the selected baseband by +6/–4.5 dB in 64

logarithmic steps to the optimal range of the ADC .

The gain of the video input stage including the ADC is

213 steps/V for all three standards (PAL/NTSC/SECAM/

Y/C), with the AGC set to 0 dB.

2.1.4. Analog-to-Digital Converters

Two ADCs are provided to digitize the input signals.

Each converter runs with 20.25 MHz and has 8 bit resolution.

An integrated bandgap circuit generates the required

reference voltages for the converters.

The two ADCs are of a 2-stage subranging type.

---------------------------------------------------------------------------

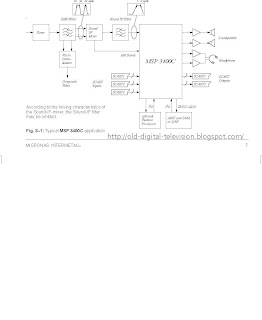

TOGHETHER WITH VIDEO PROCESSING THERE IS SOUND PROCESSING WITH MSP3400C

Multistandard Sound Processor

Release Notes: The hardware description in this

document is valid for the MSP 3400C – C8 and newer

codes. Revision bars indicate significant changes

to the previous version.

1. Introduction

The MSP 3400C is designed as single-chip Multistandard

Sound Processor for applications in analog and

digital TV sets, satellite receivers and video recorders.

The MSP-family, which is based on the MSP 2400, demonstrates

the progressive development towards highly

integrated multi-functional ICs.

The MSP 3400C, again, improves function integration:

The full TV sound processing, starting with analog

sound IF signal-in, down to processed analog AF-out, is

performed in a single chip. The IC is produced in 0.8 mm

CMOS technology, combined with high performance

digital signal processing.

The MSP 3400C 0.8 m CMOS version is fully pin and

software compatible to the 1.0 m MSP 3400 and MSP

3410. The main difference between the MSP 3400C and

the MSP 3410, consists of the MSP 3410 being able to

decode NICAM signals.

2. Features of the MSP 3400C:

2.1. Features of the Demodulator and Decoder

Sections

The MSP 3400C is designed to perform demodulation

of FM-mono TV sound and two carrier FM systems according

to the German or Korean terrestrial specs. With

certain constraints, it is also possible to do AM-demodulation

according to the SECAM system. Alternatively, the

satellite specs can be processed with the MSP 3400C.

For FM carrier detection in satellite operation, the AMdemodulation

offers a powerful feature to calculate the

carrier field strength, which can be used for automatic

search algorithms. So, the IC facilitates a first step towards

multistandard capability with its very flexible

application and may be used in TV-sets, satellite tuners,

and video recorders.

The MSP 3400C facilitates profitable multistandard capability,

offering the following advantages:

– two selectable analog inputs (TV and SAT-IF sources)

– Automatic Gain Control (AGC) for analog input: input

range: 0.14 – 3 Vpp

– integrated A/D converter for sound-IF inputs

– all demodulation and filtering is performed on chip and

is individually programmable

– no external filter hardware is required

– only one crystal clock (18.432 MHz) is necessary

– FM carrier level calculation for automatic search algorithms

and carrier mute function

– high deviation FM-mono mode (max. deviation:

approx. 360 kHz)

2.2. Features of the DSP-Section

– flexible selection of audio sources to be processed

– digital input and output interfaces via I2S-Bus for external

DSP-processors, surround sound, ADR etc.

– digital interface to process ADR (Astra Digital Radio)

together with DRP 3510 A

– performance of all deemphasis systems including

adaptive Wegener Panda 1 without external components

or controlling

– digitally performed FM-identification decoding and dematrixing

– digital baseband processing: volume, bass, treble,

5-band equalizer, loudness, pseudostereo, and basewidth

enlargement

– simple controlling of volume, bass, treble, equalizer

etc.

– increased audio bandwidth for FM-Audio-signals

(20 Hz – 15 kHz, 1 dB)

2.3. Features of the Analog Section

– three selectable analog pairs of audio baseband inputs

(= three SCART inputs)

input level: 32 V RMS,

input impedance: .25 kW

– one selectable analog mono input (i.e. AM sound),

input level: 32 V RMS,

input impedance: .10 kW

– two high quality A/D converters, S/N-Ratio: .85 dB

– 20 Hz to 20 kHz Bandwidth for SCART-to-SCARTCopy

facilities

– MAIN (loudspeaker) and AUX (headphones): two

pairs of 4-fold oversampled D/A-converters

output level per channel: max. 1.4 V RMS

output resistance: max. 5 kW

S/N-Ratio: .85 dB at maximum volume

max. noise voltage in mute mode: 310 mV (BW: 20 Hz

...16 kHz)

– one pair of four-fold oversampled D/A-converters supplying

two selectable pairs of SCART-Outputs. Output

level per channel: max. 2 V RMS, output resistance:

max. 0.5 kW, S/N-Ratio: .85 dB

(20 Hz...16 kHz).

CCU 3000, CCU 3000-I

CCU 3001, CCU 3001-I

MICRONAS INTERMETALL 4

1. Introduction

The CCU 3000, CCU 3000-I, CCU 3001, CCU 3001-I

are integrated circuits designed in 1.2 mm CMOS

technology, with the exception of CCU 3000, TC18 and

TC19, which is designed in 1 mm CMOS technology. The

CPU contained on the chips is a functionally unchanged

65C02-core, which means that for program development,

systems can be used which are on the market; including

high level language compilers.

The pin numbers mentioned in this data sheet refer to

the 68-pin PLCC package unless otherwise designated.

The CCU 3000-I is described separately in an addendum

on page 66.

1.1. Features of the CCU 3000, CCU 3000-I,

CCU 3001, CCU 3001-I

– CCU 3000 = ROM-less version of the CCU 3001

– 65C02 CPU with max. 8 MHz clock

– 32 kByte internal ROM (CCU 3001 only)

– 1344 internal Bytes RAM with stand-by option

– 51 I/O lines (CCU 3001)

– 26 I/O lines (CCU 3000)

– clock generator with programmable clock frequency

– 8 level interrupt controller

– CCU 3000, CCU 3001:

2 Multimaster IM bus interfaces

– CCU 3000-I, CCU 3001-I: 1I2C/IM bus and

1 Multimaster IM bus interface (see addendum)

– IR-input for software-decoded IR-systems

– on-chip power on, stand-by and clock supervision

logic

– on-chip watchdog

– 3 multifunctional timers

– supports memory banking (external 2MBytes)

– power down signal for external memory

– mask option: EMU mode

– programs can be written in Assembler or in “C”

– CCU 3000 TC 18/19: 1.0 mm CMOS technology, (see

addendum)

– application software available.

Functional Description

2.1. ROM

The chip is equipped with 32 kByte mask-programmable

ROM. The ROM uses up the address space from 8000H

to FFFFH. This ROM can be supplemented or replaced

externally. Only the CCU 3001 has an internal ROM.

2.2. RAM

The RAM area is split into three parts:

– page 0 (address 0 to FFH)

– page 1 (address 100H to 1FFH)

– page 3, 4, 5, 6 (address 300H to 63FH)

Page 0 offers a particularly fast access to the 65C02 and

is therefore very valuable for fast, compact programs.

Page 1 contains the stack and must therefore also have

RAM. The remaining RAM-memory follows in pages 3,

4, 5, 6, as page 2 is reserved as I/O address space. The

RAM can be kept in the stand-by mode via stand-by pin.

2.3. CPU

The CPU core is fully compatible with the 65C02 microprocessor.

However, not all the pins of the 65C02 processor

are accessible for the user outside the chip. One

switch in the control register allows the CPU to be

switched off, so that an external processor can take over

its tasks. This external processor can of course also be

an in-circuit emulator, which makes near-hardware

emulation possible, even though the status and control

lines of the internal CPU are not accessible. If an external

processor is used, all hardware blocks of the chip are

as accessible to it as if it were the internal CPU.

2.4. Clock Generator

An integrated two-pin oscillator generates the clock for

the microcontroller. The frequency created by the oscillator

can be programmed to be reduced with a divider

by the factor 1 ... 255. This enables the user to decrease

the current consumption by the controller by reducing

the working frequency as well as to increase the access

time for the (slower) external memory. This divider contains

the value 4 after a reset, so that the system can also

start with a slow external memory. If the mask-option

OSC is set (EMU version), a switch in the control register

makes it possible to receive the internal clock F2 at

XTAL2. In this case the oscillator must be external and

the clock must be fed to the pin XTAL1. In this way, the

user gets a time reference for internal operations in the

microcomputer. This is especially important with the interrupt

controller. The production version of the CCU

does not have this function!

2.5. PORT 1 to PORT 3, PORT 6 to PORT 8

8 ports belong to the system, of which 5 are 8 bits wide,

one 6 bit, one 4 bit and one 1 bit wide. All port lines of

PORTS 1 to 3 and 6 to 8 can be used as inputs or outputs

independently from each other. One register per port

defines the direction. PORT1 to PORT3 have push-pull

outputs and PORT6 to PORT8 have open drain outputs.

Even a line defined as output can be read, the pin level

being important. This property makes it possible for the

software to find desired and undesired short circuits.

Each port reserves a byte for the direction register and

the data in the I/O page. If the corresponding bit in the

direction register is set to 0, the output mode is switched

on. After a reset, all bits of a direction register are set

to 1. The falling edge of bit 7 of PORT 8 generates interrupts

if the priority of the corresponding interrupt controller

source (7) is not set to 0.

2.6. PORT 4

PORT 4 consists of only one line (LSB, P40). After a reset,

PORT 4 operates as an input only. As soon as PORT

4 is written for the first time, it is switched to output mode

(push-pull). Later read accesses read the actual level at

port 4. If bit 3 in the control word is active, P4 is used as

an R/W-line. If the internal CPU is active, R/W is an output

line, otherwise it is an input. But P4 has another, very

important function during RESET. The level at P4 during

RESET decides whether the control word is read from

the internal ROM (FFF9H) or from the external memory.

It is therefore important that the desired level during RESET

is set at P4. An internal pull-down resistor of approx.

100 kW is integrated in the CCU 3001, which ensures

that the control word is read by the internal ROM. The

external control word access is obtained via an external

pull-up resistor of approx. 5 kW. The CCU 3000 has an

internal pull-up resistor at P4 (external ROM access).

The further mode of operation of the CCU 3000, CCU

3001 depends only on the control word though.

Please note that this mode is always necessary for

the CCU 3000 since this device does not have internal

ROM!

2.7. I/O-Lines P50 to P55

The 6 additional I/O-lines have a two-fold function:

– input or output line (open drain output) or

– fully decoded I/O-select lines (push-pull outputs)

As a rule these lines can be used as input or output lines.

As soon as ports 1 to 4 are used as system bus, they are

lost as I/O-channels. However, a total of 48 port lines (24

inputs and outputs each) can be reconstructed without

difficulties (1 housing for 8 lines), if the additional 6 I/Olines

of the CCU 3000, CCU 3001 are switched into the

port select mode. They then represent the select lines of

the original ports 1 to 3. Each line can be defined as I/O

or port select line separately. In the I/O-page three bytes

are needed.

Thank you for this excellent job.

ReplyDelete