Digital Board Unit 1-663-206-15

The main core of all functions of DSP and control of the set are concentrated in this dual-board unit.

On one face we have the analog frontend and Digital sound porcessing + video processing

TDA9144

I2C-bus controlled, alignment-free

PAL/NTSC/SECAM decoder/sync

processor with PALplus helper

demodulator

FEATURES

· Multi-standard colour decoder and sync processor for

PAL, NTSC and SECAM

· PALplus helper demodulator

· PALplus helper blanking and EDTV-2 blanking

· I2C-bus controlled

· I2C-bus addresses hardware selectable

· Pin compatible with TDA9141

· Alignment free

· Few external components

· Designed for use with baseband delay lines

· Integrated video filters

· Adjustable luminance delay

· Noise detector with I2C-bus read-out

· Norm/no_norm detector with I2C-bus read-out

· CVBS or Y/C input, with automatic detection possibility

· CVBS output provided I2C-bus address 8A is used

· Vertical divider system

· Two-level sandcastle signal

· VA synchronization pulse (3-state)

· HA synchronization pulse or clamping pulse CLP

input/output

· Line-locked clock output (6.75 MHz or 6.875 MHz) or

stand-alone I2C-bus output port

· Stand-alone I2C-bus input/output port

· Colour matrix and fast YUV switch

· Comb filter enable input/output with subcarrier

frequency

· Internal bypass mode of external delay line for PALplus

and NTSC applications

· Low power standby mode with 3-state YUV outputs

· Fast blanking detector with I2C-bus read-out

· Blanked or unblanked sync on Yout by I2C-bus bit BSY

· internal MACROVISION gating for the horizontal PLL

enabled by bus bit EMG.

GENERAL DESCRIPTION

The TDA9144 is an I2C-bus controlled, alignment-free

PAL/NTSC/SECAM decoder/sync processor with helper

demodulator for PALplus signals and blanking facilities for

PALplus and EDTV-2 signals. The TDA9144 has been

designed for use with baseband chrominance delay lines,

and has a combined subcarrier frequency/comb filter

enable signal for communication with a PAL/NTSC comb

filter.

The IC can process both CVBS input signals and Y/C input

signals. The input signal is available on an output pin, in

the event of a Y/C signal, it is added into a CVBS signal.

The sync processor provides a two-level sandcastle, a

horizontal pulse (CLP or HA pulse, bus selectable) and a

vertical (VA) pulse. When the HA pulse is selected, a

line-locked clock (LLC) signal is available at the output port

pin (6.75 MHz or 6.875 MHz).

A fast switch can select either the internal Y signal with the

UV input signals, or YUV signals made of the RGB input

signals. The RGB input signals can be clamped with either

the internal or an external clamping signal.

Two pins with an input/output port and an output port of the

I2C-bus are available.

The I2C-bus address of the TDA9144 is hardware

programmable.

The TDA9144 is pin compatible with the TDA9141

(multistandard decoder/sync processor).

CXD2044

Digital Comb Filter (NTSC/PAL/PAL-M/PAL-N)

Description

The CXD2044Q is an adaptive intra-field comb

filter compatible with NTSC, PAL, PAL-M and PAL-N

systems, and can provide high-precision Y/C

separation with a single chip.

Features

• Intra-field Y/C separation by adaptive processing

• 8-bit A/D converter (1-channel)

• 8-bit D/A converter (2-channel)

• Four 1H delay lines

• Clock 4fsc

SDA 5273

MEGATEXT and MEGATEXT PLUS IC

Single chip teletext IC

Analog CVBS-input with onchip clamping circuitry

Slicer

Supports level 1, 2.5 and 3.5 ETSI teletext standard

Stores up to 14 teletext pages on chip

Stores up to 2048 teletext pages with external

16 M memory

SDA 5275: full level 2.5 processing

Analog RGB-output

41 latin script languages

12´10 character size

Parallel display attributes

64 from 4096 colors selectable

Enhanced flash modes

Dynamically redefinable character set (DRCS, PCS)

Pixel graphics

Fullscreen display (64´32 or 80´24 character positions)

Horizontal and vertical scrolling

Graphic cursors

4:3 and 16:9 display

Multinorm display (50/60/100/120 Hz)

RISC-processor

Firmware downloadable

2C / 3 wire UART-interface (1 Mbit/s)

Independent clocks for acquisition and display

Tools for greatly simplified software development

24-Kbyte on-chip reconfigurable DRAM

44160-bit character ROM

One external crystal for all standards

-----------------------------------------------------------

On second face we have the entire 100HZ scan rate technology + additional features.

- SAA4952WP Memory controller

FEATURES

· Support for acquisition, display and deflection PLL

· 50/100 Hz (or 60/120 Hz) scan conversion

· Progressive scan 50 Hz/1250 lines (60 Hz/1050 lines)

interlaced or 50 Hz/625 lines (60 Hz/525 lines)

non-interlaced in serial memory structure

· 50 Hz/625 lines (60 Hz/525 lines) mode support for a

PALplus system and basic features

· Acquisition frequencies 12, 13.5, 16 and 18 MHz and

display frequencies of 27, 32 and 36 MHz (2fH) in every

combination, horizontal compression (support for 4 : 3

and 14 : 9 display on a 16 : 9 screen) and horizontal

zoom

· Configured as a three clock system with a fixed 27 MHz

deflection clock (deflection controlled by the TDA9151)

· Configured as a two-clock system (deflection controlled

by e.g. TDA9152)

· Single clock for 50 Hz vertical and 15.625 kHz

horizontal frequency

· Support of new IC generations [PAN-IC (SAA4995WP),

VERIC (SAA4997H), MACPACIC (SAA4996H) and

LIMERIC (SAA4945H)]

· Support for two or one field memories

· Still picture

· Support for memory types such as TMS4C2970/71

· Internal simple Multi-PIP (3 ´ 3) or (4 ´ 4) conversion

· Multi-PIP support with an external PIP module/full

performance

· Programmable via microcontroller port

· Capability of reading the length of incoming fields via

microcontroller port

· Golden SCART option (clock generation for TDA9151)

· Acquisition is able to operate with external sync and

clock of digital sources (slave mode)

· Generator mode for the display, stable still picture or

OSD in the event of no input source.

GENERAL DESCRIPTION

The memory controller SAA4952WP is the improved

version of the SAA4951WP. The circuit has been designed

for high-end TV sets using 2fH technics. For basic feature

modules a 1fH mode can be activated. In this situation the

controller supplies the system with a line-locked clock.

The new device has been designed to be able to operate

in the hardware environment of the SAA4951WP.

The circuit provides all necessary write, read and clock

pulses to control different field memory concepts.

Furthermore the drive signals for the horizontal and

vertical deflection power stages are also generated.

The device is connected to a microcontroller via an 8-bit

data bus. The microcontroller receives commands via the

I2C-bus. Due to this fact the START and STOP conditions

of the main output control signals are programmable and

the SAA4952WP can be set in different function modes

depending on the TV feature concept that is used.

- SDA9280 Display Processor

Features

• 8-Bit amplitude resolution of each input component

Input sample frequency up to 30 MHz

Application in flicker reduction systems possible

• Four input data formats

4:1:1 luminance and chrominance parallel

(8 + 4 wires)

4:2:2 CCIR 656-format (8 wires)

4:2:2 luminance and chrominance parallel (2 x 8 wires)

4:4:4 all components parallel (3 x 8 wires)

• Two different representations of input data

Positive dual code

2’s complement code

• Three D/A converters on-chip

9-Bit amplitude resolution

80 MHz maximal clock frequency

• DCTI (digital color transient improvement)

A digital algorithm improves the sharpness of vertical color edges

avoiding the artifacts of analog CTI-circuits

• Luminance peaking

Separate programmable lowpass, bandpass, and highpass digital filters

• High performance digital interpolation for anti-imaging

Two-fold oversampling

Simplification of external analog postfiltering

• 16:9 compatibility

Signal compression for displaying 4:3-signals on16:9-screens

Signal expansion for displaying 16:9-signals on 4:3-screens

Full screen display of 4:3 letter box pictures

- TDA4780

RGB video processor with

automatic cut-off control and

gamma adjust

FEATURES

· Gamma adjust

· Dynamic black control (adaptive black)

· All input signals clamped on black-levels

· Automatic cut-off control, alternative: output clamping

on fixed levels

· Three adjustable reference voltage levels via the

I2C-bus for automatic cut-off control

· Luminance/colour difference interface

· Two luminance input levels allowed

· Two RGB interfaces controlled by either fast switches or

by the I2C-bus

· Two peak drive limiters, selection via the I2C-bus

· Blue stretch; selection via the I2C-bus

· Luminance output for Scan Velocity

Modulation (SCAVEM)

· Extra luminance output; same pin can be used as hue

control output e.g. for the TDA4650 and TDA4655

· Non standard operations like 50 Hz vertical at 32 kHz

horizontal are also possible

· Either 2 or 3 level sandcastle pulse applicable

· High bandwidth for 32 kHz application

· White point adjusts via the I2C-bus

· Average beam current and improved peak drive limiting

· Two switch-on delays to prevent discoloration during

start-up

· All functions and features programmable via the I2C-bus

· PAL/SECAM or NTSC matrix selection.

GENERAL DESCRIPTION

The TDA4780 is a monolithic integrated circuit with a

luminance and a colour difference interface for video

processing in TV receivers. Its primary function is to

process the luminance and colour difference signals from

a colour decoder which is equipped e.g. with the

multistandard decoder TDA4655 or TDA9160 plus delay

line TDA4661 or TDA4665 and the Picture Signal

Improvement (PSI) IC TDA467X or from a feature module.

The required input signals are:

· Luminance and negative colour difference signals

· 2 or 3-level sandcastle pulse for internal timing pulse

generation

· I2C-bus data and clock signals.

Two sets of analog RGB colour signals can also be

inserted, e.g. one from a peritelevision connector

(SCART plug) and the other one from an On-Screen

Display (OSD) generator. The TDA4780 has I2C-bus

control of all parameters and functions with automatic

cut-off control of the picture tube cathode currents.

It provides RGB output signals for the video output stages.

In clamped output mode it can also be used as an RGB

source.

The main differences with the sister type TDA4680 are:

· Additional features; namely gamma adjust, adaptive

black, blue stretch and two different peak drive limiters

· The measurement lines are triggered by the trailing

edge of the vertical component of the sandcastle pulse

· I2C-bus receiver only; automatic white level control is

not provided; the white levels are determined directly by

the I2C-bus data

· The TDA4780 is pin compatible (except pin 18) with the

TDA4680. The I2C-bus slave address can be used for

both ICs. When a function of the TDA4780 is not

included in the TDA4680, the I2C-bus command is not

executed. Special commands (except control bit FSWL)

for the TDA4680 will be ignored by the TDA4780.

- SAA4945 LIne MEmory noise Reduction IC (LIMERIC)

FEATURES

· 2-D adaptive vertically recursive noise reduction

· Noise reduction for Y, U and V signals in 4 : 1 : 1 format

· Single 5 V ±10% power supply

· Communication by means of serial communication

protocol 83C654 (SNERT bus)

· Via SNERT bus, 10 different types of noise reduction

selectable; the noise reduction function can also be

disabled

· Phase relation write enable input/output signal

simultaneously switchable over one clock period w.r.t.

input/output samples

· 8-bit wide data processing for Y, U and V; in unsigned

format (Y signal) and in 2’s complement (U and V

signals)

· One fixed line locked clock operation frequency up to

16 MHz (typical)

· Exactly one line delay.

GENERAL DESCRIPTION

The SAA4945H, LIMERIC (LIne MEmory noise Reduction

IC) is a 2-D recursive noise reduction filter for both

luminance and colour difference signals. The noise

reduction is automatically adapted to the global noise level

in the image. Ten different preferences of noise reduction

can be set using a synchronous receiver transmitter bus;

SNERT (Synchronous No parity Eight bit Receive

Transmit) bus. Alternatively, the noise reduction can be

switched off. The LIMERIC is generally placed directly

after the ADC in the feature box and works fully in the 1fh

(50/60 Hz) domain.

- P83C654EBA/560

- TDA8755 YUV 8-bit video low-power analog-to-digital interface

FEATURES

· 8-bit resolution

· Sampling rate up to 20 MHz

· TTL compatible digital inputs

· 3-state TTL outputs

· U, V two's complement outputs

· Y binary output

· Power dissipation of 550 mW (typical)

· Low analog input capacitance, no buffer amplifier

required

· High signal-to-noise ratio over a large analog input

frequency range

· Track-and-hold included

· Clamp functions included

· UV multiplexed ADC

· 4 : 1 : 1 output data encoder

· Stable voltage regulator included.

APPLICATIONS

· High speed analog-to-digital conversion for video signal

digitizing

· 100 Hz improved definition TV (IDTV).

GENERAL DESCRIPTION

The TDA8755 is a bipolar 8-bit video low-power

analog-to-digital conversion (ADC) interface for YUV

signals. The device converts the YUV analog input signal

into 8-bit coded digital words in a 4 : 1 : 1 format at a

sampling rate of 20 MHz. The U/V signals are converted in

a multiplexed manner. All analog signal inputs are digitally

clamped and a fast precharge is provided for start-up.

All digital inputs and outputs are TTL compatible. Frame

synchronization is supported in a multiplexed manner.

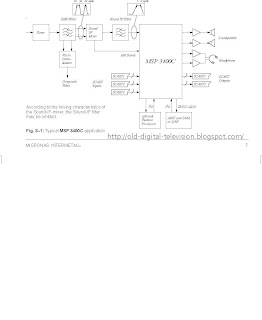

Multistandard Sound Processor

Release Notes: The hardware description in this

document is valid for the MSP 3400C – C8 and newer

codes. Revision bars indicate significant changes

to the previous version.

1. Introduction

The MSP 3400C is designed as single-chip Multistandard

Sound Processor for applications in analog and

digital TV sets, satellite receivers and video recorders.

The MSP-family, which is based on the MSP 2400, demonstrates

the progressive development towards highly

integrated multi-functional ICs.

The MSP 3400C, again, improves function integration:

The full TV sound processing, starting with analog

sound IF signal-in, down to processed analog AF-out, is

performed in a single chip. The IC is produced in 0.8 mm

CMOS technology, combined with high performance

digital signal processing.

The MSP 3400C 0.8 m CMOS version is fully pin and

software compatible to the 1.0 m MSP 3400 and MSP

3410. The main difference between the MSP 3400C and

the MSP 3410, consists of the MSP 3410 being able to

decode NICAM signals.

2. Features of the MSP 3400C:

2.1. Features of the Demodulator and Decoder

Sections

The MSP 3400C is designed to perform demodulation

of FM-mono TV sound and two carrier FM systems according

to the German or Korean terrestrial specs. With

certain constraints, it is also possible to do AM-demodulation

according to the SECAM system. Alternatively, the

satellite specs can be processed with the MSP 3400C.

For FM carrier detection in satellite operation, the AMdemodulation

offers a powerful feature to calculate the

carrier field strength, which can be used for automatic

search algorithms. So, the IC facilitates a first step towards

multistandard capability with its very flexible

application and may be used in TV-sets, satellite tuners,

and video recorders.

The MSP 3400C facilitates profitable multistandard capability,

offering the following advantages:

– two selectable analog inputs (TV and SAT-IF sources)

– Automatic Gain Control (AGC) for analog input: input

range: 0.14 – 3 Vpp

– integrated A/D converter for sound-IF inputs

– all demodulation and filtering is performed on chip and

is individually programmable

– no external filter hardware is required

– only one crystal clock (18.432 MHz) is necessary

– FM carrier level calculation for automatic search algorithms

and carrier mute function

– high deviation FM-mono mode (max. deviation:

approx. 360 kHz)

2.2. Features of the DSP-Section

– flexible selection of audio sources to be processed

– digital input and output interfaces via I2S-Bus for external

DSP-processors, surround sound, ADR etc.

– digital interface to process ADR (Astra Digital Radio)

together with DRP 3510 A

– performance of all deemphasis systems including

adaptive Wegener Panda 1 without external components

or controlling

– digitally performed FM-identification decoding and dematrixing

– digital baseband processing: volume, bass, treble,

5-band equalizer, loudness, pseudostereo, and basewidth

enlargement

– simple controlling of volume, bass, treble, equalizer

etc.

– increased audio bandwidth for FM-Audio-signals

(20 Hz – 15 kHz, 1 dB)

2.3. Features of the Analog Section

– three selectable analog pairs of audio baseband inputs

(= three SCART inputs)

input level: 32 V RMS,

input impedance: .25 kW

– one selectable analog mono input (i.e. AM sound),

input level: 32 V RMS,

input impedance: .10 kW

– two high quality A/D converters, S/N-Ratio: .85 dB

– 20 Hz to 20 kHz Bandwidth for SCART-to-SCARTCopy

facilities

– MAIN (loudspeaker) and AUX (headphones): two

pairs of 4-fold oversampled D/A-converters

output level per channel: max. 1.4 V RMS

output resistance: max. 5 kW

S/N-Ratio: .85 dB at maximum volume

max. noise voltage in mute mode: 310 mV (BW: 20 Hz

...16 kHz)

– one pair of four-fold oversampled D/A-converters supplying

two selectable pairs of SCART-Outputs. Output

level per channel: max. 2 V RMS, output resistance:

max. 0.5 kW, S/N-Ratio: .85 dB

(20 Hz...16 kHz).

SAA4990H Progressive scan-Zoom and Noise

reduction IC (PROZONIC)

FEATURES

· Progressive scan conversion

(262.5 to 525 or 312.5 to 625 lines/field)

· Field rate up-conversion (50 to 100 Hz or 60 to 120 Hz)

· Line flicker reduction

· Noise and cross-colour reduction

· Variable vertical sample rate conversion

· Movie phase detection

· Synchronous No parity Eight bit Reception and

Transmission (SNERT) interface.

GENERAL DESCRIPTION

The Progressive scan-Zoom and Noise reduction IC,

abbreviated as PROZONIC, is designed for applications

together with:

SAA4951WP Economy Controller (ECO3)

SAA4952H (memory controller)

SAA7158WP Back END IC (BENDIC)

SAA4995WP PANorama IC (PANIC)

SAA4970T ECOnomical video processing Back END IC

(ECOBENDIC)

TMS4C2970/71 (serial field memories)

TDA8755/8753A (A/D converter 4 : 1 : 1 format)

83C652/54 type of microcontroller.

No comments:

Post a Comment

The most important thing to remember about the Comment Rules is this:

The determination of whether any comment is in compliance is at the sole discretion of this blog’s owner.

Comments on this blog may be blocked or deleted at any time.

Fair people are getting fair reply. Spam and useless crap and filthy comments / scrapers / observations goes all directly to My Private HELL without even appearing in public !!!

The fact that a comment is permitted in no way constitutes an endorsement of any view expressed, fact alleged, or link provided in that comment by the administrator of this site.

This means that there may be a delay between the submission and the eventual appearance of your comment.

Requiring blog comments to obey well-defined rules does not infringe on the free speech of commenters.

Resisting the tide of post-modernity may be difficult, but I will attempt it anyway.

Your choice.........Live or DIE.

That indeed is where your liberty lies.

Note: Only a member of this blog may post a comment.