MIVAR 21L1E TVD CHASSIS TV3536/1

Tuner MIVAR TV3701 and Frequency synthesizer + prescaler and Video IF and Sound 1 IF In One module.

Frequency synthesizer + prescaler with SDA3302 (SIEMENS)

Video IF with TDA8341 (PHILIPS)

Mixer + osc with TDA5330T (PHILIPS)

PHILIPS TDA5330T VHF, UHF and Hyperband mixer/oscillator for TV and VCR 3-band tuners

GENERAL DESCRIPTION

GENERAL DESCRIPTIONThe TDA5330T is a monolithic integrated circuit that performs the band A, band B and band C mixer/oscillator functions

in TV and VCR tuners. This device gives the designer the capability to design an economical and physically small 3-band

tuner which will be capable of meeting the most stringent requirements e.g. FTZ or FCC. The tuner development time

can be drastically reduced by using this device.

Features

· Balanced mixer with a common emitter input for band A

· Amplitude-controlled oscillator for band A

· Balanced mixer with common base input for band B and C

· Balanced oscillator for band B and C

· Local oscillator buffer output for external prescaler

· SAW filter preamplifier with an output impedance of 100 W

· Bandgap voltage stabilizer for oscillator stability

· Electronic bandswitch

------------------------------------------------------------

PHILIPS TSA5511 1.3 GHz Bidirectional I2C-bus

FEATURES

· Complete 1.3 GHz single chip system

· Low power 5 V, 35 mA

· I2C-bus programming

· In-lock flag

· Varicap drive disable

· Low radiation

· Address selection for Picture-In-Picture (PIP), DBS

tuner (3 addresses)

· Analog-to-digital converter

· 8 bus controlled ports (5 for TSA5511T), 4 current

limited outputs (1 for TSA5511T), 4 open collector

outputs (bi-directional)

· Power-down flag

APPLICATIONS

· TV tuners

· VCR Tuners

GENERAL DESCRIPTION

The TSA5511 is a single chip PLL frequency synthesizer

designed for TV tuning systems. Control data is entered

via the I2C-bus; five serial bytes are required to address

the device, select the oscillator frequency, programme the

eight output ports and set the charge-pump current. Four

of these ports can also be used as input ports (three

general purpose I/O ports, one ADC). Digital information

general purpose I/O ports, one ADC). Digital informationconcerning those ports can be read out of the TSA5511 on

the SDA line (one status byte) during a READ operation.

A flag is set when the loop is “in-lock” and is read during a

READ operation. The device has one fixed I2C-bus

address and 3 programmable addresses, programmed by

applying a specific voltage on Port 3. The phase

comparator operates at 7.8125 kHz when a 4 MHz crystal

is used.

controlled synthesizer

CHASSIS TV3536/1 THOMSON TEA2164 SWITCH MODE POWER SUPPLY PRIMARY CIRCUIT

.POSITIVE AND NEGATIVE OUTPUT CURRENT

UP TO 1.2AAND – 1.7A .A TWO LEVEL COLLECTOR CURRENT LIMITATION

UP TO 1.2AAND – 1.7A .A TWO LEVEL COLLECTOR CURRENT LIMITATION.COMPLETE TURN OFF AFTER LONG DURATION

OVERLOADS .UNDER AND OVER VOLTAGELOCK-OUT .SOFT START BY PROGRESSIVE CURRENT

LIMITATION .DOUBLE PULSE SUPPRESSION .BURST MODE OPERATION UNDER STANDBY

CONDITIONS

DESCRIPTION

In amaster slave architecture, the TEA2164control

IC achieves the slave function. Primarily designed

for TV receivers and monitors applications, this

circuit provides an easy synchronizationand smart

solution for low power stand by operation.

Located at the primary side the TEA2164 Control

IC ensures :

- the power supply start-up

- the power supply control under stand-by conditions

- the process of the regulation signals sent by the

master circuit located at the secondary side

- directbasedrive of the bipolarswitching transistor

- the protection of the transistor and the power

supply under abnormal conditions.

II. GENERAL DESCRIPTION

In a master slave architecture, the TEA2164 Control

IC, located at the primary side of an off line

power supply achievesthe slave function ;whereas

the master circuit is located at the secondary side.

The link between both circuits is realized by a small

pulse transformer

In the operation of the master-slave architecture,

four majors cases must be considered :

- normal operating

- stand-bymode

- power supply start-up

- abnormal conditions : off load, short circuit, ...

II.1. Normal Operating (master slave mode)

In this configuration, the master circuit generatesa

pulse widthmodulatedsignal issued from themonitoring

of the output voltage which needs the best

accuracy (in TV applications : the horizontal deflection

stagesupplyvoltage).Themaster circuit power

supply can be supplied by another output.

The PWM signal are sent towards the primary side

through small differentiating transformer. For the

TEA2164 positive pulses are transistor switchingon

commands ; and negative pulses are transistor

switching-offcommands (Figure 4). In this configuration,

only by synchronizing the master oscillator,

the switching transistor may be synchronized with

an external signal.

II.2. Stand-by Mode

In this configuration the master circuit no longer

sends PWM signals, the structure is not synchronized

; and the TEA2164 operates in burst mode.

The average power consumption at the secondary

side may be very low 1W 3 P 3 6W (as it is

consumed in TV set during stand by).

By action on the maximum duty cycle control, a

primary loop maintains a semi-regulation of the

output voltages.Voltage on feed-back is applied on

Pin 9.

Burst period is externally programmedby capacitor

C1.

II.3. Power Supply Start-up

After the mains have been switched-on, the VCC

storage capacitor of the TEA2164 is charged

through a high value resistor connected to the

rectified high voltage.When Vcc reaches VCC start

threshold (9V typ), the TEA2164 starts operatingin

threshold (9V typ), the TEA2164 starts operatinginburst mode. Since available output power is low in

burst mode the output power consumption must

remain low before complete setting-up of output

voltage. In TV application it can be achieved by

maintaining the TV in stand-by mode during startup.

Overvoltage Protection

When VCC exceeds VCC max, an internal flip-flop

stops output conduction signals. The circuit will

start again after the capacitor C1 discharge ; it

means : after loss of synchronization or after Vcc

stop crossing (Figure 7).

In flyback converters, this function protects the

power supply against output voltage runaway.

MIVAR 21L1E TVD CHASSIS TV3536/1 Switch-mode power supply with burst mode standby operation:

In a switch mode power supply, a first switching transistor is coupled to a primary winding of a transformer for generating pulses of a switching current. A secondary winding of the transformer is coupled via a switching diode to a capacitor of a control circuit for developing a control signal in the capacitor. The control signal is applied to a mains coupled chopper second transistor for generating and regulating supply voltages in accordance with pulse width modulation of the control signal. During standby operation, the first and second transistors operate in a burst mode that is repetitive at a frequency of the AC mains supply voltage such as 50 Hz. In the burst mode operation, during intervals in which pulses of the switching current occur, the pulse width and peak amplitude of the switching current pulses progressively increase in accordance with the waveform of the mains supply voltage to provide a soft start operation in the standby mode of operation within each burst group.

Description:

The invention relates to switch-mode power supplies.

In a typical switch mode power supply (SMPS) of a television receiver the AC mains supply voltage is coupled to a bridge rectifier. An unregulated direct current (DC) input supply voltage is produced. A pulse width modulator controls the duty cycle of a chopper transistor switch that applies the unregulated supply voltage across a primary winding of a flyback transformer. A flyback voltage at a frequency that is determined by the modulator is developed at a secondary winding of the transformer and is rectified to produce DC output supply voltages such as a voltage B+ that energizes a horizontal deflection circuit of the television receiver and a voltage that energizes a remote control unit.

During normal operation, the DC output

supply voltages are regulated by the pulse width modulator in a

negative feedback manner. During standby operation, the SMPS is

required to generate the DC output supply voltage that energizes the

remote control unit. However, most other stages of the television

receiver are inoperative and do not draw supply currents.

Consequently, the average value of the duty cycle of the chopper

transistor may have to be substantially lower during standby than

during normal operation.

During normal operation, the DC output

supply voltages are regulated by the pulse width modulator in a

negative feedback manner. During standby operation, the SMPS is

required to generate the DC output supply voltage that energizes the

remote control unit. However, most other stages of the television

receiver are inoperative and do not draw supply currents.

Consequently, the average value of the duty cycle of the chopper

transistor may have to be substantially lower during standby than

during normal operation.Because of, for example, storage time limitation in the chopper transistor, it may not be possible to reduce the length of the conduction interval in a given cycle below a minimum level. Thus, in order to maintain the average value of the duty cycle low, it may be desirable to operate the chopper transistor in an intermittent or burst mode, during standby. During standby, a long dead time interval occurs between consecutively occurring burst mode operation intervals. Only during the burst mode operation interval switching operation occurs in the chopper transistor. The result is that each of the conduction intervals is of a sufficient length.

In accordance with an aspect of the invention, burst mode operation intervals are initiated and occur at a rate that is determined by a repetitive signal at the frequency of the AC mains supply voltage. For example, when the mains supply voltage is at 50 Hz, each burst mode operation interval, when switching cycles occur, may last 5 milliseconds and the dead time interval when no switching cycles occur, may last during the remainder portion or 15 milliseconds. Such arrangement that is triggered by a signal at the frequency of the mains supply voltage simplifies the design of the SMPS.

The burst mode operation intervals that occur in standby operation are synchronized to the 50 Hz signal. During each such interval, pulses of current are produced in transformers and inductances of the SMPS. The pulses of current occur in clusters that are repetitive at 50 Hz. The pulses of current occur at a frequency that is equal to the switching frequency of the chopper transistor within each burst mode operation interval. Such qurrent pulses might produce an objectionable sound during power-off or standby operation. The objectionable sound might be produced due to possible parasitic mechanical vibrations as a result of the pulse currents in, for example, the inductances and transformers of the SMPS.

In accordance with another aspect of the invention, the change in the AC mains supply voltage during each period causes the length of the conduction interval in consecutively occurring switching cycle during the burst mode operation interval to increase progressively. Such operation that occurs during each burst mode operation interval may be referred to as soft start operation. The soft start operation causes, for example, gradual charging of capacitors in the SMPS. Consequently, the parasitic mechanical vibrations are substantially reduced. Also, the frequency of the switching cycles within each burst mode operation interval is maintained above the audible range for further reducing the level of such audible noise during standby operation.

A switch mode power supply, embodying an aspect of the invention, for generating an output supply voltage during both a standby-mode of operation and during a run-mode of operation includes a source of AC mains input supply voltage. A control signal at a given frequency is generated. A switching arrangement energized by the input supply voltage and responsive to the first control signal produces a switching current during both the standby-mode of operation and the run-mode operation. The output supply voltage is generated from the switching current. An arrangement coupled to the switching arrangement and responsive to a standby-mode/run-mode control signal and to a signal at a frequency that is determined by a frequency of the AC mains input supply voltage controls the switching arrangement in a burst mode manner during the standby-mode of operation. During a burst interval, a plurality of switching cycles are performed and during an alternating dead time interval no switching cycles are performed. The two intervals alternate at a frequency that is determined by the frequency of the AC mains input supply voltage.

1. A chopped power supply control circuit intended to receive periodic

regulation control signals and to produce periodic square waves enabling

a main switch of the power supply, the square waves having a variable

width as a function of their regulation control signals, which circuit

comprises:

means for detecting the presence of regulation control signals,

a

very low frequency oscillator controlled by the detection means, this

oscillator producing, in the absence of regulation signals, a succession

of very low frequency periodic cycles, the oscillator being inhibited

by the regulation control signal detection means,

a high

frequency oscillator producing chopping signals palliating the absence

of regulation signals for producing enabling square waves,

an

inhibition means for allowing transmission of the chopping siganls to

the switch only during a first phase of each very low frequency periodic

cycle and for preventing such transmission during the rest of the

cycle, the first phase of each cycle having a duration which is long

compared with the period of the high frequency oscillator and short

compared with the period of the very low frequency oscillator.

2.

The control circuit as claimed in claim 1, wherein said high frequency

oscillator has a free oscillation period slightly greater than the

period of the regulation control signals and it is synchronized by these

signals when they are present.

3. The control circuit as claimed

in claim 1, wherein the regulation control signals comprise a positive

pulse followed by a negative pulse, one of them being used for

synchronizing the high frequency oscillator, the positive pulse being

transmitted through the inhibition means to a set input of a flip flop

for triggering off the beginning of conduction of the main switch, and

the negative pulse being transmitted to a reset input of the flip flop

for causing stopping of the conduction of the switch.

4. The control circuit according to claim 1 further comprising:

a

threshold comparator for receiving a signal measuring the current in

said switch and for outputting a signal stopping the conduction of said

switch when a threshold is exceeded;

means for varying the

threshold of said comparator including a means for producing a first

threshold value during normal operation of said circuit, a means for

producing a second threshold value at the beginning of said first phase

of said very low frequency cycle, said second threshold corresponding to

a current in said switch which is lower than during said normal

operation, and a means for producing a gradually decreasing threshold

during said first phase of said very low frequency cycle.

5.

The control circuit as claimed in claim 4, wherein said very low

frequency oscillator is a relaxation oscillator delivering a saw tooth

signal and the means for varying the threshold is driven by the output

of the very low frequency oscillator.

6. The control circuit as

claimed in one of claims 4 and 5, wherein another threshold converter is

provided receiving a signal of measurement of the current in the main

switch and delivering a signal for complete inhibition of enabling of

the switch when the current in the switch exceeds a third threshold

value higher than the first value.

7. The control circuit as

claimed in claim 6, wherein said inhibition signal delivered by the

other comparator is cancelled out when the circuit, after having

partially or totally ceased to be supplied with power, is again normally

supplied.

Description:

BACKGROUND OF THE INVENTION

1. Field of the Invention

The present invention relates to stabilized power supplies called chopped power supplies.

A

chopped power supply operates in the following way: a transformer

primary winding receives a current which comes for example from a

rectifier bridge receiving the power from the AC mains. The current in

the transformer is chopped by a switch (for example a power transistor)

placed in series with the primary winding.

A circuit controlling

the transistor establishes periodic square waves for enabling the

transistor. For the duration of the square wave the current is allowed

to pass; outside the square wave, the passage of the current is

prevented.

On one (or more) secondary windings of the transformer

an AC voltage is then collected. This voltage is rectified and filtered

so as to obtain a DC voltage which is the DC output voltage of the

chopped power supply.

To stabilize the value of this DC voltage,

the cyclic periodic conduction ratio of the switch is adjusted, that is

to say the ratio between the conduction time and the disablement time in

a chopping period.

2. Discussion of Background

In a

chopped power supply architecture proposed by the applicant and shown in

FIG. 1, two integrated circuits are used. One of the circuits, CI1,

serves for controlling the base of a power transistor Tp for applying

thereto periodic enabling and disabling control signals. The space

control circuit CI1 is placed on the primary winding side (EP) of the

transformer (TA) for reasons which will be better understood further on

in the description. The integrated circuit, regulation circuit CI2, is

on the contary placed on the secondary side (winding ES1) and its serves

for examining the output voltage Vs of the power supply for elaborating

regulation signals which it transmits to the first integrated circuit

through a small transformer TX. The first integrated circuit CI1 uses

these regulation signals for modifying the cyclic conduction ratio of

the switching transistor TP and thus for regulating the output voltage

Vs of the power supply.

We will come back in more detail hereafter to the circuit shown in FIG. 1.

Numerous problems arise during designing of a chopped power supply, and the problems with which we will be particulary concerned here are problems of starting up the power supply and problems of safety should over voltages or over currents occur at different points in the circuit. The first problem which is met with is that of starting up the power supply : on switching on, the regulation circuit CI2 will tend to cause the base control circuit CI1 to generate square waves of maximum cyclic ratio until the power supply has reached its nominal output voltage. This is all the more harmful since there is then a heavy current drain on the side of the secondary windings which are connected to initially discharged filtering capacitors. There is a risk of destruction of the power transistor through over-currents during the start-up phase.

Progressive start-up circuits have already been proposed which limit the duration of the enabling square waves during a start-up phase, on switching on the device; the U.S. Pat. No. 3,959,714 describes such a circuit in which charging of a capacitor from switch-on defines initially short square waves which gradually increase in duration until these square waves reach the duration which the regulation circuit normally assigns thereto. The short square waves have priority; but, since they become gradually longer during the start-up phase, after a certain time they cease to have priority; this time is defined by the charging time constant of the capacitor.

Another problem which arises is the risk of accidental overcurrents, or sometimes overvoltages which may occur in the circuit. These over-currents and over-voltages may cause damage and often result in the destruction of the power transistor if nothing is done to eliminate them. In particular, a short circuit at the output of the stabilized power supply rapidly destroys the power transistor. If the short circuit occurs on start-up of the power supply, it is not the gradual start-up system with short square waves which gradually increase which will allow the over-currents resulting from this short circuit to be efficiently accomodated.

Finally, another problem, particularly important in an architecture such as the one shown in FIG. 1, is the risk of disappearance of the regulation signals which should be emitted by the regulation circuit CI2 and received by the base control circuit CI1: these signals determine not only the width of the square waves for enabling the power transistor but also their periodicity; in other words, they serve for establishing the chopping frequency, possibly synchronized from a signal produced on the secondary side of the transformer. The disappearance of these signals causes a particular disturbance which must be taken into account.

Furthermore, the architecture of FIG. 1, in which the secondary circuits have been voluntarily separated galvanically from the primary circuits, is such that the base control circuit may function rapidly after switch on, as will be explained further on, whereas the regulation circuit CI2 can only function if the chopped power supply is in operation; consequently, at the beginning, the base control circuit CI1 does not receive any regulation signals and this difficulty must be taken into account.

SUMMARY OF THE INVENTION

In an attempt to resolve as well as possible the whole of these different problems which relate to safety against accidental disturbances in the operation of the power supply (initial start-up being able to be considered moreover as transitory disturbed operating phase), the present invention proposes an improved chopped power supply control circuit which accomplishes a function of gradual start-up of the power supply on switch-on and a function of passing to the safety mode should a malfunction occur such as a disappearance of appropriate regulation signals: the safety mode consists of a succession of very low frequency periodic cycles, each cycle consisting in a gradual start-up attempt during a first phase which is short compared with the period of the cycle and long compared with the chopping period of the chopped power supply, the first phase being followed by a pause at the end of the cycle, and periodic cycles succeeding each other until normal operation of the power supply is established or re-established; a very low frequency oscillator establishes these cycles when the power supply is not normal operating conditions (start up or malfunction); this oscillation is disabled when normal operation is ascertained; a high frequency oscillator generates a burst of chopping signals palliating the absence of regulation signals; these signals are transmitted solely during the first phase of each cycle; they are inhibited during the second phase.

According to a very important characteristic of the invention; gradual start-up operates not by limiting the duration of the square waves from the charging of a capacitor with a fixed time constant, but by limiting the current in the power transistor to a maximum value, this maximum value increasing gradually during the start-up phase, overshooting of this current value causing interruption of the power transistor.

Thus, even in the case of a quasi short circuit, the value of a current in the transistor is limited, which was not the case in gradual start-up circuits of the prior art.

More precisely, the chopped power supply control circuit, intended to receive periodic regulation control signals and to produce periodic square waves for enabling a main switch of the power supply, the square waves having a variable width depending on the regulation control signals; comprises:

a means for detecting the presence of regulation control signals,

a very low frequency oscillator controlled by the detection means, this oscillator establishing, in the case of absence of regulation signals, a succession of very low frequency periodic cycles, the oscillator being inhibited by the detection means when regulation control signals are present,

a high frequency oscillator producing chopping signals palliating the absence of regulation signals for producing enabling square waves,

an inhibition means only allowing chopping signals to be transmitted to the switch during a first phase of each very low frequency periodic cycle and for preventing such transmission during the rest of the cycle, the first phase of each cycle having a duration which is long compared with the period of the high frequency oscillator and short compared with the period of the very low frequency oscillator.

Preferably, the high frequency oscillator has a free oscillation period slightly greater than the period of the regulation control signals and it is synchronized by these signals when they are present.

The regulation control signals may comprise a positive pulse followed by a negative pulse, one of them serving for synchronizing the high frequency oscillator, the positive pulse being transmitted through the inhibition means to a set input of a flip flop for enabling the switch, whereas the negative pulse is transmitted to the reset input of this flip flop for disabling.

In so far as limiting the current to a gradually increasing value during the start-up cycles is concerned, a threshold comparator (92) is preferably provided receiving a signal for measuring the current in the switch in order to generate a signal for disabling the switch should the threshold be exceeded and a means (90) for causing the threshold of the comparator to vary in the following way:

under normal operating conditions the threshold is fixed at a first value;

at the beginning of the first phase of each very low frequency periodic cycle, the threshold passes suddenly from the first value to a second value corresponding to a lower current in the switch;

during the first phase of each cycle the threshold passes gradually back from the second value to the first one.

BRIEF DESCRIPTION OF THE DRAWINGS

Other features and advantages of the invention will be clear from the following detailed description made with reference to the accompanying drawings in which:

FIG. 1 shows a general chopped power supply diagram using two integrated circuits placed respectively on the primary side and on the secondary side of a transformer,

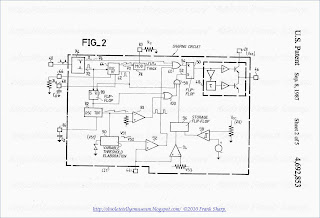

FIG. 2 shows a diagram of an integrated circuit for controlling the power transistor placed on the primary side,

FIGS. 3 to 6 show timing diagrams of signals at different points of the circuit, and

FIG. 7 shows a circuit detail for producing a variable threshold.

DESCRIPTION OF THE PREFERRED EMBODIMENTS

Referring

again to FIG. 1, which represents a chopped power supply architecture

given by way of example illustrating the utility of the invention, the

line of the public electric mains has been designated by the reference

10 (mains at 100 or 220 volts, 50 or 60 hertz). This line is connected

through a filter 12 to the input of a rectifier bridge 14 whose output

is connected on the one hand to a primary electric ground, shown

throughout by a black triangle pointing downward and, on the other hand,

to one end of the primary winding EP of the power transformer TA.

Referring

again to FIG. 1, which represents a chopped power supply architecture

given by way of example illustrating the utility of the invention, the

line of the public electric mains has been designated by the reference

10 (mains at 100 or 220 volts, 50 or 60 hertz). This line is connected

through a filter 12 to the input of a rectifier bridge 14 whose output

is connected on the one hand to a primary electric ground, shown

throughout by a black triangle pointing downward and, on the other hand,

to one end of the primary winding EP of the power transformer TA.A filtering capacitor 16 is placed in parallel across the outputs of the rectifier bridge 14. The other end of the primary winding is connected to the collector of a switching transistor TP whose emitter is connected to the primary ground through a small current measuring resistor 18.

The transformer has several secondary windings which are preferably isolated galvanically from the mains and connected for exmaple to a secondary electric ground isolated galvanically from the primary ground.

Here, each of the secondary windings has one end connected to the secondary ground. The other end feeds a respective low pass filtering capacitor through a respective rectifier diode.

The description hereafter will refer to a single secondary winding ES1, connected by a diode 20 to a capacitor 22. The DC output voltage of the chopped power supply is the voltage Vs at the terminals of the capacitor 22; but of course other DC output voltages may be obtained at the terminals of the other filtering capacitors connected to secondary windings. These output voltages forms stabilized power supply voltages for user circuits not shown. By way of example, a secondary winding ES2 supplies a stabilized voltage of a few volts for the integrated regulation circuit CI2, which has already been discussed. It can be verified therefore in this connection that this circuit is not fed with power and cannot therefore deliver signals as long as the chopped power supply is not operating.

The same goes a priori for the integrated circuit CI1 controlling the base of the power transistor TP, which circuit is supplied with a stabilized voltage delivered from a secondary winding ES3, a diode 24 and a capacitor 26 (it will be noted in passing that this winding, although a secondary winding, is connected to the primary ground and not to the secondary ground, for the very simple reason that the integrated circuit CI1 is necessarily coupled galvanically to the primary).

However, since start-up of the chopped power supply must be ensured, it is provided for the power supply terminal 28 of the integrated circuit CI1 to be also connected directly to the mains through a high resistor 30 and a diode 32; this is possible since the integrated circuit CI1 is connected to the primary gorund; this is not possible for the integrated circuit CI2 which must remain galvanically isolated from the mains. As soon as the chopped power supply is operating normally, the stabilized DC voltage delivered by winding ES3 and diode 24 take precedence over the voltage from the mains and diode 32; this diode 32 is disabled and the direct supply from the mains no longer occurs after the initial start-up phase.

The role of integrated circuits CI1 and CI2 will now be described.

The regulation circuit CI2 receives, from a divider bridge 34 placed at the terminals of the capacitor 22 that is to say at the output of the stabilized power supply, information concerning the value of the voltage to be stabilized Vs.

This information is compared with a reference value and applied to a pulse width modulator which produces periodic square waves of variable width depending on the value of the output voltage Vs; the lower Vs the wider the square waves.

The square waves are produced at the chopping frequency of the chopped power supply. This frequency is therefore established on the secondary side of the circuit; it is generated either inside circuit CI2, or outside in a circuit not shown, in the form of a saw tooth voltage at the chosen chopping frequency. This saw tooth voltage is used in a way known per se for obtaining width modulation.

The variable width square waves, at the chopping frequency, are applied to a primary winding 36 of a small transformer TX whose secondary winding 38, isolated galvanically from the primary, delivers positive and negative pulses at the rising and falling fronts respectively of the variable width square waves.

It is these pulses, whose position and frequency are determined by the regulation circuit CI2, which form regulation signals applied to an input 40 of the base control circuit CI1.

Transformer TX is formed by a few turns wound on a ferrite rod, the turns of the primary and the turns of the secondary being sufficiently spaced apart from each other for complying with the standards of galvanic isolation between primary circuits and secondary circuits in the chopped power supply.

The integrated base control circuit CI1 comprises different inputs among which have already been mentioned a power supply input 28 and a regulation signal input 40; a current measuring input 44 is connected to the current measuring resistor 18; an inhibition input monitors the magnetization condition of a transformer. Finally, inputs may be provided for connecting elements (resistors, capacitors) which should form part of the integrated circuit itself but which, for technological reasons (space) or for practical reasons (possiblities of adjustment by the user) are mounted on the outside.

The integrated circuit CI1 finally comprises an output 46 which is intended to be coupled by direct galvanic coupling to the base of the power transistor Tp. This output delivers square waves for enabling and disabling the transistor Tp.

FIG. 2 shows the general architecture of the integrated circuit CI1, limited to the elements which relate more particularly to the invention.

The output 46 of the circuit is the output of a push-pull amplification stage designated as a whole by the reference 48, this stage comprising preferably two separate amplifiers one of which receives enabling square waves and the other of which receives disabling signals formed by enabling square waves inverted and delayed by a few microseconds. Such amplifiers are now well known.

The enabling signals are delivered by a logic flip flop 50 having a set input 52 and a reset input 54. The set input causes the power transistor to be enabled. The reset input causes it to be disabled.

The set input 52 receives the pulses which pass through a logic AND gate 58, so that enabling only occurs if several conditions are simultaneously satisfied; one unsatisfied condition will be sufficient to inhibit enabling.

The reset input 54 receives the pulses which pass through a logic OR gate 60, so that disabling (after enabling) will occur as soon as a disabling signal is present at one of the inputs of this gate.

In the diagram of FIG. 2, the AND gate 58 has three inputs. One of these inputs receives periodic pulses from an output 62 of a high frequency oscillator 64; the other inputs serve for inhibiting the transmission of these pulses.

The oscillator defines the periodicity of the chopping of the power supply (20 kilohertz for example). Under normal operating conditions, the oscillator is synchronized by the regulation signals; under start-up conditions, it is self oscillating at a free frequency defined by the values of a resistor Ro and a capacitor Co external to the integrated circuit CI1 and connected respectively to an access terminal 66 and an access terminal 68. The free frequency fo is in theory slightly lower than the normal chopping frequency.

Oscillator 64 is a relaxation oscillator which produces at an output 70 a saw tooth whose zero return is caused by the appearance of a positive pulse arriving at terminal 40. This is why oscillator 64 is shown with one input connected to an output 72 of a separation and shaping circuit 74 which receives the regulation signals from terminal 40 and shapes them while separating the positive pulses from the negative pulses. The shaping circuit 74 has two outputs; 72 for the positive pulses, 76 for the negative pulses (the notation of positive pulses, negative pulse will be kept for distinguishing the enabling pulses and the disabling pulses even if the shaping circuit produces pulses of the same sign at both its outputs 72 and 76).

Oscillator 64 has two outputs: one output 70 delivering a saw tooth and one output 62 delivering a short pulse at the time of the zero return of the saw tooth.

A pulse width modulator 78 is connected on the one hand to the output 70 of the oscillator and on the other to a reference voltage adjustable by means of a resistor R1 external to the integrated circuit and connected to a terminal 80 giving access to the circuit. Modulator 78 delivers periodic square waves synchronized with the signals of the oscillator, these square waves defining a maximum conduction duration Tmax beyond which the power transistor must be disabled in any case for safety reasons. These square waves and modulator 78 are applied to an input of the OR gate 60. The duration Tmax is adjustable by means of the external resistor R1.

The elements which have just been described ensure the essential part of the operation under normal conditions of the integrated circuit CI1. The following elements are more specifically provided for controlling abnormal operation or start-up of the power supply.

A very low frequency oscillator 82 is connected to an external capacitor C2 through an access terminal 86. This external capacitor allows the very low frequency oscillation to be adjusted. The frequency may be 1 hertz for example.

Oscillator 82 is a relaxation oscillator delivering a saw tooth. This saw tooth is applied on the one hand to a threshold comparator 88 which causes periodic square waves to be produced synchronized with the very low frequency saw tooth of the oscillator. These square waves have a brief duration compared with the period of a saw tooth; this duration is fixed by the threshold of comparator 88; it may be for example be 10% of the period; it must be long compared with the free oscillation period of the high frequency oscillator 64 so that a burst of numerous pulses from the high frequency oscillator may be emitted and used during this 10% of the very low frequency period; this burst defines at start-up attempt during the first part of a start-up cycle; it is followed by a pause during the rest of the period, i.e. during the remaining 90%.

The oscillator only serves at start up; it is inhibited when regulation signals appear at terminal 40 and indicate that the chopped power supply is operating. This is why a control has been shown for inhibiting this oscillator, connected to the output 72 of the shaping circuit 74 through a flip flop 89. This flip flop switches under the action of the pulses appearing at the output 72. It is brought back to its initial state by the output 62 of oscillator 64 when there are no longer any pulses at output 71.

The saw teeth of the very low frequency oscillator are further transmitted to a circuit 90 producing a variable threshold whose purpose is to produce a threshold signal (current or voltage) having a first value Vs1 under normal operating conditions, and a threshold cyclically variable between a first value and a second value under start-up conditions. The method of varying this threshold will be described further on, but it may already be noted that the variation is driven by the very low frequency saw tooth.

The threshold signal produced by circuit 90 is applied to an input of a comparator 92 another input of which is connected to the terminal 44 already mentioned, for receiving at this input a signal representative of the amplitude of the current flowing through the power switch. The output of comparator 92 is applied to an input of the OR gate 60. It therefore acts for disabling the power transistor Tp, after it has been enabled, disabling occurring as soon as overshooting of the threshold (fixed or variable) defined by circuit 90 has been detected.

Another threshold comparator 94 has one input connected to the current measuring terminal 44 whereas another input receives a signal representing a third threshold value Vs3. The third value Vs3 corresponds to a current in the switch higher than the first value Vs1 defined by the circuit 90. The output of comparator 94 is connected through a storage flip flop 96 to an input of the AND gate 58 so that, if the current in the power switch exceeds the third threshold value Vs3, disabling of transistor Tp is not caused (such disabling being caused by the comparator 92) but any new enabling of the transistor is inhibited. Such inhibition lasts until the flip flop 96 is switched back to its initial state corresponding to normal operation.

In theory, this resetting will only take place when the integrated circuit CI1 has ceased to be supplied normally with power and is again switched on. For example, resetting of flip flop 96 is caused through a hysteresis threshold comparator 98 which compares a fraction of the power supply voltage Vcc of the circuit (taken from terminal 28) with a reference value and which resets the flip flop when Vcc first passes above this reference after dropping below another reference value lower than the first one (hysteresis).

Finally, it may be stated that the output of the flip flop 89 (which detects the presence of regulation signals at terminal 40 therefore normal operation of the power supply), is connected to an input of an OR gate 100 which receives at another input the output of comparator 88 so that the output of comparator 88 ceases to inhibit enabling of transistor Tp (inhibition during 90% of the very low frequency cycles) as soon as operation of the power supply has become normal.

OPERATION OF THE BASE CONTROL CIRCUIT

This operation will be described by illustrating it with voltage wave forms inside the chopped power supply and inside the integrated circuit CI1.

(a) Start-up on switching on

At the outset, the integrated circuit is not supplied with power at all.

The voltage at the power supply terminal 28 increases from 0 to a value Vaa which is not the nominal value Vcc but which is a lower value supplied by diode 32 and resistor 30 (cf. FIG. 1) as long as the chopped power supply does not deliver its nominal output voltage Vcc at terminal 28. Vaa is a voltage sufficient for ensuring practically normal operation of all the elements of the circuit CI1. Vaa is also sufficient for reinitializing the flip flop 96 which, as soon as that happens, no longer inhibits enabling of the power transistor Tp.

There are no regulation signals at the input 40. Consequently, the high frequency oscillator oscillates with its free frequency and the very low frequency oscillator also oscillates (it is not inhibited by the flip flop 89 since this latter does not receive any regulation signals from the output 72 of the shaper circuit 74).

The very low frequency oscillator 82 and comparator 88 define periodic cycles of start-up attempts repeated at a very low frequency.

Each cycle comprises a first part defined by the square waves of short duration at the output of comparator 88, and a second part formed by the end of the very low frequency period; the first part is an effective attempt at start-up. The second part is a pause if the effective attempt has failed. The pause lasts much longer than the effective attempt so as to limit power consumption.

During the first part of the cycle, the enabling signals delivered by the high frequency oscillator 64 are allowed to pass through the AND gate 58. They are then prevented from passing. Each pulse from the output 62 of the oscillator 64 enables the transistor Tp. There is therefore a burst of enabling pulses which is emitted for about 10% of the very low frequency period.

During start-up, the current intensities in the transistor tend to be very high. It is essentially comparator 92 which causes interruption of the conduction, after each enabling pulse delivered by oscillator 64, as soon as the current exceeds the threshold imposed by the variable threshold elaboration circuit 90. If comparator 92 does not cause enabling, modulator 78 will do so in any case at the end of the time Tmax.

The threshold elaboration circuit, which delivers to the comparator 90 a first fixed threshold value Vs1 under normal operating conditions (i.e. when the very low frequency oscillator 82 is disabled by the flip flop 89), delivers a variable threshold as a function of the saw tooth of the very low frequency oscillator in in the following way:

at the initial outset of a start-up attempt cycle (beginning of the saw tooth or zero return of the preceding saw tooth), the threshold passes suddenly from the first value Vs1 to a second value Vs2 corresponding to a lower current than the first value, then this threshold increases gradually (because driven by the very low frequency saw tooth) from the second value to the first. The growth time coincides preferably with the duration of a start-up attempt square wave (i.e. about 10% of the very low frequency period).

Then the threshold is stabilized at the first value Vs1 until the end of the period, but in any case if the circuit has not started up at that time, comparator 88 closes gate 58, through the OR gate 100 and inhibits any further enabling of the power transistor during the rest of the very low frequency period (90%). It is then the second part of the start-up attempt cycle which takes place: a pause during which the pulses of oscillator 64 are not transmitted through the AND gate 58.

Thus, the start-up cycles act from two points of view: on the one hand, a burst of enabling pulses is emitted (10% of the time) then stopped (90% of the time) until the next cycle; on the other hand, during this burst, the current limitation threshold passes gradually from its second relatively low value to its normal higher value.

Consequently, if the peak amplitude of the current in transistor Tp is observed during the start-up bursts, it can be seen that in practice it increases linearly from the second value to the first. Thus gradual start-up is obtained by a much more efficient action than that which consists simply for example in causing the duration Tmax to increase from a low value to a nominal value.

If start-up is not successful, a new burst of enabling pulses is transmitted during the first part of the next cycle (it will be recalled that this cycle is repeated about once per second and that the burst may last 100 milliseconds).

If start-up is successful, regulation signals appear at terminal 40. These signals are shaped by circuit 74. They cause the very low frequency oscillator 82 to be stopped by the flip flop 89 which prevents the zero return of the saw tooth. Furthermore, flip flop 89 sends through the OR gate 100 a signal for cancelling out the inhibition effect imposed by the comparator 88. Finally, as soon as start-up is successful, the regulation signals cause the high frequency oscillator 64 to be synchronized.

FIG. 3 illustrates the high frequency signals during the start-up period:

line a: saw tooth at the output 70 of the oscillator 64 (free oscillation at frequency fo, period To),

line b: pulses for enabling the transistor Tp : these pulses coincide with the zero return of the saw tooth signal (output 62 of oscillator 64);

line c: output square waves from modulator 78 defining the maximum cyclic conduction time of the transistor,

line d: pulses delivered comparator 92 when the current in the switch exceeds the threshold (gradually increasing during start up) defined by the circuit 90.

The conduction of transistor Tp, after being enabled by a pulse from line b, is stopped either by the square waves of line c if the current threshold is not exceeded, or by an output pulse from comparator 92.

FIG. 4 shows the very lwo frequency signals during the start-up cycles. The diagrams are not to the same time scale as in FIG. 3 since it will be recalled that an example of the frequency of the high frequency oscillator 64 is 20 kilohertz whereas an example of the very low frequency of oscillator 82 is 1 hertz. The high frequency pulses have however been shown symbolically in FIG. 4, in number more limited than in reality for facilitating the representation.

line e: saw tooth output of the very low frequency oscillator (frequency f2, period T2),

line f: output of comparator 88 showing the first phase (start-up attempt by allowing conduction of transistor Tp) and the second phase (pause by inhibiting the conduction of each very low frequency start up cycle,

line g: pulses delivered by the freely oscillating high frequency oscillator,

line h: bursts of enabling pulses at the output of the AND gate 58,

line i: diagram of the cyclic variation of the threshold produced by circuit 90 during the start-up cycles: fixed value Vs1 in theory, sudden drop to Vs2 at the beginning of the very low frequency saw tooth, and gradual rise from Vs2 to Vs1, driven by the linear growth of the saw tooth, during the start-up burst.

(b) Operation of the power supply under normal established operating

conditions

The very low frequency oscillator is not operating.

The high frequency oscillator is synchronized by the regulation signals.

The zero return of the high frequency saw tooth, coinciding with the positive pulses of the regulation signals, causes enabling of transistor Tp (no inhbition by the AND gate 58 during normal operating conditions). The negative pulses cause disabling, through the OR gate 64, except if such disabling has been caused:

either by overshooting of the first current threshold value, detected by the comparator 92,

or by the modulator 78 if the time interval between the positive pulse and the negative pulse which immediately follows it is greater than the maximum duration Tmax which is allowed.

FIG. 5 shows the high frequency signals under normal operating conditions,

line j: alternate positive and negative pulses received at the input 40 of the circuit (these are the regulation signals defining the times at the beginning and end of conduction of the power transistor Tp),

line k: shaped pulses at the output 72 of the separation and shaping circuit 74: they correspond to the positive pulses only of the regulation signals,

line l: saw tooth at the output 70 of oscillator 62; the saw tooth is synchronized with the regulation signals in that its zero return coincides with the pulses of line k,

line m: pulses at output 62 of oscillator 64; these pulses are emitted during zero returns of the saw tooth of line l,

line n: output square waves of modulator 78 further defining the maximum conduction time of the power transistor;

line o: pulses from the output 76 of the separation and shaping circuit 74: these pulses correspond to the negative pulses of the regulation signals,

line p: as a reminder, pulses have been shown at the output of comparator 92 in the case where the current in the power transistor exceeds the threshold corresponding to Vs1.

The conduction of transistor Tp, after being enabled by a pulse of line k, is normally stopped by the pulse from line o which immediately follows it, or, more exceptionally by the pulses from line p if the threshold Vs1 is exceeded before the apearance of the pulse of line o, or else, by the square waves of line n if the threshold is not exceeded and if the pulse of line o appears after the beginning of a square wave of line n.

FIG. 6 shows the very low frequency signals at the time of passing over from start-up conditions to normal operating conditions (same scale as FIG. 4).

line q: regulation signals at the input 40; these signals are initially absent and appear at a certain moment,

line r: output of the flip flop 89 indicating the absence then the presence of regulation signals,

line s: very low frequency saw tooth which rises to its high level and does not drop again if the output o the flip flop 89 is at the high level (indicating the presence of regulation signals)

line t: output of the OR gate 100 showing initially a square wave of short duration, delivered by comparator 88 and causing a start-up burst (cf. FIG. 4), then blocking at the high level which prevents subsequent inhibition of the AND gate 58 by the comparator 88.

(c) Safety mode in the case of a malfunction

The safety mode consists in fact in establishing start-up cycles as during switch on.

These cycles are triggered by start up of the very low frequency oscillator 82 when the regulation signals disappear at input 40.

Flip flop 89 returns to an intial state when it no longer receives pulses from the output 72 of the separation and shaping circuit 74. Thus, oscillator 82 will be able to oscillate again and the above described cycles are established.

(d) Serious incident: very high over current

Whatever the operating conditions, normal or start-up, over-currents in transistor Tp are detected by the comparator 92 and cause interruption of the conduction. But if there is for example a short circuit at the output of the power supply, an over-current may occur such that the current continues to increase before the conduction has time to be completely interrupted. In this case, it is provided for the threshold comparator 94 to deliver an order inhibiting the enabling when the current in transistor Tp exceeds a third threshold value which is for example greater by 30% than the first value. This inhibition order is stored by flip flop 96 which switches under the action of the comparator and disables the AND gate 58; flip flop 96 can only come back to its initial state when the integrated circuit, after having partially or totally ceased to be supplied with power, is again normally supplied. For example, the power supply must be switched off and switched on again to allow pulses to pass again for enabling the transistor Tp.

To

finish this description, there has been shown in FIG. 7 one example of

the circuit 90 which produces a variable threshold for the comparator

92: the very low frequency saw tooth deliveredy by the oscillator is

applied to a voltage/current converter 102 which produces a saw tooth

current increasing from 0 to a maximum value.

This current is

applied to a series assembly of a voltage source 104 (value Vs2) and a

resistor 106. A voltage clipper, represented by a Zener diode 108 (value

of the conduction threshold: Vs1) is connected in parallel across the

assembly 104, 106. The junction point between the output of the

converter 102, resistor 106 and the voltage clipper 108 forms the output

of circuit 90 and is connected to the input of comparator 92. Thus,

when the saw tooth returns to zero, the output voltage of circuit 90 is

Vs2. Then it increases as the current in the resistor 106 increases

(linearly). When the voltage at the terminals of resistor 106 reaches

and exceeds the value Vs1-Vs2, the voltage clipper conducts and diverts

the current surplus so that the output voltage remains limited to Vs1.

THOMSON TEA2162 / TEA2164 / TEA2165 WORKING OF CONTROL CIRCUIT FOR A CHOPPED POWER SUPPLY WITH PROGRESSIVE START UP :

A chopped power supply control circuit is provided i ntended

to receive regulation control signals and to produce square waves for

enabling a switch. A current comparator measures the current in the

switch and opens the switch when the threshold is exceeded. Under normal

operating conditions the threshold is fixed. Under start-up conditions

of should a malfunction occur a threshold variation circuit causes the

threshold to vary gradually from a low value to its normal value. Thus

the risk of over-current at start-up is reduced.

ntended

to receive regulation control signals and to produce square waves for

enabling a switch. A current comparator measures the current in the

switch and opens the switch when the threshold is exceeded. Under normal

operating conditions the threshold is fixed. Under start-up conditions

of should a malfunction occur a threshold variation circuit causes the

threshold to vary gradually from a low value to its normal value. Thus

the risk of over-current at start-up is reduced.

1.

A chopped power supply control circuit intended to receive regulation

control signals and to produce square waves for enabling a mains switch

of the power supply, wherein said square waves having a variable width

depending on the signals received, said circuit comprising:

a

current limiting circuit including a threshold comparator receiving at

one input a signal and at another input a threshold signal;

a

means for said comparator to generate a signal for disabling the switch

when the threshold is exceeded, in order to ensure gradual start-up of

the chopped power supply at the beginning of its operation and in the

case of a disturbance of operation;

a means for establishing a variable threshold signals in response to circuit means which

establish a first fixed threshold value under normal established operating conditions,

establish periodically a threshold variation cycle in the opposite case, this cycle comprising

means

to cause the threshold to pass to a second value at a time representing

the beginning of a periodic threshold variation cycle, the second

threshold value corresponding to a lower current in the switch,

means to bring the threshold gradually back from the second value to the first in a first part of the threshold variation cycle,

means for maintaining the threshold at the first value until the end of the current cycle,

means

to begin a second start-up cycle again at the end of the current cycle

if regulation control signals are still not received at the end of the

first cycle,

means for stopping the establishment of threshold variation cycles when regulation control signals are received.

2.

The control circuit as claimed in claim 1 wherein the first part of

each periodic cycle corresponds to a short time compared with the period

of the cycle and a long time compared with the switching period of the

chopped power supply.

3. The control circuit as claimed in claim

1, wherein a very low frequency oscillator is provided for defining the

periodic two phase threshold variation cycles, said oscillator being

inhibited by the reception of appropriate regulation control signals.

4.

The control circuit as claimed in claim 3, wherein said very low

frequency oscillator is a relaxation oscillator delivering a saw tooth

signal driving the threshold establishment means for establishing:

a sudden variation of the threshold at the time of the zero return of the saw tooth,

a slow linear increase of the threshold at the beginning of the saw tooth.

5.

The control circuit as claimed in claim 4, wherein a high frequency

oscillator is provided producing chopping signals palliating the absence

of regulation signals for the production of square waves enabling the

switch and an inhibition means for allowing transmission of these

signals only during the first phase of each periodic cycle.

6.

The control circuit as claimed in claim 5, wherein said high frequency

oscillator has a free oscillation period slightly greater than the

period of the regulation control signals and it is synchronized by these

signals when they are received.

7. The control circuit as

claimed in claim 1, wherein a second threshold comparator is provided

for receiving a signal representative of the current in the switch and

delivering a signal completely inhibiting enabling of the switch in the

case where the current in the switch exceeds a third threshold value

greater than the first value, the signal only ceasing when the circuit,

after having partially or totally ceased to be supplied with power, is

again normally supplied.

Description:

BACKGROUND OF THE INVENTION

The present invention relates to stabilized power supplies called chopped supplies.

A

chopped power supply operates in the following way: a primary transfer

winding receives a current which is for example delivered by a rectifier

bridge receiving the power of the AC mains. The current in the

transformer is chopped by a switch (for example a power transistor)

placed in series with the primary winding.

A circuit for

controlling the transistor produces periodic square waves for enabling

the transistor. A current is allowed to pass for the duration of the

square waves; outside the square wave, the current cannot pass.

On

one (or more) secondary windings of the transformer, an AC voltage is

collected. This is rectified and filtered so as to obtain a DC voltage

which is the output DC voltage of the chopped power supply.

For

stabilizing the value of this DC voltage, the cyclic period conduction

ratio of the switch is adjusted, that is to say the ratio between the

duration of conduction and the duration of non conduction in a chopping

period.

In

chopped power supply architecture proposed by the applicant and shown

in FIG. 1, two integrated circuits are used. One of the circuits CI1,

serves for controlling the base of a power transistor Tp for applying

thereto periodic enabling and disabling control signals. The base

control circuit CI1 is placed on the primary winding side (EP) of the

transformer (TA) for reasons which will be better understood in the rest

of the description. The other integrated circuit, regulation circuit

CI2, is on the contrary placed on the secondary side (winding ES1) and

it serves for examining the output voltage Vs of the power supply for

forming regulation signals which it transmits to the first integrated

circuit through a small transformer TX. The first integrated circuit CI1

uses these regulation signals for modifying the cyclic conduction ratio

of the switching transistor Tp and thus regulating the output voltage

Vs of the power supply.

We will come back further on in more detail to the circuit of FIG. 1.

Numerous problems arise during the design of a chopped power supply, and here we will consider more particularly the problems of starting up the supply and the problems of safety in the case of over voltages or over currents at different points in the circuit.

The first problem which is met with is that of starting up the power supply: at switch on, the regulation circuit CI2 will tend to cause the base control circuit CI1 to generate maximum cyclic ratio square waves until the power supply has reached its nominal output voltage. This is all the more harmful since there is a high current drain on the side of the secondary windings which are connected to initially discharged filtering capacitors. There is a risk of destruction of the power transistor through an overcurrent during the start up phase.

Circuits for gradual start up have already been proposed which limit the duration of the enabling square waves during a start up phase, on switching on the device; the U.S. Pat. No. 3,959,714 describes such a circuit in which charging of a capacitor from switch-on defines initially short square waves of gradually increasing duration until these square waves reach the duration which the regulation circuit normally assigns to them. The short square waves have priority; but, since they become gradually longer during the start up phase, they cease to have priority after a certain time; this time is defined by the charging time constant of the capacitor.

Another problem to be reckoned with is the risk of accidental over-currents, or sometimes over-voltages which may occur in the circuit. These overcurrents and over-voltages may be very detrimental and often result in the destruction of a power transistor if nothing is done to eliminate them. In particular, a short circuit at the output of the stabilized power supply rapidly destroys the power transistor. If this short circuit occurs on switching-on of the supply, it is not the gradual start up system with short and progressively increasing square waves which can efficiently accomodate the over-currents which result from this short circuit.

Finally, another problem particularly important in an architecture such as the one shown in FIG. 1, is the risk of disappearance of the regulation signal which should be emitted by the regulation circuit CI2 and received by the base control circuit CI1: these signals determine not only the width of the square waves enabling the power transistor but also their periodicity; in other words, they serve for establishing the chopping frequency, possibly synchronized from a signal produced on the secondary side of the transformer. The appearance of these signals causes a particular disturbance which must be taken into account.

Furthermore, the architecture shown in FIG. 1, in which the secondary circuits have been voluntarily separated galvanically from the primary circuits, is such that the base control circuit may operate rapidly after switch-on, as will be explained further on, whereas the regulation circuit CI2 can only operate if the chopped power supply is operating; consequently, at the beginning, the base control circuit CI1 does not receive any regulation signals and this difficulty must be taken into account.

SUMMARY OF THE INVENTION

To try and overcome as well as possible all these different problems which relate to security against accidental disturbances in the operation of the power supply (the initial start up being more-over considered as a transitory disturbed operating phase), the present invention provides an improved chopped power supply control circuit which provides a function of gradual start-up power supply on switch on and a function of passing to a safety mode in the case of an operating defect such as a disappearance of appropriate regulation signals; the safety mode consists of a succession of periodic cycles at a very low frequency, each cycle consisting of a gradual start-up attempt during a first phase which is short in comparison with the period of the cycle and long compared with the chopping period of the chopped power supply, the first phase being followed by a pause until the end of the cycle, and periodic cycles succeeding each other until normal operation of the power supply is established or re-established; a very low frequency oscillator establishes these cycles when the power supply is not operating under normal conditions (start-up or operating defect); this oscillator is disabled should normal operation be ascertained; a high frequency oscillator generates a burst of chopping signals palliating the absence of regulation signals; these signals are transmitted solely during the first phase of each cycle; they are inhibited during a second phase.

According to a very important characteristic of the invention, the gradual start up operates not by limiting the duration of the square waves from the charging of a capacitor with a fixed time constant, but by limiting the current in the power transistor to a maximum value, this maximum value increasing progressively during the start up phase, over-shooting of this current value causing interruption in the conduction of the power transistor.

Thus, even in the case of a quasi short circuit, the value of the current in the transistor is limited, which was not the case in the gradual start up circuits of the prior art.

More precisely, the chopped power supply control circuit of the invention is intended to receive regulation control signals and to produce square waves for enabling a main switch of the power supply, the square waves having a variable width depending on the signals received, and this circuit comprises a current limiting circuit including a threshold comparator receiving at one input a signal representative of the current flowing through the switch and at another input a threshold signal, the comparator generating a signal for stopping the switch from conducting should over shooting of the threshold occur; furthermore, in order to ensure gradual start-up of the chopped power supply at the beginning of its operation and should this operation be disturbed, the control circuit comprises a means for producing a variable threshold signal for the comparator, this means being adapted for:

establishing a first fixed threshold value under normal operating conditions,

establishing a periodic threshold variation cycle outside normal operating conditions, this cycle consisting in:

causing the threshold to pass suddenly from the first value to a second value, at a time representing the beginning of the cycle, the second value corresponding to a lower current in the switch,

bringing the threshold gradually back from the second value to the first in a first part of the threshold variation cycle,

holding the threshold at the first value until the end of the current cycle,

beginning again a second threshold variation cycle at the end of the current cycle,

stopping the production of threshold variation cycles when normal operating conditions have again been established.

Normal operating conditions will in general be defined by the presence of appropriate regulation signals and by the absence of an over-current in the switch.

The periodic cycle is at very low frequency (for example 1 hz), and the duration of a first part of the cycle is preferably small with respect to the period of the cycle (for example a tenth of this period, followed by a pause during the nine remaining tenths); it is long with respect to the chopping period of the power supply.

In order to provide even more complete safety, a second threshold comparator is preferably provided receiving at one input a signal respresentative of the measurement of the current in the switch and at another input a third threshold value corresponding to a current greater than that of the first threshold value, the comparator delivering a signal for complete inhibition of the switching of the power switch should over-shooting of this third value occur, the inhibition only ceasing when the circuit, after having partially or completely ceased to be supplied with power, is again normally supplied.

BRIEF DESCRIPTION OF THE DRAWINGS

Other features and advantages of the invention will be clear from reading the following detailed description made with reference to the accompanying drawings in which:

FIG. 1 shows a general chopped power supply diagram using two integrated circuits placed respectively on the primary side and on the secondary side of a transformer,

FIG. 2 shows a diagram of the integrated control circuit of the power transistor placed on the primary side,

FIGS. 3 to 6 show timing diagrams of signals at different points on the circuit, and

FIG. 7 shows a detail of a circuit for elaborating a variable threshold.

DESCRIPTION OF THE PREFERRED EMBODIMENT

Referri

ng

to FIG. 1 which shows a chopped power supply architecture given by way

of example and well illustrating the utility of the invention, the

electric mains line has been designated by the reference 10 (mains at

110 to 220 volts, 50 or 60 hertz). This line is connected through a

filter 12 to the input of a rectifier bridge 40 whose output is

connected on the one hand to a primary electric ground, represented

everywhere by a downward pointing black triangle, and on the other hand

to one end of the primary winding EP of the power supply transformer TA.

ng

to FIG. 1 which shows a chopped power supply architecture given by way

of example and well illustrating the utility of the invention, the

electric mains line has been designated by the reference 10 (mains at

110 to 220 volts, 50 or 60 hertz). This line is connected through a

filter 12 to the input of a rectifier bridge 40 whose output is

connected on the one hand to a primary electric ground, represented

everywhere by a downward pointing black triangle, and on the other hand

to one end of the primary winding EP of the power supply transformer TA.A filtering capacitor 16 is placed in parallel across the outputs of the rectifier bridge 14. The other end of the primary winding is connected to the collector of a switching transistor TP whose emitter is connected to the primary ground through a small current measuring resistor 18.

The transformer has several secondary windings which are preferably isolated galvanically from the mains and connected for example to a secondary electric ground isolated galvanically from the primary ground.

Here, each of the secondary windings has one end connected to the secondary ground. The other end feeds a respective low-pass filtering capacitor through a respective rectifier diode.

We will be concerned in what follows with a single secondary winding ES1, connected by a diode 20 to a capacitor 22. The DC output voltage of the chopped power supply is the voltage Vs at the terminals of the capacitor 22; but of course, other DC output voltages may be obtained at the terminals of the other filtering capacitors connected to the secondary windings. These output voltages form stabilized power supply voltages for user circuits not shown. By way of example, a secondary winding ES2 supplies a stabilized power supply voltage of a few volts for the integrated regulation circuit CI2 already mentioned. It can therefore be seen in this connection that this circuit is not supplied with power and cannot therefore supply signals as long as the chopped power supply is not operating.

The same goes a priori for the integrated circuit CI1 controlling the base of the power transistor TP, which circuit is supplied with a stabilized voltage delivered by a secondary winding ES3, a diode 24 and a capacitor 26 (it will be noted in passing that this winding, although being a secondary winding, is connected to the primary ground and not to the secondary ground, for the very simple reason that the integrated circuit CI1 is necessarily coupled galvanically to the primary).

However, since start up of the chopped power supply must be provided, the power supply terminal 28 of the integrated circuit CI1 is also connected directly to the mains through a high resistor 30 and a diode 32; this is possible since the integrated circuit CI1 is connected to the primary ground; it is not possible for the integrated circuit CI2 which must remain galvanically isolated from the mains. As soon as the chopped power supply is operating normally, the stabilized DC voltage from winding ES3 and diode 24 takes precedence over the voltage coming from the mains and from diode 32; this diode 32 is disabled and the direct supply by the mains only takes place after the initial start up phase.

The role of the integrated circuits CI1 and CI2 will now be described.

The regulation circuit CI2 receives from a divider bridge 34, placed at the terminals of capacitor 22, i.e. at the output of the stabilized power supply, information concerning the value of the voltage to be stabilized Vs.

This information is compared with a reference value and applied to a pulse width modulator which forms periodic square waves of variable width depending on the value of the output voltage Vs: the lower Vs the wider the square waves will be.

The square waves are established at the chopping frequency of the chopped power supply. This frequency is therefore established on the secondary side of the circuit; it is generated either inside the circuit CI2, or outside in a circuit not shown, in the form of a saw tooth voltage at the chosen chopping frequency. This saw tooth voltage is used in a way known per se for providing width modulation.

The variable width square waves, at the chopping frequency, are applied to a primary winding 36 of a small transformer TX whose secondary winding 38, isolated galvanically from the primary, delivers positive and negative pulses at the rising and falling fronts respectively of the variable width square waves.

It is these pulses, whose position and frequency are determined by the regulation circuits CI2, which form regulation signals applied to an input 40 of the base control circuit CI1.

The transformer TX is formed by a few turns wound on a ferrite rod, the turns of the primary and the turns of the secondary being sufficiently spaced apart from each other for complying with standards of galvanic isolation between primary circuits and secondary circuits of the chopped power supply.