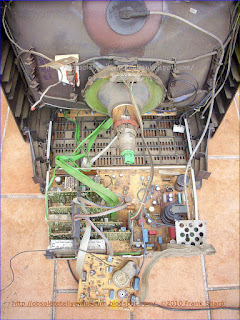

GRUNDIG SUPER COLOR M55-355A CTI CHASSIS CUC3510

Micom - SDA2080-A003 SDA2040-A007

SMPS - TDA3640 & BUT11AF

Vertical - 29504-007.09 TDA2595 HORIZ SYNC

Geometry - TDA8145

Sound - TDA1905

Tuner - 29504-101.01

Tube - A66EAK51X01 / A66EAK01X01 / A66EAK00X01 / A59EAK00X01

FBT - 29201-024.11 / 11B (HR5711)

HOT - BU508AF

RGB Amp. - TFK840 / GF759

Other ICs - TDA4052, TDA8140, UAA2022

29504-142.65 ZF-Verstarker (FR)

29504-105,.23 Farb/RGB (CTI).

29504-175.01 Farb-RGB (Spanien)

29504-145.21 Farb-RGB (FR)

29504-108.04 Videotext 2805

29504-108.92 Videotext VT

29504~-108.51 Senderkennplatte

8324-800-044 Kaskade BG 2087-642-1010

72008-090.02 Fokusregler (!)

This chassis was reliable except for the EHT tripler which was failing very often.

The EHT tripler was causing sometimes big troubles.

GRUNDIG CHASSIS CHASSIS CUC3510 CUC3410 DESCRIPTION OF THE ZNT - LINE SUPPLY TRANSFORMER  TECHNOLOGY, ONE TRANSFORMER FOR ALL FUNCTIONS :

TECHNOLOGY, ONE TRANSFORMER FOR ALL FUNCTIONS :

Short Functional  Description

Description

The GRUNDIG line/power supply unit has two important features:

- the line/mains transformer (ZNT) with ferrite core.

This transformer is provided with windings for the power supply and line output stages:

- the supply frequency corresponds to the line frequency.

The ZNT is used for electrical isolation, horizontal deflection, and

generation of the operating voltage. The ZNT windings are tightly and

loosely coupled to ensure that the load capacity of the supplies is high

enough and that back effects on the line transformer winding N-M are

avoided.

Startup Circuit

The starting voltage for IC 655 is

obtained from the bridge rectifier D 621 via R 641. If the voltage on

pin 2, which is derived from the resistor network R 642, 643, and 644,

reaches a level of approximately 10 V, the IC 655 starts to drive T 661

via pin 3 (precondition: pin 18 >10V). The line/power supply circuit

starts to oscillate. Simultaneously, the current consumption drawn via

pin 2 rises and the winding E-D of the ZNT takes over the operating

voltage supply function (D 647, R 647, C 647).

Oscillator in IC TDA 3640

The

control pulses for the T 661 are generated by are generated by an

oscillator which operates on the threshold principle where C 653 is an

externally connected frequency-determining component (oscillator

retaining range 14-17 kHz approx.). The oscillator oscillates at a

free-running frequency until the reference pulses from the ZNT exceed 1

V, at pin 12. In full operating condition (ON) a voltage of about +5 V,

is applied to

pin 12.

Line Output Stage

The deflection transistor T 521 is activated in

stand-by mode. The cyclic line-frequency control of the deflection

transistor corresponds to the “ON“ operating mode. The power for the

horizontal sweep circuit is derived from the electromotive force of coil

M-N so that no additional operating voltage is necessary for T 521.

Voltage Stabilization In stand-by mode the pulse from winding E-D

(tightly coupled with winding A-B) is used as a reference for

stabilization. The controlled variable is +10.5 V on pin 2 TDA 3640. In

full operating condition, that is “ON", the voltage in the horizontal

sweep circuit (transformer winding M-N) must be stabilized to a constant

level. This is achieved by means of a reference pulse from winding C-D

which is tightly coupled with winding M-N. The resulting direct voltage

obtained via D 633 is proportional to the width of the picture or high

voltage and is applied to pin 10 and compared with the reference voltage

(about 3V) on pin 11. In this part of the circuit the +C voltage is

adjusted by means of R 637 to 196 V and 192 V for 25” receivers and 28” receivers, respectively.

Protective Circuits of TDA 3640

The protective circuits respond immediately if:

— the operating voltage on pin 2 is too low (<7 V):

— Ice of T 521 is too high (more negative than —1 V at pin 7);

— the power supply voltage is too high (voltage at pin 18 is 2.8 V higher than at pin 2);

— the power supply voltage is too low (voltage at pin 18 is 1.4 V lower than at pin 2):

— the high voltage is excessively high (line flyback pulses =6 V at pin 12);

— the crystal temperature is too high (>135° C).

Protective Circuits of TDA 8140

The protective circuits respond immediately if:

— the operating voltage at pin 2 is too low (<7 V);

— interference pulses (incorrect control pulses) occur during line flyback;

— the crystal temperature is too high (>160° C).

GRUNDIG SUPER COLOR M55-355A CTI CHASSIS CUC3510 : SYNCHRONIZED SWITCHED-MODE POWER SUPPLY UNIT WITH POWER LINE ISOLATED HORIZONTAL OUTPUT STAGE IN TELEVISION RECEIVER:

GRUNDIG CHASSIS CUC3400 - 3510: Standby mode operation of a horizontal output stage combined with a switched-mode power supply unit. STANDBY-BETRIEB BEI EINER MIT EINEM SCHALTNETZTEIL KOMBINIERTEN HORIZONTALENDSTUFENSCHALTUNG:

1. Swi

tched-mode power supply with a combined horizontal output stage

circuit in television receivers, in which, as a point of electrical

isolation between mains and chassis side, only a transformer (1) is

provided, the primary winding (n1 ) of which is tightly coupled to at

least one chassis-side secondary winding (n3 ) and one mains-side

secondary winding (n5 ) and is loosely coupled to further secondary

windings (n2 , n4 , n6 , n7 ) which, in turn, are tightly coupled to

each other, in which arrangement one of the secondary windings (n2 )

tightly coupled to each other is electrically connected to the

deflection transistor (4) of the horizontal output stage (14), and in

which a primary-side regulating circuit (2), which is synchronized by

flyback pulses in normal operation, controls a regulating switch which

is arranged in series with the primary winding (n1 ) of the transformer

(1), characterized in that - the deflection transistor (4), which is

periodically triggered in normal operation, of the horizontal output

stage (14) is kept continuously conductive by the driver circuit (13) in

standby mode of operation, - the amount of energy transferred from the

mains-side to the chassis side is corrected in accordance with the

determination of the supply voltage of the regulating circuit (2), which

is obtained via the mains-side secondary winding (n5 ) tightly coupled

to the primary winding (n1 ), during the standby mode of operation

during which no flyback pulses are supplied to the regulating circuit, -

and the energy needed in standby mode of operation on the chassis side

for the driver circuit (13) and other loads is transferred via the

chassis-side secondary winding (n3 ) tightly coupled to the primary

winding (n1 ).

tched-mode power supply with a combined horizontal output stage

circuit in television receivers, in which, as a point of electrical

isolation between mains and chassis side, only a transformer (1) is

provided, the primary winding (n1 ) of which is tightly coupled to at

least one chassis-side secondary winding (n3 ) and one mains-side

secondary winding (n5 ) and is loosely coupled to further secondary

windings (n2 , n4 , n6 , n7 ) which, in turn, are tightly coupled to

each other, in which arrangement one of the secondary windings (n2 )

tightly coupled to each other is electrically connected to the

deflection transistor (4) of the horizontal output stage (14), and in

which a primary-side regulating circuit (2), which is synchronized by

flyback pulses in normal operation, controls a regulating switch which

is arranged in series with the primary winding (n1 ) of the transformer

(1), characterized in that - the deflection transistor (4), which is

periodically triggered in normal operation, of the horizontal output

stage (14) is kept continuously conductive by the driver circuit (13) in

standby mode of operation, - the amount of energy transferred from the

mains-side to the chassis side is corrected in accordance with the

determination of the supply voltage of the regulating circuit (2), which

is obtained via the mains-side secondary winding (n5 ) tightly coupled

to the primary winding (n1 ), during the standby mode of operation

during which no flyback pulses are supplied to the regulating circuit, -

and the energy needed in standby mode of operation on the chassis side

for the driver circuit (13) and other loads is transferred via the

chassis-side secondary winding (n3 ) tightly coupled to the primary

winding (n1 ).1. Schaltnetzteil mit kombinierter Horizontalendstufenschaltung in Fernsehempf·angern, bei dem als galvanische Tren

nstelle zwischen Netz- und Chassisseite nur ein

Transformator vorgesehen ist, dessen Prim·arwicklung mit mindestens

einer weiteren Wicklung fest und den anderen Wicklungen, die fest

aneinandergekoppelt sind, lose gekoppelt ist, wobei eine der fest

miteinander verkoppelten Sekund·arwicklungen mit dem Ablenktransistor

der Horizontalendstufe elektrisch verbunden ist, d a d u r c h g e k e n

n z e i c h n e t , dass der Ablenktransistor (4) der

Horizontalendstufe und der Regelkreis (2), der von einer lose an die

Prim·arwicklung (n1) angekoppelten Sekund·arwicklung (n4) mit

R·uckschlagimpulsen versorgt wird, zur Steuerung des Standby-Betriebes

verwendet werden.

nstelle zwischen Netz- und Chassisseite nur ein

Transformator vorgesehen ist, dessen Prim·arwicklung mit mindestens

einer weiteren Wicklung fest und den anderen Wicklungen, die fest

aneinandergekoppelt sind, lose gekoppelt ist, wobei eine der fest

miteinander verkoppelten Sekund·arwicklungen mit dem Ablenktransistor

der Horizontalendstufe elektrisch verbunden ist, d a d u r c h g e k e n

n z e i c h n e t , dass der Ablenktransistor (4) der

Horizontalendstufe und der Regelkreis (2), der von einer lose an die

Prim·arwicklung (n1) angekoppelten Sekund·arwicklung (n4) mit

R·uckschlagimpulsen versorgt wird, zur Steuerung des Standby-Betriebes

verwendet werden. 2. Schaltnetzteil nach Anspruch 1, d a d u r c h g e k e n n z e i c h n e t , dass der Ablenktransistor (4) der Horizontalendstufe zum Einschalten und/oder zum Wiedereinschalten des Normalbetriebes verwendet wird.

3. Schaltnetzteil nach Anspruch 1 oder 2, d a d u r c h g e k e n n z e i c h n e t , dass zum Einschalten des Standby-Betriebes der Ablenktransistor (4) leitend geschaltet, zum Aufrechterhalten des Standby-Betriebes leitend gehalten und zum Wiedereinschalten des Normalbetriebes gesperrt wird.

4. Schaltnetzteil nach einem oder mehreren der vorhergehenden Anspr·uche, d a d u r c h g e k e n n z e i c h n e t , dass der Regelkreis (2) bei einem Kurzschluss der Wicklung infolge einer sekund·arseitigen St·orung zur·uckgeregelt wird bzw. in den Standby-Betrieb umschaltet. EMI11.1

Ein solches Schaltnetzteil wurde von derselben Anmelderin in der deutschen Patentanmeldung P 32 10 908 vorgestellt. Dieses Schaltnetzteil zeichnet sich aus durch einen prim·arseitigen frei anlaufenden Regelkreis zur Steuerung des Hauptstromweges und einen Regelschalter, ·uber den die aus dem Netz gewonnene, ungeregelte Gleichspannung der Prim·arwicklung n1 des Transformators zugef·uhrt wird. In der lose an die Prim·arwidiung n1 gekoppelten Sekund·arwicklung n2 wird ein Strom induziert, der zum Anlauf und zur Versorgung der Horizontalendstufe vorgesehen ist.

In einer zweiten, fest an die Prim·arwicklung n1 angekoppelten Wicklung n3 wird die Niedervoltspannung f·ur die Horizontalansteuerung, die einen internen Treiber enth·alt, und die Kleinsignalstufen erzeugt. Weiterhin sind Sekund·arwicklungen vorgesehen, die fest an n2 gekoppelt sind und die Spannungen f·ur die kGB-Endstufen, Heizung, usw. erzeugen.

·Uber die Trennstelle n /n des Transformators wird 12 w·ahrend des R·ucklaufintervalles des Ablenktransistors (4) eine Spannung a

uf die

Prim·arwicklung n1 ·ubertragen, die zur Ausschaltung des Regel schalters

verwendet wird. In der fest an die Wicklung n2 gekoppelten Wicklung n4

wird eine Spannung induziert, die zur Synchronisation und Steuerung des

Regelkreises 2 herangezogen wird. Der durch den Widerstand (6)

fliessende Strom kann als ·Uberlast-Referenzstrom zum Abschalten des

Regelschalters herangezogen werden.

uf die

Prim·arwicklung n1 ·ubertragen, die zur Ausschaltung des Regel schalters

verwendet wird. In der fest an die Wicklung n2 gekoppelten Wicklung n4

wird eine Spannung induziert, die zur Synchronisation und Steuerung des

Regelkreises 2 herangezogen wird. Der durch den Widerstand (6)

fliessende Strom kann als ·Uberlast-Referenzstrom zum Abschalten des

Regelschalters herangezogen werden.Belastungs·anderungen werden in der fest an n2 gekoppelten Wicklung n4 erfasst und ·uber eine Beeinflussung der Stromflusszeit des Hauptstromkreises ausgeregelt.

Die deutsche Anmeldung P 32 10 908 enth·alt jedoch keinen Hinweis auf einen Standby-Betrieb.

Weiterhin ist aus der DE-PS 24 58 302 ein Sperrwandler-Netzteil f·ur einen Fernsehempf·anger mit Ultraschall-Fernbedienung bekannt, der als Betriebszustand u. a. einen Bereitschaftsbetrieb aufweist. Bei dieser Schaltung sind der Fernsehempf·anger und der Ultraschallempf·anger an denselben Trenntransformator sekund·arseitig angeschlossen. Die Umschaltung zwischen Normalbetrieb und Bereitschaftsbetrieb wird auf der Sekund·arseite des Trenntransformators vorgenommen.

Bei dieser Schaltung ist jedoch ein zus·atzlicher Transformator f·ur die Horizontalendstufe n·otig.

Die Aufgabe der Erfindung besteht darin, bei einem Schaltnetzteil mit kombinierter Horizontal-Endstufenschaltung der im Oberbegriff des Anspruchs 1 angegebenen Art auf besonders einfache Art und Weise den Standby-Betrieb zu erm·oglichen.

Diese Aufgabe wird durch das Kennzeichen des Patentanpsruchs 1 gel·ost. Besonders vorteilhafte Weiterbildungen der Erfindung sind in den Unteranspr·uchen gekennzeichnet.

Dic Vorteile der Erfindung liegen insbesondere darin, dass als galvanische Trennstelle nur ein Transformator f·ur die Erzeugung der Betriebsspannung, der Hochspannung, der Horizontalablenkung und der Heizspannung n·otig ist und aufgrund der gew·ahlten Wicklungsanordnung mit Hilfe des Horizontal-Ablenktransistors und der prim·arseitigen Regelschaltung auf besonders einfache Art und Weise eine Steuerung des Standby-Betriebes durchgef·uhrt werden kann.

Ein weiterer Vorteil besteht darin, dass im Falle einer sekund·arseitigen St·orung automatisch der Standby-Betrieb herbeigef·uhrt wird.

Die Erfindung wird nachfolgend unter Bezugnahme auf das aus der Figur 1 ersichtliche Ausf·uhrungsbeispiel n·aher erl·autert.

Die Schaltun

g wird ·uber die Netzspannung UN mit nachgeschalteter

Gleichrichterbr·ucke mit einer ungeregelten Gleichspannung versorgt und

ist ·uber nur einen Transformator 1 vom Netz getrennt, wobei der

Transformator die Stromversorgung f·ur das synchronisierte

Schaltnetzteil sowie die Impuls- bzw. Hochspannungserzeugung ·ubernimmt.

Wie durch die gestrichelte Linie zum Ausdruck kommt, ist die Netzseite

v·ollig von der Schaltungsseite galvanisch getrennt.

g wird ·uber die Netzspannung UN mit nachgeschalteter

Gleichrichterbr·ucke mit einer ungeregelten Gleichspannung versorgt und

ist ·uber nur einen Transformator 1 vom Netz getrennt, wobei der

Transformator die Stromversorgung f·ur das synchronisierte

Schaltnetzteil sowie die Impuls- bzw. Hochspannungserzeugung ·ubernimmt.

Wie durch die gestrichelte Linie zum Ausdruck kommt, ist die Netzseite

v·ollig von der Schaltungsseite galvanisch getrennt.In der Anlaufphase wird ·uber eine Startschaltung 7, die im einfachsten Fall aus einem hochohmigen Widerstand besteht, der Kondensator 11 aufgeladen. In dieser Phase gibt die Regelschaltung 2 keine Impulse an die Basis des Regelschalters 3 ab. Erst wenn die Spannung am Punkt A einen vorgegebenen Wert (z. B.

10 V) erreicht hat, wird ·uber eine regelschaltungsinterne Stabilisierungsschaltung die gesamte Schaltung in Betrieb genommen. Die Regelschaltung 2 liefert Impulse an die Basis des Regelschalters 3, tastet also den Regelschalter 3 auf. ueber den Regelschalter 3 fliesst somit ein pulsierender Strom in die Prim·arwicklung n1 des Transformators.

Die Wicklungen nl, n3 und n5 sind fest miteinander verkoppelt. Die Wicklungen n2, n4, n6 und n7 sind untereinander fest, aber lose an die vorgenannten Wicklungen nl, n3 und n5 gekoppelt. Ein Beispiel daf·ur, wie die genannten Kopplungsverh·altnisse erreicht werden k·onnen, zeigt die Figur 2.

Die Wicklu

ng n5 liefert ·uber eine Diode 10 einen gegen·uber der

Anlaufphase h·oheren Strom an den Kondensator 11, so dass in der

weiteren Folge die Versorgung der Regelschaltung 2 sichergestellt ist.

ng n5 liefert ·uber eine Diode 10 einen gegen·uber der

Anlaufphase h·oheren Strom an den Kondensator 11, so dass in der

weiteren Folge die Versorgung der Regelschaltung 2 sichergestellt ist.Durch die zweite, fest an n1 und lose an n2 angekoppelte Sekund·arwicklung n3 wird die Niedervoltspannung f·ur die Kleinsignalstufen und die NF-Stufe und den Horizontaloszillator bzw. die Treiberschaltung 13 der Horizontalendstufe 14 gewonnen, und damit die Ansteuerung des Ablenktransistors 4 sichergestellt. In die lose an n1 gekoppelte Sekund·arwicklung wird n2 In die lose an n1 gekoppelte Sekund·arwickl£ung n2 wird eine Spannung induziert, die nach Gleichrichtung mittels einer Diode 8 an den Kondensator 9 die ben·otigte Betriebsspannung f·ur den Ablenkkreis liefert und somit den Anlauf der Horizontalendstufe herbeif·uhrt.

·Uber die Trennstelle n 1/n2 wird ferner die an der Ablenkwicklung 15 stehende Spannung w·ahrend des K·ucklaufintervalls der Ablenkschaltung invertiert auf die Prim·arwicklung n1 betragen, um den Strom im Hauptstromweg w·ahrend der R·ucklaufzeit bei der Schaltung des Regelschalters 3 und damit die Abschaltverluste zu vermindern. Dieser Vorgang ist ausf·uhrlich beispielsweise in der DE-OS 28 35 946 dargestellt.

Aus einer fest an die Wicklung n2 und lose an n1 angekoppelten Wicklung n4 des Transformators wird eine R·ucklauf spannung gewonnen, die abh·angig von der Belastung der Wicklung n2 ist.

Strahlstrom·anderungen in der Hochspannungserzeugung ·uber die Wicklung n6 und der Hochspannungskaskade 12 (bzw. Split) werden ·uber die fest an n6 gekoppelte Wicklung n2 bzw. die fest an n2 ge

koppelte Wicklung n4 an die

Regelschaltung 2 weitergegeben, die die Stromflusszeit im

Hauptstromkreis bzw. den Regelschalter 3 beeinflusst. Somit werden ·uber

die Regelschaltung 2 Belastungsschwankungen ausgeregelt.

koppelte Wicklung n4 an die

Regelschaltung 2 weitergegeben, die die Stromflusszeit im

Hauptstromkreis bzw. den Regelschalter 3 beeinflusst. Somit werden ·uber

die Regelschaltung 2 Belastungsschwankungen ausgeregelt.Hingegen werden Belastungs·anderungen in der Wicklung n3, wie sie beispielsweise durch NF-Last·anderungen gegeben sind, fast nicht nachgeregelt, da die Wicklung n3 nur lose mit den Wicklungen n2 und n4 verkoppelt ist. Deshalb ist die Zeilenablenkschaltung weitgehend unabh·angig von Last·anderungen in der Sekund·arwicklung n3.

Die Netzspannungsnachregelung f·ur die Spannungen, die aus der Wicklung n3 gewonnen werden, erfolgt indirekt ·uber die Regelimpulse der Wicklung n4 So w·urde sich beispielsweise bei Netzunterspannung die R·ucklauf spannung ohne Nachregelung verringern.

Durch die Impulse der Wicklung n4 wird jedoch ·uber die Regelschaltung 2 die Leitzeit des Regelschalters 3 verl·angert. Damit wird mehr Energie von der Prim·arauf die Sekund·arseite ·ubertragen und demzufolge Netzspannungs·anderungen ausgeglichen.

Bei der Umschaltung vom Normalbetrieb in den Standby- Betrieb schaltet der Regelkreis 2 die Spannung ¢am Punkt A auf den vorgegebenen Wert von z. B. 10 V.

Diese Standby-Umschaltung steht in Verbindung mit einer Verk·urzung der Leitzeit des Regel schalters 3, die wie folgt ausgel·ost wird: ·Uber die Wicklung n3 bzw. eine Treiberschaltung 13 der Horizontalansteuerstufe wird die Basis des Ablenk transistors 4 so gesteuert, dass der Ablenktransistor st·andig leitet. Demzufolge kann sich im Kondensator 9 und damit auch in der Sekund·arwicklung n2 keine Spannung aufbauen. Da die Wicklung n6 f·ur die Hoch spannungs erzeugung, die Wicklung n7 f·ur die Erzeugung einer Heizspannung und sonstige Impulsspannungen sowie die Wicklung n4 f·ur die Synchronisation und Steuerung der Regelschaltung 2 fest mit der Wicklung n2 verkoppelt sind, k·onnen weder Hochspannung noch Heizung noch sonstige Impuls spannungen entstehen.

Damit sind s·amtliche im Standby-Betrieb nicht ben·otigten Spannungen abgeschaltet, ziehen also keine Leistung aus dem Netz. Ausserdem schaltet wegen des Wegfalls der R·ucklauf spannungen an n4 die Regelschaltung im beschriebenen Sinne den Regel schalter 3 auf Standby-Betrieb um.

Dagegen ist die im Standby-Betrieb n·otige Versorgung der Sekund·arseite mit Niedervoltspannung weiterhin gew·ahrleistet, da die Wicklung n3, ·uber die diese Versorgung erfolgt, fest mit der Prim·arwicklung n1 und nur lose mit der Sekund·arwicklung n2 verkoppelt ist. Die Nachregelung der Niedervoltspannung kann - falls n·otig - mit Hilfe der Spannung erfolgen, die in die ebenfalls fest an n1 gekoppelte Wicklung n5 induziert wird, die ansonsten nur die Energie f·ur die Versorgung der Regelschaltung liefert.

Der ·Ubergang vom Standby-Betrieb auf den

Normalbetrieb geschieht durch die Sperrung des Ablenktransistors 4 und

dessen weitere periodische Ansteuerung. Die an der Wicklung n2

entstehende Spannung wird in der fest an n2 gekoppelten Wicklung n4

induziert. Diese R·uckschlagimpulse gelangen an den Triggereingang der

Regelschaltung 2. Diese f·uhrt einen internen Spannungsvergleich durch

und f·uhrt die Schaltung wieder in den geregelten Normalzustand ·uber.

Der ·Ubergang vom Standby-Betrieb auf den

Normalbetrieb geschieht durch die Sperrung des Ablenktransistors 4 und

dessen weitere periodische Ansteuerung. Die an der Wicklung n2

entstehende Spannung wird in der fest an n2 gekoppelten Wicklung n4

induziert. Diese R·uckschlagimpulse gelangen an den Triggereingang der

Regelschaltung 2. Diese f·uhrt einen internen Spannungsvergleich durch

und f·uhrt die Schaltung wieder in den geregelten Normalzustand ·uber.Die dargestellte Schaltung erm·oglicht es somit, den Ablenktransistor 4 der Horizontalendstufenschaltung in besonders einfacher Weise f·ur die Steuerung des Standby-Betriebes zu verwenden.

Ein besonderer Vorteil der erfindungsgem·assen Schaltung liegt darin, dass im Falle einer sekund·arseitigen St·orung, z. B. einem Kurzschluss der Diode oder des Kondensators 16, die Schaltung automatisch in den Standby-Betrieb ·ubergef·uhrt wird. Denn im Falle eines Kurzschlusses der Diode 8 oder des Kondensators 16 kann sich an n2 keine Spannung aufbauen. Dies gilt ebenso f·ur die Wicklung n4, die fest an n2 gekoppelt ist und die R·uckschlagimpulse an den Triggereingang der Regelschaltung 2 liefert. Auch an der Wicklung n6 f·ur die Hochspannungserzeugung und der Wicklung n7 f·ur die Erzeugung einer Heizspannung, die beide ebenfalls fest an n2 gekoppelt sind, kann sich keine Spannung aufbauen.

GRUNDIG SUPER COLOR M55-355A CTI CHASSIS CUC3510 Regulated power supply device for a line sweep circuit in a television receiver:

1. A regulated power supply device, in particular for a line sweep circuit in a television receiver, whose output stage (30) contains a first electronic switch of the bidirectional type (36, 35), controlled periodically so as to be closed during the forward sweep and open during the fly-back, connected in parallel with a first series assembly containing line deviation coils (31) and a first capacitor (32), called the forward capacitor, which feeds these coils (31) during the closing of the first switch (36, 35), with a second capacitor (34), called the return capacitor, which forms a parallel resonant circuit with the inductance in particular of the coils (31) during the opening of the first switch (36, 35) and with a second series assembly containing a first winding (22) of a transformer (20), called the line transformer, and a third capacitor (33), called the power supply capacitor, which feeds the first winding (22) with D.C. voltage while the first switch (36, 35) is closed, the power supply device containing a chopper circuit (10) connected between the terminals (6, 7) of a D.C. power supply voltage source (5) and containing an inductor, called the chopper inductor, (16) and a second electronic switch (15), which is controlled, mounted in series, this second switch (15) containing a chopper transistor (11) controlled on its base by means of a recurring control signal, which is produced by means of the line return pulses picked up on a secondary winding (25) of the line transformer (20), in order to be alternately conducting and cut off during each line period, this chopper inductor (16) containing a second winding (21), called the power supply winding, of this transformer (20), which is intended for the transfer of energy between the chopper circuit (10) and the line sweep output stage (30), and being characterized by the fact that, the second switch (15) being also of the bidirectional type and containing, apart from the chopper transistor (11), which is operating in the saturated and cut off mode, a diode (12) mounted in parallel and in opposition with this transistor, the chopper circuit (10) contains also a fourth capacitor (13), called the turning capacitor, which forms a resonant circuit with the chopper inductor (16) during the opening periods of the second switch (15) which works with a constant cyclic ratio, the periods being obtained by means of a control signal which causes the cutting off of the chopper transistor (11) and their lengths being constant and greater than a half period of resonance of this resonant circuit (13, 16) whose length may reach about a half of a line period, and by the fact that the regulation of the energy exchanged between the chopper circuit (10) and the output stage (30) is obtained by the variation of the delay between the respective opening instants of the first

(36, 35) and second (15) switches.

(36, 35) and second (15) switches.2. A power supply device as in claim 1, characterized by the fact that the transistor (11) in the second switch (15) is controlled by means of a regulation circuit (40) fed by an auxiliary winding (25) of the transformer (20) which supplies it with a signal one of whose peak amplitudes is proportional to the voltage at the terminals of the power supply capacitor (33) in the output stage (30), which is recharged by means of the chopper circuit (10), and whose peak to peak amplitude is proportional to a very high voltage supplied by another winding (23) of transformer (20), the regulation circuit (40) causing the delay in the instant of cut off of transistor (11) to vary with respect to the leading edge of the line return pulse produced by the opening of the first switch (36, 35).

3. A power supply device as in claim 2, characterized by the fact that the regulation by the phase shift between the respective cut off instants is obtained as a function either of the peak to peak amplitude or of the peak amplitude during the fly back or forward sweep of the signal at the terminals of one of the windings (21 or 25) of line transformer (20) by comparing this amplitude to a reference voltage and by controlling the delay as a function of the difference between the voltage corresponding to one of these amplitudes and the reference voltage, in order to stabilize either the sweep amplitude or the power supply voltage obtained by rectifying the line return pulse.

4. A power supply device as in claim 2, characterized by the fact that the regulation circuit (40) contains an unstable multivibrator (48) whose output is coupled to the base of chopper transistor (11) by means of a control stage (50) and which operates independantly on starting up, a circuit generating a variable delay which contains a phase shift stage (46) triggered by the line return pulses and supplying to the multivibrator (48) triggering pulses which are delayed with respect to the leading edges of the line return pulses, which cause the cutting off of chopper transistor (11), and a regulator stage (47), which supplies the phase shift stage (46) with a regulation signal that makes it possible to vary the delay between the respective leading edges of the line return pulses and the triggering pulses as a function of one of the peak amplitudes or of the peak to peak amplitude of the signal supplied by the auxiliary winding (25) of the transformer (20).

5. A power supply device as in claim 4, of the type in which the power supply capacitor (33) feeds a D.C. voltage to the whole line sweep circuit, characterized by the fact that the regulation circuit (40) is fed by means of an independant power supply circuit (51) which enables the chopper circuit (10) to be started up by the independant operation of the unstable multivibrator (48) in order to start up the power supply of the line sweep circuit with the chopper voltage induced in the first winding (22) of the transformer (20) and rectified by the diode (35) which is part of the first bidirectional switch (36, 35) which charges the power supply capacitor (33).

6. A power supply device as in one of claims 4 and 5, characterized by the fact that the phase shift stage (46) contains a delay generator which supplies a voltage, in the shape of recurrent saw teeth (460, 463) which are triggered by the leading edges of the line return pulses, to an analog voltage comparator stage (469, 4600, 4601), which supplies at its output negative pulses to the base of the transistor (483) in multivibrator (48) whose cutting off controls the cut off of chopper transistor (11) at instants at which the instantaneous saw tooth amplitude exceeds a fixed threshold voltage (VZ 4601), and by the fact that the regulator stage (47) contains an assembly (470, 471) rectifying the signal supplied by the auxiliary winding (25) which feeds a signal generator (476, 475) supplying a signal which modifies, from a predetermined threshold, the saw tooth slope as a function of one of the peak amplitudes or peak to peak amplitudes of this signal (v25).

7. A power supply device as in claim 6, of the type in which the free running operating frequency of the unstable multivibrator (48) is less than the line frequency, characterized by the fact that the unstable multivibrator (48) is controlled solely by the negative pulses coming from the comparator stage (469), which are applied to one (483) of the transistors in the multivibrator (48), whose cut off controls that of chopper transistor (11).

8. A power supply device as in one of claims 4 to 6, of the type in which the free running operating frequency of the unstable multivibrator (48) is greater than the line frequency in order to limit the peak voltage (V19max) on the collector of the chopper transistor (11), characterized by the fact that the transistor (480) in the multivibrator (48), whose state is complementary to that of the chopper transistor (11), is fed on its base through a diode (4803) by a synchronizing stage (49), which supplies negative pulses whose amplitude is equal to a predetermined fraction of that of the line return pulses, in order to lengthen the cut off state of this transistor (480) until the sum of these lengths is equal to the line period.

Description:

The present invention concerns a regulated power supply device, in particular for a line sweep circuit in a television receiver, which can also provide D.C. supplies to other circuits in this receiver by splitting up a D.C. supply voltage which is usually obtained by the rectification and filtering of the A.C. mains voltage by means of a chopper.

Known chopper converters of this type contain, generally connected in series between the output terminals of a D.C. power supply source (filtered rectifier), an electronic switch such as a switching transistor operating in the saturated and cut off mode and an inductor which includes the primary winding of a transformer in which at least one secondary winding supplies the A.C. energy obtained by the chopping, which is then rectified to provide the D.C. supply voltages with a ground insulated from the mains. In most of the known chopper power supplies, one can vary the output voltages by action on the cyclic ratio, i.e. the length of the saturated (closed) state of the switch, for example, by controlling periodically the transistor-chopper by means of a monostable flip-flop of variable length as a function of a voltage which may be picked up at the output of a rectifier fed by a secondary winding of the transformer so as to form a regulation loop.

Chopper power supplies have frequently been used in television receivers to eliminate the bulky and heavy mains supply transformer and make possible a regulation of the D.C. power supply voltage for this receiver. They have often been combined in particular at the output stage of the horizontal sweep circuit which supplies them with a pulse signal at the line frequency that can be used to control the chopping. Various combinations of sweep circuits and chopper power supplies have described, for example, in the French patents or patent applications with publication Nos. 2.040.217, 2.060.495, 2.167.549, 2.232.147 or 2.269.257, in which the regulation is also done by means of the variation in the cyclic ratio of the saturated and cut off states of the chopper transistor which, in some cases, is also used as the active element of the (final) output stage of the line sweep circuit or of the feeder stage which controls this circuit.

Chopper power supplies of the so called "pump" type in which the chopper transistor feeds one of the windings of the line transformer during the line return periods and in which the regulation is done by means of the variation of the internal resistance of this transistor or of a "ballast" transistor in series with this transistor are known, for example, from the French patents with publication Nos. 2.014.820, 2.025.365 or 2.116.335. A circuit of the "pump" type whose chopper transistor has a winding of the line transformer in its collector circuit and in which the sweep circuit is electrically insulated from the mains has been described in the article by Peruth and Schrenk in the German periodical, SIEMENS BAUTEILE REPORT Vol. 12 (1974), No. 4, pages 96-98. Its structure corresponds to the contents of the introduction to claim 1. In circuits of the "pump" type, the chopper transistor or the "ballast" transistor in series with it dissipates an amount of energy which is not negligable.

In the chopper device supplying power to the output stage of the line sweep circuit with which it is combined in accordance with the invention, one no longer uses regulation by variation of the internal resistance or of the length of the saturated state of the chopper transistor (or by variation of the cyclic ratio of the chopping with a constant periodicity) but one does the regulating by variation of the relative phase between the signals of the same frequency which are supplied respectively by the chopper circuit with a constant cyclic ratio and by the output stage of the line sweep, each of which is connected to one of the windings of a transformer called the line transformer through which the transfer of energy between the chopper circuit and the sweep output stage takes place as well as in the direction of the other secondary windings of the line tranformer such as the very high tension (V.H.T.) winding.

In accordance with the invention, a regulated power supply device, in particular for a line sweep circuit of a television receiver which contains an output stage fitted with a line transformer in which a first winding is connected in series with a s

upply

capacitor, is connected in parallel with a first bidirectional switch

controlled at the line frequency, the power supply device containing a

chopper circuit with, connected in series between the terminals of a

source of a D.C. power supply voltage, an inductor and a second

electronic switch, which can also be controlled at the line frequency.

The inductor in this circuit contains a second winding of the

transformer which is intended for the transfer of energy between the

chopper circuit and the output stage. This power supply device is in

particular characterized by the fact that the second switch, which is

also bidirectional and mounted in parallel with a tuning capacitor, is

so controlled as to be alternately open and closed during each line

period with a constant cyclic ratio and by the fact that the regulation

of the power supplied and hence of the voltage at the terminals of the

supply capacitor is done by variation of the phase delay between the

respective opening instants of the first and second switch as a function

of the peak amplitude of the line return pulse for example.

upply

capacitor, is connected in parallel with a first bidirectional switch

controlled at the line frequency, the power supply device containing a

chopper circuit with, connected in series between the terminals of a

source of a D.C. power supply voltage, an inductor and a second

electronic switch, which can also be controlled at the line frequency.

The inductor in this circuit contains a second winding of the

transformer which is intended for the transfer of energy between the

chopper circuit and the output stage. This power supply device is in

particular characterized by the fact that the second switch, which is

also bidirectional and mounted in parallel with a tuning capacitor, is

so controlled as to be alternately open and closed during each line

period with a constant cyclic ratio and by the fact that the regulation

of the power supplied and hence of the voltage at the terminals of the

supply capacitor is done by variation of the phase delay between the

respective opening instants of the first and second switch as a function

of the peak amplitude of the line return pulse for example.In accordance with a preferred way of making the invention, a power supply device in accordance with the preceding paragraph, in which the s

econd

bidirectional switch, which contains a switching transistor, is

controlled on its base by a regulation circuit in which one input is fed

by an auxiliary secondary winding of the line transformer supplying

line return pulses, is remarkable in particular for the fact that the

regulation circuit contains an unstable multivibrator controlling the

base of the chopper transistor and operating independantly on starting

up, a circuit generating a variable delay containing a phase shift

stage, which is triggered by the line return pulses and supplies the

multivibrator with triggering pulses that are delayed with respect to

the leading edges of the line return pulses, which cause the cut off of

the chopper transistor, and a regulator stage fed with the line return

pulses and supplying to the phase shift stage a regulation signal which

enables the delay in the triggering pulses to be varied with respect to

the line return pulses as a function of one of the peak amplitudes or of

the peak to peak amplitude of the line return pulses.

econd

bidirectional switch, which contains a switching transistor, is

controlled on its base by a regulation circuit in which one input is fed

by an auxiliary secondary winding of the line transformer supplying

line return pulses, is remarkable in particular for the fact that the

regulation circuit contains an unstable multivibrator controlling the

base of the chopper transistor and operating independantly on starting

up, a circuit generating a variable delay containing a phase shift

stage, which is triggered by the line return pulses and supplies the

multivibrator with triggering pulses that are delayed with respect to

the leading edges of the line return pulses, which cause the cut off of

the chopper transistor, and a regulator stage fed with the line return

pulses and supplying to the phase shift stage a regulation signal which

enables the delay in the triggering pulses to be varied with respect to

the line return pulses as a function of one of the peak amplitudes or of

the peak to peak amplitude of the line return pulses.The invention will be better understood and others of its characteristics and advantages will appear from the description which follows, which is given as an example, and the drawings attached, which refer to it. Among them:

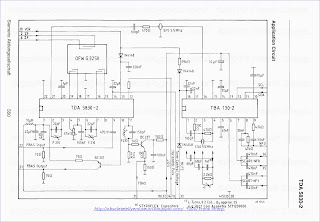

FIG. 1 represents part of a theoretical schematic diagram of a chopper power supply device combined with the output stage of the line sweep circuit in accordance with the invention;

FIGS.

2a-2f and 3a-3f are diagrams of the voltage wave forms and/or current

wave forms at various points in the circuit of FIG. 1 to explain the

operation of this circuit;

FIGS.

2a-2f and 3a-3f are diagrams of the voltage wave forms and/or current

wave forms at various points in the circuit of FIG. 1 to explain the

operation of this circuit;FIG. 4 represents part of a synoptic schematic diagram of a simple production model (without a starter device) of regulation circuit 40 in FIG. 1;

FIG. 5 represents a block diagram of a preferred production model of regulation circuit 40 in FIG. 1 in accordance with the invention;

FIG.

6 represents a theoretical schematic diagram of the whole of the

preferred production model of the regulation circuit in FIG. 5;

FIG.

6 represents a theoretical schematic diagram of the whole of the

preferred production model of the regulation circuit in FIG. 5;FIGS. 7a and 7b represent voltage wave forms illustrating the slaving of the frequency of the unstable multivibrator 48 to that of the line oscillator; and

FIGS. 8a-8c represent voltage wave forms illustrating the operation of the regulation by the variation in phase shift.

In FIG. 1 is shown schematically a chopper power supply device of line sweep output stage 30 in accordance with the invention which is electrically insulated from the A.C. mains which feed rectifier 5 whose output voltage is chopped. This power supply device has two terminals 1, 2 which are connected respectively to the two poles of the A.C. distribution mains (220 V, 50 Hz) and feed rectifier diode 3 and filter capacitor 4, whose capacity is high, which are connected in series and form together a rectifier assembly or a source of D.C. voltage 5. The output of rectifier assembly 5 formed by the two terminals 6 and 7 (plates) of the (electro-chemical) capacitor 4 is intended to supply a D.C. power supply voltage V A of the order of 300 V to chopper circuit 10. This chopper circuit 10 contains a controlled, bidirectional electronic switch 15, which consists of a switching transistor 11 of the NPN type connected with its emitter common and a junction semiconductor diode 12, which are connected in parallel in such a way as to conduct respectively in opposite directions (anti-parallel), and an inductor 16 consisting of a choke 14 and a winding 21 of a transformer 20, called a line transformer, connected in series. This winding 21 of line transformer 20 whose primary winding is normally connected in parallel with the coils of the horiziontal deviation circuit in the circuit of line sweep output stage 30 to the supply, through secondary windings, supply voltages in particular to the cathode ray tube will be called in what follows the supply voltage winding, because the transfer of energy between chopper circuit 10 and output stage 30 will be done through it. Switch 15 is mounted in parallel with a capacitor 13 and it is connected in series with inductor 16 (choke 14 and power supply winding 21 in series) between the out

put

terminals 6 and 7 of D.C. voltage source 5. This capacitor 13 forms,

because of its low capacity with respect to that of filter capacitor 4,

with inductor 16 a parallel, resonant (oscillatory) circuit when

electronic switch 15 is opened by the cutting off of switching

transistor 11 by means of a control signal applied to its base.

put

terminals 6 and 7 of D.C. voltage source 5. This capacitor 13 forms,

because of its low capacity with respect to that of filter capacitor 4,

with inductor 16 a parallel, resonant (oscillatory) circuit when

electronic switch 15 is opened by the cutting off of switching

transistor 11 by means of a control signal applied to its base.Switching transistor 11 is here connected by its collector to one of the terminals of inductor 16, whose other terminal is connected to positive terminal 6 of source 5 which supplies D.C. power supply voltage V A , by its emitter to negative terminal 7 of source 5, which forms a ground, called the primary or hot ground, 8, which is connected to the A.C. mains but is insulated from that 39 of the television set. The base of transistor 11 is controlled by means of rectangular signals supplied by a regulation circuit 40, which is described further on, in such a way as to be alternately saturated and cut off. Regulation circuit 40 is, for example, fed by a secondary winding 25 of transformer 20, that supplies signals whose peak to peak amplitude is proportional to the peak amplitude of the line return pulse. This peak amplitude is a function of the energy transfer from chopper circuit 10 to the line sweep output stage 30 which is connected to another winding 22 of transformer 20.

One may note here that chopper circuit 10 resembles a classical, transistorized, line sweep output stage and that switching transistor 11 has been chosen to withstand high collector-emitter voltages (of the order of 1500 V), and that diode 12 has to withstand the same inverse voltage while switch 15 is open. One may also note that the inductance of choke 14 may be formed partly or wholly by the leakage inductance of power supply winding 21 in transformer 20.

The line sweep output stage 30, which is arranged in classic

al fashion, contains horizontal

deviation coils 31 mounted in parallel and connected by one of their

terminals to a first capacitor 32, called the "forward" or "S effect"

capacitor, which feeds them during the forward sweep. The series

mounting of coils 31 and forward capacitor 32 is connected in parallel,

on the one hand, to a second controlled bidirectional switch containing a

second switching transistor 36 and a second diode 35, called a "shunt"

or "parallel" recuperation diode, which are connected in parallel to

conduct in opposite directions, closed (conductor) during the forward

sweep and open (cut off) during the return sweep, and, on the other

hand, to a second capacitor 34, called the "return" capacitor, which

forms, while the second switch is open, a parallel resonant circuit with

the inductance of deviation coils 31. The common point of the collector

of second transistor 36, of the NPN type, of the cathode of second

diode 35 and return 34 and forward 32 capacitors is connected to one of

the terminals 220 of winding 22 of transformer 20, which normally forms

the primary winding of this transformer. The other terminal 221 of

winding 22 is connected to one of the terminals of a third capacitor 33

of high capacity, whose other terminal is connected to the common point

of deviation coils 31, return capacitor 34, the anode of second diode 35

and the emitter of second transistor 36, which is also connected to the

ground 39 of the chassis of the television receiver, called the "cold"

ground, because it is insulated from the A.C. power supply mains. It is

at the terminals of this third capacitor 33 that one obtains the D.C.

voltage feeding this stage, whose value determines, on the one hand, the

peak to peak amplitude of the line sweep current of sawtooth form and,

on the other hand, the amplitude of the line return voltage pulse which,

when rectified after being transformed, supplies the very high voltage

that polarizes the anode of the cathode ray tube (not shown here). The

second transistor 36, also a switching transistor, is controlled by

rectangular shaped signals supplied to input terminals 37 and 38 of

stage 30, which are respectively connected to its base and its emitter,

by a feed stage (not shown and called a "driver" in anglo-american

literature) so that it is alternately cut off, during the sweep return,

and saturated, during the second part of the forward sweep.

al fashion, contains horizontal

deviation coils 31 mounted in parallel and connected by one of their

terminals to a first capacitor 32, called the "forward" or "S effect"

capacitor, which feeds them during the forward sweep. The series

mounting of coils 31 and forward capacitor 32 is connected in parallel,

on the one hand, to a second controlled bidirectional switch containing a

second switching transistor 36 and a second diode 35, called a "shunt"

or "parallel" recuperation diode, which are connected in parallel to

conduct in opposite directions, closed (conductor) during the forward

sweep and open (cut off) during the return sweep, and, on the other

hand, to a second capacitor 34, called the "return" capacitor, which

forms, while the second switch is open, a parallel resonant circuit with

the inductance of deviation coils 31. The common point of the collector

of second transistor 36, of the NPN type, of the cathode of second

diode 35 and return 34 and forward 32 capacitors is connected to one of

the terminals 220 of winding 22 of transformer 20, which normally forms

the primary winding of this transformer. The other terminal 221 of

winding 22 is connected to one of the terminals of a third capacitor 33

of high capacity, whose other terminal is connected to the common point

of deviation coils 31, return capacitor 34, the anode of second diode 35

and the emitter of second transistor 36, which is also connected to the

ground 39 of the chassis of the television receiver, called the "cold"

ground, because it is insulated from the A.C. power supply mains. It is

at the terminals of this third capacitor 33 that one obtains the D.C.

voltage feeding this stage, whose value determines, on the one hand, the

peak to peak amplitude of the line sweep current of sawtooth form and,

on the other hand, the amplitude of the line return voltage pulse which,

when rectified after being transformed, supplies the very high voltage

that polarizes the anode of the cathode ray tube (not shown here). The

second transistor 36, also a switching transistor, is controlled by

rectangular shaped signals supplied to input terminals 37 and 38 of

stage 30, which are respectively connected to its base and its emitter,

by a feed stage (not shown and called a "driver" in anglo-american

literature) so that it is alternately cut off, during the sweep return,

and saturated, during the second part of the forward sweep.In classical transistor line sweep circuits, a D.C. voltage source generally feeds either terminal 221 of winding 22 directly or an intermediate connection to this winding through a diode (see French Pat. Nos. 1.298.087 dated Aug. 11, 1961, 1.316.732 dated Feb. 15, 1962 or 1.361.201 dated June 27, 1963) which isolates the primary winding of the line transformer from the D.C. voltage source during the line return interval.

In

the circuit of FIG. 1, it is the A.C. electrical energy transmitted by

chopper circuit 10 through windings 21 and 22 of transformer 20 which

charges capacitor 33 so that it supplies a regulated supply voltage to

output stage 30. During the line sweep forward periods, when the second

bidirectional switch 35, 36 of sweep output stage 30 is closed

(conductor), the terminals of winding 22 of transformer 20 are directly

connected to those of capacitor 33 which will then receive the energy

supplied of by chopper circuit 10.

In

the circuit of FIG. 1, it is the A.C. electrical energy transmitted by

chopper circuit 10 through windings 21 and 22 of transformer 20 which

charges capacitor 33 so that it supplies a regulated supply voltage to

output stage 30. During the line sweep forward periods, when the second

bidirectional switch 35, 36 of sweep output stage 30 is closed

(conductor), the terminals of winding 22 of transformer 20 are directly

connected to those of capacitor 33 which will then receive the energy

supplied of by chopper circuit 10.In FIG. 1, line transformer 20 also has a very high voltage winding 23, one terminal 230 of which may be connected to the ground 39 (or to terminal 220 of winding 22) and whose other terminal 231 is connected to the input of the very high voltage rectifier assembly or voltage multiplier (not shown) in classical fashion, and an auxiliary winding 24 which may be used to feed either a low voltage rectifier assembly or a load regulator assembly or the filament of the cathode ray tube (not shown). These secondary windings 23, 24 will receive their energy mainly from output stage 30 of the line sweep circuit through winding 22 of transformer 20, i.e. the line return pulses, the coupling between the windings will hence be as close as possible.

The operation of the power supply device in FIG. 1 will be explained below with that of output stage 30 of the line sweep circuit, with reference to FIGS. 2 and 3 of the drawing attached, representing diagrams of the voltage wave forms and/or current wave forms at various points in the schematic diagram of FIG. 1.

In

FIGS. 2 and 3, diagram (A) represents the saw tooth wave form of the

sweep current i 31 (t) in the coils 31 of the horizontal deviation

circuit. Diagram (B) represents the wave form of the voltage v 220 (t)

on terminal 220 of winding 22, which is also that at the terminals of

the second switch 35, 36. Diagram (C) is the wave form of the voltage v

21 (t) at the terminals of power supply winding 21 when its leakage

inductance is negligable. It is obtained by the transforming of the A.C.

component of voltage v 220 (t). Diagram (D) represents the wave form of

the voltage v 19 (t) at the terminals of first switch 15 in chopper

circuit 10, i.e. between the junction 19 of this chopper circuit with

inductor 16 and primary ground 8, and diagram (E) represents as a dotted

line the current i 16 (t) in inductor 16 when output stage 30 is not

controlled and as a full line the current i 21 (t) resulting from the

superimposition in winding 21 to current i 16 (t) on that induced by

winding 22 when output stage 30 is working. Conversely, the current in

winding 22 of transformer 20 results from the superimposition of the

current induced by winding 21 on the current produced by the closing of

the second switch 35, 36, which is analogous to i 31 (t) in diagram (A).

In

FIGS. 2 and 3, diagram (A) represents the saw tooth wave form of the

sweep current i 31 (t) in the coils 31 of the horizontal deviation

circuit. Diagram (B) represents the wave form of the voltage v 220 (t)

on terminal 220 of winding 22, which is also that at the terminals of

the second switch 35, 36. Diagram (C) is the wave form of the voltage v

21 (t) at the terminals of power supply winding 21 when its leakage

inductance is negligable. It is obtained by the transforming of the A.C.

component of voltage v 220 (t). Diagram (D) represents the wave form of

the voltage v 19 (t) at the terminals of first switch 15 in chopper

circuit 10, i.e. between the junction 19 of this chopper circuit with

inductor 16 and primary ground 8, and diagram (E) represents as a dotted

line the current i 16 (t) in inductor 16 when output stage 30 is not

controlled and as a full line the current i 21 (t) resulting from the

superimposition in winding 21 to current i 16 (t) on that induced by

winding 22 when output stage 30 is working. Conversely, the current in

winding 22 of transformer 20 results from the superimposition of the

current induced by winding 21 on the current produced by the closing of

the second switch 35, 36, which is analogous to i 31 (t) in diagram (A).The wave forms of diagrams (D) and (E) in FIGS. 2 and 3 are out of phase respectively, one with respect to another, by a quarter of a line period T H /4 to allow the illustration of the regulation by the variation in the relative phase of the voltage v 21 and current i 21 waves in power supply winding 21.

The diagrams (F) represent the instantaneous energy E i transmitted by chopper circuit 10 to the output stage 30, which is equal to the product of the wave forms of current i 21 (t) and voltage v 21 (t) in winding 21, i.e. E i =-v 21 i 21 , for two different phase deviations between the voltage v 21 (t) and current i 21 (t) waves in power supply winding 21, which correspond respectively to a zero energy transfer in FIG. 2 and a maximum energy transfer in FIG. 3.

The operation of the line sweep output stage 30 is classical once the power supply capacitor 33 and forward capacitor 32 are charged to a D.C. voltage V 221 by means of a certain number of chopping cycles, which are independant on starting up, during which the negative half-cycles of the chopped voltage wave are rectified by recuperation diode 35.

During the forward sweep intervals t A , when the switch 35, 36 is closed from instant t 1 to instant t 3 , the current i 31 (see A) in the deviator varies roughly linearly between its negative peak values (at t 1 ) and positive ones (at t 3 ) with a passage through zero at instant t 2 , when current i 31 passes from diode 35 to transistor 36, which has previously been polarized to conduct. This corresponds to a roughly zero voltage v 220 (see B) at the terminals of switch 35, 36.

The line return interval t R is started by the cutting off of transistor 36 at instant t 3 , and the inductance of deviator 31 then acts as a parallel resonant circuit with the return capacitor 34 by causing the voltage v 220 (t) to pass through a positive half-sinusoid and reach its peak value at the instant t 4 (or t=0), called the line return pulse, and the current i 31 (t) to pass through a half-cosinusoid between the positi

ve

and negative peak values cited, with a passage through zero at the

instant t 4 (or t=0). The mean value of the voltage wave form v 220 (t)

at terminal 220 is equal to the D.C. power supply voltage V 221 at the

terminals of power supply capacitor 33 and forward or S effect capacitor

32.

ve

and negative peak values cited, with a passage through zero at the

instant t 4 (or t=0). The mean value of the voltage wave form v 220 (t)

at terminal 220 is equal to the D.C. power supply voltage V 221 at the

terminals of power supply capacitor 33 and forward or S effect capacitor

32.The respective peak to peak amplitudes of current i 31 (t) (hence the width of the screen sweep beam excursion) and of voltage v 220 (t) (hence the very high voltage) depend on the value of the D.C. voltage V 221 which feeds the horizontal sweep output stage and which, in most of the chopper power supplies of preceding techniques, is regulated and stabilized by modulating the length of the saturated state (the cyclic ratio) of chopper transistor 11 as a function of the amplitude of the line return pulse picked up on an auxiliary winding of line transformer 20 (hence of the voltage at the terminals of capacitor 33) and later of the rectified and filtered voltage in the network.

In accordance with the invention, the length t s of the saturated state of chopper transistor 11 and of the conducting state of diode 12 and, as a result, the ratio of this length to that of the complete cycle (line period T H ) or to that t B of the cut off state is constant and so chosen as to make the peak amplitude of voltage pulse v 19 , which is applied to the collector of transistor 11 during the cut off interval t B , considerably less than its collector-emitter D.C. breakdown voltage in the cut off state (V CEX ) which may exceed 1500 Volts. Thus, for a rectified voltage of 300 V, it is possible to limit the collector voltage V 19 to about 900 Volts by choosing a ratio t b /T H of about 0.5.

As a result, chopper circuit 10 must operate at the line frequency with conduction lengths t S (closed) and cut off lengths t B (open) of switch 15 preferably roughly equal (to a line half-period T H /2) and the regulation of the energy supplied to output stage 30 is done by causing the respective phases of the line return pulse v 220 (t) and the current i 21 (t) flowing through the power supply winding 21 of transformer 20 to vary as will be shown further on.

The operation of chopper circuit 10 (fed with D.C. voltage V A ) is in fact analogous to that of output stage 30, except as far as the form factor is concerned. This is determined mainly by the respective values of the inductance 16 (of choke 14 and the leakage inductance of winding 21 of transformer 20 connected in series) and of the capacity of tuning capacitor 13. The values L 16 and C 13 are chosen to obtain a half-period of oscillation slightly less than a line half-period, i.e.: ##EQU1## because the oscillation of the resonant circuit L 16 , C 13 occurs on one side and on the other of the D.C. voltage V A so that the cut off period of chopper switch 15 is greater than this half-period T D /2.

This operation of circuit 10 will first be explained with reference to diagrams D and E in FIG. 2. When, at the instant t=0, transistor 11 becomes saturated by a preliminary positive polarization of its base-emitter junction, it connects terminal 19 to ground 8 so that a current i 16 (t) (dotted on diagram E), which is increasing linearly, ##EQU2## passes through inductor 16 coming from positive terminal 6 of power supply 5.

When transistor 11 receives from regulation circuit 40 a cut off voltage at an instant preceding instant t 6 of the storage time of minority charge carries, switch 15 opens and the current stored in inductor 16, i 16 (t 6 )=V A t 6 /L=V A T H /4L, will flow through tuning capacitor 13 in oscillatory fashion, i.e. cosinusoidally, decreasing to a zero value, while voltage V 19 at junction 19 of inductor 16 and capacitor 13 will increase sinusoidally to a maximum value, these two values coinciding in time. Then, capacitor 13 discharges through inductor 16 also in oscillatory fashion until, at instant t 7 , voltage v 19 reaches a zero value, which corresponds to a minimum value, i.e. maximum negative, of current i 16 (t) whose absolute value is slightly less than the maximum positive value i 16 (t 6 ). The difference between the absolute peak values i 16 (t 6 ) and i 16 (t 7 ) is explained, on the one hand, by the ohmic losses in circuit 10 and, on the other, by the transfer of energy between this circuit and, in particular, output stage 30.

When oscillatory voltage v 19 (t)

has exceeded the zero value slightly in the negative direction, diode

12 starts to conduct so as to connect terminal 19 to ground and produce

in inductor 16 a current i 16 (t), which increases linearly from its

maximum negative value i 16 (t 7 ) towards a zero value where transistor

11, which has already been polarized so as to be saturated, picks it up

so that it reaches, at instant t 8 , its maximum positive value of

instant t 6 again.

When oscillatory voltage v 19 (t)

has exceeded the zero value slightly in the negative direction, diode

12 starts to conduct so as to connect terminal 19 to ground and produce

in inductor 16 a current i 16 (t), which increases linearly from its

maximum negative value i 16 (t 7 ) towards a zero value where transistor

11, which has already been polarized so as to be saturated, picks it up

so that it reaches, at instant t 8 , its maximum positive value of

instant t 6 again.It is to be noted here that the mean value of the wave form of voltage v 19 at terminal 19 is equal to the D.C. power supply voltage V A between terminals 6 and 7 of filter capacitor 4 in rectifier assembly 5.

If one wishes to obtain an adequate energy transfer between chopper circuit 10 and line sweep output stage 30, it is advantageous to choose the value of inductor 16 in series with power supply winding 21, i.e. the sum of the leakage inductance of this winding and that of series choke 14, so that it is, for example, greater than or equal to three times the inductance L 31 of the horizontal deviation coils 31, multipled by the square of the transformation ratio between windings 22 and 21, i.e. L 16 ≥3l 31 (n 11 /n 21 ) 2 , and the value of this transformation ratio n 22 /n 21 so as to obtain at the terminals of winding 21, during the forward sweep and the closing of switch 15, an induced voltage v 21 (t) whose amplitude is between 100 and 150 Volts, i.e. between a third and a half the power supply voltage V A at terminals 6, 7 of filter capacitor 4.

As the D.C. voltage V 221 at the terminals of capacitor 33 is a function of the inductance L 31 of the horizontal deviation coils 31 and, because of this, is between 50 and about 140 Volts, the transformation ratio n 22 /n 21 , i.e. between the numbers of turns n 22 and n 21 of windings 22 and 21 respectively, is between 1 and about 4 (preferably between 2 and 3).

The choice of these parameters is only given here as an example, because the criterion of this choice is a relative separation between chopper circuit 10 and, in particular, circuit 30 which it feeds, i.e. so that current i 21 (t) in winding 21 is only induced in winding 22 with peak amplitudes which do not exceed about one third those of sweep current i 31 (t) in order not to upset the operation of sweep circuit 30 during the conduction of recuperation diode 35. Also, the voltage pulses v 19 (t) of the diagrams (D) in FIGS. 2 and 3 should not appear at the terminals of winding 21 and should not be transmitted to winding 22 at least during the opening of sweep switch 36, 35 (line return interval) to winding 22 other than with amplitudes sufficiently small not to upset the operation of output stage 30 and the very high voltage rectifier fed by winding 23, while ensuring an energy transfer sufficient to obtain a regulated power supply voltage at the value required.

Transformer 20 may therefore be made in such a way as to have looser coupling between windings 21 and 22, the self-inductance then consists of that (L 14 ) of choke coil 14 and the leakage inductance (L 21 ) of winding 21. Hence it is advantageous, when one uses a

ferrite

core (magnetic circuit) of rectangular shape (in the form of a frame),

to place windings 22, 23 and 24 on one of the arms of this core and

winding 21 and, later, winding 25 on the other. This will also help

provide good insulation between the primary and secondary grounds 8 and

39. The dimension of the air gap in the magnetic circuit of transformer

20 or a magnetic shunt, which fixes the leakage inductance L 21 , and

the inductance L 14 of the choke 14 are chosen with this result in view.

ferrite

core (magnetic circuit) of rectangular shape (in the form of a frame),

to place windings 22, 23 and 24 on one of the arms of this core and

winding 21 and, later, winding 25 on the other. This will also help

provide good insulation between the primary and secondary grounds 8 and

39. The dimension of the air gap in the magnetic circuit of transformer

20 or a magnetic shunt, which fixes the leakage inductance L 21 , and

the inductance L 14 of the choke 14 are chosen with this result in view.One may consider then that, from the point of view of the energy transfer from chopper circuit 10 to output stage 30, winding 21 is passed through by current i 21 , which consists of triangular shaped current i 16 and the current in winding 22, which is induced in saw tooth form, superimposed one on the other and that voltage v 21 , which appears at its terminals and is shown in diagrams (C) of FIGS. 2 and 3, is roughly analgous to that, v 220 , at the terminals of sweep switch 35, 36 but with a mean value of zero.

The energy transmitted by transformer 20 will then be approximately equal to the product of voltage v 21 (t) and current i 21 (t) multiplied by the cosine of the phase angle if one considers the fundamental waves at the line frequency (15.625 Hz). This is also true for each of the harmonics of the current i 21 (t) and voltage v 21 (t) waves if one develops them in a Fourier series.

The energy ceded duuring each line period T H by chopper circuit 10 output stage 30 through transformer 20 may then be written: ##EQU3## In inductor 16, as a first approximation, current i 21 (t) in a sum of an A.C. component i A (t) and a D.C. component I c and, considering that the losses of chopper circuit 10 itself are negligable, that the mean value of voltage v 21 is zero and that the D.C. component I c of i 21 does not take part in the energy transfer, one may write that the energy supplied by the D.C. source during this period E s =V A I C T H and the A.C. energy supplied by chopper circuit 10, ##EQU4## are roughly equal, i.e. ##EQU5## from which it appears that there is a mean D.C. current ##EQU6## supplied by source 5 which is a consequence of the exchange of energy between winding 21 and winding 22 in particular. The A.C. energy ceded, E H , and, as a result, the D.C. current I c of source 5, varies as a function of the cosine of the phase angle α between each of the respective harmonics of the current i 21 (t) and voltage v 21 (t). Hence one can obtain regulation by causing the phase of the wave of current i 21 (t) to vary in power supply winding 21 with respect to that of voltage v 21 (t) at its terminals to stabilize the sweep (the peak to peak amplitude of current i 31 ) and/or the very high voltage by acting on the charge supplied to capacitor 33 during each cycle.

This

is illustrated respectively on the diagrams (F) in FIGS. 2 and 3

showing the instantaneous power E i =-v 21 (t)i 21 (t) corresponding to

two different phase angles between waves v 21 and i 21 , which indicate

respectively minimum (zero) energy transfers when the zeros of current i

21 coincide with the maxima of voltage v 21 or when the respective

maxima of voltages v 21 and v 19 are out of phase by a half period T H

/2 and maximum energy transfers when the maxima of voltage v 21 and

current i 21 coincide between circuit 10 and output stage 30.

This

is illustrated respectively on the diagrams (F) in FIGS. 2 and 3

showing the instantaneous power E i =-v 21 (t)i 21 (t) corresponding to

two different phase angles between waves v 21 and i 21 , which indicate

respectively minimum (zero) energy transfers when the zeros of current i

21 coincide with the maxima of voltage v 21 or when the respective

maxima of voltages v 21 and v 19 are out of phase by a half period T H

/2 and maximum energy transfers when the maxima of voltage v 21 and

current i 21 coincide between circuit 10 and output stage 30.On the diagram (F) in FIG. 2, one can see that, when there is a phase difference between the corresponding (positive) maxima of v 21 (t) and i 21 (t) of a quarter of a line period (T H /4) roughly, the energy transfer is zero, because there is equality between the surfaces bounded by the curve and the abscissa, which are respectively above and below it and give a mean value of zero as far as the energy supplied is concerned.

On the other hand, on the diagram (F) in FIG. 3 in which the product-v 21 (t)i 21 (t) corresponds to a coincidence of phase between the respective maxima of voltage v 21 and i 21 , one can see that, when one subtracts from the surfaces above the abscissa the surfaces corresponding to the shaded triangles below it, three zones remain on the positive side whose surfaces correspond to the energy which is effectively transferred whose mean value ##EQU7## is positive and shows an effective transfer of energy to output stage 30. This translates into a D.C. voltage V 33 at the terminals of capacitor 33 which forms, during the forward sweep (closing of switch 35, 36), the sole load on winding 22 (terminal 220 being connected to the ground 39).

Hence, one has shown above that, by causing the phase difference between the corresponding maxima of waves v 21 (t) and i 21 (t) to vary between 0 and T H /4, one can cause the energy transmitted to vary and, as a result, the voltage V 221 at the terminals of capacitor 33 which feeds output stage 30.

When the relative phase difference between v 21 (t) and i 21 (t) exceeds a quarter of a line period, as, for example, when the negative peak amplitude of v 21 (t) coincides with the negative peak amplitude of i 21 (t), i.e. a phase difference equal to a line half period (T H /2), the term of the energy E H becomes negative which indicates that it is output stage 30 which feeds chopper circuit 10, or, more precisely, voltage source 5 (capacitor 4). This is not permanently possible unless it is output stage 30, and hence capacitor 33, which is fed by a rectifier assembly, thus showing the reversibility of the power supply device in accordance with the invention, which is contrary to classical chopper power supplies.

Hence, the regulation is done by causing the phase of the opening of switch 15 in chopper circuit 10 to be varied by the cutting off of transistor 11 with respect to the phase of the opening of sweep switch 36, 35, which is controlled by the line oscillator (not shown) and is generally slaved in frequency and phase to the line synchronizing pulses of the video complex signal.

Such a variable phase delay is obtained from line return pulses picked up on one of the windings of transformer 20, such as winding 21 itself or, as shown in FIG. 1, auxiliary winding 25. These pulses may trigger a monostable flip-flop whose length is variable as a function of the error voltage supplied by a comparator in the form of a differential amplifier, one of whose inputs receives a voltage corresponding either to the positive amplitude of v 21 (t), which is proportional to the voltage V 33 (V 221 ) at the terminals of power supply capacitor 33 in output stage 30, or to the peak to peak amplitude of the line return pulse, which is proportional to the very high voltage, or to a combination of these two criteria. The other input of the differential amplifier receives a D.C. reference voltage, which may be adjusted, to allow the adjustment of the very high voltage and/or the horizontal sweep current amplitude.

It is to be noted here that power supply winding 21 may be connected between terminal 6 of capacitor 4 and choke 14 in two opposite directions so that the line return pulses can appear at its junction with choke 14 with opposite polarities. Two possibilities of the relative phase of voltage v 21 (t) respect to the current i 21 (t) in winding 21 result from this.

In FIG. 4, one has shown a par

tial

block diagram (without a starting up device) of a simple way of making

regulation circuit 40 which controls the cut off of transistor 11 in

chopper circuit 10 with a delay which is variable with respect to the

line return pulse as a function of the negative peak amplitude of the

signal v 25 (t) supplied by auxiliary winding 25 of transformer 20.

tial

block diagram (without a starting up device) of a simple way of making

regulation circuit 40 which controls the cut off of transistor 11 in

chopper circuit 10 with a delay which is variable with respect to the

line return pulse as a function of the negative peak amplitude of the

signal v 25 (t) supplied by auxiliary winding 25 of transformer 20.Regulation circuit 40 in FIG. 4 is fed at its first input 401 with signal v 25 (t) supplied by one of the terminals 250 of auxiliary winding 25. This signal is roughly the reverse of signal v 21 (t) illustrated by the diagrams (C) respectively in FIGS. 2 and 3 in which one distinguishes, during each line period, a line return pulse of positive polarity and a negative plateau whose amplitude is proportional to D.C. voltage V 33 at the terminals of capacitor 30. This first input 401 feeds, through a first diode 410, the triggering input 411 of a first monostable flip-flop 41 of variable length, which produces at its output 413, in response to the leading edge of the return pulse, a rectangular signal whose length varies as a function of the D.C. voltage applied to its length control input 412.

Monostable flip-flops with a pulse length variable as a function of a D.C. voltage are known and a way of making them is described, for example, in French patent application No. 73.16116 made on May 4, 1973 by the present applicant.