GRUNDIG SUPER COLOR A2402 SERIE F3015 CHASSIS CUC91 Power supply Description based on TDA4601d (SIEMENS)

What is a Flyback Transformer?

The low cost, simplicity of design and intrinsic efficiency of flyback transformers have made them a popular solution for power supply designs of below 100W to 150W. Other advantages of the flyback transformer over circuits with similar topology include isolation between primary and secondary and the ability to provide multiple outputs and a choice of positive or negative voltage for the output.

Flyback transformer, or, line output transformers are a part of the power supplies in cathode ray tubes. The flyback transformer generates a high voltage, as needed by the CRT display or similar devices (e.g. plasma lamps). A flyback transformer generates a voltage between a few kilovolts to 50 kilovolts and uses high frequency switched currents between 17 kHz and 50 kHz.

The chief difference between a flyback transformer and main/audio transformer is that flybacks transfer as well as store energy, for a just a fraction of an entire switching period. The secret behind that is the coil winding on a ferrite core that has an air gap; it increases the magnetic circuit reluctance for storing the energy.

The reason it is called a flyback transformer is because the primary winding uses a relatively low-voltage saw-tooth wave. The wave gets strengthened first and then gets switched off abruptly; this causes the beam to fly back from right to left on the display.

Applications

Cathode ray tube.

Televisions.

Plasma Lamps.

Any display requiring high voltage to operate and much more.

TDA4601 Operation. * The TDA4601 device is a single in line, 9 pin chip. Its predecessor was the TDA4600 device, the TDA4601 however has improved switching, better protection and cooler running. The (SIEMENS) TDA4601 power supply is a fairly standard parallel chopper switch mode type, which operates on the same basic principle as a line output stage. It is turned on and off by a square wave drive pulse, when switched on energy is stored in the chopper transformer primary winding in the form of a magnetic flux; when the chopper is turned off the magnetic flux collapses, causing a large back emf to be produced. At the secondary side of the chopper transformer this is rectified and smoothed for H.T. supply purposes. The advantage of this type of supply is that the high chopping frequency (20 to 70 KHz according to load) allows the use of relatively small H.T. smoothing capacitors making smoothing easier. Also should the chopper device go short circuit there is no H.T. output. In order to start up the TDA4601 I.C. an initial supply of 9v is required at pin 9, this voltage is sourced via R818 and D805 from the AC side of the bridge rectifier D801, also pin 5 requires a +Ve bias for the internal logic block. (On some sets pin 5 is used for standby switching). Once the power supply is up and running, the voltage on pin 9 is increased to 16v and maintained at this level by D807 and C820 acting as a half wave rectifier and smoothing circuit. PIN DESCRIPTIONS Pin 1 This is a 4v reference produced within the I.C. Pin 2 This pin detects the exact point at which energy stored in the chopper transformer collapses to zero via R824 and R825, and allows Q1 to deliver drive volts to the chopper transistor. It also opens the switch at pin 4 allowing the external capacitor C813 to charge from its external feed resistor R810. Pin 3 H.T. control/feedback via photo coupler D830. The voltage at this pin controls the on time of the chopper transistor and hence the output voltage. Normally it runs at Approximately 2v and regulates H.T. by sensing a proportion of the +4v reference at pin 1, offset by conduction of the photo coupler D830 which acts like a variable resistor. An increase in the conduction of transistor D830 and therefor a reduction of its resistance will cause a corresponding reduction of the positive voltage at Pin 3. A decrease in this voltage will result in a shorter on time for the chopper transistor and therefor a lowering of the output voltage and vice versa, oscillation frequency also varies according to load, the higher the load the lower the frequency etc. should the voltage at pin 3 exceed 2.3v an internal flip flop is triggered causing the chopper drive mark space ratio to extend to 244 (off time) to 1 (on time), the chip is now in over volts trip condition. Pin 4 At this pin a sawtooth waveform is generated which simulates chopper current, it is produced by a time constant network R810 and C813. C813 charges when the chopper is on and is discharged when the chopper is off, by an internal switch strapping pin 4 to the internal +2v reference, see Fig 2. The amplitude of the ramp is proportional to chopper drive. In an overload condition it reaches 4v amplitude at which point chopper drive is reduced to a mark-space ratio of 13 to 1, the chip is then in over current trip. The I.C. can easily withstand a short circuit on the H.T. rail and in such a case the power supply simply squegs quietly. Pin 4 is protected by internal protection components which limit the maximum voltage at this pin to 6.5v. Should a fault occur in either of the time constant components, then the chopper transistor will probably be destroyed. Pin 5 This pin can be used for remote control on/off switching of the power supply, it is normally held at about +7v and will cause the chip to enter standby mode if it falls below 2v. Pin 6 Ground. Pin 7 Chopper switch off pin. This pin clamps the chopper drive voltage to 1.6v in order to switch off the chopper. Pin 8 Chopper base current output drive pin. Pin 9 L.T. pin, approximately 9v under start-up conditions and 16v during normal running, Current consumption of the I.C. is typically 135mA. The voltage at this pin must reach 6.7v in order for the chip to start-up.Semiconductor

circuit for supplying power to electrical equipment, comprising a

transformer having a primary winding connected, via a parallel

connection of a collector-emitter path of a transistor with a first

capacitor, to both outputs of a rectifier circuit supplied, in turn, by a

line a-c voltage; said transistor having a base controlled via a

second capacitor by an output of a control circuit acted upon, in turn

by the rectified a-c line voltage as actual value and by a reference

voltage; said transformer having a first secondary winding to which the

electrical equipment to be supplied is connected; said transformer

having a second secondary winding with one terminal thereof connected to

the emitter of said transistor and the other terminal thereof

connected to an anode of a first diode leading to said control circuit;

said transformer having a third secondary winding with one terminal

thereof connected, on the one hand, via a series connection of a third

capacitor with a first resistance, to the other terminal of said third

secondary winding and connected, on the other hand, to the emitter of

said transistor, the collector of which is connected to said primary

winding; a point between said third capacitor and said first resistance

being connected to the cathode of a second diode; said control circuit

having nine terminals including a first terminal delivering a

reference voltage and connected, via a voltage divider formed of a

third and fourth series-connected resistances, to the anode of said

second diode; a second terminal of said control circuit serving for

zero-crossing identification being connected via a fifth resistance to

said cathode of said second diode; a third terminal of said

control-circuit serving as actual value input being directly connected

to a divider point of said voltage divider forming said connection of

said first terminal of said control circuit to said anode of said

second diode; a fourth terminal of said control circuit delivering a

sawtooth voltage being connected via a sixth resistance to a terminal

of said primary winding of said transformer facing away from said

transistor; a fifth terminal of said control circuit serving as a

protective input being connected, via a seventh resistance to the

cathode of said first diode and, through the intermediary of said

seventh resistance and an eighth resistance, to the cathode of a third

diode having an anode connected to an input of said rectifier circuit; a

sixth terminal of said control circuit carrying said reference

potential and being connected via a fourth capacitor to said fourth

terminal of said control circuit and via a fifth capacitor to the anode

of said second diode; a seventh terminal of said control circuit

establishing a potential for pulses controlling said transistor being

connected directly and an eighth terminal of said control circuit

effecting pulse control of the base of said transistor being connected

through the intermediary of a ninth resistance to said first capacitor

leading to the base of said transistor; and a ninth terminal of said

control circuit serving as a power supply input of said control circuit

being connected both to the cathode of said first diode as well as via

the intermediary of a sixth capacitor to a terminal of said second

secondary winding as well as to a terminal of said third secondary

winding.

TDA4601 Operation. * The TDA4601 device is a single in line, 9 pin chip. Its predecessor was the TDA4600 device, the TDA4601 however has improved switching, better protection and cooler running. The (SIEMENS) TDA4601 power supply is a fairly standard parallel chopper switch mode type, which operates on the same basic principle as a line output stage. It is turned on and off by a square wave drive pulse, when switched on energy is stored in the chopper transformer primary winding in the form of a magnetic flux; when the chopper is turned off the magnetic flux collapses, causing a large back emf to be produced. At the secondary side of the chopper transformer this is rectified and smoothed for H.T. supply purposes. The advantage of this type of supply is that the high chopping frequency (20 to 70 KHz according to load) allows the use of relatively small H.T. smoothing capacitors making smoothing easier. Also should the chopper device go short circuit there is no H.T. output. In order to start up the TDA4601 I.C. an initial supply of 9v is required at pin 9, this voltage is sourced via R818 and D805 from the AC side of the bridge rectifier D801, also pin 5 requires a +Ve bias for the internal logic block. (On some sets pin 5 is used for standby switching). Once the power supply is up and running, the voltage on pin 9 is increased to 16v and maintained at this level by D807 and C820 acting as a half wave rectifier and smoothing circuit. PIN DESCRIPTIONS Pin 1 This is a 4v reference produced within the I.C. Pin 2 This pin detects the exact point at which energy stored in the chopper transformer collapses to zero via R824 and R825, and allows Q1 to deliver drive volts to the chopper transistor. It also opens the switch at pin 4 allowing the external capacitor C813 to charge from its external feed resistor R810. Pin 3 H.T. control/feedback via photo coupler D830. The voltage at this pin controls the on time of the chopper transistor and hence the output voltage. Normally it runs at Approximately 2v and regulates H.T. by sensing a proportion of the +4v reference at pin 1, offset by conduction of the photo coupler D830 which acts like a variable resistor. An increase in the conduction of transistor D830 and therefor a reduction of its resistance will cause a corresponding reduction of the positive voltage at Pin 3. A decrease in this voltage will result in a shorter on time for the chopper transistor and therefor a lowering of the output voltage and vice versa, oscillation frequency also varies according to load, the higher the load the lower the frequency etc. should the voltage at pin 3 exceed 2.3v an internal flip flop is triggered causing the chopper drive mark space ratio to extend to 244 (off time) to 1 (on time), the chip is now in over volts trip condition. Pin 4 At this pin a sawtooth waveform is generated which simulates chopper current, it is produced by a time constant network R810 and C813. C813 charges when the chopper is on and is discharged when the chopper is off, by an internal switch strapping pin 4 to the internal +2v reference, see Fig 2. The amplitude of the ramp is proportional to chopper drive. In an overload condition it reaches 4v amplitude at which point chopper drive is reduced to a mark-space ratio of 13 to 1, the chip is then in over current trip. The I.C. can easily withstand a short circuit on the H.T. rail and in such a case the power supply simply squegs quietly. Pin 4 is protected by internal protection components which limit the maximum voltage at this pin to 6.5v. Should a fault occur in either of the time constant components, then the chopper transistor will probably be destroyed. Pin 5 This pin can be used for remote control on/off switching of the power supply, it is normally held at about +7v and will cause the chip to enter standby mode if it falls below 2v. Pin 6 Ground. Pin 7 Chopper switch off pin. This pin clamps the chopper drive voltage to 1.6v in order to switch off the chopper. Pin 8 Chopper base current output drive pin. Pin 9 L.T. pin, approximately 9v under start-up conditions and 16v during normal running, Current consumption of the I.C. is typically 135mA. The voltage at this pin must reach 6.7v in order for the chip to start-up.Semiconductor

circuit for supplying power to electrical equipment, comprising a

transformer having a primary winding connected, via a parallel

connection of a collector-emitter path of a transistor with a first

capacitor, to both outputs of a rectifier circuit supplied, in turn, by a

line a-c voltage; said transistor having a base controlled via a

second capacitor by an output of a control circuit acted upon, in turn

by the rectified a-c line voltage as actual value and by a reference

voltage; said transformer having a first secondary winding to which the

electrical equipment to be supplied is connected; said transformer

having a second secondary winding with one terminal thereof connected to

the emitter of said transistor and the other terminal thereof

connected to an anode of a first diode leading to said control circuit;

said transformer having a third secondary winding with one terminal

thereof connected, on the one hand, via a series connection of a third

capacitor with a first resistance, to the other terminal of said third

secondary winding and connected, on the other hand, to the emitter of

said transistor, the collector of which is connected to said primary

winding; a point between said third capacitor and said first resistance

being connected to the cathode of a second diode; said control circuit

having nine terminals including a first terminal delivering a

reference voltage and connected, via a voltage divider formed of a

third and fourth series-connected resistances, to the anode of said

second diode; a second terminal of said control circuit serving for

zero-crossing identification being connected via a fifth resistance to

said cathode of said second diode; a third terminal of said

control-circuit serving as actual value input being directly connected

to a divider point of said voltage divider forming said connection of

said first terminal of said control circuit to said anode of said

second diode; a fourth terminal of said control circuit delivering a

sawtooth voltage being connected via a sixth resistance to a terminal

of said primary winding of said transformer facing away from said

transistor; a fifth terminal of said control circuit serving as a

protective input being connected, via a seventh resistance to the

cathode of said first diode and, through the intermediary of said

seventh resistance and an eighth resistance, to the cathode of a third

diode having an anode connected to an input of said rectifier circuit; a

sixth terminal of said control circuit carrying said reference

potential and being connected via a fourth capacitor to said fourth

terminal of said control circuit and via a fifth capacitor to the anode

of said second diode; a seventh terminal of said control circuit

establishing a potential for pulses controlling said transistor being

connected directly and an eighth terminal of said control circuit

effecting pulse control of the base of said transistor being connected

through the intermediary of a ninth resistance to said first capacitor

leading to the base of said transistor; and a ninth terminal of said

control circuit serving as a power supply input of said control circuit

being connected both to the cathode of said first diode as well as via

the intermediary of a sixth capacitor to a terminal of said second

secondary winding as well as to a terminal of said third secondary

winding. The

invention relates to a blocking oscillator type switching power supply

for supplying power to electrical equipment, wherein the primary

winding of a transformer, in series with the emitter-collector path of a

first bipolar transistor, is connected to a d-c voltage obtained by

rectification of a line a-c voltage fed-in via two external supply

terminals, and a secondary winding of the transformer is provided for

supplying power to the electrical equipment, wherein, furthermore, the

first bipolar transistor has a base controlled by the output of a

control circuit which is acted upon in turn by the rectified a-c line

voltage as actual value and by a set-point transmitter, and wherein a

starting circuit for further control of the base of the first bipolar

transistor is provided.

The

invention relates to a blocking oscillator type switching power supply

for supplying power to electrical equipment, wherein the primary

winding of a transformer, in series with the emitter-collector path of a

first bipolar transistor, is connected to a d-c voltage obtained by

rectification of a line a-c voltage fed-in via two external supply

terminals, and a secondary winding of the transformer is provided for

supplying power to the electrical equipment, wherein, furthermore, the

first bipolar transistor has a base controlled by the output of a

control circuit which is acted upon in turn by the rectified a-c line

voltage as actual value and by a set-point transmitter, and wherein a

starting circuit for further control of the base of the first bipolar

transistor is provided. Such a blocking oscillator switching power supply is described in the German periodical, "Funkschau" (1975) No. 5, pages 40 to 44. It is well known that the purpose of such a circuit is to supply electronic equipment, for example, a television set, with stabilized and controlled supply voltages. Essential for such switching power supply is a power switching transistor i.e. a bipolar transistor with high switching speed and high reverse voltage. This transistor therefore constitutes an important component of the control element of the control circuit. Furthermore, a high operating frequency and a transformer intended for a high operating frequency are provided, because generally, a thorough separation of the equipment to be supplied from the supply naturally is desired. Such switching power supplies may be constructed either for synchronized or externally controlled operation or for non-synchronized or free-running operation. A blocking converter is understood to be a switching power supply in which power is delivered to the equipment to be supplied only if the switching transistor establishing the connection between the primary coil of the transformer and the rectified a-c voltage is cut off. The power delivered by the line rectifier to the primary coil of the transformer while the switching transistor is open, is interim-stored in the transformer and then delivered to the consumer on the secondary side of the transformer with the switching transistor cut off.

In the blocking converter described in the aforementioned reference in the literature, "Funkschau" (1975), No. 5, Pages 40 to 44, the power switching transistor is connected in the manner defined in the introduction to this application. In addition, a so-called starting circuit is provided. Because several diodes are generally provided in the overall circuit of a blocking oscillator according to the definition provided in the introduction hereto, it is necessary, in order not to damage these diodes, that due to the collector peak current in the case of a short circuit, no excessive stress of these diodes and possibly existing further sensitive circuit parts can occur.

Considering

the operation of a blocking oscillator, this means that, in the event

of a short circuit, the number of collector current pulses per unit

time must be reduced. For this purpose, a control and regulating

circuit is provided. Simultaneously, a starting circuit must bring the

blocking converter back to normal operation when the equipment is

switched on, and after disturbances, for example, in the event of a

short circuit. The starting circuit shown in the literature reference

"Funkschau" on Page 42 thereof, differs to some extent already from the

conventional d-c starting circuits. It is commonly known for all

heretofore known blocking oscillator circuits, however, that a

thyristor or an equivalent circuit replacing the thyristor is essential

for the operation of the control circuit.

Considering

the operation of a blocking oscillator, this means that, in the event

of a short circuit, the number of collector current pulses per unit

time must be reduced. For this purpose, a control and regulating

circuit is provided. Simultaneously, a starting circuit must bring the

blocking converter back to normal operation when the equipment is

switched on, and after disturbances, for example, in the event of a

short circuit. The starting circuit shown in the literature reference

"Funkschau" on Page 42 thereof, differs to some extent already from the

conventional d-c starting circuits. It is commonly known for all

heretofore known blocking oscillator circuits, however, that a

thyristor or an equivalent circuit replacing the thyristor is essential

for the operation of the control circuit.  It

is accordingly an object of the invention to provide another starting

circuit. It is a further object of the invention to provide a possible

circuit for the control circuit which is particularly well suited for

this purpose. It is yet another object of the invention to provide such a

power supply which is assured of operation over the entire range of

line voltages from 90 to 270 V a-c, while the secondary voltages and

secondary load variations between no-load and short circuit are largely

constant.

It

is accordingly an object of the invention to provide another starting

circuit. It is a further object of the invention to provide a possible

circuit for the control circuit which is particularly well suited for

this purpose. It is yet another object of the invention to provide such a

power supply which is assured of operation over the entire range of

line voltages from 90 to 270 V a-c, while the secondary voltages and

secondary load variations between no-load and short circuit are largely

constant. With the foregoing and other objects in view, there is provided, in accordance with the invention, a blocking oscillator-type switching power supply for supplying power to electrical equipment wherein a primary winding of a transformer, in series with an emitter-collector path of a first bipolar transistor, is connected to a d-c voltage obtained by rectification of a line a-c voltage fed-in via two external supply terminals, a secondary winding of the transformer being connectible to the electrical equipment for supplying power thereto, the first bipolar transistor having a base controlled by the output of a control circuit acted upon, in turn, by the rectified a-c line voltage as actual value and by a set-point transmitter, and including a starting circuit for further control of the base of the first bipolar transistor, including a first diode in the starting circuit having an anode directly connected to one of the supply terminals supplied by the a-c line voltage and a cathode connected via a resistor to an input serving to supply power to the c

ontrol circuit,

the input being directly connected to a cathode of a second diode, the

second diode having an anode connected to one terminal of another

secondary winding of the transformer, the other secondary winding having

another terminal connected to the emitter of the first bipolar

transmitter.

ontrol circuit,

the input being directly connected to a cathode of a second diode, the

second diode having an anode connected to one terminal of another

secondary winding of the transformer, the other secondary winding having

another terminal connected to the emitter of the first bipolar

transmitter. In accordance with another feature of the invention, there is provided a second bipolar transistor having the same conduction type as that of the first bipolar transistor and connected in the starting circuit with the base thereof connected to a cathode of a semiconductor diode, the semiconductor diode having an anode connected to the emitter of the first bipolar transistor, the second bipolar transistor having a collector connected via a resistor to a cathode of the first diode in the starting circuit, and having an emitter connected to the input serving to supply power to the control circuit and also connected to the cathode of the second diode which is connected to the other secondary winding of the transformer.

In accordance with a further feature of the invention, the base of the second bipolar transistor is connected to a resistor and via the latter to one pole of a first capacitor, the anode of the first diode being connected to the other pole of the first capacitor.

In

accordance with an added feature of the invention, the input serving

to supply power to the control circuit is connected via a second

capacitor to an output of a line rectifier, the output of the line

rectifier being directly connected to the emitter of the first bipolar

transistor.

In

accordance with an added feature of the invention, the input serving

to supply power to the control circuit is connected via a second

capacitor to an output of a line rectifier, the output of the line

rectifier being directly connected to the emitter of the first bipolar

transistor. In accordance with an additional feature of the invention, the other secondary winding is connected at one end to the emitter of the first bipolar transistor and to a pole of a third capacitor, the third capacitor having another pole connected, on the one hand, via a resistor, to the other end of the other secondary winding and, on the other hand, to a cathode of a third diode, the third diode having an anode connected via a potentiometer to an actual value input of the control circuit and, via a fourth capacitor, to the emitter of the first bipolar transistor.

In accordance with yet another feature of the invention, the control circuit has a control output connected via a fifth capacitor to the base of the first bipolar transistor for conducting to the latter control pulses generated in the control circuit.

In accordance with a concomitant feature of the invention, there is provided a sixth capacitor shunting the emitter-collector path of the first transistor.

Other features which are considered as characteristic for the invention are set forth in the appended claim.

Although the invention is illustrated and described herein as embodied in a blocking oscillator type switching power supply, it is nevertheless not intended to be limited to the details shown, since various modifications and structural changes may be made therein without departing from the spirit of the invention and within the scope and range of equivalents of the claims. The construction and method of operation of the invention, however, together with additional objects and advantages thereof will be best understood from the following description of specific embodiments when read in connection with the accompanying drawings, in which:

FIGS. 1 and 2 are circuit diagrams of the blocking oscillator type switching power supply according to the invention; and

FIG. 3 is a circuit diagram of the control unit RS of FIGS. 1 and 2.

Referring now to the drawing and, first, particularly to FIG. 1 thereof, there is shown a rectifier circuit G in the form of a bridge current, which is acted upon by a line input represented by two supply terminals 1' and 2'. Rectifier outputs 3' and 4' are shunted by an emitter-collector path of an NPN power transistor T1 i.e. t

he

series connection of the so-called first bipolar transistor referred to

hereinbefore with a primary winding I of a transformer Tr. Together

with the inductance of the transformer Tr, the capacitance C1 determines

the frequency and limits the opening voltages of the switch embodied by

the first transistor T1. A capacitance C2, provided between the base of

the first transistor T1 and the control output 7,8 of a control circuit

RS, separates the d-c potentials of the control or regulating circuit

RS and the switching transistor T1 and serves for addressing this

switching transistor T1 with pulses. A resistor R1 provided at the

control output 7,8 of the control circuit RS is the negative-feedback

resistor of both output stages of the control circuit RS. It determines

the maximally possible output pulse current of the control circuit RS. A

secondary winding II of the transformer Tr takes over the power supply

of the control circuit, in steady state operation, via the diode D1. To

this end, the cathode of this diode D1 is directly connected to a power

supply input 9 of the control circuit RS, while the anode thereof is

connected to one terminal of the secondary winding II. The other

terminal of the secondary winding II is connected to the emitter of the

power switching transistor T1.

he

series connection of the so-called first bipolar transistor referred to

hereinbefore with a primary winding I of a transformer Tr. Together

with the inductance of the transformer Tr, the capacitance C1 determines

the frequency and limits the opening voltages of the switch embodied by

the first transistor T1. A capacitance C2, provided between the base of

the first transistor T1 and the control output 7,8 of a control circuit

RS, separates the d-c potentials of the control or regulating circuit

RS and the switching transistor T1 and serves for addressing this

switching transistor T1 with pulses. A resistor R1 provided at the

control output 7,8 of the control circuit RS is the negative-feedback

resistor of both output stages of the control circuit RS. It determines

the maximally possible output pulse current of the control circuit RS. A

secondary winding II of the transformer Tr takes over the power supply

of the control circuit, in steady state operation, via the diode D1. To

this end, the cathode of this diode D1 is directly connected to a power

supply input 9 of the control circuit RS, while the anode thereof is

connected to one terminal of the secondary winding II. The other

terminal of the secondary winding II is connected to the emitter of the

power switching transistor T1.The cathode of the diode D1 and, therewith, the power supply terminal 9 of the control circuits RS are furthermore connected to one pole of a capacitor C3, the other pole of which is connected to the output 3' of the rectifier G. The capacitance of this capacitor C3 thereby smoothes the positive half-wave pulses and serves simultaneously as an energy storage device during the starting period. Another secondary windi

ng

III of the transformer Tr is connected by one of the leads thereof

likewise to the emitter of the first transistor T1, and by the other

lead thereof via a resistor R2, to one of the poles of a further

capacitor C4, the other pole of which is connected to the

first-mentioned lead of the other secondary winding III. This second

pole of the capacitor C4 is simultaneously connected to the output 3' of

the rectifier circuit G and, thereby, via the capacitor C3, to the

cathode of the diode D1 driven by the secondary winding II of the

transformer Tr as well as to the power supply input 9 of the control

circuit RS and, via a resistor R9, to the cathode of a second diode D4.

The second pole of the capacitor C4 is simultaneously connected directly

to the terminal 6 of the control circuit RS and, via a further

capacitor C 6, to the terminal 4 of the control circuit RS as well as,

additionally, via the resistor R6, to the other output 4' of the

rectifier circuit G. The other of the poles of the capacitor C4 acted

upon by the secondary winding II is connected via a further capacitor C5

to a node, which is connected on one side thereof, via a variable

resistor R4, to the terminals 1 and 3 of the control circuit RS, with

the intermediary of a fixed resistor R5 in the case of the terminal 1.

On the other side of the node, the latter and, therefore, the capacitor

C5 are connected to the anode of a third diode D2, the cathode of which

is connected on the one hand, to the resistor R2 mentioned hereinbefore

and leads to the secondary winding III of the transformer Tr and, on the

other hand, via a resistor R3 to the terminal 2 of the control circuit

RS.

ng

III of the transformer Tr is connected by one of the leads thereof

likewise to the emitter of the first transistor T1, and by the other

lead thereof via a resistor R2, to one of the poles of a further

capacitor C4, the other pole of which is connected to the

first-mentioned lead of the other secondary winding III. This second

pole of the capacitor C4 is simultaneously connected to the output 3' of

the rectifier circuit G and, thereby, via the capacitor C3, to the

cathode of the diode D1 driven by the secondary winding II of the

transformer Tr as well as to the power supply input 9 of the control

circuit RS and, via a resistor R9, to the cathode of a second diode D4.

The second pole of the capacitor C4 is simultaneously connected directly

to the terminal 6 of the control circuit RS and, via a further

capacitor C 6, to the terminal 4 of the control circuit RS as well as,

additionally, via the resistor R6, to the other output 4' of the

rectifier circuit G. The other of the poles of the capacitor C4 acted

upon by the secondary winding II is connected via a further capacitor C5

to a node, which is connected on one side thereof, via a variable

resistor R4, to the terminals 1 and 3 of the control circuit RS, with

the intermediary of a fixed resistor R5 in the case of the terminal 1.

On the other side of the node, the latter and, therefore, the capacitor

C5 are connected to the anode of a third diode D2, the cathode of which

is connected on the one hand, to the resistor R2 mentioned hereinbefore

and leads to the secondary winding III of the transformer Tr and, on the

other hand, via a resistor R3 to the terminal 2 of the control circuit

RS.The nine terminals of the control circuit RS have the following purposes or functions:

Terminal 1 supplies the internally generated reference voltage to ground i.e. the nominal or reference value required for the control or regulating process;

Terminal 2 serves as input for the oscillations provided by the secondary winding III, at the zero point of which, the pulse start of the driving pulse takes place;

Terminal 3 is the control input, at which the existing actual value is communicated to the control circuit RS, that actual value being generated by the rectified oscillations at the secondary winding III;

Terminal 4 is responsive to the occurrence of a maximum excursion i.e. when the largest current flows through the first transistor T1 ;

Terminal 5 is a protective input which responds if the rectified line voltage drops too sharply; Terminal 6 serves for the power supply of the control process and, indeed, as ground terminal;

Terminal 7 supplies the d-c component required for charging the coupling capacitor C2 leading to the base of the first transistor T1 ;

Terminal 8 supplies the control pulse required for the base of the first transistor T1 ; and

Terminal 9 serves as the first terminal of the power supply of the control circuit RS.

Further details of the control circuit RS are described hereinbelow.

The capacity C3 smoothes the positive half-wave pulses which are provided by the secondary winding II, and simultaneously serves as an energy storage device during the starting time. The secondary winding III generates the control voltage and is simultaneously used

as

feedback. The time delay stage R2 /C4 keeps harmonics and fast

interference spikes away from the control circuit RS. The resistor R3 is

provided as a voltage divider for the second terminal of the control

circuit RS. The diode D2 rectifies the control pulses delivered by the

secondary winding III. The capacity C5 smoothes the control voltage. A

reference voltage Uref, which is referred to ground i.e. the potential

of terminal 6 is present at the terminal 1 of the control circuit RS.

The resistors R4 and R5 form a voltage divider of the input-difference

control amplifier at the terminal 3. The desired secondary voltage can

be set manually via the variable resistor R4. A time-delay stage R6 /C6

forms a sawtooth rise which corresponds to the collector current rise of

the first bipolar transistor T1 via the primary winding I of the

transformer Tr. The sawtooth present at the terminal 4 of the control

circuit RS is limited there between the reference voltage 2 V and 4 V.

The voltage divider R7 /R8 (FIG. 2), brings to the terminal 5 of the

control circuit RS the enabling voltage for the drive pulse at the

output 8 of the control circuit RS.

as

feedback. The time delay stage R2 /C4 keeps harmonics and fast

interference spikes away from the control circuit RS. The resistor R3 is

provided as a voltage divider for the second terminal of the control

circuit RS. The diode D2 rectifies the control pulses delivered by the

secondary winding III. The capacity C5 smoothes the control voltage. A

reference voltage Uref, which is referred to ground i.e. the potential

of terminal 6 is present at the terminal 1 of the control circuit RS.

The resistors R4 and R5 form a voltage divider of the input-difference

control amplifier at the terminal 3. The desired secondary voltage can

be set manually via the variable resistor R4. A time-delay stage R6 /C6

forms a sawtooth rise which corresponds to the collector current rise of

the first bipolar transistor T1 via the primary winding I of the

transformer Tr. The sawtooth present at the terminal 4 of the control

circuit RS is limited there between the reference voltage 2 V and 4 V.

The voltage divider R7 /R8 (FIG. 2), brings to the terminal 5 of the

control circuit RS the enabling voltage for the drive pulse at the

output 8 of the control circuit RS.The diode D4, together with the resistor R9 in cooperation with the diode D1 and the secondary winding II, forms the starting circuit provided, in accordance with the invention. The operation thereof is as follows:

After the switching power supply is switched on, d-c voltages build up at the collector of the switching transistor T1 and at the input 4 of the control circuit RS, as a function in time of the predetermined time constants. The positive sinusoidal half-waves charge the capacitor C3 via the starting diode D4 and the starting resistor R9 in dependence upon the time constant R9.C3. Via the protective input terminal 5 and the resisto

r

R11 not previously mentioned and forming the connection between the

resistor R9 and the diode D1, on the one hand, and the terminal 5 of the

control circuit RS, on the other hand, the control circuit RS is biased

ready for switching-on, and the capacitor C2 is charged via the output

7. When a predetermined voltage value at the capacitor C3 or the power

supply input 9 of the control circuit RS, respectively, is reached, the

reference voltage i.e. the nominal value for the operation of the

control voltage RS, is abruptly formed, which supplies all stages of the

control circuit and appears at the output 1 thereof. Simultaneously,

the switching transistor T1 is switched into conduction via the output

8. The switching of the transistor T1 at the primary winding T of the

transformer Tr is transformed to the second secondary winding II, the

capacity C3 being thereby charged up again via the diode D1. If

sufficient energy is stored in the capacitor C3 and if the re-charge via

the diode D1 is sufficient so that the voltage at a supply input 9 does

not fall below the given minimum operating voltage, the switching power

supply then remains connected, so that the starting process is

completed. Otherwise, the starting process described is repeated several

times.

r

R11 not previously mentioned and forming the connection between the

resistor R9 and the diode D1, on the one hand, and the terminal 5 of the

control circuit RS, on the other hand, the control circuit RS is biased

ready for switching-on, and the capacitor C2 is charged via the output

7. When a predetermined voltage value at the capacitor C3 or the power

supply input 9 of the control circuit RS, respectively, is reached, the

reference voltage i.e. the nominal value for the operation of the

control voltage RS, is abruptly formed, which supplies all stages of the

control circuit and appears at the output 1 thereof. Simultaneously,

the switching transistor T1 is switched into conduction via the output

8. The switching of the transistor T1 at the primary winding T of the

transformer Tr is transformed to the second secondary winding II, the

capacity C3 being thereby charged up again via the diode D1. If

sufficient energy is stored in the capacitor C3 and if the re-charge via

the diode D1 is sufficient so that the voltage at a supply input 9 does

not fall below the given minimum operating voltage, the switching power

supply then remains connected, so that the starting process is

completed. Otherwise, the starting process described is repeated several

times.In FIG. 2, there is shown a further embodiment of the circuit for a blocking oscillator type switching power supply, according to the invention, as shown in FIG. 1. Essential for this circuit of FIG. 2 is the presence of a second bipolar transistor T2 of the type of the first bipolar transistor T1 (i.e. in the embodiments of the invention, an npn-transistor), which forms a further component of the starting circuit and is connected with the collector-emitter path thereof between the resistor R9 of the starting circuit and the current supply input 9 of the control circuit RS. The base of this second transistor T2 is connected to a node which leads, on the one hand, via a resistor R10 to one electrode of a capacitor C7, the other electrode of which is connected to the anode of the diode D4 of the starting circuit and, accordingl

y,

to the terminal 1' of the supply input of the switching power supply G.

On the other hand, the last-mentioned node and, therefore, the base of

the second transistor T2 are connected to the cathode of a Zener diode

D3, the anode of which is connected to the output 3' of the rectifier G

and, whereby, to one pole of the capacitor C3, the second pole of which

is connected to the power supply input 9 of the control circuit RS as

well as to the cathode of the diode D1 and to the emitter of the second

transistor T2. In other respects, the circuit according to FIG. 2

corresponds to the circuit according to FIG. 1 except for the resistor

R11 which is not necessary in the embodiment of FIG. 2, and the missing

connection between the resistor R9 and the cathode of the diode D1,

respectively, and the protective input 5 of the control circuit RS.

y,

to the terminal 1' of the supply input of the switching power supply G.

On the other hand, the last-mentioned node and, therefore, the base of

the second transistor T2 are connected to the cathode of a Zener diode

D3, the anode of which is connected to the output 3' of the rectifier G

and, whereby, to one pole of the capacitor C3, the second pole of which

is connected to the power supply input 9 of the control circuit RS as

well as to the cathode of the diode D1 and to the emitter of the second

transistor T2. In other respects, the circuit according to FIG. 2

corresponds to the circuit according to FIG. 1 except for the resistor

R11 which is not necessary in the embodiment of FIG. 2, and the missing

connection between the resistor R9 and the cathode of the diode D1,

respectively, and the protective input 5 of the control circuit RS.Regarding the operation of the starting circuit according to FIG. 2,

it can be stated that the positive sinusoidal half-wave of the line

voltage, delayed by the time delay stage C7, R10 drives the base of the

transistor T2 in the starting circuit. The amplitude is limited by the

diode D3 which is provided for overvoltage protection of the control

circuit RS and which is preferably incorporated as a Zener diode. The

second transistor T2 is switched into conduction. The capacity C3 is

charged, via the serially connected diode D4 and the resistor R9 and the

collector-emitter path of the transistor T2, as soon as the voltage

between the terminal 9 and the terminal 6 of the control circuit RS i.e.

the voltage U9, meets the condition U9 <[UDs -UBE (T2)].

it can be stated that the positive sinusoidal half-wave of the line

voltage, delayed by the time delay stage C7, R10 drives the base of the

transistor T2 in the starting circuit. The amplitude is limited by the

diode D3 which is provided for overvoltage protection of the control

circuit RS and which is preferably incorporated as a Zener diode. The

second transistor T2 is switched into conduction. The capacity C3 is

charged, via the serially connected diode D4 and the resistor R9 and the

collector-emitter path of the transistor T2, as soon as the voltage

between the terminal 9 and the terminal 6 of the control circuit RS i.e.

the voltage U9, meets the condition U9 <[UDs -UBE (T2)].Because of the time constant R9.C3, several positive half-waves are necessary in order to increase the voltage U9 at the supply terminal 9 of the control circuit RS to such an extent that the control circuit RS is energized. During the negative sine half-wave, a partial energy chargeback takes place from the capacitor C3 via the emitter-base path of the transistor T2 of the starting circuit and via the resistor R10 and the capacitor C7, respectively, into the supply network. At approximately 2/3 of the voltage U9, which is limited by the diode D3, the control circuit RS is switched on. At the terminal 1 thereof, the reference voltage Uref then appears. In addition, the voltage divider R5 /R4 becomes effective. At the terminal 3, the control amplifier receives the voltage forming the actual value, while the first bipolar transistor T1 of the blocking-oscillator type switching power supply is addressed pulsewise via the terminal 8.

Because the capacitor C6 is charged via the resistor R6, a higher voltage than Uref is present at the terminal 4 if the control circuit RS is activated. The control voltage then discharges the capacitor C6 via the terminal 4 to half the value of the reference voltage Uref, and immediately cuts off the addressing input 8 of the control circuit RS. The first driving pulse of the switching transistor T1 is thereby limited to a minimum of time. The power for switching-on the control circuit RS and for driving the transistor T1 is supplied by the capacitor C3. The voltage U9 at the capacitor C3 then drops. If the voltage U9 drops below the switching-off voltage value of the control circuit RS, the latter is then inactivated. The next positive sine half-wave would initiate the starting process again.

By switching the transistor T1, a voltage is transformed in the secondary winding II of the transformer Tr. The positive component is rectified by the diode D1, recharing of the capacitor C3 being thereby provided. The voltage U9 at the output 9 does not, therefore, drop below the minimum value required for the operation of the control circuit RS, so that the control circuit RS remains activated. The power supply continues to operate in the rhythm of the existing conditions. In operation, the voltage U9 at the supply terminal 9 of the control circuit RS has a value which meets the condition U9 >[UDs -UBE (T2)], so that the transistor T2 of the starting circuit remains cut off.

For the internal layout of the control circuit RS, the construction shown, in particular, from FIG. 3 is advisable. This construction is realized, for example, in the commercially available type TDA 4600 (Siemens AG).

The block diagram of the control circuit according to FIG. 3

shows

the power supply thereof via the terminal 9, the output stage being

supplied directly whereas all other stages are supplied via Uref. In the

starting circuit, the individual subassemblies are supplied with power

sequentially. The d-c output voltage potential of the base current gain

i.e. the voltage for the terminal 8 of the control circuit RS, and the

charging of the capacitor C2 via the terminal 7 are formed even before

the reference voltage Uref appears. Variations of the supply voltage U9

at terminal 9 and the power fluctuations at the terminal 8/terminal 7

and at the terminal 1 of the control circuit RS are leveled or smoothed

out by the voltage control. The temperature sensitivity of the control

circuit RS and, in particular, the uneven heating of the output and

input stages and input stages on the semiconductor chip containing the

control circuit in monolithically integrated form are intercepted by the

temperature compensation provided. The output values are constant in a

specific temperature range. The message for blocking the output stage,

if the supply voltage at the terminal 9 is too low, is given also by

this subassembly to a provided control logic.

shows

the power supply thereof via the terminal 9, the output stage being

supplied directly whereas all other stages are supplied via Uref. In the

starting circuit, the individual subassemblies are supplied with power

sequentially. The d-c output voltage potential of the base current gain

i.e. the voltage for the terminal 8 of the control circuit RS, and the

charging of the capacitor C2 via the terminal 7 are formed even before

the reference voltage Uref appears. Variations of the supply voltage U9

at terminal 9 and the power fluctuations at the terminal 8/terminal 7

and at the terminal 1 of the control circuit RS are leveled or smoothed

out by the voltage control. The temperature sensitivity of the control

circuit RS and, in particular, the uneven heating of the output and

input stages and input stages on the semiconductor chip containing the

control circuit in monolithically integrated form are intercepted by the

temperature compensation provided. The output values are constant in a

specific temperature range. The message for blocking the output stage,

if the supply voltage at the terminal 9 is too low, is given also by

this subassembly to a provided control logic.The outer voltage divider of the terminal 1 via the r

esistors

R5 and R4 to the control tap U forms, via terminal 3, the variable side

of the bridge for the control amplifier formed as a differential

amplifier. The fixed bridge side is formed by the reference voltage Uref

via an internal voltage divider. Similarly formed are circuit portions

serving for the detection of an overload short circuit and circuit

portions serving for the "standby" no-load detection, which can be

operated likewise via terminal 3.

esistors

R5 and R4 to the control tap U forms, via terminal 3, the variable side

of the bridge for the control amplifier formed as a differential

amplifier. The fixed bridge side is formed by the reference voltage Uref

via an internal voltage divider. Similarly formed are circuit portions

serving for the detection of an overload short circuit and circuit

portions serving for the "standby" no-load detection, which can be

operated likewise via terminal 3.Within a provided trigger circuit, the driving pulse length is determined as a function of the sawtooth rise at the terminal 4, and is transmitted to the control logic. In the control logic, the commands of the trigger circuit are processed. Through the zero-crossing identification at input 2 in the control circuit RS, the control logic is enabled to start the control input only at the zero point of the frequency oscillation. If the voltages at the terminal 5 and at the terminal 9 are too low, the control logic blocks the output amplifier at the terminal 8. The output amplifier at the terminal 7 which is responsible for the base charge in the capacitor C2, is not touched thereby.

The base current gain for the transistor T1 i.e. for the first transistor in accordance with the definition of the invention, is formed by two amplifiers which mutually operate on the capacitor C2. The roof inclination of the base driving current for the transistor T1 is impressed by the collector current simulation at the terminal 4 to the amplifier at the terminal 8. The control pulse for the transistor T1 at the terminal 8 is always built up to the potential present at the terminal 7. The amplifier working into the terminal 7 ensures that each new switching pulse at the terminal 8 finds the required base level at terminal 7.

Supplementing the comments regarding FIG. 1, it should also be mentioned that the cathode of the diode D1 connected by the anode thereof to the one end of the secondary winding II of the transformer Tr is connected via a resistor R11 to the protective input 5 of the control circuit RS whereas, in the circuit according to FIG. 2, the protective input 5 of the control circuit RS is supplied via a voltage divider R8, R7 directly from the output 3', 4' of the rectifier G delivering the rectified line a-c voltage, and which obtains the voltage required for executing its function. It is evident that the first possible manner of driving the protective input 5 can be used also in the circuit according to FIG. 2, and the second possibility also in a circuit in accordance with FIG. 1.

The control circuit RS which is shown in FIG. 3 and is realized in detail by the building block TDA 4600 and which is particularly well suited in conjunction with the blocking oscillator type switching power supply according to the invention has 9 terminals 1-9, which have the following characteristics, as has been explained in essence hereinabove:

Terminal 1 delivers a reference voltage Uref which serves as the constant-current source of a voltage divider R5.R4 which supplies the required d-c voltages for the differential amplifiers provided for the functions control, overload detection, short-circuit detection and "standby"-no load detection. The dividing point of the voltage divider R5 -R4 is connected to the terminal 3 of the control circuit RS. The terminal 3 provided as the control input of RS is controlled in the manner described hereinabove as input for the actual value of the voltage to be controlled or regulated by the secondary winding III of the transformer Tr. With this input, the lengths of the control pulses for the switching transistor T1 are determined.

Via the input provided by the terminal 2 of the control circuit RS, the zero-point identification in the control circuit is addressed for detecting the zero-point o

f

the oscillations respectively applied to the terminal 2. If this

oscillation changes over to the positive part, then the addressing pulse

controlling the switching transistor T1 via the terminal 8 is released

in the control logic provided in the control circuit.

f

the oscillations respectively applied to the terminal 2. If this

oscillation changes over to the positive part, then the addressing pulse

controlling the switching transistor T1 via the terminal 8 is released

in the control logic provided in the control circuit.A sawtooth-shaped voltage, the rise of which corresponds to the collector current of the switching transistor T1, is present at the terminal 4 and is minimally and maximally limited by two reference voltages. The sawtooth voltage serves, on the one hand as a comparator for the pulse length while, on the other hand, the slope or rise thereof is used to obtain in the base current amplification for the switching transistor T1, via the terminal 8, a base drive of this switching transistor T1 which is proportional to the collector current.

The terminal 7 of the control circuit RS as explained hereinbefore, determines the voltage potential for the addressing pulses of the transistor T2. The base of the switching transistor T1 is pulse-controlled via the terminal 8, as described hereinbefore. Terminal 9 is connected as the power supply input of the control circuit RS. If a voltage level falls below a given value, the terminal 8 is blocked. If a given positive value of the voltage level is exceeded, the control circuit is activated. The terminal 5 releases the terminal 8 only if a given voltage potential is present.

Forei

gn References:

gn References:DE2417628A1 1975-10-23 363/37

DE2638225A1 1978-03-02 363/49

Other References:

Grundig Tech. Info. (Germany), vol. 28, No. 4, (1981).

IBM Technical Disclosure Bulletin, vol. 19, No. 3, pp. 978, 979, Aug. 1976.

German Periodical, "Funkschau", (1975), No. 5, pp. 40 to 44.

Testing Flyback Transformer:

Nowadays, more and more monitor comes in with flyback transformers problems.

Testing flyback transformer are not difficult if you carefully follow the

instruction. In many cases, the flyback transformer can become short

circuit after using not more than 2 years. This is partly due to bad design

and low quality materials used during manufactures flyback transformer.

The question is what kind of problems can be found in a flyback transformer

and how to test and when to replace it. Here is an explanation that will help

you to identify many flyback transformer problems.

There are nine common problems can be found in a flyback transformer.

a) A shorted turned in the primary winding.

b) An open or shorted internal capacitor in secondary section.

c) Flyback Transformer becomes bulged or cracked.

d) External arcing to ground.

e) Internal arcing between windings.

f) Shorted internal high voltage diode in secondary winding.

g) Breakdown in focus / screen voltage divider causing blur display.

h) Flyback Transformer breakdown at full operating voltage (breakdown when under load).

i) Short circuit between primary and secondary winding.

Testing flyback transformer will be base on (a) and (b) since problem

(c) is visible while problem (d) and (e) can be detected by hearing the arcing

sound generated by the flyback transformer. Problem (f) can be checked with multimeter

set to the highest range measured from anode to ABL pin while (g) can be solved by

adding a new monitor blur buster (For 14' & 15' monitor only.) Problem (h) can only be

tested by substituting a known good similar Flyback Transformer. Different monitor have

different type of flyback transformer design. Problem (i) can be checked using an

ohm meter measuring between primary and secondary winding. A shorted turned or open

in secondary winding is very uncommon.

What type of symptoms will appear if there is a shorted turned in primary winding?

a) No display (No high voltage).

b) Power blink.

c) B+ voltage drop.

d) Horizontal output transistor will get very hot and later become shorted.

e) Along B+ line components will spoilt. Example:- secondary diode UF5404 and B+ FET IRF630.

f) Sometimes it will cause the power section to blow.

What type of symptoms will appear if a capacitor is open or shorted in a flyback transformer?

Capacitor shorted

a. No display (No high voltage).

b. B+ voltage drop.

c. Secondary diode (UF5404) will burned or shorted.

d. Horizontal output transistor will get shorted.

e. Power blink.

f. Sometimes power section will blow, for example: Raffles 15 inch monitor.

g. Power section shut down for example: Compaq V55, Samtron 4bi monitor.

h. Sometimes the automatic brightness limiter (ABL) circuitry components will get burned.

This circuit is usually located beside the flyback transformer. For example: LG520si

Capacitor open

a. High voltage shut down.

b. Monitor will have ‘tic - tic’ sound. Sometimes the capacitor may measure O.K. but

break down when under full operating voltage.

c. Horizontal output transistor will blow in a few hours or days after you have replaced it.

d. Sometimes it will cause intermittent "no display".

e. Distorted display i.e., the display will go in and out.

f. It will cause horizontal output transistor to become shorted and blow the power section.

How to check if a primary winding is good or bad in a Flyback Transformer?

a) By using a flyback/LOPT tester, this instrument identifies faults in primary winding by

doing a ‘ring’ test.

b) It can test the winding even with only one shorted turned.

c) This meter is handy and easy to use.

d) Just simply connect the probe to primary winding.

e) The readout is a clear ‘bar graph’ display which show you if the flyback transformer

primary winding is good or shorted.

f) The LOPT Tester also can be used to check the CRT YOKE coil, B+ coil and switch mode power transformer winding.

NOTE: Measuring the resistance winding of a flyback transformer, yoke coil, B+ coil and

SMPS winding using a multimeter can MISLEAD a technician into believing that a shorted

winding is good. This can waste his precious time and time is money.

How to diagnose if the internal capacitor is open or shorted?

By using a normal analog multimeter and a digital capacitance meter. A good capacitor have the range from 1.5 nanofarad to 3 nanofarad.*

1) First set your multimeter to X10K range.

2) Place your probe to anode and cold ground.

3) You must remove the anode cap in order to get a precise reading.

4) Cold ground means the monitor chassis ground.

5) If the needle of the multimeter shows a low ohms reading, this mean the internal capacitor

is shorted.

6) If the needle does not move at all, this doesn’t mean that the capacitor is O.K.

7) You have to confirm this by using a digital capacitance meter which you can easily get one

from local distributor.

8) If the reading from the digital capacitance meter shows 2.7nf, this mean the capacitor is

within range (O.K.).

9) And if the reading showed 0.3nf, this mean the capacitor is open.

10) You have three options if the capacitor is open or shorted.

- Install a new flyback transformer or

- Send the flyback transformer for refurbishing or

- Send the monitor back to customers after spending many hours and much effort on it.

* However certain monitors may have the value of 4.5nf, 6nf and 7.2nf.

Note: Sometimes the internal capacitor pin is connected to circuits (feedback) instead of ground.

Tv rca flyback transformer circuits usually do not have a internal capacitor in it.

If you have a flyback diagram and circuits which you can get it from the net, that would be an advantage to easily understand how to check them.

GENERAL BASIC TRANSISTOR LINE OUTPUT STAGE OPERATION:

The basic essentials of a transistor line output stage are shown in Fig. 1(a). They comprise: a line output transformer which provides the d.c. feed to the line output transistor and serves mainly to generate the high -voltage pulse from which the e.h.t. is derived, and also in practice other supplies for various sections of the receiver; the line output transistor and its parallel efficiency diode which form a bidirectional switch; a tuning capacitor which resonates with the line output transformer primary winding and the scan coils to determine the flyback time; and the scan coils, with a series capacitor which provides a d.c. block and also serves to provide slight integration of the deflection current to compensate for the scan distortion that would otherwise be present due to the use of flat screen, wide deflection angle c.r.t.s. This basic circuit is widely used in small -screen portable receivers with little elaboration - some use a pnp output transistor however, with its collector connected to chassis.

Circuit Variations:

Variations to the basic circuit commonly found include: transposition of the scan coils and the correction capacitor; connection of the line output transformer primary winding and its e.h.t. overwinding in series; connection of the deflection components to a tap on the transformer to obtain correct matching of the components and conditions in the stage; use of a boost diode which operates in identical manner to the arrangement used in valve line output stages, thereby increasing the effective supply to the stage; omission of the efficiency diode where the stage is operated from an h.t. line, the collector -base junction of the line output transistor then providing the efficiency diode action without, in doing so, producing scan distortion; addition of inductors to provide linearity and width adjustment; use of a pair of series -connected line output transistors in some large -screen colour chassis; and in colour sets the addition of line convergence circuitry which is normally connected in series between the line scan coils and chassis. These variations on the basic circuit do not alter the basic mode of operation however.

Resonance

The most important fact to appreciate about the circuit is that when the transistor and diode are cut off during the flyback period - when the beam is being rapidly returned from the right-hand side of the screen to the left-hand side the tuning capacitor together with the scan coils and the primary winding of the line output transformer form a parallel resonant circuit: the equivalent circuit is shown in Fig. 1(b). The line output transformer primary winding and the tuning capacitor as drawn in Fig. 1(a) may look like a series tuned circuit, but from the signal point of view the end of the transformer primary winding connected to the power supply is earthy, giving the equivalent arrangement shown in Fig. 1(b).

The Flyback Period:

Since the operation of the circuit depends mainly upon what happens during the line flyback period, the simplest point at which to break into the scanning cycle is at the end of the forward scan, i.e. with the

beam deflected to the right-hand side of the screen, see Fig. 2. At

this point the line output transistor is suddenly switched off by the

squarewave drive applied to its base. Prior to this action a linearly

increasing current has been flowing in the line output transformer

primary winding and the scan coils, and as a result magnetic fields have

been built up around these components. When the transistor is switched

off these fields collapse, maintaining a flow of current which rapidly

decays to zero and returns the beam to the centre of the screen. This

flow of current charges the tuning capacitor, and the voltage at A rises

to a high positive value - of the order of 1- 2k V in large -screen

sets, 200V in the case of mains/battery portable sets. The e

beam deflected to the right-hand side of the screen, see Fig. 2. At

this point the line output transistor is suddenly switched off by the

squarewave drive applied to its base. Prior to this action a linearly

increasing current has been flowing in the line output transformer

primary winding and the scan coils, and as a result magnetic fields have

been built up around these components. When the transistor is switched

off these fields collapse, maintaining a flow of current which rapidly

decays to zero and returns the beam to the centre of the screen. This

flow of current charges the tuning capacitor, and the voltage at A rises

to a high positive value - of the order of 1- 2k V in large -screen

sets, 200V in the case of mains/battery portable sets. The e nergy

in the circuit is now stored in the tuning capacitor which next

discharges, reversing the flow of current in the circuit with the result

that the beam is rapidly deflected to the left-hand side of the screen -

see Fig. 3. When the tuning capacitor has discharged, the voltage at A

has fallen to zero and the circuit energy is once more stored in the

form of magnetic fields around the inductive components. One half -cycle

of oscillation has occurred, and the flyback is complete.

nergy

in the circuit is now stored in the tuning capacitor which next

discharges, reversing the flow of current in the circuit with the result

that the beam is rapidly deflected to the left-hand side of the screen -

see Fig. 3. When the tuning capacitor has discharged, the voltage at A

has fallen to zero and the circuit energy is once more stored in the

form of magnetic fields around the inductive components. One half -cycle

of oscillation has occurred, and the flyback is complete.Energy Recovery:

First Part of Forward Scan The circuit then tries to continue the cycle of oscillation, i.e. the magnetic fields again collapse, maintaining a current flow which this time would charge the tuning capacitor negatively (upper plate). When the voltage at A reaches about -0.6V however the efficiency diode becomes forward biased and switches on. This damps the circuit, preventing further oscillation, but the magnetic fields continue to collapse and in doing so produce a linearly decaying current flow which provides the first part of the forward s

can,

the beam returning towards the centre of the screen - see Fig. 4. The

diode shorts out the tuning capacitor but the scan correction capacitor

charges during this period, its right-hand plate becoming positive with

respect to its left-hand plate, i.e. point A. Completion of Forward Scan

When the current falls to zero, the diode will switch off. Shortly

before this state of affairs is reached however the transistor is

switched on. In practice this is usually about a third of the way

through the scan. The squarewave applied to its base drives it rapidly

to saturation, clamping the vol

can,

the beam returning towards the centre of the screen - see Fig. 4. The

diode shorts out the tuning capacitor but the scan correction capacitor

charges during this period, its right-hand plate becoming positive with

respect to its left-hand plate, i.e. point A. Completion of Forward Scan

When the current falls to zero, the diode will switch off. Shortly

before this state of affairs is reached however the transistor is

switched on. In practice this is usually about a third of the way

through the scan. The squarewave applied to its base drives it rapidly

to saturation, clamping the vol tage

at point A at a small positive value - the collector emitter saturation

voltage of the transistor. Current now flows via the transistor and the

primary winding of the line output transformer, the scan correction

capacitor discharges, and the resultant flow of current in the line scan

coils drives the beam to the right-hand side of the screen see Fig. 5.

tage

at point A at a small positive value - the collector emitter saturation

voltage of the transistor. Current now flows via the transistor and the

primary winding of the line output transformer, the scan correction

capacitor discharges, and the resultant flow of current in the line scan

coils drives the beam to the right-hand side of the screen see Fig. 5.Efficiency:

The transistor is then cut off again, to give the flyback, and the cycle of events recurs. The efficiency of the circuit is high since there is negligible resistance present. Energy is fed into the circuit in the form of the magnetic fields that build up when the output transistor is switched on. This action connects the line output transformer primary winding across the supply, and as a result a linearly increasing current flows through it. Since the width is

dependent on the supply voltage, this must be stabilised.

Harmonic Tuning:

There is another oscillatory action in the circuit during the flyback period. The considerable leakage inductance between the primary and the e.h.t. windings of the line output transformer, and the appreciable self -capacitance present, form a tuned circuit which is shocked into oscillation by the flyback pulse. Unless this oscillation is controlled, it will continue into and modulate the scan. The technique used to overcome this effect is to tune the leakage inductance and the associated capacitance to an odd harmonic of the line flyback oscillation frequency. By doing this the oscillatory actions present at the beginning of the scan cancel. Either third or fifth harmonic tuning is used. Third harmonic tuning also has the effect of increasing the amplitude of the e.h.t. pulse, and is generally used where a half -wave e.h.t. rectifier is employed. Fifth harmonic tuning results in a flat-topped e.h.t. pulse, giving improved e.h.t. regulation, and is generally used where an e.h.t. tripler is employed to produce the e.h.t. The tuning is mainly built into the line output transformer, though an external variable inductance is commonly found in colour chassis so that the tuning can be adjusted. With a following post I will go into the subject of modern TV line timebases in greater detail with other models and technology shown here at Obsolete Technology Tellye !

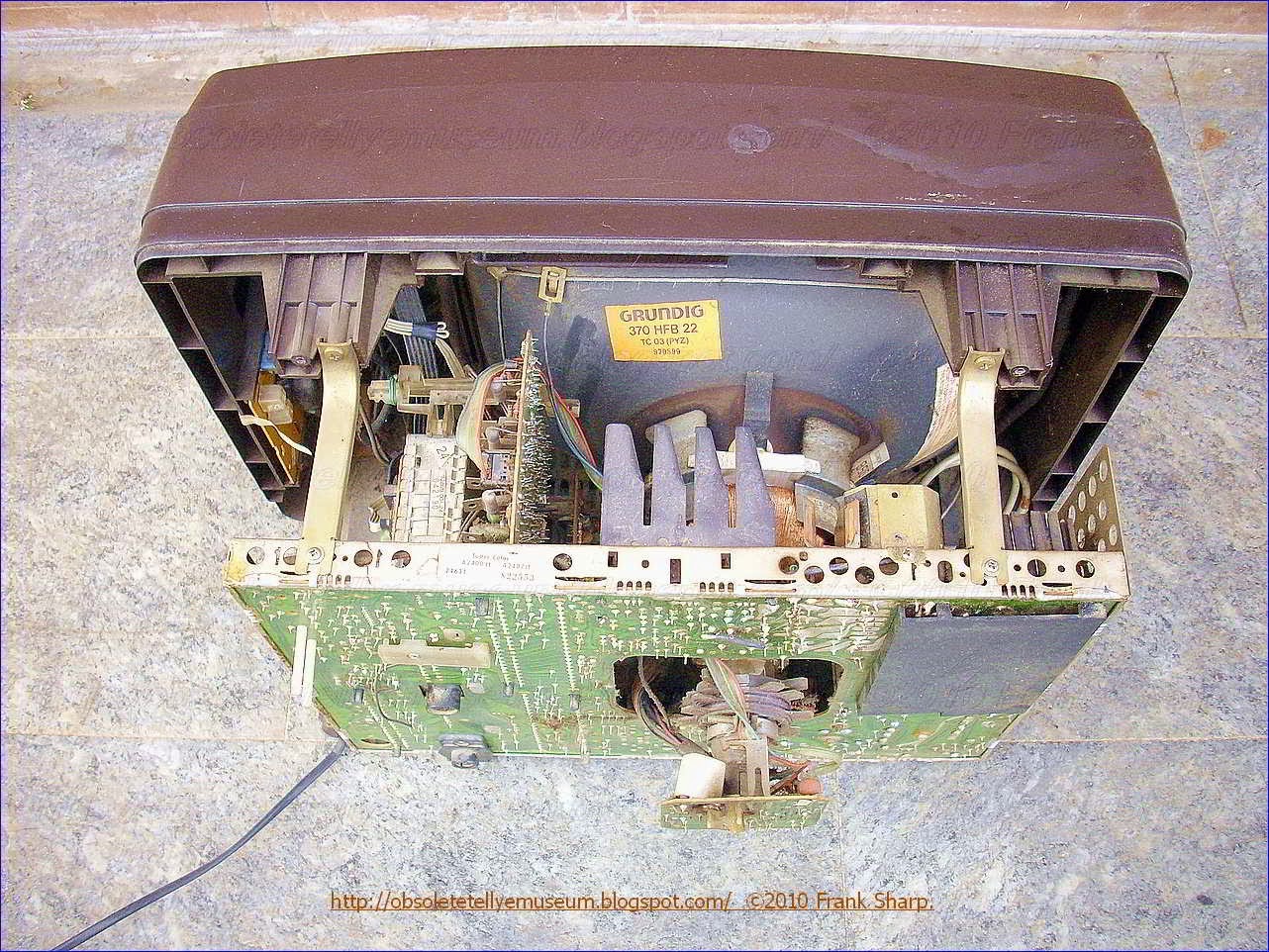

GRUNDIG SUPER COLOR A2402 SERIE F3015 CHASSIS CUC91 Simplified horizontal / line deflection circuit.

GRUNDIG SUPER COLOR A2402 SERIE F3015 CHASSIS CUC91 Simplified horizontal / line deflection circuit.

-------------------------------------------------------------------------------------------

A flyback transformer (FBT), also called a line output transformer (LOPT), is a special transformer, which is used for conversion of energy (current and voltage) in electronic circuits. It was initially designed to generate high current sawtooth signals at a relatively high frequency. In modern applications is used extensively in switched-mode power supplies for both low (3V) and high voltage (over 10 kV) supplies.

Flyback Transformer

It was invented as a means to control the horizontal movement of the electron beam in a cathode ray tube (CRT). Unlike conventional transformers, a flyback transformer is not fed with a signal of the same waveshape

as the intended output current. A convenient side effect of such a transformer is the considerable energy that is available in its magnetic circuit. This can be exploited using extra windings that can be used to provide power to operate other parts of the equipment. In particular, very high voltages are easily obtained using relatively few turns of winding which, once rectified, can provide the very high accelerating voltage for a CRT. Many more recent applications of such a transformer dispense with the need to produce high currents and just use the device as a relatively efficient means of producing a wide range of lower voltages using a transformer much smaller than a conventional mains transformer would be.

This GRUNDIG CHASSIS Series was featuring a Simplified BU208A based horizontal deflection section replacing all Thyristor horizontal timebase based circuits.

A horizontal deflection circuit makes a sawtooth

A horizontal deflection circuit makes a sawtoothcurrent flow through a deflection coil. The current

will have equal amounts of positive and negative

current. The horizontal switch transistor conducts

for the right hand side of the picture. The damper

diode conducts for the left side of the picture.

Current only flows through the fly back capacitor

during retrace time.

For time 1 the transistor is turned on. Current

ramps up in the yoke. The beam is moved from the

center of the picture to the right edge. Energy is

stored on the inductance of the yoke.

E=I2L/2

For time 2 the transistor is turned off. Energy