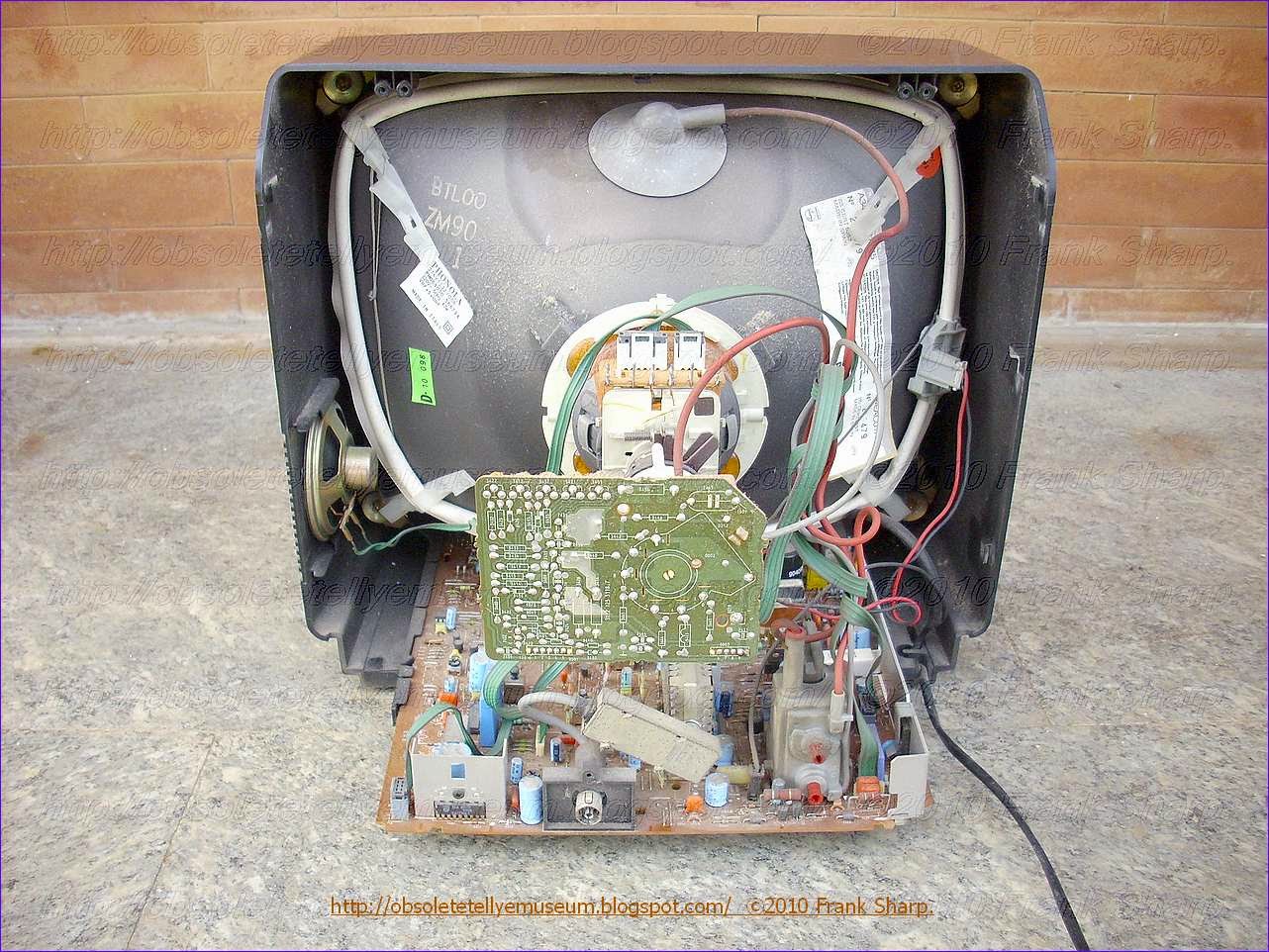

Micom - TMP47C434N-3415

Memory - 24C02

SMPS - BUK446

SAW - OFW G1961

Secam - TDA3592A

PAL - TDA3565

Video - TDA8305

Vertical - TDA3653B

Sound - TDA7052

Tuner - 3139 147 10731 UV917E/PHONO SV20

Band - LA7910

Tube - Philips

FBT - 37622TY (HR7527)

HOT - 2SC3795 (2SC3353, BUT11AF, 2SC4518)

RGB Amp. - Transistor 3 x BF422

Remote unit: - RC-8201, RC-8211

IC remote - PCA8521F.

PHILIPS TDA8305A SMALL SIGNAL COMBINATION IC FOR COLOUR TV

GENERAL DESCRIPTION:

The TDA8305A is TV sub-system circuit, for colour television receivers with the following features.

Vision IF amplifier with synchronous demodulator

Automatic gain control (AGC) detector suitable for negative modulation

AGC tuner

Automatic frequency control (AFC) circuit with sample-and-hold

Video preamplifier

Sound lF amplifier and demodulator

DC volume control or separate supply for starting the horizontal oscillator

Audio preamplifier

Horizontal synchronization circuit with two control loops

Vertical synchronization (divider system) and sawtooth generation with automatic amplitude

adjustment for 50 and 60 Hz

Transmitter identification (mute)

Generation of sandcastle pulse

FUNCTIONAL DESCRIPTION

Vision IF amplifier, demodulator and video amplifier

The IF amplifier of the TDA8305A has three AC~coupled stages, each stage having a control range

that exceeds 20 dB. AC-coupling means that the DC-feedback circuitry of the ampiifier (present in

the TDA4505) can be omitted, resulting in a saving of one pin. An additional advantage is the

symmetry of the amplifier which results in a less critical application.

In the TDA8305A the regenerated carrier signal islimited by a logarithmic limiter circuit before it is

passed on to a passive synchronous demodulator. The limiter has a very low differential phase shift

which results in good differential gain and phase figures.

The TDA8305A's video amplifier has a higher bandwidth and better linearity compared with that of

the TDA4505. A noise clamp is included in the video amplifier that limits the interference pulses

to a level just below the top sync. This circuit is more effective than the noise in

verter used in the

verter used in theTDA4505 and results in an improved picture stability, with respect to interference.

AFC circuit

In the TDA4505 and TDA8305A, the reference signal for the AFC circuit is obtained from the

demodulator tuned circuit which means only one tuned circuit and adjustment are needed. The

disadvantage with this method is that the frequency spectrum fed to the detector is determined by the

SAW filter characteristic. This spectrum is asymmetrical with respect to the picture carrier so that the

AFC output voltage is dependent on the video signal. This was the main problem found with the

TDA4505's AFC circuit.

To remove this problem the TDA8305A is equipped with a sample-and-hold circuit which samples

during the sync level of the signal. This means that only the carrier signal is available to the AFC

and it will not be affected by the video information. The additional pin required for this circuit is

provided by the pin that became available when the DC feedback circuit was removed from the IF

amplifier (see previous section).

Weak input signals will cause the drive signal of the AFC to contain a lot of noise. This noise signal

has an asymmetrical frequency spectrum that causes an offset in the AFC output voltage, this

offset can be reduced by applying a notch to the demodulator circuit. The sample-and-hold circuit

is followed by a high output impedance amplifier, therefore the AFC's control steepness is

dependent on the load impedance.

AGC circuit

The TDA8305A's AGC detector differs from that of the TDA4505 in that it doesn’t need the charge

resistor but has an internal current source. Also the circuitry between the detector capacitor and the

control stages has been changed to improve the signal-to-noise ratio of the video output signal

(no dips in the S/N ratio depending on the input signal amplitude). The point of tuner take-over

is preset by the voltage level at pin 1.

Sound circuit and horizontal oscillator starting function:

The input to the sound IF amplifier is by means of a bandpass filter coupling from the video output

(pin 17). The sound is demodulated and passed via a volume control stage to the audio

output amplifier. Volume control is obtained by connecting a potentiometer (10 k9.) between pin 11

and ground, or by supplying pin 11 with a variable voitage. Sound output is suppressed by an

internal mute signal when no TV signal is identified.

Improvement of sound quality was one of the main reasons for redesigning the TDA4505. To obtain

a better idea of the performance of the various circuits of the TDA4505 the following measurements

were carried out:

Weak signal performance when a TBA120 is driven with an intercarrier signal obtained from the

vision IF circuit of the TDA4505 (the sound IF of the latter was not used)

The same measurement for the sound IF circuit of the TDA4505 driven from another TDA4505

(again without using the sound IF circuit)

The same measurement as in the first case but with the sound IF of the TDA4505 connected

normally

From the results of these measurements it was established that the sound problem was caused by an

interaction between vision IF and sound circuits. The improved sound quality of the TDA8305A as

compared to the TDA4505 was achieved by:

A very symmetrical vision-IF amplifier which is less sensitive to radiation from the sound IF

amplifier

0 A change to the internal ground and supply connections of the IC to reduce coupling between

both circuits

DC volume control/Horizontal oscillator start

Horizontal oscillator; the operation depending on the application. During switchon if no current is

supplied to pin 11 this pin will act as a volume control. When a current of 9.0 mA is supplied to

pin 11 the volume control is set to a fixed output signal and the device will generate drive pulses

for the horizontal deflection. The main supply can then be derived from the horizontal deflection

circuit.

Horizontal synchronization

The video input signal (positive video) is connected to pin 25. The horizontal synchronization has

two control loops that generate a sandcastle pulse. Using the oscillator sawtooth facilitates

accurate timing of the burst key pulse. Therefore, the phase of this sawtooth must have a fixed

relationship to the sync pulse, which is achieved by use of the second control loop.

The TDA8305A's horizontal synchronization circuit differs from that of the TDA4505 in that:

The horizontal oscil|ator's retrace occurs during the horizontal retrace and not during the scan

period. This means that with weak input signals no interference will be visible on the screen.

It also prevents video crosstalk from disturbing the picture phase

The reference signal for the horizontal phase detector is nearer to being symmetrica

l and is

l and isindependent of the supply voltage and temperature. As a consequence the frequency shift of

the horizontal oscillator during noise is reduced

The current ratio of the phase detector for strong and weak signals is increased to obtain better

behaviour during both VCR-playback and weak signal reception. The switching level is independent

of supply voltage and temperature.

Horizontal phase detector

The circuit has the following operating conditions.

(a) Strong input signal, synchronized or non-synchronized.

(The strong/weak signal condition is obtained from the AGC circuit; the in-sync/out«of—sync

from the coincidence detector). In this condition the time constant is optimum for VCR-playback

i.e. fast time constant during the vertical retrace (to be able to correct VCR head-errors) and

such, that during scan, fluctuations of the sync are corrected. The phase detector is not gated.

lb) Weak signal — synchronized

In this condition the time constant is increased compared to condition (a). Also the phase

detector is gated when the oscillator is synchronized. This ensures a stable display which is not

disturbed by noise in the video signal.

(c) Weak signal - non-synchronized.

in this condition the time constant during scan and vertical retrace are the same as during scan

in condition (3).

Vertical synchronization

The TDA8305A's vertical circuit differs from that ofthe TDA4505 in that it has:

Improved interlacing ~ the timing of the internal pulses is now close to a 50/50 ratio. This timing

is independent of supply voltage and temperature

The temperature drift of the vertical amplitude has been reduced

Reduction of noise in the vertical output signal so that modulation of the line distance will no

longer be visible on large screen sets.

When out-of-sync is detected by the horizontal circuit the divider is switched to 625 lines.

This results in a stable amplitude when no input signal is available. In the TDA4505 the divider

remains in the wide window during this condition which means interference may affect stability.

Vertical sync pulse

The vertical sync pulse integrator will not be disturbed when the vertical sync pulses have a width

of 10 ,us with a separation of 22 ps. These types of vertical sync pulses are sometimes generated by

video tapes with anti-copy guard.

Vertical divider system

The TDA8305A embodies a synchronized divider system for generating the vertical sawtooth at pin 2.

The divider system has an internal frequency doubling circuit, which allows the horizontal oscillator to

operate at its normal line frequency. One line period equals 2 clock pulses.

Use of the divider system avoids the requirement for vertical frequency adjustment. The divider has

a discriminator window for automatic switching from 60 Hz to 50 Hz mode. When the trigger pulse

comes before line 576 the 60 Hz mode is selected, otherwise the 50 Hz mode is selected.

The divider system operates with 2 different divider reset windows for maximum interference}

disturbance protection.

The windows are activated via an up/down counter.

The counter increases its counter value by 1 each time the separated vertical sync pulse is within the

search window. When not within the search window this value is decreased by 1.

The operating modes of the divider system are as follows:

Mode A

Large search window (divider ratio between 488 and 722)

This mode is valid for the following conditions:

Divider is looking for a new transmitter

Divider ratio found - not within the narrow window limits

Up/down counter value of the divider system operating in the narrow window mode drops below

count 10

Mode 8

Narrow window (divider ratio between 522 to 528, 60 Hz; or 622 to 628, 50 Hz)

The divider system switches over to this mode when the up/down counter has reached its maximum

value of 15 approved vertical sync pulses. when the divider operates in this mode and a vertical sync

pulse is missing within the window, the divider is reset at the end of the window and the counter value

is decreased by 1. At a counter value below 10 the divider system switches over to the large window

mode.

The divider system also generates an anti-topflutter pulse which inhibits the phase 1 detector during

the vertical sync pulse. The pulse width is dependent on the divider mode. In Mode A the start is

generated by reset of the divider

in Mode B the anti-topflutter pulse starts at the beginning of the first equalizing pulse.

The anti-topflutter pulse ends at count 10 for the 50 Hz mode and count 12 for the 60 Hz mode.

The vertical blanking pulse is also generated via the divider system. The start is by reset of the divider

while the blanking pulse width is 34 (17 lines) for the 60 Hz mode and at count 42 (21 lines) for

the 50 Hz mode.

The vertical blanking pulse at the sandcastle output (pin 27) is generated by adding the anti-topflutter

pulse to the blanking pulse. Thus the vertical blanking pulse starts at the beginning of the first

equalizing pulse when the divider operates in Mode B. The length of the vertical blanking in this

condition is 21 lines in the 60 Hz mode and 25 lines in the 50 Hz mode.

Application when external video signals require synchronization

The input to the sync separator is externally available via pin 25. For normal application the video

output signal at pin 17 is AC coupled to this input as shown in Fig.11. It is possible to interrupt this

connection and drive the sync separator from other sources such as:

A teletext decoder in serial mode

An external video signal via a peritelevision connector

When a teletext decoder is applied the IF amplifier and synchronization circuit are operating in the

same phase which means that various connections between the two sections li.e. AGC gating) can

remain active. When external signals are applied to the sync separator the connections between the

two parts must be interrupted. This can be achieved by connecting pin 22 to ground, which results

in the following conditions:

AGC detector is not gated

AFC circuit is active

Mute circuit not active — sound channel remains switched on

Phase detector 1 has an optimal time constant for external video sources and is not gated.

X-ray protection

By forcing pin 1 below 1 V the horizontal output changes to a high resistance. The protection can be

released by switching off the mains.

The AFC control voltage is obtained by multiplying the IF output signal (which is also used to

drive the synchronous demodulator) with a reference carrier. This reference carrier is obtained

from the demodulator tuned circuit via a 90 degree phase shift network. The IF output signal

has an asymmetrical frequency spectrum with respect to the carrier frequency. To avoid

problems due to this asymmetrical signal the AFC circuit is followed by a sample-and-hold

circuit which samples during the sync level. As a result the AFC output voltage contains no

video information. The specified control steepness is without using an external load resistor.

The control steepness decreases when the AFC output is loaded with two resistors between

the voltage supply and ground.

At very weak input signals the drive signal for the AFC circuit will have a high noise content.

This noise input has an asymmetrical frequency spectrum which will cause an offset of the

AFC output voltage. To avoid problems due to this effect a notch filter can be built in to the

demodulator tuned circuit. The characteristics given for weak input signals are measured without

a notch circuit, with a SAW filter connected in front of the IC (input signal such that the input

signal of the IC is 150 uV (RMS value).

The minimum value is obtained with a 1.8 k9. series resistor connected between pin 17 and

pin 25. The slicing level can be varied by changing the value of this resistor (a higher resistance

results in a larger value of the minimum sync pulse amplitude). The slicing level is independent

of the video information.

Frequency control is obtained by supplying a correction current to the oscillator RC-network.

This is achieved via a resistor connected between the phase 1 detector output and the oscillator

network. The oscillator can be adjusted to the correct frequency by:

short-circuit the sync separator bias network (pin 25) to the voltage supply.

To avoid the necessity of a VCR switch, the time constant of the phase detector at strong input

signals is sufficiently short to obtain a stable picture during VCFl playback. During the vertical

retrace period the time constant is even shorter so that VCR head errors are compensated for at

the beginning of the scan. During weak signal conditions (information derived from the AGC

circuit) the time constant is increased to obtain a good noise immunity.

This figure is valid for an external load impedance of 82 kfl connected between pin 28 and

the shift adjustment potentiometer.

The horizontal flyback input and the sandcastle output have been combined on pin 27. The

flyback pulse is clamped to a level of 4.5 V. The minimum current to drive the second control

loop is 0.1 mA.

The functions in—sync/out-of-sync and transmitter identification have been combined on pin 22.

The capacitor is charged during the sync pulse and discharged during the time difference

between gating and sync pulse.

The vertical scan is synchronized by means of a divider system, therefore no adjustment is

required for the ramp generator. The divider detects whether the incoming signal has a vertical

frequency of 50 or 60 Hz and corrects the vertical amplitude.

To avoid screenburn due to a collapse of the vertical deflection, a continuous blanking level is

inserted into the sandcastle pulse when the feedback voltage of the vertical deflection is not

within the specified limits.

PHILIPS TDA3565 PAL decoder:

GENERAL DESCRIPTION

The TDA3565 PAL decoder contains all the functions required for PAL signal decoding and colour matrixing and is contained within an 18-pin package. The oscillator, a.c.c. detector and burst phase detector each have single-pin outputs and the coupling capacitor for the luminance input at pin 8 doubles as a storage capacitor for the black level clamping circuit. Black level clamping of the three colour channels is performed using feedback proportional to the red channel black level. This feedback (variable with the brightness control) controls the input level of the luminance amplifier and therefore the clamping levels of all three colour signal outputs.

PHILIPS TDA3653B TDA3653C Vertical deflection and guard circuit (90˚)

GENERAL

DESCRIPTION

DESCRIPTIONThe TDA3653B/C is a vertical deflection output circuit for drive of various deflection systems with currents up to 1.5 A peak-to-peak.

Features

• Driver

• Output stage

• Thermal protection and output stage protection

• Flyback generator

• Voltage stabilizer

• Guard circuit

FUNCTIONAL DESCRIPTION

Output stage and protection circuit

Pin 5 is the output pin. The supply for the output stage is fed to pin 6 and the output stage ground is connected to pin 4.

The output transistors of the class-B output stage can each deliver 0.75 A maximum.

The maximum voltage for pin 5 and 6 is 60 V.

The output power transistors are protected such that their operation remains within the SOAR area. This is achieved by

the co-operation of the thermal protection circuit, the current-voltage detector, the short-circuit protection and the special

measures in the internal circuit layout.

Driver and switching circuit Pin 1 is the input for the driver of the output stage. The signal at pin 1 is also applied via external resistors to pin 3 which is the input of a switching circuit. When the flyback starts, this switching circuit rapidly turns off the lower output stage and so limits the turn-off dissipation. It also allows a quick start of the flyback generator.

External connection of pin 1 to pin 3 allows for applications in which the pins are driven separately.

Flyback generator

During scan the capacitor connected between pins 6 and 8 is charged to a level which is dependent on the value of the resistor at pin 8

When the flyback starts and the voltage at the output pin (pin 5) exceeds the supply voltage, the flyback generator is activated.

The supply voltage is then connected in series, via pin 8, with the voltage across the capacitor during the flyback period.

This implies that during scan the supply voltage can be reduced to the required scan voltage plus saturation voltage of the output transistors.

The amplitude of the flyback voltage can be chosen by changing the value of the external resistor at pin 8.

It should be noted that the application is chosen such that the lowest voltage at pin 8 is > 2.5 V, during normal operation.

Guard circuit

When there is no deflection current and the flyback generator is not activated, the voltage at pin 8 reduces to less than 1.8 V. The guard circuit will then produce a DC voltage at pin 7, which can be used to blank the picture tube and thus prevent screen damage.

Voltage stabilizer

The internal voltage stabilizer provides a stabilized supply of 6 V to drive the output stage, which prevents the drive current of the output stage being affected by supply voltage variations.

PHONOLA (PHILIPS) 37KV1232 CHASSIS GR1AX Picture display apparatus with a cathode ray tube and a self-oscillating switched-mode power supply:

PHILIPS developed a small effective minimalistic power supply:

A picture display apparatus includes a

1. A picture display apparatus comprising:

a

DC voltage source for supplying a DC voltage between a first terminal

and a second terminal, said DC voltage source rectifying a line voltage;

a cathode ray tube;

a standby device which remains active in a standby state of the apparatus; and

a

self-oscillating switched-mode power supply connected to the first and

second terminals of the DC voltage source, wherein said self-oscillating

switched-mode power supply comprises:

a switch having an input coupled to the first terminal, said switch being a MOS-type field-effect transistor;

a ballast inductance having a first end coupled to an output of said switch;

an

output stage of a line-scanning circuit having a first terminal coupled

to a second end of the ballast inductance, and a second terminal

coupled to the second terminal of the DC voltage source, said output

stage of the line-scanning circuit being supplied by the

self-oscillating switched-mode power supply, and, in turn, generating

power supply voltages for different elements of the picture display

apparatus;

a storage capacitance coupled between the second end

of the ballest inductance and the second terminal of the DC voltage

source in parallel to the output stage of the line-scanning circuit; and

an

arrangement for switching ON and OFF the switch, the standby state

being obtained by de-activating the line output stage while the

switched-mode power supply is always active and supplies power to the

standby device;

characterized in that said arrangement for switching ON and OFF the switch comprises:

a

winding magnetically coupled to the ballast inductance, said winding

having a first end connected to a connection point between said switch

and the ballast inductance so as to generate, at a second end of the

winding, a control voltage which, with respect to the connection point,

is in phase opposition with a voltage generated in the ballast

inductance;

a first capacitor coupling said second end of the

winding to a gate of the MOS-type field-effect transistor for applying

said control voltage to the gate for maintaining the switch conductive

during each period of conductance, and for maintaining the switch

non-conductive during each period of non-conductance;

a second

capacitor arranged as a shunt across the drain-source path of the

MOS-type field-effect transistor, for generating a free-oscillation with

the inductance of the windings, then rendering said switch conductive

after a given delay of non-conductance; and

means for measuring a

current through said switch, and for turning the switch OFF when the

measured current exceed a predetermined value, at the end of each period

of conductance.

2. A picture display apparatus as claimed in claim 1, characterized in that the means for measuring th

3. A picture

display apparatus as claimed in claim 2, characterized in that the

shorting circuit comprises a blocking transistor having a main current

path arranged in series with a resistor between the gate of the MOS-type

field-effect transistor and the second terminal of the DC source, and a

base-emitter path coupled to the current-measuring resistor.

4. A

picture display apparatus as claimed in claim 3, characterized in that

said picture display apparatus further comprises a control circuit

connected between a terminal carrying the power supply voltage for the

line output stage, and a base of the blocking transistor.

5. A

picture display apparatus as claimed in claim 1, characterized in that

the standby circuit is fed from a rectifier arrangement connected to an

additional winding which is magnetically coupled to the ballast

inductance.

6. A picture display apparatus as claimed in claim 3,

characterized in that said arrangement for switching ON and OFF the

switch comprises means for turning the switch ON, said turning ON means

comprising a resistor in series with said first capacitor.

Description:

BACKGROUND OF THE INVENTION

1. Field of the Invention

The

invention relates to a picture display apparatus with a cathode ray

tube, comprising a standby device which remains active in a standby

state of the apparatus, and a self-oscillating switched-mode power

supply (SMPS) comprising, in cascade between two terminals of a source

of direct current obtained by line voltage rectification, a switch, a

ballast inductance, and the supply current path of a line output stage

which generates power supply voltages for different elements of the

device to be insulated from the line voltage, the standby state being

obtained by stopping the line scan while the SMPS is always active and

feeds the standby device, the SMPS switch, which has successive periods

of conductance and non-conductance, being rendered non-conducting at the

end of each period of conductance by means of a blocking arrangement

which measures the current in the switch and controls the operation of

rendering said switch non-conducting when the measured current exceeds a

predetermined value.

The invention is applicable, inter alia, in the field of television and monitors.

2. Description of the Related Art

An

SMPS is known from U.S. Pat. No. 4,788,591. It comprises a blocking

arrangement which measures the current in the switch and controls the

operation of rendering this switch non-conducting when the measured

current exceeds a predetermined value. The assembly controlling the

successive periods of conductance and non-conductance is, however,

relatively complex.

SUMMARY OF THE INVENTION

It is an

object of the invention to simplify the control in such a way that a

control at both low cost and great reliability is obtained.

To

this end, the switch, being a MOS-type field-effect transistor, is

turned on at the start of each period of conductance by means of a

winding which is magnetically coupled to the ballast inductance, this

winding having one end connected to a connection point between the

switch and the ballast inductance so as to generate, at its other end, a

control voltage which, with respect to the connection point, is in

phase opposition with the voltage generated in the ballast inductance,

said control voltage being transmitted to the gate of the field effect

transistor via a first capacitor, while a second capacitor is arranged

as a shunt across the drain-source path of the field effect transistor.

The

terminal of the DC source connected to the field-effect transistor

being referred to as first terminal, the blocking arrangement is

preferably connected between the gate of the MOS transistor and the

second terminal of the DC source, and comprises a current-measuring

resistor which is inserted between the line output stage and the second

terminal, the blocking arrangement being advantageously constituted

essentially by a blocking transistor having its main current path

between the gate of the MOS transistor and the second terminal of the DC

source, and its base-emitter path coupled to the current-measuring

resistor.

The blocking arrangement and the means for rendering the switch conducting thus cooperate in a simple manner.

The

apparatus advantageously comprises a control circuit connected between a

terminal which holds the power supply voltage of the line output stage

and the base of the blocking transistor.

The blocking arrangement and the control circuit thus cooperate in a simple manner.

The

standby circuit is advantageously fed from a rectifier arrangement

connected to an additional winding which is magnetically coupled to the

ballast inductance.

This ensures power supply of the standby circuit during the standby periods.

These

and other aspects of the invention will be apparent from and elucidated

with reference to the embodiments described hereinafter.

BRIEF DESCRIPTION OF THE DRAWINGS

In the drawings:

FIG.

1 shows diagrammatically, a picture display apparatus with a cathode

ray tube and a line output stage, a standby device and a

self-oscillating switched-mode power supply (SMPS);

FIG. 2 shows diagrammatically, a self-oscillating SMPS; and

FIG. 3 shows curves to illustrate the operation of the SMPS and,

FIG. 4 shows diagrammatically, a control module suitable for controlling the SMPS.

DESCRIPTION OF THE PREFERRED EMBODIMENTS

The

invention will be described with reference to a television set, but it

is also applicable to any other picture display apparatus, for example, a

monitor.

The

invention will be described with reference to a television set, but it

is also applicable to any other picture display apparatus, for example, a

monitor.

The television set, which is shown in a diagram in FIG.

1, comprises a tuner 22 for receiving a signal, for example, from an

antenna 37 and for transposing the frequency of the apparatus to

intermediate frequencies intended for a subsequent IF video amplifier 23

and an IF audio amplifier 24. The IF audio amplifier 24 is followed by a

demodulator 29 which supplies the audio signals in the baseband to an

audio output amplifier 27 feeding a loudspeaker 33. The IF video

amplifier 23 is followed by a unit video processor/sync. separator 25

which supplies a video signal in the baseband to a video amplifier 26

supplying the signals ad hoc to the electrodes of a cathode ray tube 32.

The video processor/sync. separator unit 25 also extracts, from the

signal, synchronizing signals which are applied to a line scanning

circuit 36 and a field scanning circuit 28. The field scanning circuit

28 supplies a current in a field deflection coil 30. The line scanning

circuit 36 comprises an output stage 35 which supplies a current in a

line deflection coil 34 and generates a voltage, referred to as

"extra-high tension" (EHT) of approximately 25 kV for supplying power to

the screen of the display tube via a connection 31. The line output

stage 35 is fed via a connection 49 by a self-oscillating switched-mode

power supply circuit 38 which itself is DC-fed by a DC soure 39 of known

type which can be connected to the line voltage by means of a current

terminal 43 and is essentially constituted by a rectifier assembly and a

storage capacitor. The other circuits 22-29, which must be insulated

from the line voltage are fed in known mariner from the line output

stage 35 through connections which, for the purpose of simplifying the

Figure, are not shown. The switched-mode power supply 38 is not

synchronized with the line frequency. A standby device 48, which remains

active in a standby state of the apparatus, is directly fed by the SMPS

38. The standby state is obtained by stopping the line output stage 35,

which suppresses the supply of the circuits 22-29 from the line output

stage 35, while the SMPS 38 is always active and feeds the standby

device 48.

The SMPS of FIG. 2 corresponds to the SMPS 38 of FIG.

1. The DC source 39 in FIG. 1 provides a voltage Vs of about 300 V,

obtained by a rectifier bridge if the mains is 220 V, or by a doubler in

the case of 110 V. This voltage is applied between a first terminal 20

and a second terminal 21, with its positive pole, for example, at the

terminal 20. The polarity types of the semiconductors mentioned

hereinafter are derived from this polarity.

The power supply

comprises, in cascade from the terminal 20, a switch consisting of an

N-channel, enhancement-mode MOS field-effect transistor 1, and a ballast

inductance 5 connected to a power supply input of the line output stage

35 in which the power supply current path ends at the terminal 21. The

line output stage 35 is shunted by a storage capacitor 4 and the

assembly consisting of the line output stage 35 in cascade with the

winding 5 is shunted by a recovery diode 2. The operation of the

elements 1, 5, 4, 2, 35 mentioned above is well known. The power supply

voltage supplied to the line output stage 35 is, for example, 100 V.

The

switch for the SMPS, namely the transistor 1, has successive periods of

conductance and non-conductance. The operation of rendering it

non-conducting is controlled by a blocking arrangement which measures

the current and controls the blocking of transistor 1 when the measured

current exceeds a predetermined value. This arrangement is essentially

constituted by transistor 10 of the NPN type, referred to as blocking

transistor, having its main current path between the gate of MOS

transistor 1 and the second terminal 21 of the DC source, in series with

a resistor 13, and having its base-emitter path connected to a current

measuring resistor 8 which is inserted between the line output stage 35

and the second terminal 21. The current which flows through the resistor

8 is substantially the same as that which flows through the transistor

1. The voltage generated by the current in the resistor 8 is transmitted

to the base 53 of the transistor 10 via a resistor 7.

One end of

a winding 6, which is magnetically coupled to the ballast inductance 5,

is connected to the point 50 between a transistor 1 and the inductance

5. This winding is coiled in such a sense that it generates, between its

other end 51 and the point 50, a control voltage which is in phase

opposition with the voltage generated in the ballast inductance, i.e.,

with the voltage between the point 49 and the point 50. The other end 51

is connected to the gate of the field-effect transistor via a first

capacitor 12 in series with a resistor 11. A second capacitor 42 is

arranged as a shunt onto the drain-source path of the field-effect

transistor.

The standby circuit 48 shown in FIG. 1 is supplied by

a terminal 44 of the SMPS from a rectifier arrangement consisting of a

diode 45 and a storage capacitor 47 connected to an additional winding

46 which is magnetically coupled to the ballast inductance 5.

The

operation of this assembly will be explained with reference to the

characteristic curves in FIG. 3 and the diagram in FIG. 2. Let it be

assumed that the transistor 1 is turned on. The voltage at the point 50

in FIG. 2, indicated by the reference numeral 16 in FIG. 3, is 300 V: if

neglecting the voltage at the terminals of the transistor 1, the

terminal 49 is at 100-300=-200 V with respect to the terminal 50. As the

windings 5 and 6 operate as a transformer, a positive voltage is

generated at the point 51 with respect to the point 50. This voltage,

transmitted to the gate of transistor 1 by the capacitor 12 and the

resistor 11, maintains the transistor 1 conducting. The voltage at the

terminals of the inductance 5, between the point 50 and the point 49,

being fixed, the current in this inductance 5, indicated by the

reference numeral 19, and also flowing in the transistor 1 and in the

resistor 8, has an approximately linear growth. Let it be assumed, for

example, that the resistor 8 has a value of 0.56 ohm. When the current

reaches approximately 1.8 amperes, it will develop a voltage of 1 Volt

which, via the resistor 7, renders the transistor 10 conducting. The

lower end of the resistor 13 then decreases to almost zero volt. The

voltage applied to the gate of transistor 1 is that of the left plate of

the capacitor 12 but is decreased by the divider bridge effect of the

resistors 11 and 13. The transistor 1 becomes non-conducting. At this

instant, the current in the inductance 5, which cannot disappear in one

go, ends via the recovery diode 2 which becomes conducting. The voltage

at the point 50 therefore decreases to approximately -0.8 V. Thus, there

is approximately 101 V between the terminal 49 and the terminal 50. As

the windings 5 and 6 always operate as a transformer, a negative voltage

is generated at the point 51 with respect to the point 50. This

voltage, transmitted to the gate of transistor 1, confirms and

reinforces the blocking operation. As the current no longer flows in the

resistor 8, the transistor 10 becomes non-conducting again and the

voltage again builds up at its collector, but as a consequence of the

voltage applied by the winding 6, this does not render the transistor 1

conducting. From this instant, the current, indicated by the reference

numeral 14, decreases in an approximately linear manner. When it has

become zero, the capacitor 42 will start resonating with the inductance

5, which triggers a free oscillation; the reference numeral 15 shows

what this oscillation would look like if it could last. However, when

the voltage at the point 50 exceeds 100 V, i.e., when it becomes higher

than the voltage at the point 49, a positive voltage will again be

induced at the point 51, this voltage being transmitted to the gate of

transistor 1 and rendering this transistor conducting. The oscillation

15 is then stopped and the voltage at the point 50 builds up to 300 V,

as indicated at 18.

A

control circuit 41 is connected between the terminal 49, having the

power supply voltage of the line output stage, and the connection to the

base 53 of the blocking transistor 10. This circuit, which is of a

known type and is based on the comparison between a voltage of a zener

diode and a fraction of the power supply voltage, is illustrated in FIG.

4. It comprises, between the terminal 49 and ground, two cascade

arrangements: that of a zener diode 58 and a resistor 57, and that of a

controllable resistor 55 and a resistor 56. The junction point of the

first-mentioned cascade arrangement is connected to the emitter of a

transistor 54 of the PNP type, and the junction point of the secondly

mentioned cascade arrangement is connected to the base of this

transistor, whose collector is connected via a resistor 59 to the base

53 of the transistor 10 in FIG. 2. With the zener diode being for

example, a 5 V model, the emitter voltage of transistor 54 is of about

95 V which is higher than the base voltage of the transistor 10 in FIG.

2. The transistor 54 thus adds a DC current in the resistor 7, this DC

current shifting the triggering threshold of the transistor 10.

In a satisfactory embodiment, the power supply comprises the following essential components:

transistor 1=BUK444, transistor 10=BF487, transistor 54=BF423,

diode 2=BYD34, zener diode 58=BZX79-C5V6

capacitor 42=330 pF, capacitor 12=33 nF,

resistor

11=1.8 kΩ, resistor 13=6.8 kΩ, resistor 8=0.56 Ω, resistor 7=330 Ω,

resistor 57=33 kΩ, resistor 55=10 kΩ, resistor 56=100 kΩ, resistor 59=10

kΩ.

The line output stage 35 may be de-activated by known means

which does not form part of the invention, in such a way that the module

35 no longer supplies voltages to the other elements 22-28 in FIG. 1,

with the effect that the apparatus is in a standby state and that the

line output stage consumes hardly any current. The known means in

question may consist of, for example, a control for the user who, by

means of an opto-coupler inserted in a signal connection of the line

output stage, interrupts this signal and stops the scan. The currents in

the power supply are then very small, but the control circuit 41

maintains the voltage of 100 V, and as that of 300 V is always also

present, the voltage at the terminals of the inductance 5 remains

unchanged and thus also the voltage at the terminals of the winding 46;

the standby circuit 58 is always supplied with the same voltage.

Inventors:

Decraemer, Alain (Garches, FR)

Dormet, Jean-claude (Chaville, FR)

U.S. Philips Corporation (New York, NY).

THE PHILIPS CHASSIS GR1AX WAS ALSO USED IN MODELS :

Philips 142021IR/14B, 142821IR/14B, 14GR1021/02B, 14GR1021/05B, 14GR1021/10B, 14GR1021/16B, 14GR1021/22B, 14GR1021/57R, 14GR1021/57X, 14GR1021/59H, 14GR1022/87R, 14GR1023/67B, 14GR1024/50B, 14GR1024/50R, 14GR1024/57R, 14GR1024/59R, 14GR1024/75R, 14GR1033/65, 14GR1033/67R, 14GR1033/68R, 14GR1034/50R, 14GR1034/55R, 14GR1034/57R, 14GR1034/75R, 14GR1034/79R, 14GR1220/05B, 14GR1220/08B, 14GR1220/10B, 14GR1220/11B, 14GR1220/11E, 14GR1220/11G, 14GR1220/16B, 14GR1220/22B, 14GR1220/50B, 14GR1220/54B, 14GR1220/57B, 14GR1220/59H, 14GR1220/73B, 14GR1220/75B, 14GR1220/77B, 14GR1220/79B, 14GR1220/85B, 14GR1220/97B, 14GR1221/02B, 14GR1221/02W, 14GR1221/05B, 14GR1221/05V, 14GR1221/05W, 14GR1221/07B, 14GR1221/08B, 14GR1221/10B, 14GR1221/10V, 14GR1221/10W, 14GR1221/15B, 14GR1221/16B, 14GR1221/16L, 14GR1221/16V, 14GR1221/16W, 14GR1221/22B, 14GR1221/32B, 14GR1221/32V, 14GR1221/42B, 14GR1221/42V, 14GR1221/43B, 14GR1221/57L, 14GR1221/57R, 14GR1221/57W, 14GR1221/59R, 14GR1221/75R, 14GR1222/87R, 14GR1223/50B, 14GR1223/79B, 14GR1224/50B, 14GR1224/50R, 14GR1224/57R, 14GR1224/59H, 14GR1224/75R, 14GR1224/79R, 14GR1225/08B, 14GR1225/10B, 14GR1225/15B, 14GR1225/16B, 14GR1227/02B, 14GR1227/05B, 14GR1227/05W, 14GR1227/07B, 14GR1227/08B, 14GR1227/10B, 14GR1227/10W, 14GR1227/15B, 14GR1227/16B, 14GR1227/42B, 14GR1228/50R, 14GR1228/54R, 14GR1228/75R, 14GR1228/77R, 14GR1228/84R, 14GR1228/85R, 14GR1228/97R, 14GR1229/05B, 14GR1229/10B, 14GR1229/16B, 14GR1230/50R, 14GR1230/57R, 14GR1230/70R, 14GR1233/65, 14GR1233/67R, 14GR1233/68R, 14GR1234/50R, 14GR1234/52R, 14GR1234/54R, 14GR1234/57R, 14GR1234/58, 14GR1234/58R, 14GR1234/59H, 14GR1234/59R, 14GR1234/62R, 14GR1234/73R, 14GR1234/75R, 14GR1234/77, 14GR1234/77R, 14GR1234/79R, 14GR1234/85, 14GR1234/85R, 14GR1234/87R, 14GR1236/50, 14GR1236/50R, 14GR1236/52, 14GR1236/52R, 14GR1236/54R, 14GR1236/57, 14GR1236/57R, 14GR1236/58, 14GR1236/58R, 14GR1236/59, 14GR1236/59H, 14GR1236/59R, 14GR1236/62R, 14GR1236/65, 14GR1236/67R, 14GR1236/68, 14GR1236/68R, 14GR1236/70, 14GR1236/75, 14GR1236/75R, 14GR1236/77, 14GR1236/77R, 14GR1236/79R, 14GR1236/79R, 14GR1236/85, 14GR1236/85R, 14GR1236/87R, 14GR1239/50R, 14GR1239/59H, 14GR1239/65R, 14PT121A/05, 14PT121A/05W, 14PT121A/10, 20GR1250/02B, 37KV1232/22B.

No comments:

Post a Comment

The most important thing to remember about the Comment Rules is this:

The determination of whether any comment is in compliance is at the sole discretion of this blog’s owner.

Comments on this blog may be blocked or deleted at any time.

Fair people are getting fair reply. Spam and useless crap and filthy comments / scrapers / observations goes all directly to My Private HELL without even appearing in public !!!

The fact that a comment is permitted in no way constitutes an endorsement of any view expressed, fact alleged, or link provided in that comment by the administrator of this site.

This means that there may be a delay between the submission and the eventual appearance of your comment.

Requiring blog comments to obey well-defined rules does not infringe on the free speech of commenters.

Resisting the tide of post-modernity may be difficult, but I will attempt it anyway.

Your choice.........Live or DIE.

That indeed is where your liberty lies.

Note: Only a member of this blog may post a comment.