The (SALORA) finlux CHASSIS 5000 was the advanced analog chassis after the digital chassis providing features from multistandard and multisound capability, multi AV, OSD, teletext.

SALORA 25U7C TYPE5025(X) FINLUX CHASSIS 5000 Switched-mode power supply control circuit: Siemens Function and Application of the Switch Mode Powersupply IC TDA4605;

A controller for a switch mode power supply includes an undervoltage

protection circuit responsive to an input supply voltage indicative

signal. The input supply voltage indicative signal is also coupled to a

foldback point correction circuit. The correction circuit causes a

decrease in a maximum duty cycle of a control signal when the input

supply voltage increases and is still smaller than a predetermined

magnitude. A zener diode limits the input supply voltage indicative

signal in a manner to prevent a further decrease in the duty cycle when

the input supply voltage exceeds the predetermined magnitude.

A controller for a switch mode power supply includes an undervoltage

protection circuit responsive to an input supply voltage indicative

signal. The input supply voltage indicative signal is also coupled to a

foldback point correction circuit. The correction circuit causes a

decrease in a maximum duty cycle of a control signal when the input

supply voltage increases and is still smaller than a predetermined

magnitude. A zener diode limits the input supply voltage indicative

signal in a manner to prevent a further decrease in the duty cycle when

the input supply voltage exceeds the predetermined magnitude.a switch responsive to a first control signal having a controllable duty cycle and coupled to said source of input supply voltage for generating an output supply voltage, in accordance with said duty cycle of said first control signal;

a duty cycle modulator responsive to a second control signal for generating said first control signal and for controlling said duty cycle of said first control signal in accordance therewith, said modulator being responsive to a signal that is indicative of said input supply voltage for decreasing said duty cycle when said input supply voltage increases; and

a limiter coupled to said modulator for limiting the decrease in duty cycle, for a given increase in said input supply voltage, when said input supply voltage exceeds a first magnitude.

2. A power supply according to claim 1, wherein said duty cycle of said first control signal varies within a control range, in accordance with said second control signal, and wherein said limiter limits a decrease of said duty cycle when said duty cycle is at an end of said control range.

3. A power supply according to claim 1, wherein said limiter comprises a clamper coupled in a signal path of said input supply voltage indicative signal for clamping said input voltage indicative signal, when said input supply voltage exceeds said first magnitude, and for disabling the clamping thereof, when said input supply voltage does not exceed said first magnitude.

4. A power supply according to claim 3, wherein said voltage clamper comprises a diode.

5. A power supply according to claim 3, further comprising a disabling circuit responsive to said input supply voltage indicative signal for disabling said output supply voltage, when said input supply voltage is smaller than a second magnitude and wherein said voltage clamper is coupled in a common signal path of said input supply voltage indicative signal with respect to each of an input of said disabling circuit and an input of said limiter.

6. A power supply according to claim 1, wherein said modulator comprises a foldback point corrector for decreasing said duty cycle, when said input supply voltage increases and wherein said limiter is coupled to said corrector.

7. A power supply according to claim 1, wherein said second control signal is produced in a feedback path for regulating said output supply voltage.

8. A power supply according to claim 1, wherein said input supply voltage indicative signal is coupled to said modulator from said source of input supply voltage via a signal path that bypasses said switch.

9. A power supply according to claim 8, wherein said limiter comprises a clamp coupled in said signal path for clamping said input supply voltage indicative signal, when said input supply voltage exceeds said first magnitude, and for disabling the clamping operation, when said input supply voltage does not exceed said first magnitude.

10. A power supply, comprising: an input supply

voltage, a transformer and a switch coupled for switch mode generation

of a regulated output supply voltage, said switch being responsive to a

first control signal having a controllable duty cycle;

10. A power supply, comprising: an input supply

voltage, a transformer and a switch coupled for switch mode generation

of a regulated output supply voltage, said switch being responsive to a

first control signal having a controllable duty cycle; a duty cycle modulator for generating said first control signal responsive to a second control signal for limiting a duty cycle of said switch, said modulator operating in a first mode when said second control signal is in a predetermined range of voltage levels and operating in a second mode when said second control signal is outside of said range; and

a voltage monitor circuit for generating said second control signal, said second control signal representing a first proportion of said input supply voltage in a first range of input supply voltage values and a second proportion of said input supply voltage in a second range of input supply voltage values.

11. A power supply according to claim 10 wherein said voltage monitor circuit comprises a clamp coupled in a signal path of said second control signal.

12. A power supply according to claim 11, wherein said second signal is coupled to said modulator from said input supply voltage via a signal path that bypasses said switch.

13. A power supply, comprising: an input supply voltage, a tran

sformer and a switch coupled for switch mode generation

of a regulated output supply voltage, said switch being responsive to a

first control signal having a controllable duty cycle;

sformer and a switch coupled for switch mode generation

of a regulated output supply voltage, said switch being responsive to a

first control signal having a controllable duty cycle; a duty cycle modulator for generating said first control signal responsive to a second control signal, said modulator operating in a first mode when said second control signal is in a predetermined range of voltage levels and operating in a second mode when said second control signal is outside of said range; and

a voltage monitor circuit for generating said second control signal, said second control signal representing a first proportion of said input supply voltage in a first range of input supply voltage values and a second proportion of said input supply voltage in a second range of input supply voltage values, such that as long as said input supply voltage is in said first range of input supply voltage values, said second control signal varies when said input supply voltage varies and said modulator operates in said first mode of operation.

14. A power supply, comprising: an input supply voltage, a transformer and a switch coupled for switch mode generation of a regulated output supply voltage, said switch being responsive to a first control signal having a controllable duty cycle;

a duty cycle modulator for generating said first control signal responsive to a second control signal, said modulator operating in a first mode when said second control signal is in a predetermined range of voltage levels and operating in a second mode when said second control signal is outside of said range; and

a nonlinear voltage divider circuit coupled to said input supply voltage for generating said second control signal, said second control signal representing a first proportion of said input supply voltage in a first range of input supply voltage values and a second proportion of said input supply voltage in a second range of input supply voltage values.

Switched-mode power supplies

efficiently generate a variety of regulated voltages

from a single line voltage level (e.g., 220 volts AC). One important use

of these power supplies is within a television signal receiver where

they are used to produce a regulated B+ voltage for the horizontal

deflection circuit as well as other regulated voltages for powering

various digital and analog circuits.

efficiently generate a variety of regulated voltages

from a single line voltage level (e.g., 220 volts AC). One important use

of these power supplies is within a television signal receiver where

they are used to produce a regulated B+ voltage for the horizontal

deflection circuit as well as other regulated voltages for powering

various digital and analog circuits. Typically, a switched-mode power supply contains a full-wave rectifier, a power supply controller, a switch, and an output transformer. The switch is typically a high-power transistor such as a MOSFET. To regulate the output voltages, the controller activates and deactivates (e.g., pulse width modulates) the gate of the transistor in response to power supply loading and other control parameters. The switched voltage from the transistor drives a primary winding of the transformer, while various power supply loads are connected to one or more secondary windings. As such, the power supply converts an AC input voltage into one or more DC voltages.

One particular controller is an integrated circuit available from Siemens as Model TDA 4605. This power supply controller is typically used to drive the MOSFET transistor, which in turn drives the primary coil of the transformer. This specific integrated circuit, as well as others used in the art, typically contain a control mechanism that disables the power supply when the input voltage drops below a pre-defined voltage level. Such protection is necessary because, to produce regulated output voltages, the switched-mode power supply increases the duty cycle of the control signal driving the transistor as the input voltage decreases. At some point, the input voltage decreases to a level where the output of the power supply is unregulated (e.g., the maximum pulse length is used to drive the transistor). Such unregulated operation can damage the power supply electronics, but is more likely to damage the load electronics.

For the integrated circuit (IC) TDA4605, as defined in the TDA4605 Technical Manual available from Siemens AG, dated Jul. 27, 1989, pin 3 of the integrated circuit is used for sensing or monitoring the primary input voltage (vp) for the power supply (e.g., the rectified AC voltage). The threshold voltage for disabling or deactivating the integrated circuit, and thus the power supply, is pre-established by the controller at one volt. As such, the primary input voltage (vp) is reduced using a voltage divider at the input of pin 3. By selecting appropriate resistor

values within the voltage

divider, a nominal value of monitoring voltage is applied to pin 3.

Typically, this voltage is approximately 2.0 volts for a primary input

voltage of 120 volts. When the primary input voltage falls to a level

that causes the monitoring voltage at pin 3 to fall below one volt, the

power supply is deactivated to avoid unregulated operation.

values within the voltage

divider, a nominal value of monitoring voltage is applied to pin 3.

Typically, this voltage is approximately 2.0 volts for a primary input

voltage of 120 volts. When the primary input voltage falls to a level

that causes the monitoring voltage at pin 3 to fall below one volt, the

power supply is deactivated to avoid unregulated operation. As stated above, this form of switched-mode power supply has been finding use within television signal receivers. However, television receivers, in particular, present peculiar loading characteristics to a power supply. Specifically, a television receiver power supply is called upon to produce a regulated B+ voltage, typically of approximately 140 volts, as well as a low voltage DC level of 16 volts for powering all of the digital and analog circuitry within the receiver. When the television receiver is switched from stand-by to run mode, a heavy load is produced by the in-rush of current into filter capacitors connected to the regulated B+ voltage. This heavy load causes the power supply to temporarily operate in an unregulated (maximum pulse width) mode, and may cause the primary input voltage to drop to a low level. Furthermore, when the degaussing circuit is activated to degauss the cathode ray tube (CRT), the main AC supply voltage is depressed due to the substantial load presented by the degaussing circuit. Consequently, the drop in line voltage could typically cause the monitoring voltage to drop below the 1 volt, first threshold level, and as such, to disable the power supply.

Therefore, there it is desirable to produce a monitoring voltage indicative of the primary input voltage, but to insure that the power supply will not be deactivated for the expected heavy loads found in a television receiver.

The IC TDA 4605 includes a foldback point correction circuit that reduces the maximum duty cycle of the MOSFET control signal, when the monitoring voltage exceeds a second threshold level of approximately 1.7 V. The monitoring voltage is applied to the correction circuit also via pin 3.

In a circuit embodying an inventive feature, a resistive voltage divider that produces the monitoring input or sense signal from the primary input voltage is designed such that the first threshold level is not attained during the expected temporary loading of the primary input voltage. However, such a voltage divider results in a higher voltage being applied to the monitoring voltage input of the controller during normal operation of the power supply. As such, an increase of the primary input voltage to a higher level, which is still within the acceptable tolerance range of the AC line voltage, can cause the monitoring voltage to rise to a level that exceeds the second threshold level at which the integrated circuit begins to limit the maximum duty cycle of the control signal that controls the MOSFET, i.e., the controller applies a foldback correction technique. When the second threshold level is exceeded, the power supply automatically limits the output power of the power supply for an increase in the primary voltage. As a result of the voltage divider design that provides sufficient headroom to overcome loading generated drop outs in the primary input voltage, the maximum power supply output could be, undesirably, significantly reduced at high primary input voltage.

In carrying out an inventive feature, to insure that such inconsequential increase in the primary input voltage does not cause the power supply to significantly reduce the maximum duty cycle of the control signal and thereby, the power output of the power supply, a zener diode is coupled to the voltage divider. The zener diode limits the magnitude of the mo

nitoring voltage to a level that avoids further maximum duty cycle

limiting when the primary input voltage further increases. Consequently,

when the power supply is used in a television signal receiver, the

voltage divider provides enough head room for the primary voltage to

drop substantially due to degaussing circuit activation or other loading

conditions, while the zener diode insures that the primary voltage can

rise above its nominal voltage without causing a significant power

limitation of the power supply output.

nitoring voltage to a level that avoids further maximum duty cycle

limiting when the primary input voltage further increases. Consequently,

when the power supply is used in a television signal receiver, the

voltage divider provides enough head room for the primary voltage to

drop substantially due to degaussing circuit activation or other loading

conditions, while the zener diode insures that the primary voltage can

rise above its nominal voltage without causing a significant power

limitation of the power supply output. A switch mode power supply, embodying an aspect of the invention, includes a source of an input supply voltage. A switch is responsive to a first control signal having a controllable duty cycle and coupled to the source of input supply voltage for generating an output supply voltage, in accordance with the duty cycle of the first control signal. A duty cycle modulator is responsive to a second control signal for generating the first control signal and for controlling the duty cycle of the first control signal in accordance therewith in a manner to control the current pulses. An increase in the duty cycle produces an increase in a magnitude of the current pulses. The modulator is responsive to a signal that is indicative of the input supply voltage for decreasing the duty cycle when the input supply voltage increases. A limiter is coupled to the modulator for limiting the decrease in duty cycle, for a given increase in said input supply voltage, when the input supply voltage exceeds a first magnitude.

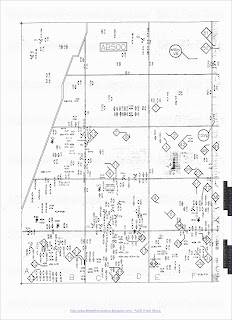

FIG. 1 depicts a schematic diagram of a switched-mode power supply incorporating the teachings of the present invention.

FIG.

1 depicts a schematic diagram of a switched-mode power supply 100

incorporating the present invention. The embodiment shown is designed

for use as a power supply for a television signal receiver, wherein the

power supply generates a regulated B+ voltage (e.g., 220 volts) and a

low voltage (e.g., 16 volts). The regulated B+ voltage is used to power a

horizontal deflection circuit and the regulated low voltage is used to

power the digital and analog electronics (continuous load 118). Other

applications for the power supply may require slight variation in the

depicted components and their interconnections; however, such variations

are well within the scope of the present invention.

FIG.

1 depicts a schematic diagram of a switched-mode power supply 100

incorporating the present invention. The embodiment shown is designed

for use as a power supply for a television signal receiver, wherein the

power supply generates a regulated B+ voltage (e.g., 220 volts) and a

low voltage (e.g., 16 volts). The regulated B+ voltage is used to power a

horizontal deflection circuit and the regulated low voltage is used to

power the digital and analog electronics (continuous load 118). Other

applications for the power supply may require slight variation in the

depicted components and their interconnections; however, such variations

are well within the scope of the present invention. The power supply contains a number of major components, including a full-wave rectifier 102, the power supply controller 106, a MOSFET transistor Q1, a monitor voltage generator 110, an output transformer 112, and a plurality of circuit components used to complete the power supply electronics. Illustratively, the input to the power supply is a 110-volt AC, 60 hertz voltage.

Rectifier 102 is a conventional full-wave bridge rectifier coupled to an AC input voltage source 101. The output of the bridge rectifier 102 is coupled to capacitor C1 approximately 680 μF). A voltage RAW B+ forms raw (unregulated) B+ voltage (also referred to herein as the primary input voltage vp) having a nominal value of approximately 150 volts. Capacitor C1, connected from the output of the rectifier to ground, smoothes the voltage from the bridge rectifier such that a DC voltage, i.e., the primary input voltage vp, is available at the upper terminal of the transformer's primary winding W1.

The primary input voltage forms an input to the monitor voltage generator 110 which produces a monitor voltage VZ1 for

the controller 106. The

monitor voltage generator is discussed in detail below.

the controller 106. The

monitor voltage generator is discussed in detail below. The controller is illustratively a TDA4605 power supply controller available from Siemens AG of Munich, Germany. The eight pins of the controller are connected to signals and voltages that enable the controller to produce a pulse width or duty cycle modulated signal at pin five for controlling the duty cycle of the transistor Q1. Specifically, pin 4 of controller 106 is grounded. Pin 3 is coupled to the monitor voltage.

Pin 2 is supplied information concerning the primary current. A primary current increase in the primary winding W1 is simulated as a voltage rise of a periodical, ramp voltage VC2 at pin 2 using an external RC element formed by resistor R3, capacitor C2, and resistor R4 (where R3 is approximately 360 kΩ, C2 is approximately 6,800 pF; and R4 is approximately 220 Ω). These elements are connected in series from the primary input voltage to ground. Pin 2 of the controller 106 is coupled to the junction of R3 and C2. A pulse width modulator 106c of the controller 106 controls the duration of the forward phase, and thus, the primary peak current, using ramp voltage VC2 that is proportional to the drain current of the transistor Q1. As indicated before, the ramp voltage is derived from the primary input voltage using the RC elements connected to pin 2, i.e., the ramp voltage simulates the primary current. Controller pin 1 is supplied secondary voltage information which internally compares the control voltage sampled from the regulating winding W3 of the transformer 112 and compares that sample voltage with an internal reference voltage.

Pin 5 generates a duty cycle modulated control signal or voltage VOUT via a push-pull output driver for rapid charge and discharge of the input capacitance of a MOSFET power transistor Q1 (Model IRF740).

Pin 6 is coupled to the supply voltage for the controller. Pin 7 forms a soft start input terminal. Capacitor C5 (0.1 μF) is connected from pin 7 to ground to reduce the pulse duration during start-up. Lastly, pin 8 is the input pin for the oscillator feedback.

In operation, the transistor Q1 is used as a power switch controlled by the controller 106. A snubber circuit is connected to the drain of the transistor Q1. The snubber circuit contains a combination of diode D3, resistor R16 and capacitor C12, which together limit the voltage overshoot when the transistor is turned off. D3 is a MUR450 diode, C12 is a 1000 pF capacitor, and R16 is a 2-watt, 30 kΩ resistor.

Together with the stray capacitance of the transformer, capacitor C7 (470 pF connected from drain terminal to ground) determines the no-load frequency, and consequently, the maximum slew rate of the drain voltage for a transistor Q1.

Transistor Q1 is driven with pulse width modulated signal VOUT produced at pin 5 of controller 106 and coupled to the gate terminal of the transistor via resistor R11 (35 Ω). Furthermore, a capacitor C6 (4700 pF) is coupled from the source terminal to the drain terminal. The source terminal is coupled to ground through resistor R13 (0.27 KΩ). Resistor R12 (10 kΩ) is optionally connected between the source terminal and gate terminal to ensure that the transistor will not be activated if power is applied to the power supply without the controller 106 being installed. The drain terminal is coupled to one terminal of the primary winding W1 of transformer 112. Consequently, the transistor Q1 controls the current flow from the primary input voltage thr

ough the primary winding.

ough the primary winding. The secondary circuit of the transformer 112 consists of several windings, each of which has a different number of turns, polarity, and load capacity. Specifically, winding W2 forms the output voltage for the regulated B+, while winding W4 forms the output winding for the regulated 16-volt low voltage output, and winding W3 generates the feedback voltage for the controller 106.

The load circuitry includes, connected to winding W2, an output diode D4 and capacitor C13 that couple power to the horizontal deflection circuit 116. Additionally, the center tap of the output secondary winding is connected to ground, and winding W4 is coupled to diode D5 and capacitor C14. This output is the 16 volts that powers the continuous load 118 of the television receiver, e.g., all of the electronics and integrated circuits. This circuit 118 also controls the timing of when the degaussing circuit 114 is activated using degaussing control line 120. The control line for the continuous load is the run/standby control signal that essentially turns the television receiver on and off. The continuous load circuitry 118 is also coupled to the horizontal deflection circuit 116 to provide control signals therefor.

The controller 106 is started up using resistor R17 (100 KΩ) as a start resistor. As such, capacitor C11 (100 μF) is charged with half-wave currents at the voltage supply pin of the controller 106, e.g., pin 6. These half-wave currents are supplied from the primary input voltage through resistor R17 (100 KΩ) to ground through series connected resistor R14 (202 Ω), diode D

2 (148 Ω) and regulating winding

W3. When the voltage at C11 reaches the switch-on threshold, the

switched-mode power supply begins to function and supplies the feedback

voltage, via winding W3, resistor R14 and diode D2. This feedback

voltage, when rectified by diode D2 and smoothed by capacitor C11, forms

the supply voltage (vcc) for the controller 106 via pin 6.

2 (148 Ω) and regulating winding

W3. When the voltage at C11 reaches the switch-on threshold, the

switched-mode power supply begins to function and supplies the feedback

voltage, via winding W3, resistor R14 and diode D2. This feedback

voltage, when rectified by diode D2 and smoothed by capacitor C11, forms

the supply voltage (vcc) for the controller 106 via pin 6. A control signal or voltage VCT for pin 1 is generated in a circuit parallel to the controller supply voltage circuit. The control voltage is produced by diode D1 (ERB43) charging capacitor C3 (1.5 μF) through resistor R8 (10 Ω). The RC element, consisting of series connected R15 (30 Ω) and C10 (0.01 μF), prevents peak value rectification of high frequency components of the feedback signal.

More specifically, regulating winding W3 is coupled to one terminal of resistor R15. The other terminal of resistor R15 is coupled to capacitor C10 to ground. Diode D1 is connected at the junction of resistor R15 and capacitor C10. Capacitor C9 (1000 pF) is connected in parallel with diode D1. Diode D1 has an output voltage that is coupled to series connected R8 and C3 which couples the output of the diode to ground. The output of the diode is also coupled through resistive divider network R6 and R7 which are respectively connected in series to ground. The voltage at the junction of R6 and R7 forms control voltage VCT and is coupled to pin 1 of the controller 106. These resistors define the no-load frequency of oscillation of the controller 106. Therefore, they are typically 0.1% accurate resistors having R6 being 5.49 KΩ, and R7 being 174 Ω. Control voltage VCT is coupled to a pulse-width modulator 106c within controller 106 that co

ntrols the duty cycle modulation of voltage VOUT for

regulating, for example, voltage REGB+.

ntrols the duty cycle modulation of voltage VOUT for

regulating, for example, voltage REGB+. During the power supply start-up, capacitor C5 at the soft-start pin (e.g., pin 7), influences the duration of the forward phase by controlling the error voltage of the pulse width modulator. The controller detects the end of the transformer discharge phase via resistor R10 (20 KΩ) that is coupled at one end to controller pin 8 and at the other end to resistor R14, and ultimately to the regulating winding W3. Additionally, capacitor C8 (0.022 μF) is coupled from the junction of R10 and R14 to ground. At this point, the voltage changes polarity from positive to negative, i.e., the voltage represents zero crossings.

A voltage VZ1, embodying an inventive feature, is generated by the monitor voltage generator 110 and is coupled to pin 3 of the controller 106. Voltage VZ1 is used both for determining the minimum line voltage that will allow the power supply to o

perate and for controlling a foldback point

correction circuit 106b within the controller 106.

perate and for controlling a foldback point

correction circuit 106b within the controller 106. The monitor voltage generator 110 contains resistor R1 (270 kΩ) coupled in series with resistor R2 (5100 Ω) to form a resistive voltage divider network with respect to primary input voltage RAW B+. The junction of the two resistors is coupled to the pin 3 of controller 106. Furthermore, a zener diode Z1 (B2X55/C3VO), embodying an inventive feature, is connected in parallel with resistor R2 from the junction point to ground. Zener diode Z1 forms a limiter for limiting the maximum voltage across R2 to the breakdown voltage of the zener diode Z1. Consequently, the voltage at the output of the monitor voltage generator 110 tracks the primary input voltage RAW B+ up to the threshold point where the zener diode Z1 begins to conduct.

The controller 106 includes an under-voltage detector 106a that uses a fixed, internal voltage threshold that causes the controller to disable the power supply whenever the monitor voltage VZ1 drops below a first threshold voltage. For the TDA 4605 integrated circuit, this first threshold voltage is one volt. As such, the divider network of R1 and R2 defines a voltage at the output that under typical operation would not cause the controller to deactivate the power supply.

In one particular application, e.g., a television signal receiver, a degaussing circuit 114 for a television signal receiver is typically connected directly across the input AC power. Consequently, when the degaussing circuit is activated, it will typically cause a drop in the AC voltage that is applied to the input of the voltage rectifier 102. Consequently, the primary input voltage RAW B+ will drop significantly during the degaussing period. Since this is a normal behavior of a conventional television receiver circuit, it is desirable that the monitor voltage generator 110 be designed such that the controller 106 will not deactivate the power supply during the degaussing period.

For a primary input voltage of 120 volts and using a resistive divider of 270 KΩ for R1 and 5100 Ω for R2, the nominal voltage VZ1 at the voltage monitor input pin is 2 volts. Such a value for the voltage monitor voltage will avoid power supply deactivation during the degaussing period or other heavy load period.

When the duty cycle of voltage VOUT is at the maximum as a result of an overload condition, an increase in voltage RAW B+, produced by an increase in the AC line voltage, causes the voltage across primary winding w1 to increase. As the primary input voltage RAW B+ rises, the available input power to the power supply increases which could damage the power supply when the power supply is overloaded. During a period of overloaded, unregulated output, the modulator 106c generates the voltage VOUT having a maximum duty cycle for driving transistor Q1. As a result, a primary current IP in winding W1 of transformer 112 has also a maximum duty cycle. Therefore, undesirably an increase in voltage RAW B+ can produce a large voltage across the transistor that could damage the transistor or other circuitry.

To maintain the power supply within a safe operation range, the controller 106 includes what is known as a foldback or overload point correction circuit 106b. This foldback point correction circuit reduces the maximum duty cycle of voltage VOUT when the primary input voltage exceeds a predetermined magnitude. An increase above the predetermined magnitude causes the foldback point correction circuit 106b to decrease the maximum duty cycle of signal VOUT as voltage RAW B+ increases. The decrease is done by generating a correction curren

t ICOR

that is coupled to capacitor C2 causing an increase in the rate of

change of voltage VC2 at pin 2 of controller 106 when voltage VZ1

exceeds a second threshold voltage.

t ICOR

that is coupled to capacitor C2 causing an increase in the rate of

change of voltage VC2 at pin 2 of controller 106 when voltage VZ1

exceeds a second threshold voltage. When voltage RAW B+ increases and causes voltage VZ1 to further increase above the second threshold voltage an increase in current ICOR produces a decrease in the maximum duty cycle of signal VOUT, in a well know manner. The second threshold voltage occurs when voltage VZ1 is above a voltage level of approximately 1.7 V. The result is that, when voltage RAW B+ further increases the maximum duty cycle decreases proportionally. The decrease in the maximum duty cycle tends to stabilize the maximum power produced in the power supply against an increase of voltage RAW B+. On the other hand, an increase of voltage VZ1 when voltage VZ1 is below the 1.7 V level, does not affect current ICOR and the duty cycle of voltage VOUT.

Because the divider network (R1 and R2) establishes a sufficiently large monitor voltage VZ1 that provides sufficient headroom for preventing power supply shutdown when the degaussing circuit is activated, primary input voltage RAW B+ may be at a level that causes voltage VZ1 to exceed the second threshold voltage of circuit 106b by an excessive amount even when voltage RAW B+ is within the normal tolerance range. Therefore, disadvantageously, the maximum duty cycle may further decrease by a significant amount in a manner to lower the maximum power that can be derived. Such significant reduction in power capability can occur even though primary input voltage is not truly at such a high level that could damage the power supply.

In accordance with an inventive feature, to prevent current ICOR from further reducing the maximum duty cycle of voltage VOUT when voltage RAW B+ increases above a threshold magnitude that corresponds to voltage VZ1 being equal to 3 V, the monitor voltage generator 110 contains the zener diode Z1 operating as a limiter which limits the primary input voltage indicative voltage VZ1 to 3 V. Consequently, the monitor voltage VZ1 can never rise above a pre-defined level (e.g., 3 volts) that would otherwise cause the foldback point correction circuit 106b within the controller 106 to further decrease the maximum duty cycle. In this way, advantageously, the decrease in the maximum duty cycle as a function of an increase in voltage RAW B+ is limited.

The decrease in the duty cycle of voltage VOUT produced by current ICOR, for a given increase in voltage RAW B+, is limited

when voltage RAW B+ is greater than a threshold

magnitude that corresponds to voltage VZ1 equal to 3 V. In contrast, the

decrease in the duty cycle produced by current ICOR is not limited but

varies proportionally to voltage RAW B+ when voltage VZ1 is between 1.7 V

and 3 V. Thus, zener diode Z1 operates as a limiter for limiting the

decrease in the duty cycle when the voltage RAW B+ exceeds the threshold

magnitude relative to when voltage RAW B+ does not exceed the threshold

magnitude. An increase in voltage RAW B+ that produces voltage VZ1

below the second threshold voltage of 1.7 V, does not affect current

ICOR.

when voltage RAW B+ is greater than a threshold

magnitude that corresponds to voltage VZ1 equal to 3 V. In contrast, the

decrease in the duty cycle produced by current ICOR is not limited but

varies proportionally to voltage RAW B+ when voltage VZ1 is between 1.7 V

and 3 V. Thus, zener diode Z1 operates as a limiter for limiting the

decrease in the duty cycle when the voltage RAW B+ exceeds the threshold

magnitude relative to when voltage RAW B+ does not exceed the threshold

magnitude. An increase in voltage RAW B+ that produces voltage VZ1

below the second threshold voltage of 1.7 V, does not affect current

ICOR. Specifically, for the TDA4605 integrated circuit control, the zener diode has a value of three volts. Consequently, the input signal to the monitor voltage generator cannot rise above the three volt level before the zener diode will begin to conduct current to ground. As such, the monitor voltage generator establishes a range of voltages that pre-defines a range of primary input voltages at which the controller 106 operates in a normal manner that avoids both an undervoltage power supply deactivation and a further decrease in the maximum duty cycle. The input voltage dynamic range is thereby extended.

SALORA 25U7C TYPE5025(X) FINLUX CHASSIS 5000 TDA 4605-3 Control IC for Switched-Mode Power Supplies usingMOS-Transistor

The IC TDA 4605-3 controls the MOS-power transistor and performs all necessary control and

The IC TDA 4605-3 controls the MOS-power transistor and performs all necessary control andprotection functions in free running flyback converters. Because of the fact that a wide load range

is achieved, this IC is applicable for consumer as well as industrial power supplies.

The serial circuit and primary winding of the flyback transformer are connected in series to the input

voltage. During the switch-on period of the transistor, energy is stored in the transformer. During the

switch-off period the energy is fed to the load via the secondary winding. By varying switch-on time

of the power transistor, the IC controls each portion of energy transferred to the secondary side

such that the output voltage remains nearly independent of load variations. The required control

information is taken from the input voltage during the switch-on period and from a regulation winding

during the switch-off period. A new cycle will start if the transformer has transferred the stored

energy completely into the load.

In the different load ranges the switched-mode power supply (SMPS) behaves as follows:

No load operation

The power supply is operating in the burst mode at typical 20 to 40 kHz. The output voltage can be

a little bit higher or lower than the nominal value depending of the design of the transformer and the

resistors of the control voltage divider.

Nominal operation

The switching frequency is reduced with increasing load and decreasing AC-voltage.

The output voltage is only dependent on the load.

Overload point

Maximal output power is available at this point of the output characteristic.

Overload

The energy transferred per operation cycle is limited at the top. Therefore the output voltages

declines by secondary overloading.

Circuit Description

Application Circuit

The application circuit shows a flyback converter for video recorders with an output power rating of

70 W. The circuit is designed as a wide-range power supply for AC-line voltages of 180 to 264 V.

The AC-input voltage is rectified by the bridge rectifier GR1 and smoothed by C1 . The NTC limits

the rush-in current.

In the period before the switch-on threshold is reached the IC is suppled via resistor R 1 ; during the

start-up phase it uses the energy stored in C2 , under steady state conditions the IC receives its

supply voltage from transformer winding n1 via diode D1. The switching transistor T1 is a BUZ 90.

The parallel connected capacitor C3 and the inductance of primary winding n 2 determine the

system resonance frequency. The R 2-C4-D2 circuitry limits overshoot peaks, and R 3 protects the

gate of T1 against static charges.

During the conductive phase of the power transistor T1 the current rise in the primary winding

depends on the winding inductance and the mains voltage. The network consisting of R 4-C5 is used

to create a model of the sawtooth shaped rise of the collector current. The resulting control voltage

is fed into pin 2 of the IC. The RC-time constant given by R 4-C5 must be designed that way that

driving the transistor core into saturation is avoided.

The ratio of the voltage divider R 10/R 11 is fixing a voltage level threshold. Below this threshold the

switching power supply shall stop operation because of the low mains voltage. The control voltage

present at pin 3 also determines the correction current for the fold-back point. This current added to

the current flowing through R 4 and represents an additional charge to C5 in order to reduce the turnon

phase of T1. This is done to stabilize the fold-back point even under higher mains voltages.

Regulation of the switched-mode power supplies via pin 1. The control voltage of winding n1 during

the off period of T1 is rectified by D3, smoothed by C6 and stepped down at an adjustable ratio by

R 5 , R 6 and R 7 . The R 8-C7 network suppresses parasitic overshoots (transformer oscillation). The

peak voltage at pin 2, and thus the primary peak current, is adjusted by the IC so that the voltage

applied across the control winding, and hence the output voltages, are at the desired level.

When the transformer has supplied its energy to the load, the control voltage passes through zero.

The IC detects the zero crossing via series resistors R 9 connected to pin 8. But zero crossings are

also produced by transformer oscillation after T1 has turned off if output is short-circuited. Therefore

the IC ignores zero crossings occurring within a specified period of time after T1 turn-off.

The capacitor C8 connected to pin 7 causes the power supply to be started with shorter pulses to

keep the operating frequency outside the audible range during start-up.

On the secondary side, five output voltages are produced across winding n3 to n7 rectified by D4 to

D8 and smoothed by C9 to C13 . Resistors R 12 , R 14 and R 19 to R 21 are used as bleeder resistors.

Fusable resistors R 15 to R 18 protect the rectifiers against short circuits in the output circuits, which

are designed to supply only small loads.

Pin 1

The regulating voltage forwarded to this pin is compared with a stable internal reference voltage VR

in the regulating and overload amplifier. The output of this stage is fed to the stop comparator. If

the control voltage is rather small at pin 1 an additional current is added by means of current source

which is controlled according the level at pin 7. This additional current is virtually reducing the

control voltage present at pin 1.

Pin 2

A voltage proportional to the drain current of the switching transistor is generated there by the

external RC-combination in conjunction with the primary current transducer. The output of this

transducer is controlled by the logic and referenced to the internal stable voltage V2B . If the voltage

V2 exceeds the output voltage of the regulations amplifier, the logic is reset by the stop comparator

and consequently the output of pin 5 is switched to low potential. Further inputs for the logic stage

are the output for the start impulse generator with the stable reference potential VST and the

supply voltage motor.

Pin 3

The down divided primary voltage applied there stabilizes the overload point. In addition the logic is

disabled in the event of low voltage by comparison with the internal stable voltage VV in the primary

voltage monitor block.

Pin 4

Ground

Pin 5

In the output stage the output signals produced by the logic are shifted to a level suitable for MOSpower

transistors.

Pin 6

From the supply voltage V6 are derived a stable internal references VREF and the switching

threshold V6A , V6E , V6 max and V6 min for the supply voltage monitor. All references values (VR ,

V2B , VST) are derived from VREF . If V6 > VVE , the VREF is switched on and switched off when V6 <

V 6A . In addition, the logic is released only for V6 min < V6 < V6 max .

Pin 7

The output of the overload amplifier is connected to pin 7. A load on this output causes a reduction

in maximal impulse duration. This function can be used to implement a soft start, when pin 7 is

connected to ground by a capacitor.

Pin 8

The zero detector controlling the logic block recognizes the transformer being discharged by

positive to negative zero crossing of pin 8 voltage and enables the logic for a new pulse. Parasitic

oscillations occurring at the end of a pulse cannot lead to a new pulse (double pulsing), because an

internal circuit inhibits the zero detector for a finite time tUL after the end of each pulse.

Start-Up Behaviour

The start-up behaviour of the application circuit per sheet 88 is represented an sheet 90 for a line

The start-up behaviour of the application circuit per sheet 88 is represented an sheet 90 for a linevoltage barely above the lower acceptable limit time t0 the following voltages built up:

– V6 corresponding to the half-wave charge current over R1

– V2 to V2 max (typically 6.6 V)

– V3 to the value determined by the divider R 10/R 11 .

The current drawn by the IC in this case is less than 1.6 mA.

If V6 reaches the threshold V6E (time point t1), the IC switches on the internal reference voltage. The

current draw max. rises to 12 mA. The primary current- voltage reproducer regulates V2 down to V2B

and the starting impulse generator generates the starting impulses from time point t5 to t6 . The

feedback to pin 8 starts the next impulse and so on. All impulses including the starting impulse are

controlled in width by regulating voltage of pin 1. When switching on this corresponds to a shortcircuit

event, i.e. V1 = 0. Hence the IC starts up with "short-circuit impulses" to assume a width

depending on the regulating voltage feedback (the IC operates in the overload range). The IC

operates at the overload point. Thereafter the peak values of V2 decrease rapidly, as the starting

attempt is aborted (pin 5 is switched to low). As the IC remains switched on, V6 further decreases

to V6 . The IC switches off; V6 can rise again (time point t4) and a new start-up attempt begins at

time point t1 . If the rectified alternating Iine voltage (primary voltage) collapses during load, V3 can

fall below V3A , as is happening at time point t3 (switch-on attempt when voltage is too low). The

primary voltage monitor then clamps V3 to V3S until the IC switches off (V6 < V6A). Then a new startup

attempt begins at time point t1 .

Regulation, Overload and No-Load Behaviour

When the IC has started up, it is operating in the regulation range. The potential at pin 1 typically is

400 mV. If the output is loaded, the regulation amplifier allows broader impulses (V5 = H). The peak

voltage value at pin 2 increases up to V2S max . If the secondary load is further increased, the

overload amplifier begins to regulate the pulse width downward. This point is referred to as the

overload point of the power supply. As the IC-supply voltage V6 is directly proportional to the

secondary voltage, it goes down in accordance with the overload regulation behaviour. If V6 falls

below the value V6 min , the IC goes into burst operation. As the time constant of the half-wave

charge-up is relatively large, the short-circuit power remains small. The overload amplifier cuts back

to the pulse width tpk . This pulse width must remain possible, in order to permit the IC to start-up

without problems from the virtual short-circuit, which every switching on with V1 = 0 represents. If

the secondary side is unloaded, the loading impulses (V5 = H) become shorter. The frequency

the secondary side is unloaded, the loading impulses (V5 = H) become shorter. The frequencyincreases up to the resonance frequency of the system. If the load is further reduced, the secondary

voltages and V6 increase. When V6 = V6 max the logic is blocked. The IC converts to burst

operation.This renders the circuit absolutely safe under no-load conditions.

Behaviour when Temperature Exceeds Limit

An integrated temperature protection disables the logic when the chip temperature becomes too

high. The IC automatically interrogates the temperature and starts as soon as the temperature

decreases to permissible values.

SALORA 25U7C TYPE5025(X) FINLUX CHASSIS 5000 TDA4650 Multistandard colour decoder, with negative colour difference output signals

GENERAL DESCRIPTION

The TDA4650 is a monolitic

The TDA4650 is a monoliticintegrated multistandard colour

decoder for PAL, SECAM and NTSC

(3.58 and 4.43 MHz) with negative

colour difference output signals. The

colour-difference output signals are

fed to the TDA4660/TDA4661,

Switched capacitor delay line.

FEATURES

Identifies and demodulates PAL,

SECAM, NTSC 3.58 and NTSC 4.43

chrominance signals with:

· Identification

– automatic standard identification

by sequential inquiry

– secure SECAM identification at

50 Hz only, with PAL priority

– four switched outputs for

chrominance filter selection and

display control

– external service switch for

oscillator adjustment

· PAL / NTSC demodulation

– H (burst) and V blanking

– PAL switch (disabled for NTSC)

– NTSC phase shift (disabled for

PAL)

– PLL-controlled reference

oscillator

– two reference oscillator crystals

on separate pins with automatic

switching

– quadrature demodulator with

subcarrier reference

· SECAM demodulation

– limiter-amplifier

– quadrature-demodulator with a

single external reference tuned

circuit

– alternate line blanking, H and V

blanking

– de-emphasis

· Gain controlled chrominance

amplifier

· ACC demodulation controlled by

system scanning

· Internal colour-difference signal

output filters to remove the residual

subcarrier.

GENERAL DESCRIPTION

The TDA4650 is a monolitic

integrated multistandard colour

decoder for PAL, SECAM and NTSC

(3.58 and 4.43 MHz) with negative

colour difference output signals. The

colour-difference output signals are

fed to the TDA4660/TDA4661,

Switched capacitor delay line.

Notes to the characteristics

1. For the

SECAM standard, amplitude and H/2 ripple content of the CD signals (R-Y) and (B-Y) depend on the

SECAM standard, amplitude and H/2 ripple content of the CD signals (R-Y) and (B-Y) depend on thecharacteristics of the external tuned circuit at pins 7 to 10. The resonant frequency of the external tuned circuit must

be adjusted such that the demodulated fo voltage level is zero in the -(B-Y) output channel at pin 3.

Now it is possible to adjust the quality of the external circuit such that the demodulated fo voltage level is zero in the

-(R-Y) output channel at pin 1. If necessary, the fo voltage level in the -(B-Y) output channel must be readjusted to

zero by the coil of the tuned circuit.

The external capacitors at the pins 2 and 4 (220 pF each) are matched to the internal resistances of the de-emphasis

network such that every alternate scanned line is blanked.

2. The fo frequencies of the 8.8 MHz crystal at pin 21, and the 7.2 MHz crystal at pin 19, can be adjusted when the

voltage at pin 17 is less than 0.5 V (burst OFF), thus providing double subcarrier frequencies of the chrominance

signal.

3. The inquiry sequence for the standard is: PAL - SECAM - NTSC (3.58 MHz) - NTSC (4.43 MHz).

PAL has priority with respect to SECAM, etc.

4. The super sandcastle pulse is compared with three internal threshold levels which are proportional to VP.

SALORA 25U7C TYPE5025(X) FINLUX CHASSIS 5000 TDA3654 TDA3654Q Vertical deflection and guard circuit (110°)

GENERAL DESCRIPTION

The TDA3654 is a full performance vertical deflection output circuit for direct drive of the deflection coils and can be used

for a wide range of 90° and 110° deflection systems.

A guard circuit is provided which blanks the picture tube screen in the absence of deflection current.

A guard circuit is provided which blanks the picture tube screen in the absence of deflection current.Features

· Direct drive to the deflection coils

· 90° and 110° deflection system

· Internal blanking guard circuit

· Internal voltage stabilizer

FUNCTIONAL DESCRIPTION

Output stage and protection circuits

The output stage consists of two Darlington configurations in class B arrangement.

Each output transistor can deliver 1,5 A maximum and the VCEO is 60 V.

Protection of the output stage is such that the operation of the transistors remains well within the SOAR area in all

circumstances at the output pin, (pin 5). This is obtained by the cooperation of the thermal protection circuit, the

current-voltage detector and the short circuit protection.

Special measures in the internal circuit layout give the output transistors extra solidity, this is illustrated in Fig.5 where

typical SOAR curves of the lower output transistor are given. The same curves also apply for the upper output device.

The supply for the output stage is fed to pin 6 and the output stage ground is connected to pin 4.

Driver and switching circuit

Pin 1 is the input for the driver of the output stage. The signal at pin 1 is also applied to pin 3 which is the input of a

switching circuit (pin 1 and 3 are connected via external resistors).

This switching circuit rapidly turns off the lower output stage when the flyback starts and it, therefore, allows a quick start

of the flyback generator. The maximum required input signal for the maximum output current peak-to-peak value of 3 A

is only 3 V, the sum of the currents in pins 1 and 3 is then maximum 1 mA.

Flyback generator

During scan, the capacitor between pins 6 and 8 is charged to a level which is dependent on the value of the resistor at pin 8.

When the flyback starts and the voltage at the output pin (pin 5) exceeds the supply voltage, the flyback generator is

activated.

The supply voltage is then connected in series, via pin 8, with the voltage across the capacitor during the flyback period.

This implies that during scan the supply voltage can be reduced to the required scan voltage plus saturation voltage of

the output transistors.

The amplitude of the flyback voltage can be chosen by changing the value of the external resistor at pin 8.

It should be noted that the application is chosen such that the lowest voltage at pin 8 is > 1,5 V, during normal operation.

Guard circuit

When there is no deflection current, for any reason, the voltage at pin 8 becomes less than 1 V, the guard circuit will

produce a d.c. voltage at pin 7. This voltage can be used to blank the picture tube, so that the screen will not burn in.

Voltage stabilizer

The internal voltage stabilizer provides a stabilized supply of 6 V to drive the output stage, so the drive current is not

affected by supply voltage variations.

TDA8443A I2C-bus controlled YUV/RGB switch

GENERAL DESCRIPTION

The TDA8443A is a

general purpose two-channel switch

general purpose two-channel switchfor YUV or RGB signals. One channel provides matrixing

from RGB to YUV, which can be bypassed.

The IC is controlled via I2C-bus by seven different

addresses or can be used in a non-I2C-bus mode. In the

non-I2C-bus mode, control of the circuit is achieved by DC

voltages.

FEATURES

· Two RGB/YUV selectable clamped inputs with

associated synchronization

· RGB/YUV matrix

· 3-state switching with an OFF-state

· Selectable gain

· I2C-bus or non-I2C-bus mode

· Address selection for 7 devices

· Fast switching.

FUNCTIONAL DESCRIPTION

The circuit contains two sets of inputs (see Fig.1). Both

channels can receive RGB or YUV signals. Each set of

inputs has its own synchronization input, which internally

generates a pulse to clamp the inputs. The internal

clamping pulse can also be controlled by a signal (e.g. a

sandcastle pulse) applied to pin 24. The pulse will occur

during the time that the signal at pin 24 is between

5.5 and 6.5 V. If both a sync signal and a pin 24 signal are

used the signal should be applied to pin 24 via a 1 kW

resistor.

RGB signals of Channel 2 can be matrixed to YUV signals.

The outputs can be set in a high impedance OFF state,

which allows the use of seven devices in parallel

(I2C-bus mode).

The circuit can be controlled by an I2C-bus compatible

microcontroller or directly by DC voltages. The fast

switching input can be operated via pin 16 of the

peritelevision connector.

Input clamps

The R, G, B respectively (R-Y), Y and (B-Y) video signals

are AC-coupled to the IC where they are clamped on the

black level. The timing information for this clamping action

is derived from the associated synchronization signal

SYNC, which could also consist of the composite video

information signal CVBS. The syncsignal is AC-coupled to

the IC where it is clamped on top-sync level, information

obtained from this action is used to generate the clamp

pulses.

The clamp pulses can be generated in two ways:

1. Using the sync information (internal clamping)

1. Using the sync information (internal clamping)The sync information is clamped on top-sync and the

information obtained from this action is used to switch

an internal current source at pin 24.

Pin 24 should be connected to VP via a 4.7 kW resistor,

and a 1 nF capacitor to ground. During video scan the

voltage at pin 24 will be HIGH (equals positive supply

voltage). During the synchronization pulses the

voltage at pin 24 will drop to zero because of the

current sink (2.5 mA).

When the synchronization pulse is over, the current

source is switched off and the voltage at pin 24 will rise

to its higher level. Because of the time constant at

pin 24, the restoration will take some microseconds.

The voltage at pin 24 is also sensed internally and at

the time it is between 0.456VP and 0.544VP, a time

pulse is generated and used for the clamping action.

2. Using a sandcastle pulse (external clamping)

If an associated sandcastle pulse is available, it can

also be used as a clamping pulse. In this event the

sandcastle pulse should be connected to pin 24, the

top of the clamping pulse should be between 0.544VP

and 0.456VP. The timing of the internal clamping pulse

will be equal to the timing of the higher part of the

sandcastle pulse. If the sync signal is also connected,

the current sink will also become active during the

synchronization pulses. This means that the

sandcastle pulse should be connected to pin 24 via a

1 kW dropping resistor. In this event only the

sandcastle pulse at pin 24 will be influenced during

sync pulses, but the sandcastle pulse at the

sandcastle source will be unchanged.

TDA2579B Horizontal/vertical synchronization circuit.

GENERAL DESCRIPTION

The TDA2579B generates and synchronizes horizontal and vertical signals. The device has a 3 level sandcastle output;

a transmitte

r identification signal and also 50/60 Hz identification.

r identification signal and also 50/60 Hz identification.Features

· Horizontal phase detector, (sync to oscillator), sync separator and noise inverter

· Triple current source in the phase detector with automatic selection

· Second phase detector for storage compensation of the horizontal output

· Stabilized direct starting of the horizontal oscillator and output stage from mains supply

· Horizontal output pulse with constant duty cycle value of 29 ms

· Internal vertical sync separator, and two integration selection times

· Divider system with three different reset enable windows

· Synchronization is set to 628 divider ratio when no vertical sync pulses and no video transmitter is identified

· Vertical comparator with a low DC feedback signal

· 50/60 Hz identification output combined with mute function

· Automatic amplitude adjustment for 50 and 60 Hz and blanking pulse duration

· Automatic adaption of the burst-key pulsewidth.

FUNCTIONAL DESCRIPTION

Vertical part (pins 1,2,3,4)

The IC embodies a synchronized divider system for generating the vertical sawtooth at pin 3. The divider system has an

internal frequency doubling circuit, so the horizontal oscillator is working at its normal line frequency and one line period

equals 2 clock pulses. Due to the divider system no vertical frequency adjustment is needed. The divider has a

discriminator window for automatically switching over from the 60 Hz to 50 Hz system. The divider system operates with

3 different divider reset windows for maximum interference/disturbance protection.

The windows are activated via an up/down counter. The counter increases its counter value by 1 for each time the

separated vertical sync pulse is within the searched window. The count is decreased by 1 when the vertical sync pulse

is not present.

Large (search) window: divider ratio between 488 and 722

This mode is valid for the following conditions:

1. Divider is looking for a new transmitter.

2. Divider ratio found, not within the narrow window limits.

3. Up/down counter value of the divider system operating in the narrow window mode decreases below count 1.

4. Externally setting. This can be reached by loading pin 18 with a resistor of 220 kW to earth or connecting a 3.6 V

diode stabistor between pin 18 and ground.

Narrow window: divider ratio between 522-528 (60 Hz) or 622-628 (50 Hz).

The divider system switches over to this mode when the up/down counter has reached its maximum value of 12 approved

vertical sync pulses. When the divider operates in this mode and a vertical sync pulse is missing within the window the

divider is reset at the end of the window and the counter value is decreased by 1. At a counter value below count 1 the

divider system switches over to the large window mode.

Standard TV-norm

When the up/down counter has reached its maximum value of 12 in the narrow window mode, the information applied to

the up/down counter is changed such that the standard divider ratio value is tested. When the counter has reached a

value of 14 the divider system is changed over to the standard divider ratio mode. In this mode the divider is always reset

at the standard value even if the vertical sync pulse is missing. A missed vertical sync pulse decreases the counter value

by 1. When the counter reaches the value of 10 the divider system is switched over to the large window mode.

The standard TV-norm condition gives maximum protection for video recorders playing tapes with anti-copy guards.

No-TV-transmitter found: (pin 18 < 1.2 V)

In this condition, only noise is present, the divider is rest to count 628. In this way a stable picture display at normal height

is achieved.

Video tape recorders in feature mode

It should be noted that some VTRs operating in the feature modes, such as picture search, generate such

distorted

distortedpictures that the no-TV-transmitter detection circuit can be activated as pin V18 drops below 1.2 V. This would imply a

rolling picture (see Phase detector, sub paragraph d). In general VTR-machines use a re-inserted vertical sync pulse in

the feature mode. Therefore the divider system has been made such that the automatic reset of the divider at count 628

when V18 is below 1.2 V is inhibited when a vertical sync pulse is detected.

The divider system also generates the anti-top-flutter pulse which inhibits the Phase 1 detector during the vertical sync.

pulse. The width of this pulse depends on the divider mode. For the divider mode a the start is generated at the reset of

the divider. In mode b and c the anti-top-flutter pulse starts at the beginning of the first equalizing pulse.

The anti-top-flutter pulse ends at count 8 for 50 Hz and count 10 for 60 Hz. The vertical blanking pulse is also generated

via the divider system. The start is at the reset of the divider while the pulse ends at count 34 (17 lines) for 60 Hz, and at

count 44 (22 lines) for 50 Hz systems. The vertical blanking pulse generated at the sandcastle output pin 17 is made by

adding the anti-top-flutter pulse and the blanking pulse. In this way the vertical blanking pulse starts at the beginning of

the first equalizing pulse when the divider operates in the b or c mode. For generating a vertical linear sawtooth voltage

a capacitor should be connected to pin 3. T

he recommended value is 150 nF to 330 nF (see Fig.1).

he recommended value is 150 nF to 330 nF (see Fig.1).The capacitor is charged via an internal current source starting at the reset of the divider system. The voltage on the

capacitor is monitored by a comparator which is activated also at reset. When the capacitor has reached a voltage value

of 5.85 V for the 50 Hz system or 4.85 V for the 60 Hz system the voltage is kept constant until the charging period ends.

The charge period width is 26 clock pulses. At clock pulse 26 the comparator is switched off and the capacitor is

discharged by an npn transistor current source, the value of which can be set by an external resistor between pin 4 and

ground (pin 9). Pin 4 is connected to a pnp transistor current source which determines the current of the npn current

source at pin 3. The pnp current source on pin 4 is connected to an internal zener diode reference voltage which has a

typical voltage of » 7.5 volts. The recommended operating current range is 10 to 75 mA. The resistance at pin R4 should

be 100 to 770 kW. By using a double current mirror concept the vertical sawtooth pre-correction can be set on the desired

value by means of external components between pin 4 and pin 3, or by connecting the pin 4 resistor to the vertical current

measuring resistor of the vertical output stage. The vertical amplitude is set by the current of pin 4. The vertical feedback

voltage of the output stage has to be applied to pin 2. For the normal amplitude adjustment the values are DC = 1 V and

AC = 0.8 V. Due to the automatic system adaption both values are valid for 50 Hz and 60 Hz.

The low DC voltage value improves the picture bounce behaviour as less parabola compensation is necessary. Even a

fully DC coupled feedback circuit is possible.

Vertical guard

The IC also contains a vertical guard circuit. This circuit monitors the vertical feedback signal on pin 2. When the level

on pin 2 is below 0.35 V or higher than 1.85 V the guard circuit inserts a continuous level of 2.5 V in the sandcastle output

signal of pin 17. This results in the blanking of the picture displayed, thus preventing a burnt-in horizontal line. The guard

levels specified refer to the zener diode reference voltage source level.

Driver output

The driver output is at pin 1, it can deliver a drive current of 1.5 mA at 5 V output. The internal impedance is approximately

170 W. The output pin is also connected to an internal current source with a sink current of 0.25 mA.

Sync separator, phase detector and TV-station identification (pins 5,6,7,8 and 18)

The video input signal is connected to pin 5. The sync separator is designed such that the slicing level is independent of

the amplitude of the sync pulse. The black level is measured and stored in the capacitor at pin 7. The slicing level value

is stored in the capacitor at pin 6. The slicing level value can be chosen by the value of the external resistor between

pins 6 and 7.

Black level detector

A gating signal is used for the black level detector. This signal is composed of an internal horizontal reference pulse with

a duty factor of 50% and the flyback pulse at pin 12. In this way the TV-transmitter identification operates also for all DC

conditions at input pin 5 (no video modulation, plain carrier only).

During the frame interval the slicing level detector is inhibited by a signal which starts with the anti-top flutter pulse and

ends with the reset vertical divider circuit. In this way shift of the slicing level due to the vertical sync signal is reduc

ed

edand separation of the vertical sync pulse is improved.

Noise level detector

An internal noise inverter is activated when the video level at pin 5 decreases below 0.7 V. The IC also embodies a

built-in sync pulse noise level detection circuit. This circuit is directly connected to pin 5 and measures the noise level at

the middle of the horizontal sync pulse. When a signal-to-noise level of 19 dB is detected a counter circuit is activated.

A video input signal is processed as “acceptable noise free” when 12 out of 15 sync pulses have a noise level below

19 dB for two successive frame periods. The sync pulses are processed during a 15 line width gating period generated

by the divider system. The measuring circuit has a built-in noise level hysteresis of approximately 3 dB. When the

“acceptable noise free” condition is found the phase detector of pin 8 is switched to not gated and normal time constant.

When a higher sync pulse noise level is found the phase detector is switched over to slow time constant and gated sync

pulse phase detection.

Phase detector

The phase detector circuit is connected to pin 8. This circuit consists of 3 separate phase detectors which are activated

depending on the voltage of pin 18 and the state of the sync pulse noise detection circuit. For normal and fast time

constants all three phase detectors are activated during the vertical blanking period, this with the exception of the

anti-top-flutter pulse period, and the separated vertical sync-pulse time. As a result, phase jumps in the video signal

related to the video head, take over of video recorders are quickly restored within the vertical blanking period. At the end

of the blanking period the phase director time constant is increased by 1.5 times. In this way there is no requirement for

external VTR time constant switching, and so all station numbers are suitable for signals from VTR, video games or home

computers.

For quick locking of a new TV station starting from a noise only signal condition (normal time constant) a special circuit

is incorporated. A new TV station which is not locked to the horizontal oscillator will result in a voltage decrease below

0.1 V at pin 18. This will activate a frame period counter which switches the phase detector to fast for 3 frame periods

during the vertical scan period.

The horizontal oscillator will now lock to the new TV-station and as a result, the voltage on pin 18 will increase to

approximately 6.5 V. When pin 18 reaches a level of 1.8 V the mute output transistor of pin 13 is switched OFF and the

divider is set to the large window. In general the mute signal is switched OFF within 5 ms (pin C18 = 47 nF) after reception

of a new TV-signal. When the voltage on pin 18 reaches a level of 5 V, usually within 15 ms, the frame counter is switched

OFF and the time constant is switched from fast to normal during the vertical scan period.

If the new TV station is weak, the sync-noise detector is activated. This will result in a change over of pin 18 voltage from

6.5 V to »10 V. When pin 18 exceeds the level of 7.8 V the phase detector is switched to slow time constant and gated

sync pulse condition. The current is also reduced during the vertical blanking period by 1 mA. When desired, most

conditions of the phase detector can also be set by external means in the following way:

a. Fast time constant TV transmitter identification circuit not active, connect pin 18 to earth (pin 9).

b. Fast time constant TV transmitter identification circuit active, connect a resistor of 220 kW between pin 18 and ground.

This condition can also be set by using a 3.6 V stabistor diode instead of a resistor.

c. Slow time constant, (with exception of frame blanking period), connect pin 18 via a resistor of 10 kW to + 12 V, pin 10.

In this condition the transmitter identification circuit is not active.

d. No switching to slow time constant desired (transmitter identification circuit active), connect a 6.8 V zener diode

between pin 18 and ground.

Supply (pins 9, 10 and 16)

The IC ha

s been designed such that the horizontal oscillator and output stage can start operating by application of a very

s been designed such that the horizontal oscillator and output stage can start operating by application of a verylow supply current into pin 16.

The horizontal oscillator starts at a supply current of approximately 4 mA. The horizontal output stage is forced into the

non-conducting stage until the supply current has a typical value of 5 mA. The circuit has been designed so that after

starting the horizontal output function a current drop of » 1 mA is allowed. The starting circuit has the ability to derive the

main supply (pin 10) from the horizontal output stage. The horizontal output signal can also be used as the oscillator

signal for synchronized switched mode power supplies. The maximum allowed starting current is 9.7 mA (Tamb = 25 °C).

The main supply should be connected to pin 10, and pin 9 should be used as ground. When the voltage on pin 10

increases from zero to its final value (typically 12 V) a part of the supply current of the starting circuit is taken from pin 10

via internal diodes, and the voltage on pin 16 will stabilize to a typical value of 9.4 V.

In a stabilized condition (pin V10 > 10 V) the minimum required supply current to pin 16 is » 2.5 mA. All other IC functions

are switched on via the main supply voltage on pin 10. When the voltage on pin 10 reaches a value of » 7 V the horizontal

phase detector circuit is activated and the vertical ramp on pin 3 is started. The second phase detector circuit and burst

pulse circuit are started when the voltage on pin 10 reaches the stabilized voltage value of pin 16 which is typically 9.4 V.

To close the second phase detector loop, a flyback pulse must be applied to pin 12. When no flyback pulse is detected

the duty factor of the horizontal output stage is 50%.

For remote switch-off pin 16 can be connected to ground (via a npn transistor with a series resistor of » 500 W) which

switches off the horizontal output.

Horizontal oscillator, horizontal output transistor, and second phase detector (pins 11, 12, 14 and 15)

The horizontal oscillator is connected to pin 15. The frequency is set by an external RC combination between pin 15 and

ground, pin 9. The open collector horizontal output stage is connected to pin 11. An internal zener diode configuration

limits the open voltage of pin 11 to » 14.5 V.

The horizontal output transistor at pin 11 is blocked until the current into pin 16 reaches a value of » 5 mA.

A higher current results in a horizontal output signal at pin 11, which starts with a duty factor of » 40% HIGH.

The duty factor is set by an internal current-source-loaded npn emitter follower stage connected to pin 14 during starting.

When pin 16

changes over to voltage stabilization the npn emitter follower and current source load at pin 14 are switched

changes over to voltage stabilization the npn emitter follower and current source load at pin 14 are switchedOFF and the second phase detector circuit is activated, provided a horizontal flyback pulse is present at pin 12.

When no flyback pulse is detected at pin 12 the duty factor of the horizontal output stage is set to 50%.

The phase detector circuit at pin 14 compensates for storage time in the horizontal deflection output stage. The horizontal

output pulse duration is 29 ms HIGH for storage times between 1 ms and 17 ms (flyback pulse of 12 ms). A higher storage

time increases the HIGH time. Horizontal picture shift is possible by forcing an external charge or discharge current into

the capacitor at pin 14.

Mute output and 50/60 Hz identification (pin 13)

The collector of an npn transistor is connected to pin 13. When the voltage on pin 18 drops below 1.2 V

(no TV-transmitter) the npn transistor is switched ON.

When the voltage on pin 18 increases to a level of » 1.8 V (new TV-transmitter found) the npn transistor is switched OFF.

Pin 13 has also the possibility for 50/60 Hz identification. This function is available when pin 13 is connected to pin 10

(+ 12 V) via an external pull-up resistor of 10 to 20 kW. When no TV-transmitter is identified the voltage on pin 13 will be

LOW (< 0.5 V). When a TV-transmitter with a divider ratio > 576 (50 Hz) is detected the output voltage of pin 13 is HIGH

(+ 12 V).

When a TV-transmitter with a divider ratio < 576 (60 Hz) is found an internal pnp transistor with its emitter connected to

pin 13 will force this pin output voltage down to » 7.6 V.

Sandcastle output (pin 17)

The sandcastle output pulse generated at pin 17, has three different voltage levels. The highest level, (10.4 V), can be