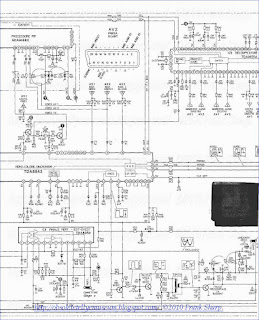

MIVAR 25S5 CHASSIS 1086 STEREO PHILIPS TDA8843 I2C-bus controlled PAL/NTSC/SECAM TV processor:

GENERAL DESCRIPTION:

The various versions of the PHILIPS TDA 884X/5X series are

intended to be applied in PAL, NTSC, PAL/NTSC and

multi-standard television receivers. The N2 version is pin

and application compatible with the N1 version, however,

a new feature has been added which makes the N2 more

attractive. The IF PLL demodulator has been replaced by

an alignment-free IF PLL demodulator with internal VCO

(no tuned circuit required). The setting of the various

frequencies (33.4, 33.9, 38, 38.9, 45,75 and 58.75 MHz)

can be made via the I2C-bus.

Because of this difference the N2 version is compatible

with the N1, however, N1 devices cannot be used in an

optimised N2 application.

Functionally the IC series is split up is 3 categories, viz:

· Versions intended to be used in economy TV receivers

with all basic functions (envelope: S-DIP 56 and QFP

64)

· Versions with additional features like E-W geometry

control, H-V zoom function and YUV interface which are

intended for TV receivers with 110° picture tubes

(envelope: S-DIP 56)

· Versions which have in addition a second RGB input

with saturation control and a second CVBS output

(envelope: QFP 64)

FUNCTIONAL DESCRIPTION

Vision IF amplifier

The IF-amplifier contains 3 ac-coupled control stages with

a total gain control range which is higher then 66 dB. The

sensitivity of the circuit is comparable with that of modern

IF-IC’s.

The video signal is demodulated by means of an

alignment-free PLL carrier regenerator with an internal

VCO. This VCO is calibrated by means of a digital control

circuit which uses the X-tal frequency of the colour

decoder as a reference. The frequency setting for the

various standards (33.4, 33.9, 38, 38.9, 45.75 and 58.75

MHz) is realised via the I2C-bus. To get a good

performance for phase modulated carrier signals the

control speed of the PLL can be increased by means of the

FFI bit.

The AFC output is generated by the digital control circuit of

the IF-PLL demodulator and

can be read via the I2C-bus.

can be read via the I2C-bus.For fast search tuning systems the window of the AFC can

be increased with a factor 3. The setting is realised with the

AFW bit. The AFC data is valid only when the horizontal

PLL is in lock (SL = 1)

Depending on the type the AGC-detector operates on

top-sync level (single standard versions) or on top sync

and top white- level (multi standard versions). The

demodulation polarity is switched via the I2C-bus. The

AGC detector time-constant capacitor is connected

externally. This mainly because of the flexibility of the

application. The time-constant of the AGC system during

positive modulation is rather long to avoid visible variations

of the signal amplitude. To improve the speed of the AGC

system a circuit has been included which detects whether

the AGC detector is activated every frame period. When

during 3 field periods no action is detected the speed of the

system is increased. For signals without peak white

information the system switches automatically to a gated

black level AGC. Because a black level clamp pulse is

required for this way of operation the circuit will only switch

to black level AGC in the internal mode.

The circuits contain a video identification circuit which is

independent of the synchronisation circuit. Therefore

search tuning is possible when the display section of the

receiver is used as a monitor. However, this ident circuit

cannot be made as sensitive as the slower sync ident

circuit (SL) and we recommend to use both ident outputs

to obtain a reliable search system. The ident output is

supplied to the tuning system via the I2C-bus.

The input of the identification circuit is connected to pin 13

(S-DIP 56 devices), the “internal” CVBS input (see Fig.6).

This has the advantage that the ident circuit can also be

made operative when a scrambled signal is received

(descrambler connected between pin 6 (IF video output)

and pin 13). A second advantage is that the ident circuit

can be used when the IF amplifier is not used (e.g. with

built-in satellite tuners).

The video ident circuit can also be used to identify the

selected CBVS or Y/C signal. The switching between the

2 modes can be realised with the VIM bit.

Video switches

The circuits have two CVBS inputs (internal and external

CVBS) and a Y/C input. When the Y/C input is not required

the Y input can be used as third CVBS input. The switch

configuration is given in Fig.6. The selection of the various

sources is made via the I2C-bus.

For the TDA 884X devices the video switch configuration

is identical to the switch of the TDA8374/75 series. So the

circuit has one CVBS output (amplitude of 2 VP-P for the

TDA 884X series) and the I2C-bus control is similar to that

of the TDA 8374/75. For the TDA 885X IC’s the video

switch circuit has a second output (amplitude of 1 VP-P)

which can be set independently of the position of the first

output. The input signal for the decoder is also available on

the CVBS1-output.

Therefore this signal can be used to drive the Teletext

decoder. If S-VHS is selected for one of the outputs the

luminance and chrominance signals are added so that a

CVBS signal is obtained again.

Sound circuit

The sound bandpass and trap filters have to be connected

externally. The filtered intercarrier signal is fed to a limiter

externally. The filtered intercarrier signal is fed to a limitercircuit and is demodulated by means of a PLL

demodulator. This PLL circuit tunes itself automatically to

the incoming carrier signal so that no adjustment is

required.

The volume is controlled via the I2C-bus. The deemphasis

capacitor has to be connected externally. The

non-controlled audio signal can be obtained from this pin

(via a buffer stage).

The FM demodulator can be muted via the I2C-bus. This

function can be used to switch-off the sound during a

channel change so that high output peaks are prevented.

The TDA 8840/41/42/46 contain an Automatic Volume

Levelling (AVL) circuit which automatically stabilises the

audio output signal to a certain level which can be set by

the viewer by means of the volume control. This function

prevents big audio output fluctuations due to variations of

the modulation depth of the transmitter. The AVL function

can be activated via the I2C-bus.

Synchronisation circuit

The sync separator is preceded by a controlled amplifier

which adjusts the sync pulse amplitude to a fixed level.

These pulses are fed to the slicing stage which is operating

at 50% of the amplitude. The separated sync pulses are

fed to the first phase detector and to the coincidence

detector. This coincidence detector is used to detect

whether the line oscillator is synchronised and can also be

used for transmitter identification. This circuit can be made

less sensitive by means of the STM bit. This mode can be

used during search tuning to avoid that the tuning system

will stop at very weak input signals. The first PLL has a

very high statical steepness so that the phase of the

picture is independent of the line frequency.

The horizontal output signal is generated by means of an

oscillator which is running at twice the line frequency. Its

frequency is divided by 2 to lock the first control loop to the

incoming signal. The time-constant of the loop can be

forced by the I2C-bus (fast or slow). If required the IC can

select the time-constant depending

on the noise content of

on the noise content ofthe incoming video signal.

The free-running frequency of the oscillator is determined

by a digital control circuit which is locked to the reference

signal of the colour decoder. When the IC is switched-on

the horizontal output signal is suppressed and the

oscillator is calibrated as soon as all sub-address bytes

have been sent. When the frequency of the oscillator is

correct the horizontal drive signal is switched-on. To obtain

a smooth switching-on and switching-off behaviour of the

horizontal output stage the horizontal output frequency is

doubled during switch-on and switch-off (slow start/stop).

During that time the duty cycle of the output pulse has such

a value that maximum safety is obtained for the output

stage.

To protect the horizontal output transistor

the horizontal

the horizontaldrive is immediately switched off when a power-on-reset is

detected. The drive signal is switched-on again when the

normal switch-on procedure is followed, i.e. all

sub-address bytes must be sent and after calibration the

horizontal drive signal will be released again via the slow

start procedure. When the coincidence detector indicates

an out-of-lock situation the calibration procedure is

repeated. The circuit has a second control loop to generate

the drive pulses for the horizontal driver stage. The

horizontal output is gated with the flyback pulse so that the

horizontal output transistor cannot be switched-on during

the flyback time.

Via the I2C-bus adjustments can be made of the horizontal

and vertical geometry. The vertical sawtooth generator

drives the vertical output drive circuit which has a

differential output current. For the E-W drive a single

ended current output is available. A special feature is the

zoom function for both the horizontal and vertical

deflection and the vertical scroll function which are

available in some versions. When the horizontal scan is

reduced to display 4:3 pictures on a 16:9 picture tube an

accurate video blanking can be switched on to obtain well

defined edges on the screen.

Overvoltage conditions (X-ray protection) can be detected

via the EHT tracking pin. When an overvoltage condition is

detected the horizontal output drive signal will be

switched-off via the slow stop procedure but it is also

possible that the drive is not switched-off and that just a

protection indication is given in the I2C-bus output byte.

The choice is made via the input bit PRD. The IC’s have a

second protection input on the j2 filter capacitor pin. When

this input is activated the drive signal is switched-off

immediately and switched-on again via the slow start

procedure. For this reason this protection input can be

used as “flash protection”.

The drive pulses for the vertical sawtooth generator are

obtained from a vertical countdown circuit. This countdown

circuit has various windows depending on the incoming

signal (50 Hz or 60 Hz and standard or non standard). The

countdown circuit can be forced in various modes by

means of the I2C-bus. During the insertion of RGB signals

the maximum vertical frequency is increased to 72 Hz so

that the circuit can also synchronise on signals with a

higher vertical frequency like VGA. To obtain short

switching times of the countdown circuit during a channel

change the divider can be forced in the search window by

means of the NCIN bit. The vertical deflection can be set

in the de-interlace mode via the I2C bus.

To avoid damage of the picture tube when the vertical

deflection fails the guard output current of the TDA

8350/51 can be supplied to the beam current limiting input.

When a failure is detected the RGB-outputs are blanked

and a bit is set (NDF) in the status byte of the I2C-bus.

When no vertical deflection output stage is connected this

guard circuit will also blank the output signals. This can be

overruled by means of the EVG bit.

Chroma and luminance processing

The circuits contain a chroma bandpass and trap circuit.

The filters are realised by means of gy

rator circuits and

rator circuits andthey are automatically calibrated by comparing the tuning

frequency with the X-tal frequency of the decoder. The

luminance delay line and the delay for the peaking circuit

are also realised by means of gyrator circuits. The centre

frequency of the chroma bandpass filter is switchable via

the I2C-bus so that the performance can be optimised for

“front-end” signals and external CVBS signals. During

SECAM reception the centre frequency of the chroma trap

is reduced to get a better suppression of the SECAM

carrier frequencies. All IC’s have a black stretcher circuit

which corrects the black level for incoming video signals

which have a deviation between the black level and the

blanking level (back porch). The timeconstant for the black

stretcher is realised internally.

The resolution of the peaking control DAC has been

increased to 6 bits. All IC’s have a defeatable coring

function in the peaking circuit. Some of these IC’s have a

YUV interface (see table on page 2) so that picture

improvement IC’s like the TDA 9170 (Contrast

improvement), TDA 9177 (Sharpness improvement) and

TDA 4556/66 (CTI) can be applied. When the CTI IC’s are

applied it is possible to increase the gain of the luminance

channel by means of the GAI bit in subaddress 03 so that

the resulting RGB output signals are not affected.

Colour decoder

Depending on the IC type the colour decoder can decode

PAL, PAL/NTSC or PAL/NTSC/SECAM signals. The

PAL/NTSC decoder contains an alignment-free X-tal

oscillator, a killer circuit and two colour difference

demodulators. The 90° phase shift for the reference signal

is made internally.

The IC’s contain an Automatic Colour Limiting (ACL)

circuit which is switchable via the I2C-bus and which

prevents that oversaturation occurs when signals with a

high chroma-to-burst ratio are received. The ACL circuit is

designed such that it only reduces the chroma signal and

not the burst signal. This has the advantage that the colour

sensitivity is not affected by this function.

The SECAM decoder contains an auto-calibrating PLL

demodulator which has two references, viz: the 4.4 MHz

sub-carrier frequency which is obtained from the X-tal

oscillator which is used to tune the PLL to the desired

free-running frequency and the bandgap reference to

obtain the correct absolute value of the output signal. The

VCO of the PLL is calibrated during each vertical blanking

period, when the IC is in search or SECAM mode.

The frequency of the active X-tal is fed to the Fsc output

(pin 33) and can be used to tune an external comb filter

(e.g. the SAA 4961).

The base-band delay line (TDA 4665 function) is

integrated in the PAL/SECAM IC’s and in the NTSC IC

TDA 8846A. In the latter IC it improves the cross colour

TDA 8846A. In the latter IC it improves the cross colourperformance (chroma comb filter). The demodulated

colour difference signals are internally supplied to the

delay line. The colour difference matrix switches

automatically between PAL/SECAM and NTSC, however,

it is also possible to fix the matrix in the PAL standard.

The “blue stretch” circuit is intended to shift colour near

“white” with sufficient contrast values towards more blue to

obtain a brighter impression of the picture.

Which colour standard the IC’s can decode depends on

the external X-tals. The X-tal to be connected to pin 34

must have a frequency of 3.5 MHz (NTSC-M, PAL-M or

PAL-N) and pin 35 can handle X-tals with a frequency of

4.4 and 3.5 MHz. Because the X-tal frequency is used to

tune the line oscillator the value of the X-tal frequency

must be given to the IC via the I2C-bus. It is also possible

to use the IC in the so called “Tri-norma” mode for South

America. In that case one X-tal must be connected to pin

34 and the other 2 to pin 35. The switching between the 2

latter X-tals must be done externally. This has the

consequence that the search loop of the decoder must be

controlled by the m-computer. To prevent calibration

problems of the horizontal oscillator the external switching

between the 2 X-tals should be carried out when the

oscillator is forced to pin 34. For a reliable calibration of the

horizontal oscillator it is very important that the X-tal

indication bits (XA and XB) are not corrupted. For this

reason the X-tal bits can be read in the output bytes so that

the software can check the I2C-bus transmission.

the software can check the I2C-bus transmission.RGB output circuit and black-current stabilisation

The colour-difference signals are matrixed with the

luminance signal to obtain the RGB-signals. The TDA

884X devices have one (linear) RGB input. This RGB

signal can be controlled on contrast and brightness (like

TDA 8374/75). By means of the IE1 bit the insertion

blanking can be switched on or off. Via the IN1 bit it can be

read whether the insertion pin has a high level or not.

The TDA 885X IC’s have an additional RGB input. This

RGB signal can be controlled on contrast, saturation and

brightness. The insertion blanking of this input can be

switched-off by means of the IE2 bit. Via the IN2 bit it can

be read whether the insertion pin has a high level or not.

The output signal has an amplitude of about 2 volts

black-to-white at nominal input signals and nominal

settings of the controls. To increase the flexibility of the IC

it is possible to insert OSD and/or teletext signals directly

at the RGB outputs. This insertion mode is controlled via

the insertion input (pin 26 in the S-DIP 56- and pin 38 in the

QFP-64 envelope). This blanking action at the RGB

outputs has some delay which must be compensated

externally.

To obtain an accurate biasing of the picture tube a

To obtain an accurate biasing of the picture tube a“Continuous Cathode Calibration” circuit has been

developed. This function is realised by means of a 2-point

black level stabilisation circuit. By inserting 2 test levels for

each gun and comparing the resulting cathode currents

with 2 different reference currents the influence of the

picture tube parameters like the spread in cut-off voltage

can be eliminated. This 2-point stabilisation is based on

the principle that the ratio between the cathode currents is

coupled to the ratio between the drive voltages according

to:

The feedback loop makes the ratio between the cathode

currents Ik1 and Ik2 equal to the ratio between the

reference currents (which are internally fixed) by changing

the (black) level and the amplitude of the RGB output

signals via 2 converging loops. The system operates in

such a way that the black level of the drive signal is

controlled to the cut-off point of the gun so that a very good

controlled to the cut-off point of the gun so that a very goodgrey scale tracking is obtained. The accuracy of the

adjustment of the black level is just dependent on the ratio

of internal currents and these can be made very accurately

in integrated circuits. An additional advantage of the

2-point measurement is that the control system makes the

absolute value of Ik1 and Ik2 identical to the internal

reference currents. Because this adjustment is obtained

by means of an adaption of the gain of the RGB control

stage this control stabilises the gain of the complete

channel (RGB output stage and cathode characteristic).

As a result variations in the gain figures during life will be

compensated by this 2-point loop.

An important property of the 2-point stabilisation is that the

off-set as well as the gain of the RGB path is adjusted by

the feedback loop. Hence the maximum drive voltage for

the cathode is fixed by the relation between the test

pulses, the reference current and the relative gain setting

of the 3 channels. This has the consequence that the drive

level of the CRT cannot be adjusted by adapting the gain

of the RGB output stage. Because different picture tubes

may require different drive levels the typical “cathode drive

level” amplitude can be adjusted by means of an I2C-bus

setting. Dependent on the chosen cathode drive level the

typical gain of the RGB output stages can be fixed taking

into account the drive capability of the RGB outputs (pins

19 to 21). More details about the design will be given in the

application report.

The measurement of the “high” and the “low” current of the

2- point stabilisation circuit is carried out in 2 consecutive

fields. The leakage current is measured in each field. The

maximum allowable leakage current is 100 mA

When the TV receiver is switched-on the RGB output

signals are blanked and the black current loop will try to set

the right picture tube bias levels. Via the AST bit a choice

can be made between automatic start-up or a start-up via

the m-processor. In the automatic mode the RGB drive

signals are switched-on as soon as the black current loop

has been stabilised. In the other mode the BCF bit is set to

has been stabilised. In the other mode the BCF bit is set to0 when the loop is stabilised. The RGB drive can than be

switched-on by setting the AST bit to 0. In the latter mode

some delay can be introduced between the setting of the

BCF bit and the switching of the AST bit so that switch-on

effects can be suppressed.

It is also possible to start-up the devices with a fixed

internal delay (as with the TDA 837X and the TDA884X/5X

N1). This mode is activated with the BCO bit.

The vertical blanking is adapted to the incoming CVBS

signal (50 Hz or 60 Hz). When the flyback time of the

vertical output stage is longer than the 60 Hz blanking time

the blanking can be increased to the same value as that of

the 50 Hz blanking. This can be set by means of the LBM

bit.

For an easy (manual) adjustment of the Vg2 control voltage

the VSD bit is available. When this bit is activated the black

current loop is switched-off, a fixed black level is inserted

at the RGB outputs and the vertical scan is switched-off so

that a horizontal line is displayed on the screen. This line

can be used as indicator for the Vg2 adjustment. Because

of the different requirements for the optimum cut-off

voltage of the picture tube the RGB output level is

adjustable when the VSD bit is activated. The control

range is 2.5 ± 0.7 V and can be controlled via the

brightness control DAC.

It is possible to insert a so called “blue back” back-ground

level when no video is available. This feature can be

activated via the BB bit in the control2 subaddress.

CRT Line Output Stage Operation Principle:

CRT Line Output Stage Operation Principle: I'll examine the operation of the line output stage, whose basic job is to generate a sawtooth current in the line scan coils so that the beams are deflected horizontally across the picture tube's screen. The beams are deflected from the left-hand side to the right-hand side to give the forward line scan: this is followed by a rapid, blanked flyback to the left-hand side ready to trace out the next viewed line. Because of the way in which the flyback is achieved, the line output transformer generates various pulse voltages which are rectified to produce the e.h.t. required by the tube and other supplies. The line output stage is not just any sort of amplifier. The active device, almost always a transistor though valves, thyristors and gate -controlled switches have been used in the past, operates as a switch, the inductive components in the stage being mainly responsible for generating the sawtooth current waveform. Tuning is used to generate and control the flyback. The line drive waveform controls the output transistor's on/off switching and thus determines the timing of the cycle of operations, keeping them phase synchronised with the transmitted picture signal.

Basic Operation

Fig. 1 shows in most basic form the main elements in the line output stage, the active device (transistor) being shown as a switch. When the switch is closed, capacitor C and diode D are shorted out and the 150V supply is connected across coil L. Now it's a basic law of inductance that when a d.c. voltage is connected across a coil the current flowing through the coil builds up linearly from zero. Fig. 2(a) shows this as a positive -going ramp that starts at time t 1 , when the switch is closed. After about 26psec (t2), roughly the time required to deflect the beams from screen centre flows via the large -value capacitor CR, charging the tuning capacitor C with the result that the voltage at its 'upper' plate (the one connected to the coil) rises to a relatively high positive value. When all the energy in coil L has been transferred to capacitor C (time t3) the latter begi

ns

to discharge, passing the energy back the other way to L via CR which,

as far as the circuit's a.c. operation is concerned, can be regarded as a

short-circuit. At time t4 the capacitor has discharged, having

transferred the energy back to the coil. This to-and-fro interchange of

energy between L and C, which from the a.c. point of view are in

parallel (CR representing a short-circuit), is the normal action of a

tuned/resonant/oscillatory circuit. The resonant frequency is determined

by the values of L and C. These are selected so that when time t4 is

reached, i.e. after a half cycle of oscillation, the sawtooth current

has passed through zero to a negative point on the ramp and the beams

have been deflected to the left-hand side of the screen ready for the

next active line scan. To complete the oscillatory cycle (the normal

resonant circuit action) the voltage at the upper plate of capacitor C

would have to move negatively with respect to chassis. It can't do so

because of the presence of diode D, which is called the efficiency diode

- we'll explain that in a minute. When the voltage at the cathode of D

tries to swing negatively it conducts, i.e. switches on, providing a

discharge path for the coil. Once again because of the inductance in the

circuit there's a gradual, linear current discharge, the enegery being

returned to the supply's reservoir capacitor CR. During this discharge,

the beams are deflected back towards the centre of the screen (times t4

to t5). At this point the magnetic flux (energy) in L has been

dissipated. C is still in its discharged state, being shorted out by

diode D. So at time t5, with the beams at screen centre (zero

deflection), the switch has to be closed so that the cycle of operation

can be repeated. The action of diode D has, with the inductance in the

circuit, provided half the scan power while in the process returning the

energy (minus inevitable circuit losses) to the reservoir capacitor. No

wonder it's called the efficiency diode. It's important to note that

the beam flyback period t2 to t4 is governed by the time -constant of L

and C, consisting of one half cycle of oscillation. To achieve a flyback

time of 12μsec the duration of one cycle needs to be 24μsec: so the

resonant frequency of L and C works out at 41.67kHz. Fig. 3 illustrates

the four phases in the operation of the line output stage. Now the

voltage developed across an inductor is propor- tional to the rate of

change of the current flowing through it. Thus the voltage across L is

relatively low during the forward scan period but correspondingly high

during the flyback, when the current flow is faster because of the

circuit resonance. The voltage developed at the positive plate of

capacitor C is shown in Fig. 2(b), typically peaking at 1,200V. Both the

line output transistor and the efficiency diode must be capable of

withstanding this high reverse voltage. As we've seen, the circuit

action is highly efficient as the energy stored in L is returned to the

supply during the first half of the forward scan: indeed with 'perfect'

components there would be no net demand on the power supply at all! In

practice because of the resistance of the inductor and the losses in the

diode, switch and capacitor the circuit takes out a little more than it

puts back, while the practice of loading the transformer with rectifier

circuits to provide power for other sections of the set increases the

stage's current demand. To make up for these losses, the line output

transistor is switched on slightly before instead of at the centre of

the forward scan. In a practical circuit L is the primary winding of the

line output transformer and the deflection coils are connected across

it via a d.c. blocking capacitor, CB, as shown in Fig. 4. This coupling

capacitor also provides scan -correction (often referred to as S

-correction). Why is this required? If a linear deflection current was

used to control the scanning with a relatively flat -faced picture tube

the sides of the picture would be stretched out in comparison with the

centre section. Hence S -correction: the value of the coupling capacitor

is chosen so that it resonantes with the inductance of the scan coils

at about 5kHz. This has the effect of adding a sinewave component to the

sawtooth current, as shown in

ns

to discharge, passing the energy back the other way to L via CR which,

as far as the circuit's a.c. operation is concerned, can be regarded as a

short-circuit. At time t4 the capacitor has discharged, having

transferred the energy back to the coil. This to-and-fro interchange of

energy between L and C, which from the a.c. point of view are in

parallel (CR representing a short-circuit), is the normal action of a

tuned/resonant/oscillatory circuit. The resonant frequency is determined

by the values of L and C. These are selected so that when time t4 is

reached, i.e. after a half cycle of oscillation, the sawtooth current

has passed through zero to a negative point on the ramp and the beams

have been deflected to the left-hand side of the screen ready for the

next active line scan. To complete the oscillatory cycle (the normal

resonant circuit action) the voltage at the upper plate of capacitor C

would have to move negatively with respect to chassis. It can't do so

because of the presence of diode D, which is called the efficiency diode

- we'll explain that in a minute. When the voltage at the cathode of D

tries to swing negatively it conducts, i.e. switches on, providing a

discharge path for the coil. Once again because of the inductance in the

circuit there's a gradual, linear current discharge, the enegery being

returned to the supply's reservoir capacitor CR. During this discharge,

the beams are deflected back towards the centre of the screen (times t4

to t5). At this point the magnetic flux (energy) in L has been

dissipated. C is still in its discharged state, being shorted out by

diode D. So at time t5, with the beams at screen centre (zero

deflection), the switch has to be closed so that the cycle of operation

can be repeated. The action of diode D has, with the inductance in the

circuit, provided half the scan power while in the process returning the

energy (minus inevitable circuit losses) to the reservoir capacitor. No

wonder it's called the efficiency diode. It's important to note that

the beam flyback period t2 to t4 is governed by the time -constant of L

and C, consisting of one half cycle of oscillation. To achieve a flyback

time of 12μsec the duration of one cycle needs to be 24μsec: so the

resonant frequency of L and C works out at 41.67kHz. Fig. 3 illustrates

the four phases in the operation of the line output stage. Now the

voltage developed across an inductor is propor- tional to the rate of

change of the current flowing through it. Thus the voltage across L is

relatively low during the forward scan period but correspondingly high

during the flyback, when the current flow is faster because of the

circuit resonance. The voltage developed at the positive plate of

capacitor C is shown in Fig. 2(b), typically peaking at 1,200V. Both the

line output transistor and the efficiency diode must be capable of

withstanding this high reverse voltage. As we've seen, the circuit

action is highly efficient as the energy stored in L is returned to the

supply during the first half of the forward scan: indeed with 'perfect'

components there would be no net demand on the power supply at all! In

practice because of the resistance of the inductor and the losses in the

diode, switch and capacitor the circuit takes out a little more than it

puts back, while the practice of loading the transformer with rectifier

circuits to provide power for other sections of the set increases the

stage's current demand. To make up for these losses, the line output

transistor is switched on slightly before instead of at the centre of

the forward scan. In a practical circuit L is the primary winding of the

line output transformer and the deflection coils are connected across

it via a d.c. blocking capacitor, CB, as shown in Fig. 4. This coupling

capacitor also provides scan -correction (often referred to as S

-correction). Why is this required? If a linear deflection current was

used to control the scanning with a relatively flat -faced picture tube

the sides of the picture would be stretched out in comparison with the

centre section. Hence S -correction: the value of the coupling capacitor

is chosen so that it resonantes with the inductance of the scan coils

at about 5kHz. This has the effect of adding a sinewave component to the

sawtooth current, as shown in Fig. 5. Thus the deflection power is tailored to suit the length of the

beam paths as the screen is scanned, correcting the horizontal

linearity of the display. At the line scanning frequency the scan coils

behave as an almost perfect inductor, but their small d.c. resistance is

in series with the fixed voltage that should be present across the

coil. It has the effect of introducing an asymmetric sensitivity loss

during the forward scan. To counteract it a further component is added

in series with the scan coils - an inductor with a saturable magnetic

core, biased by a permanent magnet so that its inductance falls as the

scan current increases. The voltage drop across this inductor, which is

known as the linearity coil, varies in the opposite sense to that

produced by the resistance of the coils, thus providing an equal -but

-opposite cancellation effect. In some TV sets the permanent magnet can

be adjusted to trim the linearity correction, though many modern sets

use components with such tight tolerances that a sealed linearity

-correction coil can be used. With some very small -screen sets the

horizontal non -linearity effect is small enough to be ignored.

Fig. 5. Thus the deflection power is tailored to suit the length of the

beam paths as the screen is scanned, correcting the horizontal

linearity of the display. At the line scanning frequency the scan coils

behave as an almost perfect inductor, but their small d.c. resistance is

in series with the fixed voltage that should be present across the

coil. It has the effect of introducing an asymmetric sensitivity loss

during the forward scan. To counteract it a further component is added

in series with the scan coils - an inductor with a saturable magnetic

core, biased by a permanent magnet so that its inductance falls as the

scan current increases. The voltage drop across this inductor, which is

known as the linearity coil, varies in the opposite sense to that

produced by the resistance of the coils, thus providing an equal -but

-opposite cancellation effect. In some TV sets the permanent magnet can

be adjusted to trim the linearity correction, though many modern sets

use components with such tight tolerances that a sealed linearity

-correction coil can be used. With some very small -screen sets the

horizontal non -linearity effect is small enough to be ignored.Practical Line Output Stage

Fig. 6 shows a relatively simple line output stage circuit used with a 90° -deflection tube. Tr5 is the line output transistor, which incorporates the efficiency diode in the same package. The primary winding of the line output trans- former T4 is the section between pins 2 and 10, C95 being the flyback tuning capacitor. Scan coil coupling and S - correction are provided by C94, the line linearity coil L14 being connected in series on the chassis side of the scan current path. L14 is damped by R110 to prevent it ringing when the line flyback pulse occurs - the effect of an undamped linearity coil is velocity modulation of the beams at the beginning of their sweeps, showing up as black -and - white vertical striations at the left-hand side of the screen. C92 is the reservoir capacitor, the h.t. feed being via 8105. 8106 and R109 feed pulses to the second phase -locked loop (APC2) in the sync chip - we dealt with this in last month's instalment. A second pulse feed from the same point goes to the colour decoder chip to provide line blanking, burst gating and PAL switch drive - this particular set doesn't use the sandcastle pulse approach.

Secondary Supplies

So much for the generation and control of the sawtooth scanning current. The rest of the components in this circuit are used to harness the energy in the transformer to provide power supplies for other sections of the receiver. The winding between pins 4 and 8 pulse energises the picture tube's heaters at 6.3V r.m.s. The other supplies make use of the transformer as the heart of a d.c.-to-d.c. converter system, by means of secondary windings that provide pulse feeds to diode/capacitor rectifier circuits. Small -value (0.680) resistors in the 25V and 200V supplies provide surge limiting and protection (by going open -circuit) in the event of a short-circuit in one of these supplies. The most significant supply is obtained from the diode - split winding that starts at pin 9. Although not shown in full detail it consists of several 'cells', each of which consists of an electrically isolated secondary winding, a built-in high - voltage rectifier diode and, as the reservoir capacitor, the carefully contrived capacitance that's present between adjacent, highly -insulated winding layers. These cells are connected in series to form a voltage -multiplier system capable of providing an e.h.t. supply for the tube's final anode of typically 24kV - it may be as high as 30kV in some designs. There's a built-in surge limiter resistor at the output end of the chain of cells. An important part of the e.h.t. multiplier system is the final reservoir capacitor that split chain provides about 8kV to a built-in potential -divider chain that contains two pres

ets:

the one at the top provides the supply for the tube's focus electrode

while the one near the bottom provides its first anode supply of about

800V. The bottom of the diode -split chain (pin 9) is returned to

chassis via a diode/capacitor/resistor network (not shown here). The

voltage developed across this network is proportional to the total beam

current, since this flows from the tube's cathodes via the e.h.t.

connector and the diode -split chain to chassis. Above a certain

threshold the voltage at pin 9 reduces the picture brightness and/or

contrast via the colour decoder/matrixing chip, limiting the beam

current and hence the dissipation in the tube's shadowmask to safe

levels. The winding between pins 10 and 7 of the transformer produces

50-70V pulses that sit on the h.t. voltage present at pin 10. When

rectified by D23 and C100 a 200V supply is provided for the RGB output

stages that drive the tube's cathodes. Secondary winding 4-6 feeds D24

and C99 which provide a 25V supply for the field timebase. In some

designs supplies for the audio output stage and the signal sections of

the receiver are also obtained from the line output transformer: in this

particular chassis they are obtained from the chopper transformer in

the power supply instead. Incidentally there have been one or two

designs, the Ferguson/philco TX10 chassis being a well-known example,

where the e.h.t. is also obtained from the chopper transformer, the line

output transformer then acting mainly as a load for the line output

transistor. In earlier designs a separate diode - capacitor multiplier

unit (tripler) was fed from a single line output transformer overwiding

to provide the e.h.t.

ets:

the one at the top provides the supply for the tube's focus electrode

while the one near the bottom provides its first anode supply of about

800V. The bottom of the diode -split chain (pin 9) is returned to

chassis via a diode/capacitor/resistor network (not shown here). The

voltage developed across this network is proportional to the total beam

current, since this flows from the tube's cathodes via the e.h.t.

connector and the diode -split chain to chassis. Above a certain

threshold the voltage at pin 9 reduces the picture brightness and/or

contrast via the colour decoder/matrixing chip, limiting the beam

current and hence the dissipation in the tube's shadowmask to safe

levels. The winding between pins 10 and 7 of the transformer produces

50-70V pulses that sit on the h.t. voltage present at pin 10. When

rectified by D23 and C100 a 200V supply is provided for the RGB output

stages that drive the tube's cathodes. Secondary winding 4-6 feeds D24

and C99 which provide a 25V supply for the field timebase. In some

designs supplies for the audio output stage and the signal sections of

the receiver are also obtained from the line output transformer: in this

particular chassis they are obtained from the chopper transformer in

the power supply instead. Incidentally there have been one or two

designs, the Ferguson/philco TX10 chassis being a well-known example,

where the e.h.t. is also obtained from the chopper transformer, the line

output transformer then acting mainly as a load for the line output

transistor. In earlier designs a separate diode - capacitor multiplier

unit (tripler) was fed from a single line output transformer overwiding

to provide the e.h.t.Scan Rectification

The e.h.t., focus and 200V supplies d

erived

from the transformer are relatively lightly loaded, i.e. no great

current demand is placed on them. They can therefore be obtained by

rectifying the pulses present during the flyback period (time t2 -t4 in

Fig. 2), which is about twenty per cent of the scan cycle. Where the

current demand is greater, e.g. in a supply for the field timebase or an

audio output stage, the phasing of the relevant transformer winding is

often arranged so that the rectifier diode conducts during the scan

rather than the flyback period. Although the voltage available is much

lower, it's present for a longer period (about eighty per cent of the

scan/duty cycle). As a result the output regulation is much better. The

relatively high peak reverse voltage has to be taken into account in the

rectifier diode's specification.

erived

from the transformer are relatively lightly loaded, i.e. no great

current demand is placed on them. They can therefore be obtained by

rectifying the pulses present during the flyback period (time t2 -t4 in

Fig. 2), which is about twenty per cent of the scan cycle. Where the

current demand is greater, e.g. in a supply for the field timebase or an

audio output stage, the phasing of the relevant transformer winding is

often arranged so that the rectifier diode conducts during the scan

rather than the flyback period. Although the voltage available is much

lower, it's present for a longer period (about eighty per cent of the

scan/duty cycle). As a result the output regulation is much better. The

relatively high peak reverse voltage has to be taken into account in the

rectifier diode's specification.EHT Regulation

The internal impedance of a diode -sp

lit

e.h.t. supply is typically about 1MOhm. Thus with a total beam current

of lmA, present when a bright picture is being displayed on a 22in.

picture tube, the e.h.t. voltage will drop by about 1kV or five per

cent. The result of this is some ballooning, i.e. increase in picture

size. Compensation can be provided by reducing the line scanning power.

Careful choice of the value of the resistor that feeds the line output

transformer - R105 in Fig. 6 - gives automatic compensation in the

horizontal direction, while deriving the supply for the field output

stage from the line output transformer tends to cancel out the

ballooning in the vertical plane. Various 'anti -breathing' arrangements

are used in TV receiver design. Most operate via the diode -modulator

circuit we'll come to shortly. With any line output stage circuit the

picture width and e.h.t. voltage depend on the stage's h.t. supply, so

this must be well regulated and set up correctly. In the circuit shown

in Fig. 6 the h.t. voltage has to be 119V with a 20in. tube and 145V

with a 22in. tube.

lit

e.h.t. supply is typically about 1MOhm. Thus with a total beam current

of lmA, present when a bright picture is being displayed on a 22in.

picture tube, the e.h.t. voltage will drop by about 1kV or five per

cent. The result of this is some ballooning, i.e. increase in picture

size. Compensation can be provided by reducing the line scanning power.

Careful choice of the value of the resistor that feeds the line output

transformer - R105 in Fig. 6 - gives automatic compensation in the

horizontal direction, while deriving the supply for the field output

stage from the line output transformer tends to cancel out the

ballooning in the vertical plane. Various 'anti -breathing' arrangements

are used in TV receiver design. Most operate via the diode -modulator

circuit we'll come to shortly. With any line output stage circuit the

picture width and e.h.t. voltage depend on the stage's h.t. supply, so

this must be well regulated and set up correctly. In the circuit shown

in Fig. 6 the h.t. voltage has to be 119V with a 20in. tube and 145V

with a 22in. tube.Pincushion Distortion

The raster produced on an almost -flat faced picture tube by constant -amplitude scan currents has pincushion distortion at all four sides. This is because of the disparity between the image plane and the screen's profile - . As a general rule the deflection yokes used with modern 90° tubes have built-in correction for both NS (vertical) and EW (horizontal) pincushion distortion while 110° tubes (generally above 22in. screen size) have in -yoke correction for NS distortion but cannot fully compensate for the

pincushion

effect at the sides of the screen. Thus with these the line scan

current has to be amplitude -modulated by a parabolic waveform at field

frequency as shown in Fig. 7. With present-day tube designs a modulation

depth of about seven per cent is required. the peak -to -peak scan

current being typically 4.1A at the top and bottom of the screen and

4.4A towards the centre of the screen, where the deflection power is

greatest. Amplitude modulation of the line scan current can be achieved

by including a saturable -reactance transformer in series with the scan

coils, but this is expensive. You could put a suitably -shaped ripple on

the supply to the line output stage, but the parabola would be

superimposed on any secondary supplies derived from the line output

transformer. The most widely used solution is to employ a diode -modu-

lator circuit, since this gives full control of the raster shape and

scan amplitude while providing a constant load current and flyback time.

pincushion

effect at the sides of the screen. Thus with these the line scan

current has to be amplitude -modulated by a parabolic waveform at field

frequency as shown in Fig. 7. With present-day tube designs a modulation

depth of about seven per cent is required. the peak -to -peak scan

current being typically 4.1A at the top and bottom of the screen and

4.4A towards the centre of the screen, where the deflection power is

greatest. Amplitude modulation of the line scan current can be achieved

by including a saturable -reactance transformer in series with the scan

coils, but this is expensive. You could put a suitably -shaped ripple on

the supply to the line output stage, but the parabola would be

superimposed on any secondary supplies derived from the line output

transformer. The most widely used solution is to employ a diode -modu-

lator circuit, since this gives full control of the raster shape and

scan amplitude while providing a constant load current and flyback time.The Diode Modulator

Fig. 8 shows the essence of a diode -modulator arrange- ment. The efficiency diode is split in two, DI and D2, which perform the same clamping action as before. The flyback tuning capacitor is also split in two, Cl and C2: the upper one tunes the transformer and scan coils (L1) as before while the lower one tunes a bridge coil, L2, via C4 to the same flyback frequency of about 42kHz. C3 is the scan coupling capacitor, which corresponds with CB in Fig. 4. Modulation is achieved by using transistor Tr2, whose conduction governs the scan width, to vary the load across C4. When Tr2 is off, the scan energy is shared between the the two series LC combinations C3/L1 and L2/C4. The charge on C3 and C4 is in the ratio of about 7:1, the scan current being reduced in proportion. When Tr2 is fully conductive, C4 is effectively shorted out and acquires no charge. Thus a greater proportion of the energy is present in C3/L1 and the scan current and picture width are increased. By varying the conduction of Tr2 during the forward scan in a parabolic manner, EW pincushion correction is achieved. The basic picture width can be controlled by varying Tr2's standing bias. Choke L3 and the large -value capacitor

C5

filter the line -frequency energy so that it doesn't reach Tr2. And

because both sections of the load (L 1/C1 and L2/C2) are individually

tuned to the flyback frequency the flyback time, and hence the e.h.t.

and the other line output transformer -derived supplies, remain constant

over the field period despite the line scan current variation. There

are several different versions of the diode -modu- lator arrangement.

Some tube/yoke combinations have a scan -geometry characteristic such

that when the line scan current is modulated by a simple parabolic

waveform as described above the raster has inner pincushion distortion

as shown in Fig. 9.

C5

filter the line -frequency energy so that it doesn't reach Tr2. And

because both sections of the load (L 1/C1 and L2/C2) are individually

tuned to the flyback frequency the flyback time, and hence the e.h.t.

and the other line output transformer -derived supplies, remain constant

over the field period despite the line scan current variation. There

are several different versions of the diode -modu- lator arrangement.

Some tube/yoke combinations have a scan -geometry characteristic such

that when the line scan current is modulated by a simple parabolic

waveform as described above the raster has inner pincushion distortion

as shown in Fig. 9. Because

of this. the EW-correction system also has to modulate the S

-correction. Fig. 10 shows, in skeleton circuit form. how this can be

done. There are two coupling/S-correction capacitors. C3 and C3A. C3 is

the usual S -correction capacitor, but C3A has an increasing influence

as the diode modulator begins to have maximum effect towards the centre

of the screen. Critical choice of the value of C3A ensures that the

inner curved verticals shown in Fig. 9 are straightened out to give a

raster completely free from geometric distortion. Although all diode

modulators work on the same basic principle, in some designs a

transformer is used in place of the bridge coil to give better impedance

matching and balance. Fig. 11 shows such an arrangement, used by Bang

and Olufsen. The EW correction waveform is applied to transformer T6.

whose winding 1-2 takes the place of L2 in Figs. 8 and 10. This circuit

also provides inner -pincushion distortion correction as just described,

the supplementary S - correction capacitor being C36.

Because

of this. the EW-correction system also has to modulate the S

-correction. Fig. 10 shows, in skeleton circuit form. how this can be

done. There are two coupling/S-correction capacitors. C3 and C3A. C3 is

the usual S -correction capacitor, but C3A has an increasing influence

as the diode modulator begins to have maximum effect towards the centre

of the screen. Critical choice of the value of C3A ensures that the

inner curved verticals shown in Fig. 9 are straightened out to give a

raster completely free from geometric distortion. Although all diode

modulators work on the same basic principle, in some designs a

transformer is used in place of the bridge coil to give better impedance

matching and balance. Fig. 11 shows such an arrangement, used by Bang

and Olufsen. The EW correction waveform is applied to transformer T6.

whose winding 1-2 takes the place of L2 in Figs. 8 and 10. This circuit

also provides inner -pincushion distortion correction as just described,

the supplementary S - correction capacitor being C36.Diode Modulator Drive

The parabolic EW drive waveform required is easily obtained by feeding the field -scan sawtooth waveform to a double integrator. By adding a sawtooth component the shape of the parabolic waveform can be tilted in either direction to give keystone -distortion correction if required - this is not generally necessary with modern tube/yoke designs. These EW correction characteristics are adjustable by preset resistors or, in the case of bus -programmable sets, remote control commands to the deflection processor. Very often the EW modulator is used to correct the previously mentioned picture breathing effect: this is done by feeding to the EW modulator's control circuit a voltage that's proportional to beam current.

MIVAR 25S5 CHASSIS 1086 STEREO TEA2261 SWITCH MODE POWER SUPPLY CONTROLLER: MIVAR CS1086.

The control means IP1 provide a soft start for a safe start-up after

switching on the line power. This is accomplished via a resistor R5

charging slowly a capacitor C14 with a high capacitance which provides

the necessary power for the integrated circuit IP1 at pins 15 and 16.

Additionally

the SMPS starts with a low oscillating frequency to avoid a current

build-up in the switching transistor T1. A current build-up can arise

when the energy stored in the primary inductance is not fully

transferred to the secondary side before a new conduction period is

initiated. This will lead to operation in continuous mode and the

switching transistor T1 may leave therefore his safe operating area. To

reduce the oscillating frequency during start-up, the SMPS includes a

resistor R511 and a diode D9 in series which connect the capacitor C26

with a capacitor C12 which is charged by the feed-back winding W2. The

capacitor C12 is not charged up initially when the SMPS is switched on.

Therefore, the diode D9 disconnects capacitor C26 from capacitor C12.

The operating frequency is then fixed by R13 and C26, which is a low

frequency (a few kHz). After a certain time capacitor C12 is charged up

and then D9 will be conducting and an additional current will charge C26

via R511, thus the oscillating frequency increases to its normal

operating frequency (about 22 kHz). This ensures that the SMPS starts

safely in discontinuous mode, i.e. the energy stored in the primary

inductance is always fully transferred to the secondary side before a

new conduction period of transistor T1 is initiated.

The start-up

of this known SMPS is depending on the charge-up time of capacitor C14

via resistor R5, therefore, depending on the voltage value of the AC

mains input voltage. This leads to a quite long start-up time at a low

mains input voltage.

The start-up

of this known SMPS is depending on the charge-up time of capacitor C14

via resistor R5, therefore, depending on the voltage value of the AC

mains input voltage. This leads to a quite long start-up time at a low

mains input voltage.

The invention relates to a switch mode power supply (SMPS) comprising

control means which include an oscillator for generating a pulse width

modulated signal.

It is the object of the invention to provide a SMPS as previously

described having a fast start-up time over a wide input voltage range.

This object is accomplished with a switch mode power supply according to

claim 1. The subclaims relate to preferred embodiments.

According

to the invention, the switch mode power supply comprises a network

which provides in case of a high input voltage a start-up with a low

oscillation frequency only for the start-up time. After start-up, the

oscillation frequency changes to the normal oscillating frequency. In

case of a low input voltage, the network provides a start-up with

essentially the normal oscillation frequency. This can be done without

safety risk for the switching transistor because the operating voltages

are low in this case. Even if a slight current build-up phenomenon

occurs during start-up, the switching transistor stays in the safe

operating area because of the low voltages. The network, therefore,

includes means which change the oscillating frequency only in case of a

high mains input voltage. No soft start is provided in case of a low

mains input voltage. The frequency control of the oscillation frequency

can be done advantageously by frequency control means including a

transistor stage which change in case of a high mains input voltage the

time constant of the oscillator network which determines the oscillation

frequency.

In a special embodiment the network comprises a

transistor used in inverse mode as a switching element. With this

circuit arrangement an additional diode is not necessary. This utilizes

the fact that the maximum collector base breakdown's voltage is

distinctly higher than the maximum emitter base breakdown's voltage. The

SMPS can be used especially for a TV receiver which works in a mains

input voltage range of 90 V to 270 V, in a TV receiver the start-up time

of the picture tube has to be considered additionally.

.POSITIVE AND NEGATIVE CURRENT UP TO

1.2A and – 2A

.LOW START-UP CURRENT

.DIRECT DRIVE OF THE POWER TRANSISTOR

.TWO LEVELS TRANSISTOR CURRENT LIMITATION

.DOUBLE PULSE SUPPRESSION

.SOFT-STARTING

.UNDER AND OVERVOLTAGE LOCK-OUT

.AUTOMATIC STAND-BY MODE RECOGNITION

.LARGE POWER RANGE CAPABILITY IN

STAND-BY (Burst mode)

.INTERNAL PWM SIGNAL GENERATOR

DESCRIPTION

The TEA2260/61 is a monolithic integrated circuit

for the use in primary part of an off-line switching

mode power supply.

All functions required for SMPS control under normal

operating,transient or abnormal conditions are

provided.

The capability of working according to the ”masterslave”

concept, or according to the ”primary regulation”

mode makes the TEA2260/61 very flexible

and easy to use. This is particularly true for TV

receivers where the IC provides an attractive and

low cost solution (no need of stand-by auxiliary

power supply).

GENERAL DESCRIPTION

The TEA2260/61 is an off-line switch mode power

The TEA2260/61 is an off-line switch mode power

supply controller. The synchronization functionand

the specificoperationin stand-bymodemake itwell

adapted to video applications such as TV sets,

VCRs, monitors, etc...

The TEA2260/61 can be used in two types of

architectures :

- Master/slave architecture. In this case, the

TEA2260/61 drives the power transistor according

to the pulse width modulated signals generated

by the secondary located master circuit. A

pulse transformer provides the feedback (see

Figure 1).

- Conventional architecture with linear feedback

signal (feedback sources : optocoupler or transformer

winding) (see Figure 2).

power supply, often realized with a small but costly

50Hz transformer, is no longer necessary. The

burst mode operation of the TEA2260/61 makes

possible the control of very low output power (down

to less than 1W) with the main power transformer.

When used in a master/slave architecture, the

TEA2260/61and also the power transistor turn-off

can be easily synchronized with the line transformer.

The switching noise cannot disturb the

picture in this case.

As an S.M.P.S.controller, the TEA2260/61features

the following functions :

- Power supply start-up (with soft-start)

- PWM generator

- Direct power transistor drive (+1.2A, -2.0A)

- Safety functions : pulse by pulse current limitation,

output power limitation, over and under voltage

lock-out.

S.M.P.S. OPERATING DESCRIPTION

Starting Mode - Stand By Mode

Power for circuit supply is taken from the mains

through a high value resistor before starting. As

long as VCC of the TEA2260/61 is below VCC start,

the quiescent current is very low (typically 0.7mA)

and the electrolytic capacitor across VCC is linearly

charged. When VCC reaches VCC start (typically

10.3V), the circuit starts, generating output pulses

with a soft-starting. Then the SMPS goes into the

stand-bymode and the output voltage is a percentage

of the nominal output voltage (eg. 80%).

For this the TEA2260/61 contains all the functions

required for primary mode regulation : a fixed frequency

oscillator, a voltage reference, an error

amplifier and a pulse width modulator (PWM).

For transmission of low power with a good efficiency

in stand-by, an automatic burst generation

system is used, in order to avoid audible noise.

Normal Mode (secondary regulation)

The normal operating of the TV set is obtained by

sending to the TEA2260/61regulation pulses generated

sending to the TEA2260/61regulation pulses generatedby a regulator located in the secondary side

of the power supply.

This architectureuses the ”Master-slave Concept”,

advantages of which are now well-known especially

the very high efficiency in stand-bymode, and

the accurate regulation in normal mode.

Stand-by mode or normal mode are obtained by

supplying or not the secondary regulator. This can

be ordonneredfor exemple by a microprocessor in

relation with the remote control unit.

Regulation pulses are applied to the TEA2260/61

through a small pulse-transformer to the IN input

(Pin 2). This input is sensitive to positive square

pulses. The typical threshold of this input is 0.85V.

The frequency of pulses coming from the secondary

regulator can be lower or higher than the

frequency of the starting oscillator.

The TEA2260/61has no soft-starting system when

The TEA2260/61has no soft-starting system whenit receives pulses from the secondary. The softstarting

has to be located in the secondary regulator.

Due to the principle of the primary regulation,

pulses generated by the starting system automatically

SMPS increases.

Stand-by Mode - Normal Mode Transition

During the transition there are simultaneously

pulses coming from the primary and secondary

regulators.

These signals are not synchronizedand some care

has to betaken toensure the safety of theswitching

power transistor.

Avery sure and simple way consist in checking the

transformer demagnetization state.

- A primary pulse is taken in account only if the

transformer is demagnetized after a conduction

of the power transistor required by the secondary

regulator.

- A secondary pulse is taken in account only if the

transformer is demagnetized after a conduction

of the power transistor required by the primary

regulator.

With this arrangement the switching safety area of

the power transistor is respected and there is no

risk of transformer magnetization.

The magnetization state of the transformer is

checked by sensing the voltage across a winding

of the transformer (generally the same which supplies

the TEA2261). This is made by connecting a

resistor between this winding and the demagnetization

sensing input of the circuit (Pin 1).

SECURITY FUNCTIONS OF THE TEA2261 (see flow-chart below)

- Undervoltage detection. This protection works

in association with the starting device ”VCC

switch” (see paragraph Starting-mode - standby

mode). If VCC is lower than VCCstop (typically

7.4V) output pulses are inhibited, in order to avoid

wrong operation of the power supply or bad

power transistor drive.

- Overvoltage detection. If VCC exceedsVCCmax

(typically 15.7V) output pulses are inhibited. Restarting

of the power supply is obtained by reducing

VCC below VCCstop.

- Current limitation of the power transistor. The

current is measured by a shunt resistor. Adouble

threshold system is used :

- When the first threshold (VIM1) is reached, the

conduction of the power transistor is stopped

until the end of the period : a new conduction

signal is needed to obtain conduction again.

- Furthermore as long as the first threshold is

reached (it means during several periods), an

external capacitor C2 is charged. When the

voltage across the capacitor reaches VC2 (typically

2.55V) the output is inhibited.This is called

the ”repetitive overload protection”. If the overload

diseappears before VC2 is reached, C2 is

discharged, so transient overloads are tolerated.

- Second current limitation threshold (VIM2).

When this thresholdis reached the output of the

circuit is immediatly inhibited. This protection is

helpfull in case of hard overload for example to

avoid the magnetization of the transformer.

- Restart of the power supply. After stopping due

to VC2, VIM2, VCCMax or VCCstop triggering, restart

of the power supply can be obtained by the

normal operating of the ”VCC switch” but thanks

to an integrted counter, if normal restart cannot

be obtained after three trials, the circuit is definitively

stopped. In this case it is necessary to

reduce VCC below approximately 5V to reset the

circuit. From a practical point of view, it means

that the power supply has to be temporarily disconnected

from any power source to get the

restart.

PHILIPS TDA8358J

Full bridge vertical deflection output circuit in LVDMOS with east-west amplifier

FEATURES

• Few external components required

• High efficiency fully DC coupled vertical bridge output circuit

• Vertical flyback switch with short rise and fall times

• Built-in guard circuit

• Thermal protection circuit

• Improved EMC performance due to differential inputs

• East-west output stage.

GENERAL DESCRIPTION

The TDA8358J is a power circuit for use in 90° and 110° colour deflection systems for 25 to 200 Hz field frequencies, and for 4 : 3 and 16 : 9 picture tubes. The IC contains a vertical deflection output circuit, operating as a high efficiency class G system. The full bridge output circuit allows DC coupling of the deflection coil in combination with single positive supply voltages. The east-west output stage is able to supply the sink current for a diode modulator circuit. The IC is constructed in a Low Voltage DMOS (LVDMOS) process that combines bipolar, CMOS and DMOS devices. DMOS transistors are used in the output stage because of absence of second breakdown.

FUNCTIONAL DESCRIPTION

Vertical output stage

The vertical driver circuit has a bridge configuration. The deflection coil is connected between the complimentary driven output amplifiers. The differential input circuit is voltage driven. The input circuit is specially designed for direct connection to driver circuits delivering a differential signal but it is also suitable for single-ended applications. The output currents of the driver device are converted to voltages by the conversion resistors RCV1 and RCV2 (see Fig.3) connected to pins INA and INB. The differential input voltage is compared with the voltage across the measuring resistor RM, providing internal feedback information. The voltage across RM is proportional with the output current. The relationship between the differential input current and the output current is defined by: 2 × Ii(dif)(p-p) × RCV = Io(p-p) × RM The output current should measure 0.5 to 3.2 A (p-p) and is determined by the value of RM and RCV. The allowable input voltage range is 100 mV to 1.6 V for each input. The formula given does not include internal bondwire resistances. Depending on the value of RM and the internal bondwire resistance (typical value 50 mΩ) the actual value of the current in the deflection coil will be about 5% lower than calculated.

Flyback supply

The flyback voltage is determined by the flyback supply voltage VFB. The principle of two supply voltages (class G) allows to use an optimum supply voltage VP for scan and an optimum flyback supply voltage VFB for flyback, thus very high efficiency is achieved. The available flyback output voltage across the coil is almost equal to VFB, due to the absence of a coupling capacitor which is not required in a bridge configuration. The very short rise and fall times of the flyback switch are determined mainly by the slew-rate value of more than 300 V/μs.

Protection

The output circuit contains protection circuits for:

• Too high die temperature

• Overvoltage of output A.

Guard circuit

A guard circuit with output pin GUARD is provided. The guard circuit generates a HIGH-level during the flyback period. The guard circuit is also activated for one of the following conditions: • During thermal protection (Tj ≈ 170 °C) • During an open-loop condition. The guard signal can be used for blanking the picture tube and signalling fault conditions. The vertical synchronization pulses of the guard signal can be used by an On Screen Display (OSD) microcontroller.

Damping resistor compensation

HF loop stability is achieved by connecting a damping resistor RD1 (see Fig.4) across the deflection coil. The current values in RD1 during scan and flyback are significantly different. Both the resistor current and the deflection coil current flow into measuring resistor RM, resulting in a too low deflection coil current at the start of the scan. The difference in the damping resistor current values during scan and flyback have to be externally compensated in order to achieve a short settling time. For that purpose a compensation resistor RCMP is connected between pins OUTA and COMP. The value of RCMP is calculated by: ( VFB – Vloss ( FB ) – VP ) × R D1 × ( RS + 300) RCMP = ------------------------------------------------------------------------------------------------------------- ( V FB – Vloss ( FB ) – I coil (peak ) × Rcoil) × RM where: • Rcoil is the coil resistance • Vloss(FB) is the voltage loss between pins VFB and OUTA at flyback.

East-west amplifier

The east-west amplifier is a current driver sinking the current of a diode modulator circuit. A feedback resistor REWF (see Fig.4) has to be connected between the input and output of the inverting east-west amplifier in order to convert the east-west correction input current into an output voltage. The output voltage of the east-west circuit at pin OUTEW is given by: Vo ≈ Ii × REWF + Vi The maximum output voltage is Vo(max) = 68 V, while the maximum output current of the circuit is Io(max) = 750 mA.

Power dissipation calculation for the east-west stage

In general the shape of the east-west output wave form is a parabola. The output voltage will be higher at the beginning and end of the vertical scan compared to the voltage at the scan middle, while the output current will be higher at the scan middle. This results in an almost uniform power dissipation distribution during scan. Therefore the power dissipation can be calculated by multiplying the average values of the output voltage and the output current of pin OUTEW. When verifying the dissipation also the start-up and stop dissipation should be taken into account. Power dissipation during start-up can be 3 to 5 times higher than during normal operation.

Heatsink calculation

The value of the heatsink can be calculated in a standard way with a method based on average temperatures. The required thermal resistance of the heatsink is determined by the maximum die temperature of 150 °C. In general we recommend to design for an average die temperature not exceeding 130 °C. It should be noted that the heatsink thermal resistance Rth(h-a) found by performing a standard calculation will be lower then normally found for a vertical deflection stand alone device, due to the contribution of the EW power dissipation to this value.

The Audio / Sound Processing is based on TDA9870A (PHILIPS)

FEATURES

1.1

Demodulator and decoder section

• Sound IF (SIF) input switch e.g. to select between

terrestrial TV SIF and SAT SIF sources

• SIF AGC with 24 dB control range

• SIF 8-bit Analog-to-Digital Converter (ADC)

• Two-carrier multistandard FM demodulation (B/G, D/K

and M standard)

• Decoding for three analog multi-channel systems (A2,

A2+ and A2*) and satellite sound

• Programmable identification (B/G, D/K and M standard)

and different identification times.

1.2

DSP section

• Digital crossbar switch for all digital signal sources and

destinations

• Control of volume, balance, contour, bass, treble,

pseudo stereo, spatial, bass boost and soft-mute

• Plop-free volume control

• Automatic Volume Level (AVL) control

• Adaptive de-emphasis for satellite

• Programmable beeper

• Monitor selection for FM/AM DC values and signals,

with peak detection option

• I2S-bus interface for a feature extension (e.g. Dolby

surround) with matrix, level adjust and mute.

1.3

Analog audio section

• Analog crossbar switch with inputs for mono and stereo

(also applicable as SCART 3 input), SCART 1

input/output, SCART 2 input/output and line output

• User defined full-level/−3 dB scaling for SCART outputs

• Output selection of mono, stereo, dual A/B, dual A or

dual B

• 20 kHz bandwidth for SCART-to-SCART copies

• Standby mode with functionality for SCART copies

• Dual audio Digital-to-Analog Converter (DAC) from DSP

to analog crossbar switch, bandwidth of 15 kHz

• Dual audio ADC from analog inputs to DSP

• Two dual audio DACs for loudspeaker (Main) and

headphone (Auxiliary) outputs; also applicable for

L, R, C and S in the Dolby Pro Logic mode with feature

extension.

2

GENERAL DESCRIPTION

The TDA9870A is a single-chip Digital TV Sound Processor (DTVSP) for analog multi-channel sound systems in TV sets and satellite receivers.

2.1

Supported standards