56613500.00 rgb ampl.

TELEFUNKEN (THOMSON) PALCOLOR SP212 STEREO CHASSIS 418 IS A THOMSON Chassis IKC2 stereo with a 90 ° CRT TUBE AND TELETEXT AFTER ADDED UNIT IN 1993.

This chassis was with small variants also used in brands and models:

BRANDT 36289B, 36291T, 42232T, 44231, 51203T, 55280P, 55281S, 63258T, 63281S, VCA40F

FERGUSON 41P3, A36F, A51F

NORDMENDE 36A-GALAXY, 40IMC, 40IMCVT, F19, F20

SABA 36C41, 36C904, 36T905, 55ES955, 63PL945, 70E991, M3702, T6345VT

TELEFUNKEN MP142, MP175, MP202, MP202S, MP211, MP215, MR212S, P320C, P330M, P331M, P350NV, S238, SM214, SN252

THOMSON 36201, 36210T, 36231T, 36241T, 36289T, 36291TB, 36C11, 36C41, 36C904, 36M907, 36ML10, 36ML11, 36MP11, 36MPS45, 36MPS46, 36MSE41, 36T905, 40231T, 40M901, 40MPS45, 40MSE41, 40MV11, 40MV16, 42210T, 42232T, 42250T, 42MPS45, 42MPS46, 44231PL, 44232T, 44M920, 44ML10, 44MP21, 44MPS41, 44MSE41, 44MV11, 44MV11S, 44MV22, 51203T, 51233T, 51M932, 51ML11, 51MPS45, 51MPS46, 51MSE41, 55251T, 55254T, 55256T, 55260PL, 55261T, 55265ST, 55280PLST, 55281T, 55292ST, 55AP11, 55DP21, 55ES955, 55FKC22, 55FPS30, 55FPS31, 55M940, 55M942, 55ML10, 55ML11, 55MLL0, 55MP11, 55MP45, 55MPS27, 55MPS28, 55MPS29, 55MS11TX, 55MV11, 55MV21, 55MV21TX, 55MXP43, 55MXP44, 63252T, 63258T, 63261T, 63281ST, 63283ST, 63DP21, 63ES966, 63M964, 63PS27, 63PS28, 70284ST, 70DP28, 70ES991, 70PS28, 7112, 7132, 7138, 72DP21, 7332, 7338, 8138, 8232, 8238, 8328, 8338, 8358, 8428, 8448, 8578, A5501, F3706, M3701, M3702, M3705, M3705S, M4006, M4506, M5105, M5105S, M5505, M5506, M5522, M5523, MP140, MP141, MP142, MP142S, MP155, MP162, MP162S, MP175, MP202, MP211, MP213, MP215, MR143, MR212, MR212S, SM214, TF5557, TF5571, TF5573, TF6353, TF6357, TF7253, TF7257, TS5125, TS5171, TS5575

WALTHAM TS3625PSN, TS3659PSN

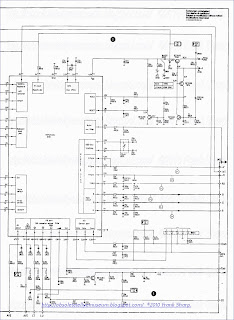

TELEFUNKEN (THOMSON) PALCOLOR SP212 STEREO CHASSIS 418 (THOMSON IKC-2) Power supply with protection circuits This chassis is equipped with a line-frequency synchronized power supply with secondary regulation and included stand-by power supply. by power supply is used. When the mains switching transistor is switched on, energy is supplied via the bridge rectifier. transistor is switched through, and this energy is temporarily stored in the stored in the mains isolating transformer. During the blocking phase of the switch energy reaches the consumers on the secondary side via rectifier diodes. consumers. Special features of this concept:

-

Low weight and volume.

-

No separate stand-by transformer required.

-

Voltage constancy (changes smaller than 2%).

-

Multiple stabilized output voltages.

-

Low sieve media consumption.

-

Galvanic isolation from the mains.

-

Low power consumption in stand-by mode (approx. 6 W).

-

Control range from 180 U to 264 V.

(figure 1)

.The block diagram shows the function of the switching power supply both in stand-by mode and in operating mode. To be able to switch on the device remotely, the power supply for the function of the IR preamplifier and microcomputer must be guaranteed. In order to cover this small power requirement, the flyback converter operates in so-called burst mode. Here, pulse packets control the base of the TP29 transistor, which have different widths and frequencies depending on the mains voltage. These control pulses are generated by the standby regulator together with the standby oscillator. The stand-by regulator generates a sawtooth voltage whose amplitude and frequency depend on the mains voltage and the load on the secondary side. In order to control the power demand in the LP36 transformer, the stand-by regulator is regulated from the auxiliary winding (terminals 9/10). The sawtooth voltage from the regulator serves as the supply voltage for the oscillator and determines the burst frequency and burst width with its frequency. The oscillator oscillates sawtooth with a frequency of approx. 18 kHz. These pulses (G 7) are fed to the driver, which in turn drives the base of the switching transistor TP29 after current amplification. When switching from stand-by to normal operation, the control circuit increases the amplitude of the sawtooth and thus tries to compensate for the change in load until the control of the driver is taken over by pulses generated on the secondary side via LP42.

The stand-by regulator and the oscillator are now controlled by the voltage at transformer LP36, terminal 10, and the control voltage out of operation set. The generation of the line-frequency takeover pulses begins, after the horizontal deflection stage has operated and has supplied the quent-sawtooth-shaped signal "Ba" into the pulse generator. This, together with the system voltage "Usyst" and the voltage U2, 15 V, determines the pulse width of the takeover pulses (H 8). They enter the driver circuit via TP69, LP42 and trigger the the stand-by drive signal. Protection circuits In the event of the collector current of the switching transistor TP29 rising too high, the switching transistor TP29, the voltage drop across the RP32/RP34 activates the primary protection circuit TP18, TP19. 19. transistor TP29 is now no longer triggered. In case of over overvoltage or overload of the 13V busbar, U5, positive voltage is positive voltage enters the pulse generator via the protective circuit input "SP". pulse generator. This provides the supply of the line-frequency control signal for the drive signal for the driver. The power supply in stand-by mode. Power supply unit function description Stand-by mode After start-up of the unit by the mains switch the bridge rectifier DP01...DP04 supplies a voltage of 300 V via winding 2-7 of the transformer LP36, a voltage of 300 V to the coliector of the TP29. For the power supply of the small signal transistors in the primary power supply the bridge rectifier diode DP01 serves as the start-up voltage. diode DP01 serves as the starting voltage. It is fed via the RP06, RP36, RP35 into the filter capacitors CP07 and CP28. Stand-by rectification and oscillator While the transistors TP02, TP03 are still disabled, the charge current generates RP03, RP37 in CP08 generates a sawtooth shaped increase of the oscillator operating voltage. of the oscillator operating voltage at RP09. When the voltage reaches the voltage reaches 2.5 Vpp, TP09 switches via the voltage divider RP08, RP37 in CP08. voltage divider RP08, RP12 is

switched through for the first time. This also makes TP12 conducts, which in turn keeps TP09 in a conductive state until CP09 has discharged. CP09 thus shifts its potential difference steeply potential difference, because DP13 prevents rapid discharge. The negative voltage peaks now generated via CP09 reach DP14 and block TP09. DP14 and block TP13, which was previously blocked by the start-up voltage via RP06, RP13. voltage via RP06, RP13, which was previously in an idle state. After CP09 has discharged via the transistors TP09, TP12, they are again and the charging process of CP09 starts again. The operating state set with RP08, RP12 changes with the oscilla- supply voltage at RP09 and thus also shifts the switching point of TP09, TP12. switching point of TP09, TP12.

switched through for the first time. This also makes TP12 conducts, which in turn keeps TP09 in a conductive state until CP09 has discharged. CP09 thus shifts its potential difference steeply potential difference, because DP13 prevents rapid discharge. The negative voltage peaks now generated via CP09 reach DP14 and block TP09. DP14 and block TP13, which was previously blocked by the start-up voltage via RP06, RP13. voltage via RP06, RP13, which was previously in an idle state. After CP09 has discharged via the transistors TP09, TP12, they are again and the charging process of CP09 starts again. The operating state set with RP08, RP12 changes with the oscilla- supply voltage at RP09 and thus also shifts the switching point of TP09, TP12. switching point of TP09, TP12. The frequency of the oscillator operating with TP09, TP12 is primarily determined by the sawtooth voltage of the oscillator at Measure point (G 4) and the time constant element RP09, CP09 be determined. It is at approx. 18 kHz. The standby regulator, consisting of consisting of TP03, TP02 draws from the mains isolating transformer LP36, connection 10, via DP30, RP38, CP30, RP07 and DP20. ning voltage. If TP02 is switched through by the rising current via RP02, then TP03 TP03 also switches through and draws the supply voltage of the oscillator. voltage of the oscillator down to 0.7 V with a steep edge. This causes a fast discharge of the CP08 via TP03, TP02. When 0.7 V is reached, both transistors are blocked and CP08 can be charged again via RP03, RP37. A new sawtooth new sawtooth is created, which, as described before, serves the oscillator as a working voltage for the oscillator. The frequency of the sawtooth is approx. 170 Hz. Driver and output stage circuit The transistor TP13 is driven by the output signal of the oscillator for for the conduction time of the switching transistor TP29 and switched through for the switched through for the blocking phase. TP13 controls the push-pull emitter follower. follower. A bootstrap circuit consisting of DP18, CP14 increases the efficiency of this circuit. The push-pull emitter The push-pull emitter follower, consisting of TP16, TP17, supplies the base current for TP 29. During the conduction phase, TP16 is switched through and TP17 is disabled. is blocked. During the blocking phase of TP29, TP16 is blocked and TP17 is conductive. The positive base current of TP29 charges CP24. The charging voltage is limited to 2.1 V by the diodes DP24, DP26, DP27. After TP17, CP24 generates a negative reverse voltage for the base of TP29 for the base of TP29. The coil LP 28 causes the base current in TP29 to increase according to an e function, thereby reducing its power dissipation. At the turn-off moment, LP28 rapidly withdraws electrons from the the base zone of TP29 and thus also reduces the dissipation. stance. A further contribution to the reduction of the shutdown losses is made by the attenuator CP29, DP31, RP33, RP 31. By recharging CP29, the collector is CP29 reduces the collector voltage rise and thus the power peak. power peak is reduced. If TP29 is connected through, a sawtooth current flows, starting from the bridge rectifier and CP06, a sawtooth-shaped increasing current flows through the storage inductance in the transformer LP. storage inductance in transformer LP36 (terminals 2/7), TP29, RP32, RP34 to ground.

Afterwards TP29 is blocked again. The collector voltage TP29 results from the sum of the DC voltage of approx. 300 V and the voltage induced by the secondary current flow. induced by the secondary current flow. In this phase, the energy is transferred from the from the primary to the secondary side of the mains isolating transformer LP36. tor LP36. Here, after rectification via DP50, DP65 and DP63, the reduced stand-by operating voltages are available. Power supply in full load operation In full load operation, the switching power supply is supplied by the line output stage line frequency via the line "Ba", CP57, RP57 and TP54. controlled. In order to reduce the collector current of the switching transistor TP29 at the switching transistor TP29 in case of a sudden full load (switching on the device from stand-by!). a soft start is performed first. This is controlled by TP 53, DP56, CP55 and TP54. When switching over from stand-by to full load operation, the emitter-collector path of the TP53 is low impedance the emitter-collector path of the TP53 is low impedance. Without CP55 there would immediately be a 5V voltage at the emitter of TP54 and TP 54 would immediately supply line impulses at the collector with maximum pulse width. Due to the charging time constant of CP55 the voltage rises only slowly in a sawtooth fashion to 5V and TP54 delivers line pulses with slowly increasing pulse width. The secu dary operating voltages Ul, U2, U2', U5, U3 and Us assume their setpoints. CP55 charges to 13V via RP59 and disables DP56. DP58 ensures a fast discharge of CP 55 when switching back to stand-by mode. TP53 regulates, damped by CP54, depending on the system voltage. CP54, depending on the system voltage, regulates the emitter of TP 54. This emitter is determined by a line-frequency sawtooth-shaped base- and a load-dependent regulated DC voltage at the emitter. the pulse width of the control signals for the switching transistor TP29. TP69 amplifies the pulses from TP54 and supplies them to the pulse transformer via the pulse transformer LP42 to the base of TPl3. The further signal processing when DP14 is disabled is the same as in the stand-by by mode and already explained. With PP52 the required system voltage {depending on the screen size) is set at the multipoint N 4. U 3 supplies a 7V operating voltage for the teletext decoder. However, this power rail is only released when the horizontal deflection stage is working and from there the voltage U5, 13 V, is available. It ignites via RP66 the thyristor TP 66, which now takes over the rectification of the pulses from LP36. Protection circuits Overcurrent protection circuit for TP29 If the collector current in TP29 rises above the maximum permissible value, then the voltage drop across the two reference resistors resistors RP32, RP34, so that the transistors TP18, LP36 and LP36, which are connected as thyristors transistors TP18, TP19 switch through. Via DP19 and the transistor TP19, the control pulses intended for the push-pull driver are driver are short-circuited to ground. A new start of the power supply is only possible when the capacitors CP28, CP30 and CP28, CP30 and CP07 have discharged. To do this, the unit must be disconnected from the mains for approx. three seconds. This protection circuit can be activated, for example, in the case of the following fault possibilities: Short circuit of DP50, DP63, DP65, LP36, TL19, DL13, LL05. The stand-by LED display remains dark or goes out dark or goes out within approx. 3 seconds. Mains voltage boost In case that pulse peaks are superimposed on the 220V mains voltage, they are are superimposed on the 220V mains voltage, they reach the base of TP19 via CP10, RP10 and activate the protection circuit through TP19, TP18. The stand-by LED goes out immediately.

Overcurrent protection circuit for the horizontal deflection stage In the event of a short-circuit in the horizontal deflection  section the pulses at transformer LP36, terminal 10. CP30 discharges to such an extent that the transistors TP02, TP03 lock and are no longer switched. This causes CP08 via RP37, RP35 and RP36 to approx. 17V. This voltage can be a current into the base of TP12 via RP27, DP21, RP30. This switches through and prevents the standby oscillator from starting. by oscillator. Since TP29 is not affected by the horizontal deflection stage nor by the stand-by oscillator. from the stand-by oscillator, the complete power supply is out of power supply is out of operation. Overvoltage protection circuit Overvoltage is caused either by a defect of the vertical deflection or by a faulty regulator circuit in the secondary power supply. secondary power supply. In the event of a malfunction, the protection circuit described in chapter 2. SP", DP57, RP57 supplies a high level to the base of the TP54. the base of the TP54. This locks and thus no longer supplies a line- frequent control signal. The power supply now operates in the stand-by node. When the protection circuit is activated, the stand-by LED lights up constantly. steadily. Overcurrent protection for the AF output stages In case of a short circuit of Us, 28V, the diodes DP61, DP62 will also the voltage U2, 15V, is pulled to low level. The microcomputer IR 01 and the multifunction processor IV01 lack the operating voltage. voltage. The deflection stages are out of operation, because the control signal is missing. gnal is missing. Due to the load on the LP36, the stand-by regulator via regulator via DP20 is missing the control signal. At the breakpoint "G 4" the voltage rises the voltage rises to approx. 17V, DP21 becomes conductive and disables the stand-by oscillator. The power supply is switched off.

section the pulses at transformer LP36, terminal 10. CP30 discharges to such an extent that the transistors TP02, TP03 lock and are no longer switched. This causes CP08 via RP37, RP35 and RP36 to approx. 17V. This voltage can be a current into the base of TP12 via RP27, DP21, RP30. This switches through and prevents the standby oscillator from starting. by oscillator. Since TP29 is not affected by the horizontal deflection stage nor by the stand-by oscillator. from the stand-by oscillator, the complete power supply is out of power supply is out of operation. Overvoltage protection circuit Overvoltage is caused either by a defect of the vertical deflection or by a faulty regulator circuit in the secondary power supply. secondary power supply. In the event of a malfunction, the protection circuit described in chapter 2. SP", DP57, RP57 supplies a high level to the base of the TP54. the base of the TP54. This locks and thus no longer supplies a line- frequent control signal. The power supply now operates in the stand-by node. When the protection circuit is activated, the stand-by LED lights up constantly. steadily. Overcurrent protection for the AF output stages In case of a short circuit of Us, 28V, the diodes DP61, DP62 will also the voltage U2, 15V, is pulled to low level. The microcomputer IR 01 and the multifunction processor IV01 lack the operating voltage. voltage. The deflection stages are out of operation, because the control signal is missing. gnal is missing. Due to the load on the LP36, the stand-by regulator via regulator via DP20 is missing the control signal. At the breakpoint "G 4" the voltage rises the voltage rises to approx. 17V, DP21 becomes conductive and disables the stand-by oscillator. The power supply is switched off.

TELEFUNKEN (THOMSON) PALCOLOR SP212 STEREO CHASSIS 418 (THOMSON IKC-2) IR remote control

TELEFUNKEN (THOMSON) PALCOLOR SP212 STEREO CHASSIS 418 (THOMSON IKC-2) IR remote control

In this device series a remote control concept is used, which is characterized by service-friendliness and operational reliability. operational reliability. Characteristics:

-

IR remote control for 64 commands

-

Command output by 11-bit data words

-

"Toggle-bits" for unique command recognition

-

Clock oscillator with 400kHz

-

Particularly low power consumption (active approx. 2mA,

stand-by approx. 2nA)

-

Wide supply voltage range (2...6V)

-

Low power, "flashed", pulse transmission The whole electronic of the IR remote control is composed of only a few few components, which guarantees a high operational reliability. is guaranteed. A mechanical key matrix supplements the electronic circuitry. In idle state, the driver outputs pin 13...19 of the IC01 with their "Open-drain" outputs are at low level. The "pull- up" sensor inputs, on the other hand, are on High level (pin 2-9). Pressing a key on the 8 x 8 matrix sets a sensor input to low and sensor input is set to low and a polling cycle is started. During the key matrix scan only one driver output is switched low. driver output is switched to low impedance. If the IC detects the actuation of a key, the oscillator starts to oscillate. oscillator starts to oscillate.

The oscillator mainly consists of an inverter inverter, which is extremely fed back with a ceramic oscillator. is. Cl and C2 ensure a short oscillation time over a wide supply voltage range. wide supply voltage range. The oscillator signal is a divider, whose output signal clocks the downstream counter. downstream counter. The respective counter reading is decoded, fed to the driver stage and is available at the outputs pin 13 to 19 for the for

interrogation of the key matrix. A signal detected in the sensor decoder (Pin 2 to 9) is taken over into the data memory. memory. This data is fed via a data multiplexer to the modulation counter, which uses the counter, which generates an 11-bit data word in pulse spacing modulation. bit data word, which, via an amplifier decoupled, which is decoupled via an amplifier and available at the output, pin 1. Figure 2 shows the 11-bit data word. The word interval is 121 ms. Tl and TO are toggle bits. With the toggle bits change, i.e. a new command is only accepted by the receiver when the a new command is only accepted by the receiver, if the new toggle bit differs from the old one. If the transmission path (e.g. a person passes between the IR transmitter and receiver diodes), the toggle bits diode), the state of the toggle bits will not change. change. From this the receiver recognizes that there is no renewed key actuation. key is not pressed again. The user will notice this interlocking especially during teletext operation. After output of the toggle bits, which also contain the reference time for the receiver, S2, S1 and time for the receiver, the data output is continued with S2, S1 and S0 as the address. address the data output is continued. The address is set to 3 x High. The remaining 6 data bits are used for command control. The 11-bit data word runs through IC1 at pin 1 and reaches the base of the output stage transistors Tl, R 2 to the base of the output stage transistors Tl, T2. If these are are controlled, a current of approx. 1A flows from the electrolytic capacitor C3 of approx. 1A flows through the IR transmitting diodes and the transistors to ground. ground. During the pulse pauses, C3 is recharged via the decoupling resistor R5. gresistor R5. The transmit frequency is set by the IR transmit diodes to 950 nm. by the IR transmitting diodes. The range of the transmission system is approx. 15m.

interrogation of the key matrix. A signal detected in the sensor decoder (Pin 2 to 9) is taken over into the data memory. memory. This data is fed via a data multiplexer to the modulation counter, which uses the counter, which generates an 11-bit data word in pulse spacing modulation. bit data word, which, via an amplifier decoupled, which is decoupled via an amplifier and available at the output, pin 1. Figure 2 shows the 11-bit data word. The word interval is 121 ms. Tl and TO are toggle bits. With the toggle bits change, i.e. a new command is only accepted by the receiver when the a new command is only accepted by the receiver, if the new toggle bit differs from the old one. If the transmission path (e.g. a person passes between the IR transmitter and receiver diodes), the toggle bits diode), the state of the toggle bits will not change. change. From this the receiver recognizes that there is no renewed key actuation. key is not pressed again. The user will notice this interlocking especially during teletext operation. After output of the toggle bits, which also contain the reference time for the receiver, S2, S1 and time for the receiver, the data output is continued with S2, S1 and S0 as the address. address the data output is continued. The address is set to 3 x High. The remaining 6 data bits are used for command control. The 11-bit data word runs through IC1 at pin 1 and reaches the base of the output stage transistors Tl, R 2 to the base of the output stage transistors Tl, T2. If these are are controlled, a current of approx. 1A flows from the electrolytic capacitor C3 of approx. 1A flows through the IR transmitting diodes and the transistors to ground. ground. During the pulse pauses, C3 is recharged via the decoupling resistor R5. gresistor R5. The transmit frequency is set by the IR transmit diodes to 950 nm. by the IR transmitting diodes. The range of the transmission system is approx. 15m.TELEFUNKEN (THOMSON) PALCOLOR SP212 STEREO CHASSIS 418 (THOMSON IKC-2) IR preamplifier

The IR preamplifier is used to process the received IR signals. signals. The output of the preamplifier is directly connected with the "interrupt" of the microprocessor, which is responsible for the logical evaluation of the incoming pulses. The circuit is designed interference signals are suppressed to a large extent. Special features: - Functionality even in direct sunlight. - Optimum suppression of interfering transmitters, such as fluorescent lamps, IR sound transmission and dimmed incandescent lamps. The receiving diode DA01 converts the incoming infrared impulses into an electrical an electrical quantity. Its internal resistance is determined by the incident light. In darkness, this value is in the megaOhm range in darkness, while in sunlight it is only a few kiloOhm in sunlight. To ensure that the operating point of DA01 is optimal over the entire here TA01 is interposed as a variable working resistor. connected. The control stage is designed in such a way that it only responds to DC or low-frequency signals. CA01 couples the AC voltage component to the downstream three-stage bandpass amplifier with TA03, TA07 and TA08. Their emitter circuitry has low-pass characteristics and sets the lower cutoff frequency to approx. 6kHz. Thus the low lying signal components are suppressed. The emitter resistors RA07, RA08 and RA11 are used for operating point stabilization. The operating point is determined by the voltage divider RA03 and RA02. The working resistor of TA08 with LA09, CA08 is connected as a selective circuit tuned to the fundamental wave of the transmit pulses of 56kHz. This gives the amplifier bandpass characteristics. The following amplifier section with TA12 is designed as low pass, so that higher frequency interferences are cut off. The following driver stage with TA13 has three tasks: it serves as a driver stage, peak rectifier and for the control voltage voltage for the automatic gain control. The time constant of RA16, CA14 is less than 5ms and therefore shorter than the smallest pulse interval of the IR transmitter. With this peak rectification ensures that interfering signals, signals smaller than the useful signal amplitude are not transmitted. are not transmitted. The capacitor CA19 forms a low-pass filter in conjunction with RA14, which limits short-term interference pulse peaks. A further time constant element with RA19, CA19 is used for broadening the of the output pulses to approx. 20μs, so that a safe "noise" can be switching transistor TA22 to ensure safe interrupt triggering in the microcomputer. microcomputer is guaranteed. The automatic gain control is dimensioned in such a way that TA08 is not overdriven in the last amplifier stage. From CA14 via RA16, RA17 the "AGC" reaches the amplifier directly via the TA06 to the amplifier TA07. The control time constant is determined by CA14, RA16, RA17. stant is determined by CA14, RA16 and RA17. This large control time constant is paralleled by a faster control branch via DA09. It is used to immediately compensate for very large signals, so that they do not the amplifier TA12, respectively the peak rectifier TA 13, RA16, CA14 before the actual control starts. starts. This control branch is only effective for very large signals. effective. The RC element RA24, CA24 is used for coarse filtering of the operating voltage. voltage. RA10 and CA03 additionally smooth the operating voltages of the first of the first amplifier stages.

Microcomputer-controlled operating electronics

The 1 chip microcomputer IR01 located on the main chassis has a high processing speed of the versatile program with its 4 MHz clock frequency. processing speed of the versatile program. The explanation features, i.e. the software of the microcomputer, would go beyond the the scope of this circuit description. This information can be taken from the instruction manual. As can be seen from the circuit diagram, the power supply unit supplies in stand-by mode, the power supply provides the operating voltage U2 with approx. 10V. It reaches to the stand-by LED GE01 and via DR83, the series transistor TR82, DR82 stabilized to 5V to the VDD input, pin 42, of the micro- computer and to the IR preamplifier. In the absence of mains voltage the XR81 battery supplies the microcomputer with a backup voltage of 2.4V. of 2.4V. This voltage is also present at the RESET input, pin 33, while the HOLD input, pin 34, is set to low. This ensures that even in the event of a power failure, the 40 program locations stored in the RAM and the data stored in the RAM and the picture and sound settings selected by the user remain sound settings selected by the user remain stored. When remote control is active, an 11 bit data word is sent to the IR input, pin 35, from the IR preamplifier. preamplifier when the remote control is active. Only if this is within the time window specified by the μC and if it is provided with the correct address, the command is accepted. After actuation of the the power switch, 5V is immediately present at pin 42 (VDD). Now oscillates the IC-internal 4 MHz clock oscillator CP6. Time delayed via DR78 TR77, TR76 switch through and set the HOLD input, pin 34, to high level. The voltage rise at the collector of TR76 arrives as a positive pulse via CR73, RR73 at the base of TR 73 and switches it to low for a short time. This low level generates the RESET. This ensures that, when the pC starts operating the operating voltage and the clock frequency are correct. The The switch-on command for full operation is given either via the the IR input, or by the switching voltage of a video recorder to pin of a video recorder to pin 6 of the microcomputer. First the μC checks which way the switch-on command is given. If no IR signal is present and also the mains flip-flop (ON/OFF, pin 20) has not been set by the near control panel, then there has been a mains interrupt. interruption has occurred. This can also be caused by switching off and on by means of a mains switch. Now the μC checks whether the device was in standby or off mode was in standby or on mode before the power was interrupted. In the the latter case, it remains switched on at the selected program position. In the other case, the μC switches to stand-by. The The μC controls the switch-on function by means of a low level at pin 20, TR16 switches through TR17, which controls the stand-by voltage of approx. by voltage of approx. 10V to the multifunction processor IV01, pin 40, supplies. The power-on command is followed by 58 bit words via the I/O serial port, pin 40. accompanied by clock pulses at pin 41. This I2C bus determines with the first byte determines with the first byte the address for command control of the PLL or the VT decoder. The second control byte is followed by the byte for the band selection. Byte 4 and 5 determines the divider ratio in the PLL to obtain the tuner tuning voltage. The D/A converter is equipped with a five-channel pulse width modulator whose base frequency for the tint output, pin 1, is at 7.9kHz. For contrast, pin 2, color, pin 3, brightness, pin 4, and volume, pin 5, the basic frequency is 31.5kHz. All 5 output signals can be finely adjusted in 64 steps. steps. Downstream RC elements form variable control voltages control voltages for the corresponding functions. The volume as well as the mode selection stereo, mono, two-tone is done via the is done via the I2C bus. Instead of the formerly used display LEDs, this chassis concept uses the comfortable the comfortable "Picture Control System"(BRS) is used in this chassis concept. used. All operating and programming procedures are displayed on the large displayed on the screen. Here, too, the microcomputer From the RGB outputs, pin 22, 23, 24, the multifunction processor IV01 controls the picture tube. The Y-blank signal from pin 25 scans the back of the picture during the fade-in time. fade-in time the picture background black. In two lines 16 characters each, with a resolution of 64 pixels in 7 different colors. different colors, can be displayed. The vertical horizontal positioning of the fade-in is fixed in the microcomputer and cannot be and cannot be changed. For synchronous a horizontal pulse is applied to pin 26 and a vertical pulse to pins 27, 38. a vertical pulse. Nit LR03 at pin 28, 29 can be used to determine the line length of the insertion can be determined. As already mentioned, a video recorder connected via the Scart socket provides a horizontal connected via the scart socket supplies a 12V switching voltage to pin 8 of the scart socket during playback. pin 8 of the scart socket, which gives the switch-on command via RR64 at pin 6. the switch-on command via RR64 on pin 6. AV detect, Pin 7, accepts low level and the video and audio signal path on the scart interface board for the for the transmission of the signals at the scart socket.

The 1 chip microcomputer IR01 located on the main chassis has a high processing speed of the versatile program with its 4 MHz clock frequency. processing speed of the versatile program. The explanation features, i.e. the software of the microcomputer, would go beyond the the scope of this circuit description. This information can be taken from the instruction manual. As can be seen from the circuit diagram, the power supply unit supplies in stand-by mode, the power supply provides the operating voltage U2 with approx. 10V. It reaches to the stand-by LED GE01 and via DR83, the series transistor TR82, DR82 stabilized to 5V to the VDD input, pin 42, of the micro- computer and to the IR preamplifier. In the absence of mains voltage the XR81 battery supplies the microcomputer with a backup voltage of 2.4V. of 2.4V. This voltage is also present at the RESET input, pin 33, while the HOLD input, pin 34, is set to low. This ensures that even in the event of a power failure, the 40 program locations stored in the RAM and the data stored in the RAM and the picture and sound settings selected by the user remain sound settings selected by the user remain stored. When remote control is active, an 11 bit data word is sent to the IR input, pin 35, from the IR preamplifier. preamplifier when the remote control is active. Only if this is within the time window specified by the μC and if it is provided with the correct address, the command is accepted. After actuation of the the power switch, 5V is immediately present at pin 42 (VDD). Now oscillates the IC-internal 4 MHz clock oscillator CP6. Time delayed via DR78 TR77, TR76 switch through and set the HOLD input, pin 34, to high level. The voltage rise at the collector of TR76 arrives as a positive pulse via CR73, RR73 at the base of TR 73 and switches it to low for a short time. This low level generates the RESET. This ensures that, when the pC starts operating the operating voltage and the clock frequency are correct. The The switch-on command for full operation is given either via the the IR input, or by the switching voltage of a video recorder to pin of a video recorder to pin 6 of the microcomputer. First the μC checks which way the switch-on command is given. If no IR signal is present and also the mains flip-flop (ON/OFF, pin 20) has not been set by the near control panel, then there has been a mains interrupt. interruption has occurred. This can also be caused by switching off and on by means of a mains switch. Now the μC checks whether the device was in standby or off mode was in standby or on mode before the power was interrupted. In the the latter case, it remains switched on at the selected program position. In the other case, the μC switches to stand-by. The The μC controls the switch-on function by means of a low level at pin 20, TR16 switches through TR17, which controls the stand-by voltage of approx. by voltage of approx. 10V to the multifunction processor IV01, pin 40, supplies. The power-on command is followed by 58 bit words via the I/O serial port, pin 40. accompanied by clock pulses at pin 41. This I2C bus determines with the first byte determines with the first byte the address for command control of the PLL or the VT decoder. The second control byte is followed by the byte for the band selection. Byte 4 and 5 determines the divider ratio in the PLL to obtain the tuner tuning voltage. The D/A converter is equipped with a five-channel pulse width modulator whose base frequency for the tint output, pin 1, is at 7.9kHz. For contrast, pin 2, color, pin 3, brightness, pin 4, and volume, pin 5, the basic frequency is 31.5kHz. All 5 output signals can be finely adjusted in 64 steps. steps. Downstream RC elements form variable control voltages control voltages for the corresponding functions. The volume as well as the mode selection stereo, mono, two-tone is done via the is done via the I2C bus. Instead of the formerly used display LEDs, this chassis concept uses the comfortable the comfortable "Picture Control System"(BRS) is used in this chassis concept. used. All operating and programming procedures are displayed on the large displayed on the screen. Here, too, the microcomputer From the RGB outputs, pin 22, 23, 24, the multifunction processor IV01 controls the picture tube. The Y-blank signal from pin 25 scans the back of the picture during the fade-in time. fade-in time the picture background black. In two lines 16 characters each, with a resolution of 64 pixels in 7 different colors. different colors, can be displayed. The vertical horizontal positioning of the fade-in is fixed in the microcomputer and cannot be and cannot be changed. For synchronous a horizontal pulse is applied to pin 26 and a vertical pulse to pins 27, 38. a vertical pulse. Nit LR03 at pin 28, 29 can be used to determine the line length of the insertion can be determined. As already mentioned, a video recorder connected via the Scart socket provides a horizontal connected via the scart socket supplies a 12V switching voltage to pin 8 of the scart socket during playback. pin 8 of the scart socket, which gives the switch-on command via RR64 at pin 6. the switch-on command via RR64 on pin 6. AV detect, Pin 7, accepts low level and the video and audio signal path on the scart interface board for the for the transmission of the signals at the scart socket.The standard detection of the microcomputer is done via pin 17 and pin 18. according to the wiring of RR93 to RR97 the "ON-SCREEN" menu for single standard or multi-standard is activated. Pin 19 supplies low level in NTSC mode. A High-Pege1, supplied by the IV01 multifunction processor to pin 8 of the microcomputer, fits the the "ON-SCREEN" menu to the 60Hz deflection frequency. Low level at pin 37 mutes the FM tone on the stereo decoder and activates the AM tone activates the AM tone signal path if wired accordingly. Pin 35 is directly with the mute circuit connected. During the During the station search function, the sound is muted by low level. level. A high level signals to the microcomputer that a station has been found and a station and stops the station search. An IC-internal time loop switches the device to stand-by mode after approx. 5 minutes ("snooze function"). At When a key on the local control unit is pressed, pulses are sent to the command control from the A/D converter in the Keyboard-Input- Pin 13, 14, 15, 16. Pin 30 "TEST" is exclusively used for test programs used exclusively for test programs fed in by the production side. Chapter 5 VHF/UHF tuner with PLL The HF receiving section consists of a UHF/VHF tuner with built-in PLL. PLL. It is through a metal housing anti-interference next to the IF amplifier assembly on the chassis. net. The tuner, designed for the B/G standard, processes the following frequency ranges: - Band I - Band III - Band IV V 48,25... 84.25 MHz 126.25...294.25 MHz 471.25...855.25 MHz The HF input signal is split and routed to the UHF or VHF tuner. tuner. LH26 and CH02 couple the UHF signal into the input filter LH01, DH01 and CH03. Via CH01 the MOS- FET transistor TH04 at the gate receives the signal. Its source potential is by the UHF band switching voltage of TI11 via RH07, RH04 and RH06. CH06 decouples the now preamplified UHF signal to the RF two-pole filter consisting of DH01, CH07, LH07, DH01, CH08 and LH08. The mixing stage with TH14 forms from the input signal and the oscillator signal coming from TH16 via CH17 at the emitter the IF signal. The 1st IF circuit CH44, LH44, CH45, LH43 couples the the IF signal via DH46, RH46, CH 86 and the emitter follower TH 93. low impedance via terminal 3 of the tuner to the IF module, terminal l. In the VHF signal path, there is first an IF blocking circuit with CH31, LH31. It is followed by a low pass filter switchable with DH58 for band I and III. pass filter, consisting of CH58, LH58, LH59, CH59, LH61, LH62, DH61, LH57, DH57, CH61. The upper cutoff frequency is 300 MHz. The diodes DH55 and DH56 protect the MOS-FET transistor TH 65 from voltage peaks. TH65 is the first amplifier stage after the low-pass filter. The IF module supplies the two preamplifier transistors TH65, TH56 and TH65. TH65, TH04 an AGC control voltage for protection against overload. overload. The signal amplified in TH65 is fed back to the IF module via the band I and III and tuned with DH57, DH57. two-pole filter to the mixing transistor TH75. Transistor TH87 works as an oscillator. This couples its frequency via RH87, CH87, CH78 to the VHF input signal to the base of mixer TH75.

A two-pole filter with CH77, LH81, CH84, LH82, CH83 supplies the IF signal signal coming from the mixing transistor via the decoupling diode DH83 to the first IF amplifier stage TH 93. PLL circuit The circuit concept used here includes a 1-chip PLL with integrated prescaler and three band selector outputs (Bd. I, Bd. III, UHF). For a tuner tuning operation, the control unit- microcomputer supplies the divider and band data via the data bus in four four 15 bit shift registers of the PLL IC II06, pin 14/15. process takes place with each channel- or Program- ' place call and repeats itself periodically. The I2C bus contains five bytes for calling up a program location. Byte 1 gives the address, byte 2 and 3 contain control bits and the tape infor- formation, byte 4 and 5 define the tuning voltage at pin l and thus the thus the receive frequency. The band select transistors TI14, Bd.I, TI13, Bd.III and TI 11, UHF, are activated by the PLL-IC. From the oscillator signal applied to pin 4 and the 4MHz- reference signal (pin 16), a comparison quantity for tuner tuning is formed and tuning and is fed to the operational amplifier at pin 18. to the operational amplifier. The operational amplifier works as a switch and acts for the 30V signal connected to pin 2 via RI 10 at pin 2 as a controllable load resistor. Thus a tuning voltage of 0.5 to 30V is available for the tuner. is available for the tuner. If the frequency at the output of the programmable part changes as a result of a tuning process, controlled by the data bus, at the output of the programmable divider, the tuning voltage of the tuner is the tuner oscillator is controlled by the tuning voltage until the oscillator is until the oscillator frequency and the divided crystal frequency are identical again. are identical again. The smallest tuning step is 62.5 kHz. This means that the 7 MHz bandwidth of the VHF standard radio can be tuned in 112 fine standard can be tuned. IF amplifier The IF amplifier consists of the decoupling emitter follower TH93 in the tuner. the emitter follower TH93 in the tuner, the preamplifier TI10 with downstream surface wave filter FI19 for the picture and QI 30 for the sound. for the sound. Due to its physical and electrical properties, the surface physical and electrical properties, the surface acoustic wave filter replaces conventional LC in IF signal processing. At the output of QI30, the image the 38.9MHz image carrier and the 33.4MHz audio carrier are selectively audio carrier with 33.4MHz are available. The outputs pin 4, pin 5, of the FI19 couple the image IF signal symmetrically to the image IF IC II20. II20. A three-stage regulated wideband amplifier feeds the IF signal into the image carrier controlled demodulator, whose external resonant circuit FI20 is tuned to 38.9MHz. Above a two-stage video amplifier with a low-pass characteristic the video signal to pin ll for further signal processing. coupled. Adjustable with PS21, the RF preamplifiers in the tuner receive the delayed AGC from pin 5 of the IF block. An AFC is not necessary because of the frequency synthesizer tuning system. necessary. The audio IF signal processing is performed by IC II71. Here, according to the quasi-parallel tone method, image and sound carriers are combined. are combined. The oscillating circuit FI30 at pin 8 and 9 supplies the carrier frequency carrier frequency required for demodulation. Pin 12 is used for further the audio IF signal with 5.5MHz and additionally with 5.74MHz for stereo for stereo additionally with 5.74MHz.

TELEFUNKEN (THOMSON) PALCOLOR SP212 STEREO CHASSIS 418 (THOMSON IKC-2) Sound signal processing and muting

Stereoderoder The stereo decoder module includes the follo

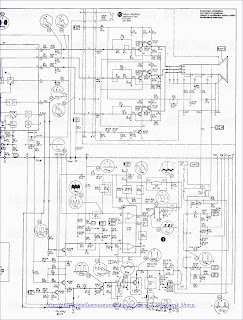

wing functional groups: - Two FM IF amplifiers with demodulator (TBA 120 UB) - Pilot frequency decoder for stereo and two-tone with matrix for left-right separation of left-right information (TDA 6600) - I2C bus controlled tone adjuster with surround sound section and Scart input Demodulator At input BA04, connection 10, of the stereo decoder module the audio IF frequencies 5.5MHz and 5.74MHz (for stereo/two-tone) or 6.5MHz for OIRT tone transmitters are available frequency modulated. Since without switching information in the case of 6.5 MHz IF, this should also be demodulated. demodulated, a 6.5 MHz ceramic filter QS01 is required in the 5.5 MHz input branch. 6.5MHz ceramic filter QS09 is connected in parallel with QS01 and in series with the 5.5MHz reference circuit (FSOS/CH08), a resonant circuit (FS10/CS10) tuned to 6.5MHz. tuned to 6.5MHz (FS10/CS10) (Attention, this applies only to devices for devices which are factory equipped with the reception possibility transmitters at the factory). The circuits are damped in such a way that that the output LF just matches the amplitude of the following IC amplitude of the following IC IS30. At a deviation of 50 kHz it amounts to approx. 300 mV. Via a diode matrix (DS01/DS02/DS03/DS04 /DS11) the demodulator IC's IS10 and IS01 can be muted with low level at pin 2 via three control paths: 1. from the mute circuit via DS03. 2. data bus controlled via DS04. 3. sound standard controlled by microcomputer IR01 via DS02. For devices in multi-standard version, e.g. demodulated AM- sound signals can be fed as AF to pin 3 of IC IS01. Uon pin 8 of the ICs TBA 120 UB the AF signals are fed to the stereo decoder IC TDA 6600. Stereo decoder In stereo mode the L + R signal is fed to IC IS30, pin 23, and the pin 21 the 2R signal, accompanied by the modulated 54kHz pilot tone. tone. Here the right and left signals are processed in the stereo matrix. signals are processed in the stereo matrix, and in two-tone mode the channels l and 2 are are separated. The outputs pin 2 and pin 6 supply the AF signal galvanically decoupled via CS20/CS23 to the scart socket, connection l/3 and via CS50/CS51 to IC IS60. PS35 is set to lowest crosstalk. For evaluation of the pilot tone CS17 to the oscillating circuit FS38, which is tuned to the pilot carrier frequency. FS38, which is tuned to the pilot carrier frequency. From there, the 54kHz pilot sig- nal via pin 20 into two PLL loops. Here the evaluation of the evaluation of the modulated pilot carrier. 117Hz for stereo and 274Hz for two-tone. Four IC-internal demodulators support this task. task, whereby the capacitors at the mixer outputs pin 14/15/17/18 determine the bandwidth and thus the signal-to-noise ratio. determine. The PLL is supplied with line pulses at pin 13, coming from the diode splitter transformer. from the diode splitter transformer. The external wiring of the PLL time constant is connected to pin 11 for stereo and to pin 10 for dual tone. 10. the degree of noise suppression for stereo is set with CS25 at pin 9. For two-tone CS24 at pin 8 takes over this task. The IC-internal digital evaluation stereo/mono/two-tone delivers the information to the matrix and to the four-level input/output, Pin 7. Data bus controlled IC IS60 signals coming from pin 2 at pin 7 with OV forced mono. IC IS30 on the other hand supplies via pin 7 6V for stereo, 3V for dual tone and l.3V for mono. Tone control The control of IC IS60 is done via the I2C bus pin 24, 25 and the four level lines at pin 2. At the input pin 1, pin 3 there is a two-channel AF analog switch for switching between between TV mode or scart playback. A subsequent switch is used to switch between channel 1 or 2 for multi-channel multi-channel audio broadcasts. Next in the signal path is the surround sound circuit, the at Nono signal a spatial, stereo-like sound impression. This function can be switched and switched on. The spatial sound circuit consists of one operational amplifier per amplifier per channel. The first amplifier (output pin 21) has an internally IC-internally fixed gain of -1. The second amplifier is switchable amplifier is switchable between gain -l and a gain selected by gain selected by RS55. The surround sound effect is is achieved by connecting the input of the second amplifier via the the bandstop RS50/RS51/CS52/RS52/RS53/CS53/RS54/CS54 a signal via the bandstop rs50/rs51/cs52/rs52/rs53/rs54/cs54 and the phase inverted signal via the bandpass CS56/RS58/CS55/RS 57 the phase inverted signal is fed. It amplitude is linear, but the phase is inverted by 180° at medium frequencies. 180° at medium frequencies.

wing functional groups: - Two FM IF amplifiers with demodulator (TBA 120 UB) - Pilot frequency decoder for stereo and two-tone with matrix for left-right separation of left-right information (TDA 6600) - I2C bus controlled tone adjuster with surround sound section and Scart input Demodulator At input BA04, connection 10, of the stereo decoder module the audio IF frequencies 5.5MHz and 5.74MHz (for stereo/two-tone) or 6.5MHz for OIRT tone transmitters are available frequency modulated. Since without switching information in the case of 6.5 MHz IF, this should also be demodulated. demodulated, a 6.5 MHz ceramic filter QS01 is required in the 5.5 MHz input branch. 6.5MHz ceramic filter QS09 is connected in parallel with QS01 and in series with the 5.5MHz reference circuit (FSOS/CH08), a resonant circuit (FS10/CS10) tuned to 6.5MHz. tuned to 6.5MHz (FS10/CS10) (Attention, this applies only to devices for devices which are factory equipped with the reception possibility transmitters at the factory). The circuits are damped in such a way that that the output LF just matches the amplitude of the following IC amplitude of the following IC IS30. At a deviation of 50 kHz it amounts to approx. 300 mV. Via a diode matrix (DS01/DS02/DS03/DS04 /DS11) the demodulator IC's IS10 and IS01 can be muted with low level at pin 2 via three control paths: 1. from the mute circuit via DS03. 2. data bus controlled via DS04. 3. sound standard controlled by microcomputer IR01 via DS02. For devices in multi-standard version, e.g. demodulated AM- sound signals can be fed as AF to pin 3 of IC IS01. Uon pin 8 of the ICs TBA 120 UB the AF signals are fed to the stereo decoder IC TDA 6600. Stereo decoder In stereo mode the L + R signal is fed to IC IS30, pin 23, and the pin 21 the 2R signal, accompanied by the modulated 54kHz pilot tone. tone. Here the right and left signals are processed in the stereo matrix. signals are processed in the stereo matrix, and in two-tone mode the channels l and 2 are are separated. The outputs pin 2 and pin 6 supply the AF signal galvanically decoupled via CS20/CS23 to the scart socket, connection l/3 and via CS50/CS51 to IC IS60. PS35 is set to lowest crosstalk. For evaluation of the pilot tone CS17 to the oscillating circuit FS38, which is tuned to the pilot carrier frequency. FS38, which is tuned to the pilot carrier frequency. From there, the 54kHz pilot sig- nal via pin 20 into two PLL loops. Here the evaluation of the evaluation of the modulated pilot carrier. 117Hz for stereo and 274Hz for two-tone. Four IC-internal demodulators support this task. task, whereby the capacitors at the mixer outputs pin 14/15/17/18 determine the bandwidth and thus the signal-to-noise ratio. determine. The PLL is supplied with line pulses at pin 13, coming from the diode splitter transformer. from the diode splitter transformer. The external wiring of the PLL time constant is connected to pin 11 for stereo and to pin 10 for dual tone. 10. the degree of noise suppression for stereo is set with CS25 at pin 9. For two-tone CS24 at pin 8 takes over this task. The IC-internal digital evaluation stereo/mono/two-tone delivers the information to the matrix and to the four-level input/output, Pin 7. Data bus controlled IC IS60 signals coming from pin 2 at pin 7 with OV forced mono. IC IS30 on the other hand supplies via pin 7 6V for stereo, 3V for dual tone and l.3V for mono. Tone control The control of IC IS60 is done via the I2C bus pin 24, 25 and the four level lines at pin 2. At the input pin 1, pin 3 there is a two-channel AF analog switch for switching between between TV mode or scart playback. A subsequent switch is used to switch between channel 1 or 2 for multi-channel multi-channel audio broadcasts. Next in the signal path is the surround sound circuit, the at Nono signal a spatial, stereo-like sound impression. This function can be switched and switched on. The spatial sound circuit consists of one operational amplifier per amplifier per channel. The first amplifier (output pin 21) has an internally IC-internally fixed gain of -1. The second amplifier is switchable amplifier is switchable between gain -l and a gain selected by gain selected by RS55. The surround sound effect is is achieved by connecting the input of the second amplifier via the the bandstop RS50/RS51/CS52/RS52/RS53/CS53/RS54/CS54 a signal via the bandstop rs50/rs51/cs52/rs52/rs53/rs54/cs54 and the phase inverted signal via the bandpass CS56/RS58/CS55/RS 57 the phase inverted signal is fed. It amplitude is linear, but the phase is inverted by 180° at medium frequencies. 180° at medium frequencies.The tone and volume control per stereo channel consists of three operational amplifiers with electronic potentiometers. The volume setting is made - for both channels separately - in 64 steps. A balance adjustment can thus be made by different by adjusting both channels in different ways. The aurally correct (physiological) volume characteristic is achieved by linking the volume the volume setting with the treble/ bass setting. adjustment. In the case of treble and bass settings, the following is achieved by means of an external circuit with one capacitor each. in 31 steps each. The IR01 microcomputer, based on the IS60 sound adju IS60, the information mono/stereo/two-tone is displayed on the screen via the I2C bus. Two-tone is displayed on the screen via the I2C bus. The connections Pin 13, 15 couple, galvanically separated by CS61/CS65 the NF signals to the NF power amplifier ICs IA05/IA25. IC's IA05/IA25. NF power amplifiers Both output stages are identical in design. The NF-IC's work as operational amplifiers with negative feedback path; they are short-circuit short-circuit proof and thermally protected. The sine output power is lOW at 8 ohms. To suppress disturbing switch-off noises in the loudspeaker, the microcomputer IR01, Pin 20, sends a high level via RA13 high level via RA13/RA15 to the base of the TA15. This srhaltet RA03/RA04, RA23/RA24 to the AF input, pin 1, of the IC. pin 1 of the ICs. Thereby the LF output stages are immediately disabled. Mute Since the chassis must comply with legal requirements, a mute circuit blocks the sound a mute circuit blocks the audio channel as long as no standard television signal is television signal is received. This mute circuit should only evaluate the FBAS signal coming from the IF section. signal coming from the IF section. Teletext, on-screen text or video signals fed in externally via the the Scart socket must not influence the sound cutoff. must not influence the sound cutoff. The mute circuit is realized with the transistors TM03, TM 12, TM16, TM18. At the same time it generates the search STOP im pulse. TM03 is controlled via RM01, CM02 with the FBAS signal from the IF module, terminal 6. It acts as a pulse separator and and supplies the horizontal and vertical synchronous pulses to an electronic electronic bandpass filter, which is tuned to 15625Hz. At the collector of the TM12 a sinusoidal horizontal- frequency control voltage for the switching stage with TM16 and TM18. TM16 periodically becomes conductive and charges CM17 (2.2 μF) via RM17, whereupon TM18 remains conductive as long as H-synchronous pulses are present in the control signal. control signal are present. The 12V voltage reaches the mute input from the collector of TM18. input, terminal BA 04-17, of the audio module and as STOP signal pin 36 of the IR01 control processor as a STOP signal for the station search. the snooze circuit (automatic switching to standby after 5 seconds). (automatic switching to standby after 5 minutes without a transmitter signal). activated.

TELEFUNKEN (THOMSON) PALCOLOR SP212 STEREO CHASSIS 418 (THOMSON IKC-2) Video signal processing

TELEFUNKEN (THOMSON) PALCOLOR SP212 STEREO CHASSIS 418 (THOMSON IKC-2) Video signal processingFrom output 6 of the IF amplifier, the FBAS signal passes through the 5,5MHz-lock ( sound carrier) CV63, LV63, RV63, and RV62 to the connection connection 13 of the Scart interface board. Decoupled with CE11, the the FBAS signal from pin 3 of the IC IE10 via pin 2 and RE11 to the to the Scart socket, pin 19. External video si- gnals are fed to connection 20 of the Scart socket. Lying, from the IROl microcomputer is high at connection 7 of the scart interface faceplate, transistor TE10 switches through and applies a low level to pin 5. and applies a low level to pin 5 of the IE10. In this case the internal internal video signal passes the video switch to pin 6 of the IC. At low level at pin 7 of the scart interface board, the external video signal is at the Scart socket is switched through. From connector 10 of the scart interface board the video signal is fed through via RV27, RV 28, the Y-delay line VV28 and CV71 the video signal is connected to pin 58 of the multifunction processor IC IV01. Integrated in VV28 there is a 4.43 MHz trap. Consequently, the Y-signal without color information is Y signal without color information. In SECAM mode, the 4.25MHz trap LV29, CV29, TV29 is also activated. By TV65, CV65, LV 64, RV64 the Y-signal is differentiated and via CV68 at pin 56 is added to the Y-signal in the sharpness stage. The amount of the the resulting frequency boost in the Y-signal path is determined by the pin 55 with PV58. At pin 59 takes place, voltage controlled, the contrast is set, whereby the color saturation is the color saturation is also changed at the same time. An IC-internal matrix forms a color difference matrix from the Y-signal and the already the RGB signals from the supplied Y-signal and the already low-frequency color difference signals. External RGB-H signals from the Scart connector or "picture control sy- stem" signals from the control unit microcomputer reach the multi-function unit via pin 47, 49, 51 and 53 to the multifunction processor. The "Fastblan- king" signal on pin 53 determines whether the video input signal or the the RGB signals are routed to the picture tube control. The brightness adjustment is DC-controlled at Pin 48, while in the capacitors CV49, CV51, CV52 at Pin 44, 45, 46 a DC voltage is stored for black level control. is stored. After horizontal and vertical reverse darkening, the RGB signals leave the the RGB signals leave the multi-function processor at pins 41, 42, 43. function processor. A downstream low-pass filter frees the RGB signal from any the RGB signal from parasitic oscillations above 5 MHz. above 5MHz. From here the RGB signals are transmitted via connector BV01 to the picture tube plate. Beam current limitation Depending on the beam current, the following occurs at the base point, connection 4, of the high voltage winding of the diode split transformer via RL08 a negative control voltage, which is converted into a positive one by the voltage via RL05 into a positive one. It reaches the contrast controller via RL 06, CV81, DV81 and with PV79 adjustable to the contrast control input, pin 59. This automatically prevents an excessive increase of the beam current in the picture beam current in the picture tube. Chroma signal processing The IV01 multifunction processor includes a multistandard chroma decoder chroma decoder, as well as an automatic color standard recognition which can be used for PAL, Secam, NTSC 4.43 MHz (Videore- NTSC 3.58 MHz (transmitter), activates the respective color decoder. activated. The device version shown in the enclosed circuit diagram processes PAL and PAL and SECAM B/G signals. From the Scart interface plate, the FBAS signal reaches the chroma filters. chroma filters. A special switch circuit is required for each standard. is required for each standard. The PAL chroma filter, consisting of RC24, LC24, CC24, CC25, RC26, LC26, CC26 and CC53 provides the required 4.43 MHz bandwidth. 4.43 MHz bandpass characteristic. In the Secam signal path RC22, CC22 contains the bell filter characteristic for this standard. CC23, LC23, RC23 and CC48. The PAL signal path leads from pin 20 via a regulated amplifier stage. amplifier stage. This is necessary to compensate for slightly different IF passband curves or receiver tuning, the color difference signals are always signals always in a certain relation to the Y-signal. to the Y-signal. As "actual value signal" for the control, the burst amplitude for the PAL- the burst amplitude is used for the PAL signal and for the frequency-modulated Secam- signal the total signal is used. CC47 and RC47 serve as filter for the control voltage. The controlled chroma signal reaches the standard identification with the burst part. To the identification signals on the rear black shoulder are used for this purpose. shoulder are used. Here, the individual standards differ standards differ characteristically from one another. The identification The identification circuit in the decoder consists of three modules:

-

Phase discriminator for comparing the burst phases of PAL and

NTSC-H signals with the reference signal.

-

Frequency discriminator for deriving the H/2 signal in seram-

transmissions.

-

H/2 demodulator for PAL and Secam signal with logic circuitry

for the actual identification.

The IC contains one identification circuit each for PAL, Secam and NTSC. At the external capacitors CC57 (Pin 22), CC58 (pin 23), CC62 (pin 27), the DC voltage levels applied there indicate the voltage level at synchronized reference oscillator the recognized standard. A logic circuit supplies at pin 10, 11 and 21 a switching voltage corresponding to the Chroma standard. Pin 21 is not used with this chassis concept. With PAL, TC34 switches through and blocks TV29, so the 4.25 MHz trap is ineffective. MHz trap is ineffective. Via the logic connectors, by applying external voltage levels, the voltage levels, according to the Chroma standard table, the Chroma standard must be selected by force: Standard Logic connection Identification connection Pin Pin 10 11 22 23 27 PAL 6V 6V 12V 6V 12V Secam 6V OV 6V 12V 6V NTSC 4,43MHz 0V 6V 6V 6V 12V NTSC 3,58MHz 0V 0V 0V 0V 12V In SECAM mode the IC works with horizontal identification. If pin 18 is terminated with a resistor to ground, the IC is automatically switched to horizontal or vertical identification vertical identification according to the requirement. After standard detection and burst blanking, the chroma signal from pin chroma signal from pin 14 via CC44, RC44, phase adjustable with LC43 to the PAL delay line VC43. This delivers the signal delayed by one line, amplitude adjustable with PC44, via pin via pin 12 to the color signal demodulator. In the matrix, to obtain the two carrier-frequency components F (B-Y) and F (R-Y), the IC-internally looped signal and the signal delayed by one line with VC 43 is added and subtracted respectively. In the (R-Y) demodulator is the PAL switch, which is used to control the phase position of the carrier-frequency signal component F (B-Y) and the component F (B-Y) and F (R-Y) is reversed. The demodulators are synchronous demodulators, which are fed from the from the 4.43 MHz reference carrier generated by CQ66, pin 26. are switched. When sequential Secam signals are received, they are sent directly to the cross switch (permutator). This supplies the two synchronous demodulator stages in an alternating sequence from line to line. from line to line the undelayed signal and the signal delayed by VC43. signal. For frequency demodulation of these signals quadra- quadrature demodulators, each consisting of a phase shifter circuit at pins 4 and 5 (VC43). phase shifter circuit at pins 4 and 5 (B-Y) and pins 8 and 9 (R-Y), respectively, and a multiplier stage. the Secam reference circuits rotate the phase of the corresponding color signal. phase of the corresponding color signal at the respective unbundled frequency. 90°, so that the signal voltage at the demodulator output disappears. disappears. With Secam decoding, two deempha- CC01 at pin 1 (B-Y) and CC02 at pin 3 (R-Y) are switched on. connected. NTSC signals take the same signal path as PAL. For NTSC 3.58MHz a 3.58MHz reference carrier crystal is required at pin 28. is required. The multifunction processor supplies the color difference signals from pin 2 and pin 64. color difference signals from pin 2 and pin 64 via one low pass each LL03, RC03, CC04, CC 03 and RC07, LC07, CC07 to pin 60, 62. They are used to remove any existing HF residues are eliminated. After clamping of the (R-Y) and (B-Y) signals in the IC, they pass through a controllable amplifier, which is externally the color saturation externally from pin 7. externally from pin 7. Then the color difference signals are mixed with the Y-signal in the RGB matrix. signals are mixed with the Y-signal in the RGB matrix. RGB output stages The positive RGB output signals supplied by the IV01 video processor IC RGB output signals delivered by the video processor IC IV01 have to be RGB output stage transistors TT11, TT21, TT31 to drive the picture tube. inverted. Since all three video output stages are identical the blue output stage will be explained for the purpose of this will be explained.

In order to ensure a good constancy of the amplification factor and the working point, it is necessary that the amplification of the power amplifier is amplification of the power amplifier without negative feedback is sufficiently is sufficiently large. For this reason the present AB output stage was chosen. The TT31 transistor amplifies the video sig nal to approx. 70 Vpp. Rising signal edges reach the cathode via TT27, RT28 and LT28 to the cathode, while falling signal edges via via DT28, RT28 and LT28 to the picture tube. This type of of the picture tube cathode and improves the frequency response in the cathode capacitance and improves the frequency response in the high frequencies. The gain (white balance) of the red and green output stages is set with PT11, PT21; the gray balance with PT12, PT22. These settings may influence each other slightly and should therefore be repeated should therefore be repeated alternately. Transistor TT33 serves as a common low impedance footpoint of the RGB output stage. If the device is switched off or into stand-by mode, the collector will be mode, from the collector of the protection switching transistor TV02 via DV47, DT32, DT31 to the base of the TT33, so that the TT33 is so that the TT33 is blocked. Thus the complete RGB output stage is deenergized and the and the screen is dark. A flashing of the screen at the moment of flashing of the screen at the moment of switch-off is thus largely prevented. Flare suppression During normal operation CT03 is charged via RT10 and DT04, limited by DT03 limited, charged to 150 V. After decommissioning the or return to the stand-by node, the voltage U4 (180V) is very voltage U4 (180V) decreases very quickly. In CT03 a charge so that at grid 1 of the picture tube minus 150 V is present for a longer period. minus 150 V for a longer period. Thus the screen remains dark after dark after switching off. Automatic black level and gain control (Auto Cut Off) In modification to the preceding explanations, some models are equipped with this additional device models are equipped with this additional circuit. The IC ID01 is a special circuit to control the automatic black and white automatic black and white level control. Since the DC operating point and the amplitude of the RGB si- gnals must match, a clamp is required in each channel. is required in each channel. With the positive edge of the negative vertical return pulse at connector pin BD 04, after signal inver- tigation in in TD31, the cut-off function is started at pin 18 of the IC. started. The control compensates the drift of all video stages, including the video output stages. including the video output stages. The control loop works in parallel for all RGB stages, invisible for the viewer, during the image change. In terms of time, the start of the black level control is line 18 of the 23 lines of vertical rewind. vertical rewind. The clock signal is provided by the line pulses fed to pin 13. pin 13 serve as the clock signal. During the 18th and 19th line the IC supplies at pin 22, 26, 30 for black level measurement for the RGB output stage. In lines 20 and 21 the white value is measured in the same way. measurement. To process the control pulses, the IC requires a DC voltage at pins 2, 4 and 6 a DC voltage level of 3V. Pin 15 is connected during during the measuring time (18th to 22nd line) to IC ID12, pin 9, 10, 11, 11. This now supplies from the voltage divider RD11, ID11, RD 14, PD11, RD13 the required 3V-DC level. The measuring resistors of the RGB output stage PT12, RT09, PT22, RT19, RT30 provide a voltage drop proportional to the cathode current. This voltage drop is fed to IC ID01 via pins 19, 23, 27 and is compared there compared with two reference voltages. As comparison voltage voltage is 9.5V for the black level and 5V for the gain. and a voltage of 5V for the gain control. This results in a ratio This results in a ratio of 1:10 between the black and white value measurement. The The difference between the DC voltage level at pins 2, 4 and 6 and the voltage drop and the voltage drop at the measurement resistors is used for the black the black level in the capacitors CD 01, CD02, CD03. for the black level. The capacitors CD04, CD06 and CD07 store the voltage for the white value. voltage for the white value. According to the level of these voltages IC ID01, individually adapted to the picture tube, adjusts the gray and gray value and white value. The amplitude of the RGB output signals determines the white level and is is adjustable with PT12, PT22. The DC voltage applied to the RGB signal DC voltage under the RGB signal determines the gray value. This can be set with PD11. adjustable.

TELEFUNKEN (THOMSON) PALCOLOR SP212 STEREO CHASSIS 418 (THOMSON IKC-2) Horizontal deflection stage with east/west correction circuitry

The drive signals for the horizontal output stage are processed in a PLL function processor IV01 in a PLL circuit. A VCO (Voltage Controlled Oscillator) oscillating at 503 kHz. voltage controlled oscillator) supplies via a divider line-frequency pulses. A phase comparison compares these with the the frequency of the line sync

pulses from the amplitude sieve. If there is a frequency or phase deviation of the VCO, a control voltage pulls it the VCO, a control voltage is applied to the VCO until the two frequencies match exactly in frequency and phase. Externally at pin 37 operates the 503kHz ceramic oscillator QL45. For filtering the VCO CL43, RL44 and CL 44 are connected to pin 36 for filtering the VCO control voltage. line return pulses from the diode split transformer LL05 via RL38, RL41, CL41 at pin 38 determine in phase comparison the start of the line on the screen. on the screen. With PL39 the basic setting of the horizon- tal position (-phase). At pin 39 the processed line-frequency square-wave im- pulses are fed out. Decoupled with DL17, they reach TL17 via RL 16, CL16 to TL17. The horizontal driver transistor TL17 amplifies the pulses to amplifies the pulses in order to supply the necessary base required base saturation current for TL19. The RC element RL18, CL18 attenuates the voltage peaks that occur when TL17 is switched off. voltage peaks that occur when TL17 is switched off. Transistor TL19 operates as a switch with diodes DL21, DL22 are connected in parallel. This prevents an inverse operation of the transistor is prevented. In addition, the diodes are part of the 0/W diode modulator(110° devices). The function of the horizontal deflection circuit in the steady state is circuit in the steady state. The most important components are marked as follows: - BL01 = Horizontal deflection coil - CL24 = Forward and tangential capacitor - CL21/22 = Return capacitor - TL19 = Switching transistor - DL21/22 = Switching diode The effective flyback capacitor during the blocking phase of TL19 is formed by series connection of CL21 and CL22. Voltage and current waveforms during the time interval of one line are shown in Figures 3 and 4.

pulses from the amplitude sieve. If there is a frequency or phase deviation of the VCO, a control voltage pulls it the VCO, a control voltage is applied to the VCO until the two frequencies match exactly in frequency and phase. Externally at pin 37 operates the 503kHz ceramic oscillator QL45. For filtering the VCO CL43, RL44 and CL 44 are connected to pin 36 for filtering the VCO control voltage. line return pulses from the diode split transformer LL05 via RL38, RL41, CL41 at pin 38 determine in phase comparison the start of the line on the screen. on the screen. With PL39 the basic setting of the horizon- tal position (-phase). At pin 39 the processed line-frequency square-wave im- pulses are fed out. Decoupled with DL17, they reach TL17 via RL 16, CL16 to TL17. The horizontal driver transistor TL17 amplifies the pulses to amplifies the pulses in order to supply the necessary base required base saturation current for TL19. The RC element RL18, CL18 attenuates the voltage peaks that occur when TL17 is switched off. voltage peaks that occur when TL17 is switched off. Transistor TL19 operates as a switch with diodes DL21, DL22 are connected in parallel. This prevents an inverse operation of the transistor is prevented. In addition, the diodes are part of the 0/W diode modulator(110° devices). The function of the horizontal deflection circuit in the steady state is circuit in the steady state. The most important components are marked as follows: - BL01 = Horizontal deflection coil - CL24 = Forward and tangential capacitor - CL21/22 = Return capacitor - TL19 = Switching transistor - DL21/22 = Switching diode The effective flyback capacitor during the blocking phase of TL19 is formed by series connection of CL21 and CL22. Voltage and current waveforms during the time interval of one line are shown in Figures 3 and 4.The following sequence can be seen: At the end of the forward propagation time tl, TL19 is disabled by a corresponding base drive signal. The stored energy in the coil and the diode-splitting transformer leads to a rapid charging of the return charging of the return capacitor. At the end of the first return half at time t2, the charge reaches the maximum value. value. The current passes through the zero point and changes direction during the second return half. direction during the second half of the return flow. Now the return capacitor discharges capacitor discharges and shifts the energy back into the deflection deflection coil (resonant circuit principle). At the end of the return t3 the voltage passes through zero and takes on negative values. At DL21/22 become conductive and prevent the so-called "inverse operation" of the The return capacitor CL21/22 is short-circuited via the diodes and is short-circuited via the diodes and the run-up phase begins. The circuit energy is in the deflection coil. During the half of the outward phase, current flows from the deflection coil via DL21/22 into the via DL21/22 into the forward capacitor CL24 and charges it. This process is completed at t4 in the middle of the picture. The current changes its direction and flows from CL24 via TL19 into the deflection coil. via TL19 back into the deflection coil. Precondition is however, that TL19 is controlled accordingly at the base. For the defi- at the end of the outward run t5, TL19 receives a negative impulse from the receives a negative pulse from the driver stage at the base, which is which is slightly advanced in time. During this period the base zone of TL19 be cleared of charge carriers very quickly. Practical execution of the circuit In addition to the basic function of the horizontal deflection three further functional groups are to be considered to be considered: 1. the L-C-R circuit, consisting of LL23, CL23, RL23 attenuates harmonics. During the line scan they could lead to modulation and vertical dark interference stripes on the screen. on the screen. 2. 2. to at vertical lines of a grid test pattern at black/white jump to prevent "mousing", additional energy is fed into the deflection circuit via RL27, RL28, CL27 and LG08. deflection circuit. 3. to compensate the east/west pincushion distortion the 0/W-IC IG01 of pin 5 provides a line-frequency pulse width modu- lated signal. modulated signal. This signal is applied via the coupling coil LG08 to the capacitor CL24 and causes a vertical-frequency parabolic distortion. vertical-frequency parabolic modulation of the deflection current.