LOEWE CHASSIS E3001.

- LOEWE developed this CHASSIS E3000 E3001 BASING IT ON ITT/MICRONAS CHIPSET

which allows Full Digital Processing of VIDEO AND SOUND in high sophisticated way.

- Results are in Ultra superb picture and clear sound.

Technical specifications

Profil Plus 3472

with micro digital chassis E 3000 / 8 bit

Picture tube: Super Flat Line 29”, picture diagonal length: 72cm (visible 68cm),

deflection angle 110°, heating voltage 6.3 Vrms (28Vp-p)/310 mA,

degaussing each time the set is switched on

Power requirement: 200 to 260 V~, 50 or 60 Hz

Power consumption: 145 W (SB mode 5 W)

Vertical frequency: 50 Hz ,60 Hz NTSC-M #)

Horizontal freq.: 15625 Hz, 15750 Hz NTSC-M #)

Dimensions: 80 x 57.5 x 48.5 (W x H x D)

Weight: 40 kg

Connections

(front): Headphones jack with separate setting, F

ront AV: two cinch jacks

for sound input, hosiden jack for video input

(back) EURO jack 1: for RGB, Y/C input signals, RC 5, CVBS and sound

input/output, EURO jack 2: RC 5, CVBS, Y/C and sound input/

output, two cinch jacks for sound output (regulable), (jacks programmable

via dialogue control system), AV through antenna jack

Features: TV Timer programming with VPT, Video Copy function, Dialogue

control system IDC, dual-sound decoder, tuning and memory

system digital, digital channel selector ACP, 1OO programme

locations in memory 00 to 99, OSD indication, Sharpness Control

System (SCS), DTI Plus, Automatic Volume Control AVC, Child

Lock, Photo CD, electronic alignment with the remote control,

#) hyperband tuner Multi Standard 8 MHz:

47 MHz - 861 MHz

PAL B/G/D/K/L/I/M/N + 60Hz • SECAM B/G/D/K/L

NTSC-VIDEO (4.43) • NTSC-M (3.58)

hyperband tuner Standard 8 MHz:

47 MHz - 861 MHz

PAL B/G + 60Hz • SECAM B/G/D/K • NTSC-Video (4.43)

*) SAT tuner: 914 MHz - 2154 MHz

Standard selection by means with the remote control, teletext

decoder as standard feature (TOP/FLOF)

Audio system: Rated power at an audio modulation frequency of 1 kHz: 2 x 20 W

for an impedance of 4 ohms, harmonic distortion less then 1 per

cent, 2 loudspeakers, base broadening for stereo, spatial sound for

mono

Retrofit kit: Stereo Satellite Tuner

RIGHT SIDE

Line deflection output + EHT

Frame deflection output with TDA8175

Supply based on TDA4605-3 (SIEMENS)

- LEFT SIDE

Tuner + IF

Sound Amplifiers with TDA7262

IN THE MIDDLE: DIGITAL BOARD UNIT.

Single-Chip Video Processor VDP3108:

1. Introduction

The entire video processing and controlling for a color

TV has been developed on a single chip in 0.8m CMOS

technology. Modular design and submicron technology

allow the economic integration of features in all classes

of TV sets.

Open architecture is the key word to the new DSP generation.

Flexible standard building blocks have been defined

that offer continuity and transparency of the entire

system.

One IC contains the entire video and deflection processing

and builds the heart of a modern color TV. Its performance

and complexity allow the user to standardize

his product development. Hardware and software applications

can profit from the modularity as well as manufacturing,

system support or maintenance. The main

features are:

– low cost, high performance

– all digital video processing

– multi-standard color decoder PAL/NTSC/SECAM

– 3 composite, 1 S–VHS input

– integrated high-quality AD/DA converters

– sync and deflection processing

– luminance and chrominance features, e.g.

peaking, color transient improvement

– programmable RGB matrix

– various digital interfaces

– embedded RISC controller (80 MIPS)

– one crystal, few external components

– single power supply 5 V

– 0.8m CMOS Technology

– 68-pin PLCC or 64-pin Shrink DIL Package

1.1. System Architecture

Two main modules have been defined:

Video Processor and

Display Processor.

They are designed as silicon building blocks. Their partitioning

permits a variety of IC configurations with the aim

to satisfy the particular requirements of different applications.

Both, analog and digital interfaces, support

state of the art TV receivers as well as other environments.

Fig. 1–1 shows the block diagram of the singlechip

Video Processor which consists of both modules.

2. Functional Description

2.1. Analog Front End

This block provides the analog interfaces to all video inputs

and mainly carries out analog-to digital conversion

for the following digital video processing. A block diagram

is given in figure 2–1.

Most of the functional blocks in the front end are digitally

controlled (clamping, AGC and clock-DCO). The control

loops are closed by the Fast Processor (‘FP’) embedded

in the decoder.

2.1.1. Input Selector

Up to four analog inputs can be connected. Three inputs

are for input of composite video or S–VHS luma signal.

These inputs are clamped to the sync back porch and

are amplified by a variable gain amplifier. One input is

for connection of S–VHS carrier–chrominance signal.

This input is internally biased and has a fixed gain amplifier.

2.1.2. Clamping

The composite video input signals are AC coupled to the

IC. The clamping voltage is stored on the coupling capacitors

and is generated by digitally controlled current

sources. The clamping level is the back porch of the video

signal. S-VHS chroma is also AC coupled. The input

pin is internally biased to the center of the ADC input

range.

2.1.3. Automatic Gain Control

A digitally working automatic gain control adjusts the

magnitude of the selected baseband by +6/–4.5 dB in 64

logarithmic steps to the optimal range of the ADC .

The gain of the video input stage including the ADC is

213 steps/V for all three standards (PAL/NTSC/SECAM/

Y/C), with the AGC set to 0 dB.

2.1.4. Analog-to-Digital Converters

Two ADCs are provided to digitize the input signals.

Each converter runs with 20.25 MHz and has 8 bit resolution.

An integrated bandgap circuit generates the required

reference voltages for the converters.

The two ADCs are of a 2-stage subranging type.

---------------------------------------------------------------------------

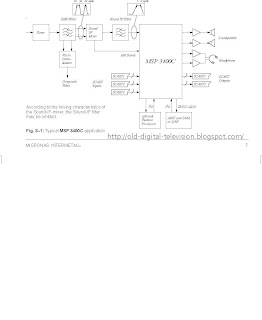

TOGHETHER WITH VIDEO PROCESSING THERE IS SOUND PROCESSING WITH MSP3400C

Multistandard Sound Processor

Release Notes: The hardware description in this

document is valid for the MSP 3400C – C8 and newer

codes. Revision bars indicate significant changes

to the previous version.

1. Introduction

The MSP 3400C is designed as single-chip Multistandard

Sound Processor for applications in analog and

digital TV sets, satellite receivers and video recorders.

The MSP-family, which is based on the MSP 2400, demonstrates

the progressive development towards highly

integrated multi-functional ICs.

The MSP 3400C, again, improves function integration:

The full TV sound processing, starting with analog

sound IF signal-in, down to processed analog AF-out, is

performed in a single chip. The IC is produced in 0.8 mm

CMOS technology, combined with high performance

digital signal processing.

The MSP 3400C 0.8 m CMOS version is fully pin and

software compatible to the 1.0 m MSP 3400 and MSP

3410. The main difference between the MSP 3400C and

the MSP 3410, consists of the MSP 3410 being able to

decode NICAM signals.

2. Features of the MSP 3400C:

2.1. Features of the Demodulator and Decoder

Sections

The MSP 3400C is designed to perform demodulation

of FM-mono TV sound and two carrier FM systems according

to the German or Korean terrestrial specs. With

certain constraints, it is also possible to do AM-demodulation

according to the SECAM system. Alternatively, the

satellite specs can be processed with the MSP 3400C.

For FM carrier detection in satellite operation, the AMdemodulation

offers a powerful feature to calculate the

carrier field strength, which can be used for automatic

search algorithms. So, the IC facilitates a first step towards

multistandard capability with its very flexible

application and may be used in TV-sets, satellite tuners,

and video recorders.

The MSP 3400C facilitates profitable multistandard capability,

offering the following advantages:

– two selectable analog inputs (TV and SAT-IF sources)

– Automatic Gain Control (AGC) for analog input: input

range: 0.14 – 3 Vpp

– integrated A/D converter for sound-IF inputs

– all demodulation and filtering is performed on chip and

is individually programmable

– no external filter hardware is required

– only one crystal clock (18.432 MHz) is necessary

– FM carrier level calculation for automatic search algorithms

and carrier mute function

– high deviation FM-mono mode (max. deviation:

approx. 360 kHz)

2.2. Features of the DSP-Section

– flexible selection of audio sources to be processed

– digital input and output interfaces via I2S-Bus for external

DSP-processors, surround sound, ADR etc.

– digital interface to process ADR (Astra Digital Radio)

together with DRP 3510 A

– performance of all deemphasis systems including

adaptive Wegener Panda 1 without external components

or controlling

– digitally performed FM-identification decoding and dematrixing

– digital baseband processing: volume, bass, treble,

5-band equalizer, loudness, pseudostereo, and basewidth

enlargement

– simple controlling of volume, bass, treble, equalizer

etc.

– increased audio bandwidth for FM-Audio-signals

(20 Hz – 15 kHz, 1 dB)

2.3. Features of the Analog Section

– three selectable analog pairs of audio baseband inputs

(= three SCART inputs)

input level: 32 V RMS,

input impedance: .25 kW

– one selectable analog mono input (i.e. AM sound),

input level: 32 V RMS,

input impedance: .10 kW

– two high quality A/D converters, S/N-Ratio: .85 dB

– 20 Hz to 20 kHz Bandwidth for SCART-to-SCARTCopy

facilities

– MAIN (loudspeaker) and AUX (headphones): two

pairs of 4-fold oversampled D/A-converters

output level per channel: max. 1.4 V RMS

output resistance: max. 5 kW

S/N-Ratio: .85 dB at maximum volume

max. noise voltage in mute mode: 310 mV (BW: 20 Hz

...16 kHz)

– one pair of four-fold oversampled D/A-converters supplying

two selectable pairs of SCART-Outputs. Output

level per channel: max. 2 V RMS, output resistance:

max. 0.5 kW, S/N-Ratio: .85 dB

(20 Hz...16 kHz).

LOEWE PROFIL PLUS 3472 E 3001 Super Flatline Art.No. 59433 L 00 CHASSIS E3001Switched-mode power supply control circuit: Siemens Function and Application of the Switch Mode Powersupply IC TDA4605;

a switch responsive to a first control signal having a controllable duty cycle and coupled to said source of input supply voltage for generating an output supply voltage, in accordance with said duty cycle of said first control signal;

a duty cycle modulator responsive

to a second control signal for generating said first control signal and

for controlling said duty cycle of said first control signal in

accordance therewith, said modulator being responsive to a signal that

is indicative of said input supply voltage for decreasing said duty

cycle when said input supply voltage increases; and

a duty cycle modulator responsive

to a second control signal for generating said first control signal and

for controlling said duty cycle of said first control signal in

accordance therewith, said modulator being responsive to a signal that

is indicative of said input supply voltage for decreasing said duty

cycle when said input supply voltage increases; and a limiter coupled to said modulator for limiting the decrease in duty cycle, for a given increase in said input supply voltage, when said input supply voltage exceeds a first magnitude.

2. A power supply according to claim 1, wherein said duty cycle of said first control signal varies within a control range, in accordance with said second control signal, and wherein said limiter limits a decrease of said duty cycle when said duty cycle is at an end of said control range.

3. A power supply according to claim 1, wherein said limiter comprises a clamper coupled in a signal path of said input supply voltage indicative signal for clamping said input voltage indicative signal, when said input supply voltage exceeds said first magnitude, and for disabling the clamping thereof, when said input supply voltage does not exceed said first magnitude.

4. A power supply according to claim 3, wherein said voltage clamper comprises a diode.

5. A power supply according to claim 3, further comprising a disabling circuit responsive to said input supply voltage indicative signal for disabling said output supply voltage, when said input supply voltage is smaller than a second magnitude and wherein said voltage clamper is coupled in a common signal path of said input supply voltage indicative signal with respect to each of an input of said disabling circuit and an input of said limiter.

6. A power supply according to claim 1, wherein said modulator comprises a foldback point corrector for decreasing said duty cycle, when said input supply voltage increases and wherein said limiter is coupled to said corrector.

7. A power supply according to claim 1, wherein said second control signal is produced in a feedback path for regulating said output supply voltage.

8. A power supply according to claim 1, wherein said input supply voltage indicative signal is coupled to said modulator from said source of input supply voltage via a signal path that bypasses said switch.

9. A power supply according to claim 8, wherein said limiter comprises a clamp coupled in said signal path for clamping said input supply voltage indicative signal, wh

en said input supply voltage

exceeds said first magnitude, and for disabling the clamping operation,

when said input supply voltage does not exceed said first magnitude.

en said input supply voltage

exceeds said first magnitude, and for disabling the clamping operation,

when said input supply voltage does not exceed said first magnitude.

10. A power supply, comprising: an input supply voltage, a transformer and a switch coupled for switch mode generation of a regulated output supply voltage, said switch being responsive to a first control signal having a controllable duty cycle;

a duty cycle modulator for generating said first control signal responsive to a second control signal for limiting a duty cycle of said switch, said modulator operating in a first mode when said second control signal is in a predetermined range of voltage levels and operating in a second mode when said second control signal is outside of said range; and

a voltage monitor circuit for generating said second control signal, said second control signal representing a first proportion of said input supply voltage in a first range of input supply voltage values and a second proportion of said input supply voltage in a second range of input supply voltage values.

11. A power supply according to claim 10 wherein said voltage monitor circuit comprises a clamp coupled in a signal path of said second control signal.

12. A power supply according to claim 11, wherein said second signal is coupled to said modulator from said input supply voltage via a signal path that bypasses said switch.

13. A power supply, comprising: an input supply voltage, a tran

sformer and a switch coupled for switch mode generation

of a regulated output supply voltage, said switch being responsive to a

first control signal having a controllable duty cycle;

sformer and a switch coupled for switch mode generation

of a regulated output supply voltage, said switch being responsive to a

first control signal having a controllable duty cycle; a duty cycle modulator for generating said first control signal responsive to a second control signal, said modulator operating in a first mode when said second control signal is in a predetermined range of voltage levels and operating in a second mode when said second control signal is outside of said range; and

a voltage monitor circuit for generating said second control signal, said second control signal representing a first proportion of said input supply voltage in a first range of input supply voltage values and a second proportion of said input supply voltage in a second range of input supply voltage values, such that as long as said input supply voltage is in said first range of input supply voltage values, said second control signal varies when said input supply voltage varies and said modulator operates in said first mode of operation.

14. A power supply, comprising: an input supply voltage, a transformer and a switch coupled for switch mode generation of a regulated output supply voltage, said switch being responsive to a first control signal having a controllable duty cycle;

a duty cycle modulator for generating said first control signal responsive to a second control signal, said modulator operating in a first mode when said second control signal is in a predetermined range of voltage levels and operating in a second mode when said second control signal is outside of said range; and

a nonlinear voltage divider circuit coupled to said input supply voltage for generating said second control signal, said second control signal representing a first proportion of said input supply voltage in a first range of input supply voltage values and a second proportion of said input supply voltage in a second range of input supply voltage values.

Switched-mode power supplies efficiently generate a variety of regulated voltages from a single line voltage level (e.g., 110 volts AC). One important use of these power supplies is within a television signal receiver where they are used to produce a regulated B+ voltage for the horizontal deflection circuit as well as other regulated voltages for powering various digital and analog circuits.

Typically, a switched-mode power supply contains a full-wave rectifier, a power supply controller, a switch, and an output transformer. The switch is typically a high-power transistor such as a MOSFET. To regulate the output voltages, the controller activates and deactivates (e.g., pulse width modulates) the gate of the transistor in response to power supply loading and other control parameters. The switched voltage from the transistor drives a primary winding of the transformer, while various power supply loads are connected to one or more secondary windings. As such, the power supply converts an AC input voltage into one or more DC voltages.

One particular controller is an integrated circuit available from Siemens as Model TDA 4605. This power supply controller is typically used to drive the MOSFET transistor, which in turn drives the primary coil of the transformer. This specific integrated circuit, as well as others used in the art, typically contain a control mechanism that disables the power supply when the input voltage drops below a pre-defined voltage level. Such protection is necessary because, to produce regulated output voltages, the switched-mode power supply increases the duty cycle of the control signal driving the transistor as the input voltage decreases. At some point, the input voltage decreases to a level where the output of the power supply is unregulated (e.g., the maximum pulse length is used to drive the transistor). Such unregulated operation can damage the power supply electronics, but is more likely to damage the load electronics.

For the integrated circuit (IC) TDA4605, as defined in the TDA4605 Technical Manual available from Siemens AG, dated Jul. 27, 1989, pin 3 of the integrated circuit is used for sensing or monitoring the primary input voltag

e (vp) for the power supply (e.g.,

the rectified AC voltage). The threshold voltage for disabling or

deactivating the integrated circuit, and thus the power supply, is

pre-established by the controller at one volt. As such, the primary

input voltage (vp) is reduced using a voltage divider at the input of

pin 3. By selecting appropriate resistor values within the voltage

divider, a nominal value of monitoring voltage is applied to pin 3.

Typically, this voltage is approximately 2.0 volts for a primary input

voltage of 120 volts. When the primary input voltage falls to a level

that causes the monitoring voltage at pin 3 to fall below one volt, the

power supply is deactivated to avoid unregulated operation.

e (vp) for the power supply (e.g.,

the rectified AC voltage). The threshold voltage for disabling or

deactivating the integrated circuit, and thus the power supply, is

pre-established by the controller at one volt. As such, the primary

input voltage (vp) is reduced using a voltage divider at the input of

pin 3. By selecting appropriate resistor values within the voltage

divider, a nominal value of monitoring voltage is applied to pin 3.

Typically, this voltage is approximately 2.0 volts for a primary input

voltage of 120 volts. When the primary input voltage falls to a level

that causes the monitoring voltage at pin 3 to fall below one volt, the

power supply is deactivated to avoid unregulated operation. As stated above, this form of switched-mode power supply has been finding use within television signal receivers. However, television receivers, in particular, present peculiar loading characteristics to a power supply. Specifically, a television receiver power supply is called upon to produce a regulated B+ voltage, typically of approximately 140 volts, as well as a low voltage DC level of 16 volts for powering all of the digital and analog circuitry within the receiver. When the television receiver is switched from stand-by to run mode, a heavy load is produced by the in-rush of current into filter capacitors connected to the regulated B+ voltage. This heavy load causes the power supply to temporarily operate in an unregulated (maximum pulse width) mode, and may cause the primary input voltage to drop to a low level. Furthermore, when the degaussing circuit is activated to degauss the cathode ray tube (CRT), the main AC supply voltage is depressed due to the substantial load presented by the degaussing circuit. Consequently, the drop in line voltage could typically cause the monitoring voltage to drop below the 1 volt, first threshold level, and as such, to disable the power supply.

Therefore, there it is desirable to produce a monitoring voltage indicative of the primary input voltage, but to insure that the power supply will not be deactivated for the expected heavy loads found in a television receiver.

The IC TDA 4605 includes a foldback point correction circuit that reduces the maximum duty cycle of the MOSFET control signal, when the monitoring voltage exceeds a second threshold level of approximately 1.7 V. The monitoring voltage is applied to the correction circuit also via pin 3.

In a circuit embodying an inventive feature, a resistive voltage divider that produces the monitoring input or sense signal from the primary input voltage is designed such that the first threshold level is not attained during the expected temporary loading of the primary input voltage. However, such a voltage divider results in a higher voltage being applied to the monitoring voltage input of the controller during normal operation of the power supply. As such, an increase of the primary input voltage to a higher level, which is still within the acceptable tolerance

range of the AC line voltage, can cause the

monitoring voltage to rise to a level that exceeds the second threshold

level at which the integrated circuit begins to limit the maximum duty

cycle of the control signal that controls the MOSFET, i.e., the

controller applies a foldback correction technique. When the second

threshold level is exceeded, the power supply automatically limits the

output power of the power supply for an increase in the primary voltage.

As a result of the voltage divider design that provides sufficient

headroom to overcome loading generated drop outs in the primary input

voltage, the maximum power supply output could be, undesirably,

significantly reduced at high primary input voltage.

range of the AC line voltage, can cause the

monitoring voltage to rise to a level that exceeds the second threshold

level at which the integrated circuit begins to limit the maximum duty

cycle of the control signal that controls the MOSFET, i.e., the

controller applies a foldback correction technique. When the second

threshold level is exceeded, the power supply automatically limits the

output power of the power supply for an increase in the primary voltage.

As a result of the voltage divider design that provides sufficient

headroom to overcome loading generated drop outs in the primary input

voltage, the maximum power supply output could be, undesirably,

significantly reduced at high primary input voltage. In carrying out an inventive feature, to insure that such inconsequential increase in the primary input voltage does not cause the power supply to significantly reduce the maximum duty cycle of the control signal and thereby, the power output of the power supply, a zener diode is coupled to the voltage divider. The zener diode limits the magnitude of the monitoring voltage to a level that avoids further maximum duty cycle limiting when the primary input voltage further increases. Consequently, w

hen the power supply is used in a television signal receiver, the

voltage divider provides enough head room for the primary voltage to

drop substantially due to degaussing circuit activation or other loading

conditions, while the zener diode insures that the primary voltage can

rise above its nominal voltage without causing a significant power

limitation of the power supply output.

hen the power supply is used in a television signal receiver, the

voltage divider provides enough head room for the primary voltage to

drop substantially due to degaussing circuit activation or other loading

conditions, while the zener diode insures that the primary voltage can

rise above its nominal voltage without causing a significant power

limitation of the power supply output. A switch mode power supply, embodying an aspect of the invention, includes a source of an input supply voltage. A switch is responsive to a first control signal having a controllable duty cycle and coupled to the source of input supply voltage for generating an output supply voltage, in accordance with the duty cycle of the first control signal. A duty cycle modulator is responsive to a second control signal for generating the first control signal and for controlling the duty cycle of the first control signal in accordance therewith in a manner to control the current pulses. An increase in the duty cycle produces an increase in a magnitude of the current pulses. The modulator is responsive to a signal that is indicative of the input supply voltage for decreasing the duty cycle when the input supply voltage increases. A limiter is coupled to the modulator for limiting the decrease in duty cycle, for a given increase in said input supply voltage, when the input supply voltage exceeds a first magnitude.

FIG. 1 depicts a schematic diagram of a switched-mode power supply incorporating the teachings of the present invention.

FIG.

1 depicts a schematic diagram of a switched-mode power supply 100

incorporating the present invention. The embodiment shown is designed

for use as a power supply for a television signal receiver, wherein the

power supply generates a regulated B+ voltage (e.g., 140 volts) and a

low voltage (e.g., 16 volts). The regulated B+ voltage is used to power a

horizontal deflection circuit and the regulated low voltage is used to

power the digital and analog electronics (continuous load 118). Other

applications for the power supply may require slight variation in the

depicted components and their interconnections; however, such variations

are well within the scope of the present invention.

FIG.

1 depicts a schematic diagram of a switched-mode power supply 100

incorporating the present invention. The embodiment shown is designed

for use as a power supply for a television signal receiver, wherein the

power supply generates a regulated B+ voltage (e.g., 140 volts) and a

low voltage (e.g., 16 volts). The regulated B+ voltage is used to power a

horizontal deflection circuit and the regulated low voltage is used to

power the digital and analog electronics (continuous load 118). Other

applications for the power supply may require slight variation in the

depicted components and their interconnections; however, such variations

are well within the scope of the present invention. The power supply contains a number of major components, including a full-wave rectifier 102, the power supply controller 106, a MOSFET transistor Q1, a monitor voltage generator 110, an output transformer 112, and a plurality of circuit components used to complete the power supply electronics. Illustratively, the input to the power supply is a 110-volt AC, 60 hertz voltage.

Rectifier 102 is a conventional full-wave bridge rectifier coupled to an AC input voltage source 101. The output of the bridge rectifier 102 is coupled to capacitor C1 approximately 680 μF). A voltage RAW B+ forms raw (unregulated) B+ voltage (also referred to herein as the primary input voltage vp) having a nominal value of approximately 150 volts. Capacitor C1, connected from the output of the rectifier to ground, smoothes the voltage from the bridge rectifier such that a DC voltage, i.e., the primary input voltage vp, is available at the upper terminal of the transformer's primary winding W1.

The primary input voltage forms an input to the monitor voltage generator 110 which produces a monitor voltage VZ1 for the controller 106. The monitor voltage generator is discussed in detail below.

The controller is illustratively a TDA 4605 power supply controller available from Siemens AG of Munich, Germany. The eight pins of the controller are connected to signals and voltages that enable the controller to produce a pulse width or duty cycle modulated signal at pin five for controlling the duty cycle of the transistor Q1. Specifically, pin 4 of controller 106 is grounded. Pin 3 is coupled to the monitor voltage.

Pin 2 is supplied information concerning the primary current. A primary current increase in the primary winding W1 is simulated as a voltage rise of a periodical, ramp voltage VC2 at pin 2 using an external RC element formed by resistor R3, capacitor C2, and resistor R4 (where R3 is approximatel

y 360 kΩ, C2 is approximately

6,800 pF; and R4 is approximately 220 Ω). These elements are connected

in series from the primary input voltage to ground. Pin 2 of the

controller 106 is coupled to the junction of R3 and C2. A pulse width

modulator 106c of the controller 106 controls the duration of the

forward phase, and thus, the primary peak current, using ramp voltage

VC2 that is proportional to the drain current of the transistor Q1. As

indicated before, the ramp voltage is derived from the primary input

voltage using the RC elements connected to pin 2, i.e., the ramp voltage

simulates the primary current. Controller pin 1 is supplied secondary

voltage information which internally compares the control voltage

sampled from the regulating winding W3 of the transformer 112 and

compares that sample voltage with an internal reference voltage.

y 360 kΩ, C2 is approximately

6,800 pF; and R4 is approximately 220 Ω). These elements are connected

in series from the primary input voltage to ground. Pin 2 of the

controller 106 is coupled to the junction of R3 and C2. A pulse width

modulator 106c of the controller 106 controls the duration of the

forward phase, and thus, the primary peak current, using ramp voltage

VC2 that is proportional to the drain current of the transistor Q1. As

indicated before, the ramp voltage is derived from the primary input

voltage using the RC elements connected to pin 2, i.e., the ramp voltage

simulates the primary current. Controller pin 1 is supplied secondary

voltage information which internally compares the control voltage

sampled from the regulating winding W3 of the transformer 112 and

compares that sample voltage with an internal reference voltage. Pin 5 generates a duty cycle modulated control signal or voltage VOUT via a push-pull output driver for rapid charge and discharge of the input capacitance of a MOSFET power transistor Q1 (Model IRF740).

Pin 6 is coupled to the supply voltage for the controller. Pin 7 forms a soft start input terminal. Capacitor C5 (0.1 μF) is connected from pin 7 to ground to reduce the pulse duration during start-up. Lastly, pin 8 is the input pin for the oscillator feedback.

In operation, the transistor Q1 is used as a power switch controlled by the controller 106. A snubber circuit is connected to the drain of the transistor Q1. The snubber circuit contains a combination of diode D3, resistor R16 and capacitor C12, which together limit the voltage overshoot when the transistor is turned off. D3 is a MUR450 diode, C12 is a 1000 pF capacitor, and R16 is a 2-watt, 30 kΩ resistor.

Together with the stray capacitance of the transformer, capacitor C7 (470 pF connected from drain terminal to ground) determines the no-load frequency, and consequently, the maximum slew rate of the drain voltage for a transistor Q1.

Transistor Q1 is driven with pulse width modulated signal VOUT produced at pin 5 of controller 106 and coupled to the gate terminal of the transistor via resistor R11 (35 Ω). Furthermore, a capacitor C6 (4700 pF) is coupled from the source terminal to the drain terminal. The source terminal is coupled to ground through resistor R13 (0.27 KΩ). Resisto

r R12 (10 kΩ) is optionally connected between the

source terminal and gate terminal to ensure that the transistor will not

be activated if power is applied to the power supply without the

controller 106 being installed. The drain terminal is coupled to one

terminal of the primary winding W1 of transformer 112. Consequently, the

transistor Q1 controls the current flow from the primary input voltage

through the primary winding.

r R12 (10 kΩ) is optionally connected between the

source terminal and gate terminal to ensure that the transistor will not

be activated if power is applied to the power supply without the

controller 106 being installed. The drain terminal is coupled to one

terminal of the primary winding W1 of transformer 112. Consequently, the

transistor Q1 controls the current flow from the primary input voltage

through the primary winding. The secondary circuit of the transformer 112 consists of several windings, each of which has a different number of turns, polarity, and load capacity. Specifically, winding W2 forms the output voltage for the regulated B+, while winding W4 forms the output winding for the regulated 16-volt low voltage output, and winding W3 generates the feedback voltage for the controller 106.

The load circuitry includes, connected to winding W2, an output diode D4 and capacitor C13 that couple power to the horizontal deflection circuit 116. Additionally, the center tap of the output secondary winding is connected to ground, and winding W4 is coupled to diode D5 and capacitor C14. This output is the 16 volts that powers the continuous load 118 of the television receiver, e.g., all of the electronics and integrated circuits. This circuit 118 also controls the timing of when the degaussing circuit 114 is activated using degaussing control line 120. The control line for the continuous load is the run/standby control signal that essentially turns the television receiver on and off. The continuous load circuitry 118 is also coupled to the horizontal deflection circuit 116 to provide control signals therefor.

The controller 106 is started up using resistor R17 (100 KΩ) as a start resistor. As such, cap

acitor C11 (100 μF) is charged

with half-wave currents at the voltage supply pin of the controller

106, e.g., pin 6. These half-wave currents are supplied from the primary

input voltage through resistor R17 (100 KΩ) to ground through series

connected resistor R14 (202 Ω), diode D2 (148 Ω) and regulating winding

W3. When the voltage at C11 reaches the switch-on threshold, the

switched-mode power supply begins to function and supplies the feedback

voltage, via winding W3, resistor R14 and diode D2. This feedback

voltage, when rectified by diode D2 and smoothed by capacitor C11, forms

the supply voltage (vcc) for the controller 106 via pin 6.

acitor C11 (100 μF) is charged

with half-wave currents at the voltage supply pin of the controller

106, e.g., pin 6. These half-wave currents are supplied from the primary

input voltage through resistor R17 (100 KΩ) to ground through series

connected resistor R14 (202 Ω), diode D2 (148 Ω) and regulating winding

W3. When the voltage at C11 reaches the switch-on threshold, the

switched-mode power supply begins to function and supplies the feedback

voltage, via winding W3, resistor R14 and diode D2. This feedback

voltage, when rectified by diode D2 and smoothed by capacitor C11, forms

the supply voltage (vcc) for the controller 106 via pin 6. A control signal or voltage VCT for pin 1 is generated in a circuit parallel to the controller supply voltage circuit. The control voltage is produced by diode D1 (ERB43) charging capacitor C3 (1.5 μF) through resistor R8 (10 Ω). The RC element, consisting of series connected R15 (30 Ω) and C10 (0.01 μF), prevents peak value rectification of high frequency components of the feedback signal.

More specifically, regulating winding W3 is coupled to one terminal of resistor R15. The other terminal of resistor R15 is coupled to capacitor C10 to ground. Diode D1 is connected at the junction of resistor R15 and capacitor C10. Capacitor C9 (1000 pF) is connected in parallel with diode D1. Diode D1 has an output voltage that is coupled to series connected R8 and C3 which couples the output of the diode to ground. The output of the diode is also coupled through resistive divider network R6 and R7 which are respectively connected in series to ground. The voltage at the junction of R6 and R7 forms control voltage VCT and is coupled to pin 1 of the controller 106. These resistors define the no-load frequency of oscillation of the controller 106. Therefore, they are typically 0.1% accurate resistors having R6 being 5.49 KΩ, and R7 being 174 Ω. Control voltage VCT is coupled to a pulse-width modulator 106c within controller 106 that co

ntrols the duty cycle modulation of voltage VOUT for

regulating, for example, voltage REGB+.

ntrols the duty cycle modulation of voltage VOUT for

regulating, for example, voltage REGB+. During the power supply start-up, capacitor C5 at the soft-start pin (e.g., pin 7), influences the duration of the forward phase by controlling the error voltage of the pulse width modulator. The controller detects the end of the transformer discharge phase via resistor R10 (20 KΩ) that is coupled at one end to controller pin 8 and at the other end to resistor R14, and ultimately to the regulating winding W3. Additionally, capacitor C8 (0.022 μF) is coupled from the junction of R10 and R14 to ground. At this point, the voltage changes polarity from positive to negative, i.e., the voltage represents zero crossings.

A voltage VZ1, embodying an inventive feature, is generated by the monitor voltage generator 110 and is coupled to pin 3 of the controller 106. Voltage VZ1 is used both for determining the minimum line voltage that will allow the power supply to operate and for controlling a foldback point correction circuit 106b within the controller 106.

The monitor voltage generator 110 contains resistor R1 (270 kΩ) coupled in series with resistor R2 (5100 Ω) to form a resistive voltage divider network with respect to primary input voltage RAW B+. The junction of the two resistors is coupled to the pin 3 of controller 106. Furthermore, a zener diode Z1 (B2X55/C3VO), embodying an inventive feature, is connected in parallel with resistor R2 from the junction point to ground. Zener diode Z1 forms a limiter for limiting the maximum voltage across R2 to the breakdown voltage of the zener diode Z1. Consequently, the voltage at the output of the monitor voltage generator 110 tracks the primary input voltage RAW B+ up to the threshold point where the zener diode Z1 begins to conduct.

The controller 106 includes an under-voltage detector 106a that uses a fixed, internal voltage threshold that causes the controller to disable the power supply whenever the monitor voltage VZ1 drops below a first threshold voltage. For the TDA 4605 integrated circuit, this first threshold voltage is one volt. As such, the divider network of R1 and R2 defines a voltage at the output that under typical operation would not cause the controller to deactivate the power supply.

In one particular application, e.g., a television signal receiver, a degaussing circuit 114 for a television signal receiver is typically connected directly across the input AC power. Consequently, when the degaussing circuit is activated, it will typically cause a drop in the AC voltage that is applied to the input of the voltage rectifier 102. Consequently, the primary input voltage RAW B+ will drop significantly during the degaussing period. Since this is a normal behavior of a conventional television receiver circuit, it is desirable that the monitor voltage generator 110 be designed such that the controller 106 will not deactivate the power supply during the degaussing period.

For a primary input voltage of 120 volts and using a resistive divider of 270 KΩ for R1 and 5100 Ω for R2, the nominal voltage VZ1 at the voltage monitor input pin is 2 volts. Such a value for the voltage monitor voltage will avoid power supply deactivation during the degaussing period or other heavy load period.

When the duty cycle of voltage VOUT is at the maximum as a result of an overload condition, an increase in voltage RAW B+, produced by an increase in the AC line voltage, causes the voltage across primary winding w1 to increase. As the primary input voltage RAW B+ rises, the available input power to the power supply increases which could damage the power supply when the power supply is overloaded. During a period of overloaded, unregulated output, the modulator 106c generates the voltage VOUT having a maximum duty cycle for driving transistor Q1. As a result, a primary current IP in winding W1 of transformer 112 has also a maximum duty cycle. Therefore, undesirably an increase in voltage RAW B+ can produce a large voltage across the transistor that could damage the transistor or other circuitry.

To maintain the power supply within a safe operation range, the controller 106 includes what is known as a foldback or overload point correction circuit 106b. This foldback point correction circuit reduces the maximum duty cycle of voltage VOUT when the primary input voltage exceeds a predetermined magnitude. An increase above the predetermined magnitude causes the foldback point correction circuit 106b to decrease the maximum duty cycle of signal VOUT as voltage RAW B+ increases. The decrease is done by generating a correction curren

t ICOR

that is coupled to capacitor C2 causing an increase in the rate of

change of voltage VC2 at pin 2 of controller 106 when voltage VZ1

exceeds a second threshold voltage.

t ICOR

that is coupled to capacitor C2 causing an increase in the rate of

change of voltage VC2 at pin 2 of controller 106 when voltage VZ1

exceeds a second threshold voltage. When voltage RAW B+ increases and causes voltage VZ1 to further increase above the second threshold voltage an increase in current ICOR produces a decrease in the maximum duty cycle of signal VOUT, in a well know manner. The second threshold voltage occurs when voltage VZ1 is above a voltage level of approximately 1.7 V. The result is that, when voltage RAW B+ further increases the maximum duty cycle decreases proportionally. The decrease in the maximum duty cycle tends to stabilize the maximum power produced in the power supply against an increase of voltage RAW B+. On the other hand, an increase of voltage VZ1 when voltage VZ1 is below the 1.7 V level, does not affect current ICOR and the duty cycle of voltage VOUT.

Because the divider network (R1 and R2) establishes a sufficiently large monitor voltage VZ1 that provides sufficient headroom for preventing power supply shutdown when the degaussing circuit is activated, primary input voltage RAW B+ may be at a level that causes voltage VZ1 to exceed the second threshold voltage of circuit 106b by an excessive amount even when voltage RAW B+ is within the normal tolerance range. Therefore, disadvantageously, the maximum duty cycle may further decrease by a significant amount in a manner to lower the maximum power that can be derived. Such significant reduction in power capability can occur even though primary input voltage is not truly at such a high level that could damage the power supply.

In accordance with an inventive feature, to prevent current ICOR from further reducing the maximum duty cycle of voltage VOUT when voltage RAW B+ increases above a threshold magnitude that corresponds to voltage VZ1 being equal to 3 V, the monitor voltage generator 110 contains the zener diode Z1 operating as a limiter which limits the primary input voltage indicative voltage VZ1 to 3 V. Consequently, the monitor voltage VZ1 can never rise above a pre-defined level (e.g., 3 volts) that would otherwise cause the foldback point correction circuit 106b within the controller 106 to further decrease the maximum duty cycle. In this way, advantageously, the decrease in the maximum duty cycl

e as a function of an increase in

voltage RAW B+ is limited.

e as a function of an increase in

voltage RAW B+ is limited. The decrease in the duty cycle of voltage VOUT produced by current ICOR, for a given increase in voltage RAW B+, is limited when voltage RAW B+ is greater than a threshold magnitude that corresponds to voltage VZ1 equal to 3 V. In contrast, the decrease in the duty cycle produced by current ICOR is not limited but varies proportionally to voltage RAW B+ when voltage VZ1 is between 1.7 V and 3 V. Thus, zener diode Z1 operates as a limiter for limiting the decrease in the duty cycle when the voltage RAW B+ exceeds the threshold magnitude relative to when voltage RAW B+ does not exceed the threshold magnitude. An increase in voltage RAW B+ that produces voltage VZ1 below the second threshold voltage of 1.7 V, does not affect current ICOR.

Specifically, for the TDA 4605 integrated circuit control, the zener diode has a value of three volts. Consequently, the input signal to the monitor voltage generator cannot rise above the three volt level before the zener diode will begin to conduct current to ground. As such, the monitor voltage generator establishes a range of voltages that pre-defines a range of primary input voltages at which the controller 106 operates in a normal manner that avoids both an undervoltage power supply deactivation and a further decrease in the maximum duty cycle. The input voltage dynamic range is thereby extended.

LOEWE PROFIL PLUS 3472 E 3001 Super Flatline Art.No. 59433 L 00 CHASSIS E3001 TDA 4605-3 Control IC for Switched-Mode Power Supplies usingMOS-Transistor

The IC TDA 4605-3 controls the MOS-power transistor and performs all necessary control and

The IC TDA 4605-3 controls the MOS-power transistor and performs all necessary control andprotection functions in free running flyback converters. Because of the fact that a wide load range

is achieved, this IC is applicable for consumer as well as industrial power supplies.

The serial circuit and primary winding of the flyback transformer are connected in series to the input

voltage. During the switch-on period of the transistor, energy is stored in the transformer. During the

switch-off period the energy is fed to the load via the secondary winding. By varying switch-on time

of the power transistor, the IC controls each portion of energy transferred to the secondary side

such that the output voltage remains nearly independent of load variations. The required control

information is taken from the input voltage during the switch-on period and from a regulation winding

during the switch-off period. A new cycle will start if the transformer has transferred the stored

energy completely into the load.

In the different load ranges the switched-mode power supply (SMPS) behaves as follows:

No load operation

The power supply is operating in the burst mode at typical 20 to 40 kHz. The output voltage can be

a little bit higher or lower than the nominal value depending of the design of the transformer and the

resistors of the control voltage divider.

Nominal operation

The switching frequency is reduced with increasing load and decreasing AC-voltage.

The output voltage is only dependent on the load.

Overload point

Maximal output power is available at this point of the output characteristic.

Overload

The energy transferred per operation cycle is limited at the top. Therefore the output voltages

declines by secondary overloading.

Circuit Description

Application Circuit

The application circuit shows a flyback converter for video recorders with an output power rating of

70 W. The circuit is designed as a wide-range power supply for AC-line voltages of 180 to 264 V.

The AC-input voltage is rectified by the bridge rectifier GR1 and smoothed by C1 . The NTC limits

the rush-in current.

In the period before the switch-on threshold is reached the IC is suppled via resistor R 1 ; during the

start-up phase it uses the energy stored in C2 , under steady state conditions the IC receives its

supply voltage from transformer winding n1 via diode D1. The switching transistor T1 is a BUZ 90.

The parallel connected capacitor C3 and the inductance of primary winding n 2 determine the

system resonance frequency. The R 2-C4-D2 circuitry limits overshoot peaks, and R 3 protects the

gate of T1 against static charges.

During the conductive phase of the power transistor T1 the current rise in the primary winding

depends on the winding inductance and the mains voltage. The network consisting of R 4-C5 is used

to create a model of the sawtooth shaped rise of the collector current. The resulting control voltage

is fed into pin 2 of the IC. The RC-time constant given by R 4-C5 must be designed that way that

driving the transistor core into saturation is avoided.

The ratio of the voltage divider R 10/R 11 is fixing a voltage level threshold. Below this threshold the

switching power supply shall stop operation because of the low mains voltage. The control voltage

present at pin 3 also determines the correction current for the fold-back point. This current added to

the current flowing through R 4 and represents an additional charge to C5 in order to reduce the turnon

phase of T1. This is done to stabilize the fold-back point even under higher mains voltages.

Regulation of the switched-mode power supplies via pin 1. The control voltage of winding n1 during

the off period of T1 is r

ectified by D3, smoothed by C6 and stepped down at an adjustable ratio by

ectified by D3, smoothed by C6 and stepped down at an adjustable ratio byR 5 , R 6 and R 7 . The R 8-C7 network suppresses parasitic overshoots (transformer oscillation). The

peak voltage at pin 2, and thus the primary peak current, is adjusted by the IC so that the voltage

applied across the control winding, and hence the output voltages, are at the desired level.

When the transformer has supplied its energy to the load, the control voltage passes through zero.

The IC detects the zero crossing via series resistors R 9 connected to pin 8. But zero crossings are

also produced by transformer oscillation after T1 has turned off if output is short-circuited. Therefore

the IC ignores zero crossings occurring within a specified period of time after T1 turn-off.

The capacitor C8 connected to pin 7 causes the power supply to be started with shorter pulses to

keep the operating frequency outside the audible range during start-up.

On the secondary side, five output voltages are produced across winding n3 to n7 rectified by D4 to

D8 and smoothed by C9 to C13 . Resistors R 12 , R 14 and R 19 to R 21 are used as bleeder resistors.

Fusable resistors R 15 to R 18 protect the rectifiers against short circuits in the output circuits, which

are designed to supply only small loads.

Pin 1

The regulating voltage forwarded to this pin is compared with a stable internal reference voltage VR

in the regulating and overload amplifier. The output of this stage is fed to the stop comp

arator. If

arator. Ifthe control voltage is rather small at pin 1 an additional current is added by means of current source

which is controlled according the level at pin 7. This additional current is virtually reducing the

control voltage present at pin 1.

Pin 2

A voltage proportional to the drain current of the switching transistor is generated there by the

external RC-combination in conjunction with the primary current transducer. The output of this

transducer is controlled by the logic and referenced to the internal stable voltage V2B . If the voltage

V2 exceeds the output voltage of the regulations amplifier, the logic is reset by the stop comparator

and consequently the output of pin 5 is switched to low potential. Further inputs for the logic stage

are the output for the start impulse generator with the stable reference potential VST and the

supply voltage motor.

Pin 3

The down divided primary voltage applied there stabilizes the overload point. In addition the logic is

disabled in the event of low voltage by comparison with the internal stable voltage VV in the primary

voltage monitor block.

Pin 4

Ground

Pin 5

In the output stage the output signals produced by the logic are shifted to a level suitable for MOSpower

transistors.

Pin 6

From the supply voltage V6 are derived a stable internal references VREF and the switching

threshold V6A , V6E , V6 max and V6 min for the supply voltage monitor. All references values (VR ,

V2B , VST) are derived from VREF . If V6 > VVE , the VREF is switched on and switched off when V6 <

V 6A . In addition, the logic is released only for V6 min < V6 < V6 max .

Pin 7

The output of the overload amplifier is connected to pin 7. A load on this output causes a reduction

in maximal impulse duration. This function can be used to implement a soft start, when pin 7 is

connected to ground by a capacitor.

Pin 8

The zero detector controlling the logic block recognizes the transformer being discharged by

positive to negative zero crossing of pin 8 voltage and enables the logic for a new pulse. Parasitic

oscillations occurring at the end of a pulse cannot lead to a new pulse (double pulsing), because an

internal circuit inhibits the zero detector for a finite time tUL after the end of each pulse.

Start-Up Behaviour

The start-up behaviour of the

application circuit per sheet 88 is represented an sheet 90 for a line

application circuit per sheet 88 is represented an sheet 90 for a linevoltage barely above the lower acceptable limit time t0 the following voltages built up:

– V6 corresponding to the half-wave charge current over R1

– V2 to V2 max (typically 6.6 V)

– V3 to the value determined by the divider R 10/R 11 .

The current drawn by the IC in this case is less than 1.6 mA.

If V6 reaches the threshold V6E (time point t1), the IC switches on the internal reference voltage. The

current draw max. rises to 12 mA. The primary current- voltage reproducer regulates V2 down to V2B

and the starting impulse generator generates the starting impulses from time point t5 to t6 . The

feedback to pin 8 starts the next impulse and so on. All impulses including the starting impulse are

controlled in width by regulating voltage of pin 1. When switching on this corresponds to a shortcircuit

event, i.e. V1 = 0. Hence the IC starts up with "short-circuit impulses" to assume a width

depending on the regulating voltage feedback (the IC operates in the overload range). The IC

operates at the overload point. Thereafter the peak values of V2 decrease rapidly, as the starting

attempt is aborted (pin 5 is switched to low). As the IC remains switched on, V6 further decreases

to V6 . The IC switches off; V6 can rise again (time point t4) and a new start-up attempt begins at

time point t1 . If the rectified alternating Iine voltage (primary voltage) collapses during load, V3 can

fall below V3A , as is happening at time point t3 (switch-on attempt when voltage is too low). The

primary voltage monitor then clamps V3 to V3S until the IC switches off (V6 < V6A). Then a new startup

attempt begins at time point t1 .

Regulation, Overload and No-Load Behaviour

When the IC has started up, it is operating in the regulation range. The potential at pin 1 typically is

When the IC has started up, it is operating in the regulation range. The potential at pin 1 typically is400 mV. If the output is loaded, the regulation amplifier allows broader impulses (V5 = H). The peak

voltage value at pin 2 increases up to V2S max . If the secondary load is further increased, the

overload amplifier begins to regulate the pulse width downward. This point is referred to as the

overload point of the power supply. As the IC-supply voltage V6 is directly proportional to the

secondary voltage, it goes down in accordance with the overload regulation behaviour. If V6 falls

below the value V6 min , the IC goes into burst operation. As the time constant of the half-wave

charge-up is relatively large, the short-circuit power remains small. The overload amplifier cuts back

to the pulse width tpk . This pulse width must remain possible, in order to permit the IC to start-up

without problems from the virtual short-circuit, which every switching on with V1 = 0 represents. If

the secondary side is unloaded, the loadin

g impulses (V5 = H) become shorter. The frequency

g impulses (V5 = H) become shorter. The frequencyincreases up to the resonance frequency of the system. If the load is further reduced, the secondary

voltages and V6 increase. When V6 = V6 max the logic is blocked. The IC converts to burst

operation.This renders the circuit absolutely safe under no-load conditions.

Behaviour when Temperature Exceeds Limit

An integrated temperature protection disables the logic when the chip temperature becomes too

high. The IC automatically interrogates the temperature and starts as soon as the temperature

decreases to permissible values.

TDA8175 TV VERTICAL DEFLECTION OUTPUT CIRCUITPOWER AMPLIFIER

.FLYBACK GENERATOR

.AUTOMATIC PUMPING COMPENSATION

.THERMAL PROTECTION

.REFERENCE VOLTAGE

DESCRIPTION

The TDA8175 is a monolithic integrated circuit in

HEPTAWAT

T package. It is a high efficiency power

T package. It is a high efficiency powerbooster for direct driving of vertical windings of TV

yokes. It is intended for use in Color and B & W

television sets as well as in monitors and displays. THERMAL PROTECTION

The thermal protection circuit intervenes when the

die temperatures reaches 150oC and turns-off the

output power device.

PUMPING COMPENSATION

The device incorporatesa special preampliflier, the

gain of which varies withchanges in supplyvoltage.

This functionallows perfect compensationof height

variations caused by changes in brightness.

TDA7262 20+20W STEREO AMPLIFIER WITH STAND-BYWIDE SUPPLY VOLTAGE RANGE

HIGH OUTPUT POWER

28+28W TYP. MUSIC POWER

20+20W@THD = 10%, RL = 4W, VS = 28V

HIGHCURRENT CAPABILITY (UP TO 3.5A)

STAND-BY FUNCTION

AC SHORT CIRCUIT PROTECTION

THERMAL OVERLOAD PROTECTION

DESCRIPTION

The TDA7262 is class AB dual Hi-Fi Audio power

amplifier assembled in Multiwatt package, specilally

designed for high quality stereo application

as Hi-Fi music centers and TV sets.

BUILD-IN PROTECTION SYSTEMS

Thermal shut-down

The presence of a thermal limiting circuit offers

the following advantages:

1) an overload on the output (even if it is permanent),

or an excessive ambient temperature

can be easily withstood.

2) the heatsink can have a smaller factor of

safety compared with that o

f a conventional

f a conventionalcircuit. There is no device damage in the case

of excessive junction temperature; all that

happens is that PO ( and therefore Ptot) and

IO are reduced. The maximum allowable

power dissipation depends upon the size of

the external heatsink (i.e. its thermal resistance);

Figure 12 shows this dissipable power

as a function of ambient temperature for different

thermal resistance.

Short circuit (AC Conditions)

The TDA7262 can withstand accidental short circuits

across the speaker made by a wrong connection

during normal play operation.

-----------------------------------------------------------------------------

No comments:

Post a Comment

The most important thing to remember about the Comment Rules is this:

The determination of whether any comment is in compliance is at the sole discretion of this blog’s owner.

Comments on this blog may be blocked or deleted at any time.

Fair people are getting fair reply. Spam and useless crap and filthy comments / scrapers / observations goes all directly to My Private HELL without even appearing in public !!!

The fact that a comment is permitted in no way constitutes an endorsement of any view expressed, fact alleged, or link provided in that comment by the administrator of this site.

This means that there may be a delay between the submission and the eventual appearance of your comment.

Requiring blog comments to obey well-defined rules does not infringe on the free speech of commenters.

Resisting the tide of post-modernity may be difficult, but I will attempt it anyway.

Your choice.........Live or DIE.

That indeed is where your liberty lies.

Note: Only a member of this blog may post a comment.