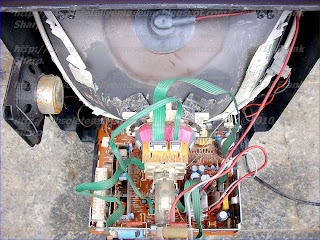

The PHILIPS CHASSIS CP90 was fitted from 15 to 21 Inches television sets in many various models types.

It was reliable except for the Line deflection output EHT Transformer which was failing often, and for some dry joints around the power parts and of course the NiCd backup battery.

I've noticed that if they were hardly used (10 or more hours per day) the were more reliable than one used few or less hours a day.

The PHILIPS CHASSIS CP90 is indeed compact and seems simple, but is not so simple as is.

Some times repairing it can be time consuming work and you have to know how it runs.

TDA3561A PAL decoderGENERAL DESCRIPTION

The TDA3561A is a decoder for the PAL colour television standard. It combines all functions required for the identification

The TDA3561A is a decoder for the PAL colour television standard. It combines all functions required for the identificationand demodulation of PAL signals. Furthermore it contains a luminance amplifier, an RGB-matrix and amplifier. These

amplifiers supply output signals up to 5 V peak-to-peak (picture information) enabling direct drive of the discrete output

stages. The circuit also contains separate inputs for data insertion, analogue as well as digital, which can be used for

text display systems (e.g. (Teletext/broadcast antiope), channel number display, etc. Additional to the TDA3560, the

circuit includes the following features:

· The peak white limiter is only active during the time that the 9,3 V level at the output is exceeded. The start of the

limiting function is delayed by one line period. This avoids peak white limiting by test patterns which have abrupt

transitions from colour to white signals.

· The brightness control is obtained by inserting a variable pulse in the luminance channel. Therefore the ratio of

brightness variation and signal amplitude at the three outputs will be identical and independent of the difference in gain

of the three channels. Thus discolouring due to adjustment of contrast and brightness is avoided.

· Improved suppression of the internal RGB signals when the device is switched to external signals, and vice versa.

· Non-synchronized external RGB signals do not disturb the black level of the internal signals.

· Improved suppression of the residual 4,4 MHz signal in the RGB output stages.

· Cascoded stages in the demodulators and burst phase detector minimize the radiation of the colour demodulator

inputs.

· High current capability of the RGB outputs and the chrominance output.

APPLICATION INFORMATION

The function is described against the corresponding pin

number.

1. + 12 V power supply

The circuit gives good operation in a supply voltage range

between 8 and 13,2 V provided that the supply voltage for

the controls is equal to the supply voltage for the

TDA3561A. All signal and control levels have a linear

dependency on the supply voltage. The current taken by

the device at 12 V is typically 85 mA. It is linearly

dependent on the supply voltage.

2. Control voltage for identification

This pin requires a detection capacitor of about 330 nF for

correct operation. The voltages available under various

signal conditions are given in the specification.

3. Chrominance input

The chroma signal must be a.c.-coupled to the input.

Its amplitude must be between 55 mV and 1100 mV

peak-to-peak (25 mV to 500 mV peak-to-peak burst

signal). All figures for the chroma signals are based on a

colour bar signal with 75% saturation, that is the

burst-to-chroma ratio of the input signal is 1 : 2,25.

4. Reference voltage A.C.C. detector

This pin must be decoupled by a capacitor of about 330

nF. The voltage at this pin is 4,9 V.

5. Control voltage A.C.C.

The A.C.C. is obtained by synchronous detection of the

burst signal followed by a peak detector. A good noise

immunity is obtained in this way and an increase of the

colour for weak input signals is prevented. The

recommended capacitor value at this pin is 2,2 mF.

6. Saturation control

The saturation control range is in excess of 50 dB.

The control voltage range is 2 to 4 V. Saturation control is

a linear function of the control voltage.

When the colour killer is active, the saturation control

voltage is reduced to a low level if the resistance of the

external saturation control network is sufficiently high.

Then the chroma amplifier supplies no signal to the

demodulator. Colour switch-on can be delayed by proper

choice of the time constant for the saturation control

setting circuit.

W

hen the saturation control pin is connected to the power

hen the saturation control pin is connected to the powersupply the colour killer circuit is overruled so that the colour

signal is visible on the screen. In this way it is possible to

adjust the oscillator frequency without using a frequency

counter (see also pins 25 and 26).

7. Contrast control

The contrast control range is 20 dB for a control voltage

change from + 2 to + 4 V. Contrast control is a linear

function of the control voltage. The output signal is

suppressed when the control voltage is 1 V or less. If one

or more output signals surpasses the level of 9 V the peak

white limiter circuit becomes active and reduces the output

signals via the contrast control by discharging C2 via an

internal current sink.

8. Sandcastle and field blanking input

The output signals are blanked if the amplitude of the input

pulse is between 2 and 6,5 V. The burst gate and clamping

circuits are activated if the input pulse exceeds a level of

7,5 V.

The higher part of the sandcastle pulse should start just

after the sync pulse to prevent clamping of video signal on

the sync pulse. The width should be about 4 ms for proper

A.C.C. operation.

9. Video-data switching

The insertion circuit is activated by means of this input by

an input pulse between 1 V and 2 V. In that condition, the

internal RGB signals are switched off and the inserted

signals are supplied to the output amplifiers. If only normal

operation is wanted this pin should be connected to the

negative supply. The switching times are very short

(< 20 ns) to avoid coloured edges of the inserted signals

on the screen.

10. Luminance signal input

The input signal should have a peak-to-peak amplitude of

0,45 V (peak white to sync) to obtain a black-white output

signal to 5 V at nominal contrast. It must be a.c.-coupled to

the input by a capacitor of about 22 nF. The signal is

clamped at the input to an internal reference voltage.

A 1 kW luminance delay line can be applied because the

luminance input impedance is made very high.

Consequently the charging and discharging currents of the

coupling capacitor are very small and do not influence the

signal level at the input noticeably. Additionally the

coupling capacitor value may be small.

PHILIPS 15CE1510 /08B TXT CARRA' CHASSIS CP90 Switched-mode self oscillating supply voltage circuit:POWER SUPPLY (PHILIPS SOPS - Self Oscillating Power Supply)

A switched-mode self-oscillating supply voltage circuit for converting an input voltage into an output d.c. voltage which is substantially independent of variations of the input voltage and/or a load connected to the output voltage. The circuit comprises a first controllable switch connected in series with a transformer winding and a second controllable switch for turning-off the first switch. The conduction period of the first switch is controlled by means of a control voltage present on a control electrode of the second switch. The circuit can be switched-over to a stand-up state in which the energy supplied to the load is reduced to zero. A starting network is connected bet

ween

the input voltage and the second switch so that the current therein

flows through the second switch during the period of time this switch

conducts and does not flow to the control electode of the first switch

in the stand-by state.

ween

the input voltage and the second switch so that the current therein

flows through the second switch during the period of time this switch

conducts and does not flow to the control electode of the first switch

in the stand-by state.1. A switched-mode self-oscillating supply voltage circuit for converting an input voltage into an output d.c. voltage which is substantially independent of variations of the input voltage and/or of a load connected to the terminals of the output voltage, comprising a transformer having a primary and a feedback winding, a first controllable switch connected in series with the primary winding, the series arrangement thus formed being coupled between terminals for the input voltage, a second controllable switch coupled via a turn-off capacitor to the control electrode of the first switch to turn it off, means coupling the feedback winding to said control electrode, a transformer winding being coupled via a rectifier to an output capacitor having terminals which supply the output voltage, an output voltage-dependent control voltage being present on a control electrode of the second switch for controlling the conduction period of the first switch, the circuit being switchable between an operating state and a stand-by state in which relative to the operating state the supply energy supplied to the load is considerably reduced, a starting network connected to a terminal for the input voltage, means for adjusting the control voltage in the stand-by state to a value at which the first controllable switch is cut-off, a connection which carries current during the conduction period for the second controllable switch being provided between the starting network and said second switch, and means providing a connection between the starting network and the control electrode of the first switch, which connection does not carry current in the stand-by state.

2. A supply voltage circuit as claimed in claim 1, further comprising a resistor included between the connection of the starting network to the second switch and a turn-off capacitor present in the connection to the control electrode of the first switch.

3. A supply voltage circuit as claimed in claim 2, characterized in that the second controllable switch comprises a thyristor having a main current path included in the control electrode connection of the first controllable switch, said thyristor having a first control gate electrode for adjusting the turn-off instant of the first switch and a second control electrode to which the starting network and the resistor are connected.

4. A supply voltage circuit as claimed in claim 1, characterized in that a resistor is included in the connection to the control electrode of the second controllable switch so that a current flows through said resistor in the stand-by state of a value sufficient to cut-off the first controllable switch.

endent

of variations of the input voltage and/or of a load connected to the

terminals of the output voltage. This circuit comprises a transformer

having a primary and a feedback winding and a first controllable switch

arranged in series with the primary winding. The series arrangement

thus formed is coupled between the terminals of the input voltage. A

second controllable switch which is coupled via a turnoff capacitor to

the control electrode of the first switch to turn it off. The feedback

winding is coupled to this control electrode and the primary winding is

coupled via a rectifier to an output capacitor the terminals of which

are the terminals for the output voltage. An output voltage-dependent

control voltage is present on a control electrode of the second switch

for controlling the conduction period of the first switch. The circuit

is switchable between an operating state and a stand-by state in which

relative to the operating state the energy supplied to the load is

considerably reduced, and the circuit further comprises a starting

network connected to a terminal for the input voltage.

endent

of variations of the input voltage and/or of a load connected to the

terminals of the output voltage. This circuit comprises a transformer

having a primary and a feedback winding and a first controllable switch

arranged in series with the primary winding. The series arrangement

thus formed is coupled between the terminals of the input voltage. A

second controllable switch which is coupled via a turnoff capacitor to

the control electrode of the first switch to turn it off. The feedback

winding is coupled to this control electrode and the primary winding is

coupled via a rectifier to an output capacitor the terminals of which

are the terminals for the output voltage. An output voltage-dependent

control voltage is present on a control electrode of the second switch

for controlling the conduction period of the first switch. The circuit

is switchable between an operating state and a stand-by state in which

relative to the operating state the energy supplied to the load is

considerably reduced, and the circuit further comprises a starting

network connected to a terminal for the input voltage. Such a supply voltage circuit is disclosed in German Patent Application No. 2,651,196. With this prior art circuit supply energy can be applied in the operating state to the different portions of a television receiver. In the stand-by state the majority of the output voltages of the circuit are so low that the receiver is substantially in the switched-off condition. In the prior art circuit the starting network is formed by a resistor connected to the unstabilized input voltage and through which on turn-on of the circuit a current flows via the feedback winding to the control electrode of the first controllable switch, which is a switching transistor, and brings it to and maintains it in the conductive state, as a result of which the circuit can start.

In the stand-by state the transistor is non-conducting in a large part of the period of the generated oscillation so that little energy is stored in the transformer. However, the starting resistor is connected via a diode to the second controllable switch, which is a thyristor. As the sum of the voltages across these elements is higher than the base-emitter threshold voltage of the transistor, the diode and the thyristor cannot simultaneously carry current. This implies that current flows through the starting resistor to the base of the transistor via the feedback winding after a capacitor connected to the feedback winding has been charged.

The invention has for its object to provide an improved circuit of the same type in which in the stand-by state the supply energy applied to the load is reduced to

zero. The prior art circuit cannot be improved in this respect without

the use of mechanical switches, for example relays. According to the

invention, the switched-mode self-oscillating supply voltage circuit

does not comprise such relays and is characterized in that it further

comprises means for adjusting the control voltage in the stand-by state

to a value at which the first controllable switch is cut-off. A

connection which carries current during the conduction period of the

second controllable switch is provided between the starting network and

said second switch while a connection present between the starting

network and the control electrode of the first switch does not carry

current in the stand-by state.

zero. The prior art circuit cannot be improved in this respect without

the use of mechanical switches, for example relays. According to the

invention, the switched-mode self-oscillating supply voltage circuit

does not comprise such relays and is characterized in that it further

comprises means for adjusting the control voltage in the stand-by state

to a value at which the first controllable switch is cut-off. A

connection which carries current during the conduction period of the

second controllable switch is provided between the starting network and

said second switch while a connection present between the starting

network and the control electrode of the first switch does not carry

current in the stand-by state. The invention is based on the recognition that the prior art supply voltage circuit cannot oscillate, so that the energy supplied by it is zero, if the control voltage obtains a value as referred to, while the starting network is connected in such a manner that in the stand-by state no current can flow through it to the control electrode of the first controllable switch.

It should be noted that in the said German Patent Application the starting network is in the form of a resistor which is connected to an unstabilized input d.c. voltage. It is, however, known, for example, from German Patent Specification No. 2,417,628 to employ for this purpose a rectifier network connected to an a.c. voltage from which the said input d.c. voltage is derived by rectification.

The invention will now be further described by way of example with reference to the accompanying drawing, which shows a basic circuit diagram of a switched-mode self-oscillating supply voltage circuit.

The self-oscillating supply circuit shown in the FIGURE comprises a npn-switching transistor Tr1 having its collector connected to the primary winding L1 of a transformer T, while the emitter is connected to ground via a small resistor R1, for example 1.5 Ohm. Resistor R1 is decoupled for the high frequencies by means of a 150 nF capacitor C1. One end of winding L1 is connected to a conductor which carries an unstabilized input d.c. voltage V B of, for example, 300 V. Voltage V B has a negative rail connected to ground and is derived from the electric power supply by rectification. One end of a feedback winding L2 is connected to the base of transistor Tr1 via the parallel arrangement of a small inductance L3 and a damping resistor R2. A terminal of a 47 μF capacitor C2 is connected to the junction of the elements L2, L3 and R2. The series arrangement of a diode D1 and a 2.2 Ohm-limiting resistor R3 is arranged between the other terminal of capacitor C2 and the other end of winding L2 and the series arrangement of a resistor R4 of 12 Ohm and a diode D2 is arranged between the same end of winding L2 and the emitter of transistor Tr1. A 150 nF capacitor C3 is connected in parallel with diode D2. The anode of diode D1 is connected to that end of winding L2 which is not connected to capacitor C2, while the anode of diode D2 is connected to the emitter of transistor Tr1. In the FIGURE the winding sense of windings L1 and L2 is indicated by means of dots.

The junction of capacitor C2 and resistor R3 is connected to a 100 Ohm resistor R5 and to the emitter of a pnp-transistor Tr2. The base of transistor Tr2 is connected to the other terminal of resistor R5 and to the collector of an npn-transistor Tr3, whose emitter is connected to ground. The base of Tr3 is connected to the collector of transistor Tr2. Transistors Tr2 and Tr3 form an artificial thyristor, i.e. a controllable diode whose anode is the emitter of transistor Tr2 while the cathode is the emitter of transistor Tr3. The base of transistor Tr2 is the anode gate and the base of transistor Tr3 is the cathode gate of the thyristor formed. Between the last-mentioned base and the emitter of transistor Tr1 there is arranged the series network of a 2.2 kOhm resistor R6 with the parallel arrangement of a 2.2 kOhm resistor R7 and a 100 μF capacitor C4. The series arrangement of a diode D11 and a 220 Ohm limiting resistor R19 is arranged between the junction of components R6, R7 and C4 and the junction of components C2, L2, R2 and L3. The cathode of diode D11 is connected to capacitor C2.

Because

of the feedback the described circuit oscillates independently as soon

as the steady state is achieved. It will be described hereinafter how

this state is obtained. During the time transistor Tr1 conducts the

current flowing through the resistor R1 increases linearly. The resistor

R4 then partly determines the base current of transistor Tr1.

Capacitor C4 and resistor R7 form a voltage source the voltage of which

is subtracted from the voltage drop across resistor R1. As soon as the

voltage on the base of transistor Tr3 is equal to approximately 0.7 V

this transistor becomes conductive, as a result of which the thyristor

formed by transistors Tr2 and Tr3 becomes rapidly conductive and

remains so. Across capacitor C2 there is a negative voltage by means of

which transistor Tr1 is turned off. The inverse base current thereof

flows through thyristor Tr2, Tr3. This causes charge to be withdrawn

from capacitor C2, while the charge carriers stored in transistor Tr1

are removed with the aid of inductance L3. As soon as the collector

current of transistor Tr1 has been turned off, the voltage across

winding L2 reverses its polarity, which current recharges the

capacitor. Now the voltage at the junction of components C2, R3 and R5

is negative, causing thyristor Tr2, Tr3 to extinguish.

Because

of the feedback the described circuit oscillates independently as soon

as the steady state is achieved. It will be described hereinafter how

this state is obtained. During the time transistor Tr1 conducts the

current flowing through the resistor R1 increases linearly. The resistor

R4 then partly determines the base current of transistor Tr1.

Capacitor C4 and resistor R7 form a voltage source the voltage of which

is subtracted from the voltage drop across resistor R1. As soon as the

voltage on the base of transistor Tr3 is equal to approximately 0.7 V

this transistor becomes conductive, as a result of which the thyristor

formed by transistors Tr2 and Tr3 becomes rapidly conductive and

remains so. Across capacitor C2 there is a negative voltage by means of

which transistor Tr1 is turned off. The inverse base current thereof

flows through thyristor Tr2, Tr3. This causes charge to be withdrawn

from capacitor C2, while the charge carriers stored in transistor Tr1

are removed with the aid of inductance L3. As soon as the collector

current of transistor Tr1 has been turned off, the voltage across

winding L2 reverses its polarity, which current recharges the

capacitor. Now the voltage at the junction of components C2, R3 and R5

is negative, causing thyristor Tr2, Tr3 to extinguish. Secondary windings L4, L5 and L6 are provided on the core of transformer T with the indicated winding senses. When transistor Tr1 is turned off, a current which recharges a smoothing capacitor C5, C6 or C7 via a rectifier D3, D4 or D5 flows through each of these windings. The voltages across these capacitors are the output voltages of the supply circuit for loads connectable thereto. These loads, which are not shown in the FIGURE, are, for example, portions of a television receiver.

In

parallel with winding L1 there is the series network of a 2.2 nF

tuning capacitor C8 and a 100 Ohm limiting resistor R8. The anode of a

diode D6 is connected to the junction of components R8 and C8, while

the cathode is connected to the other terminal of resistor R8. Winding

L1 and capacitor C8 form a resonant circuit across which an oscillation

is produced after windings L4, L5 and L6 have become currentless. At a

later instant the current through circuit L1, C8 reverses its

direction. As a result thereof a current is generated in winding L2

which flows via diode D2 and resistor R4 to the base of transistor Tr1

and makes this transistor conductive and maintains it in this state.

The dissipation in resistor R8 is reduced by means of diode D6. A

clamping network formed by the parallel arrangement of a 22 kOhm

resistor R9 and a 120 nF capacitor C9 is arranged in series with a

diode D7. This whole assembly is in parallel with winding L1 and

cuts-off parasitic oscillations which would be produced during the

period of time in which transistor Tr1 is non-conductive. The output

voltages of the supply circuit are kept substantially constant in spite

of variations of voltage V B and/or the loads, thanks to a

control of the turning-on instant of thyrisistor Tr2, Tr3. For this

purpose the emitter of a light-sensitive transistor Tr4 is connected to

the base of transistor Tr3. The collector of transistor Tr4 is

connected via a resistor R10 to the conductor which carries the voltage

V B and to a Zener diode Z1 which has a positive voltage

of approximately 7.5 V, while the base is unconnected. The other end of

diode Z1 is connected to ground. A light-emitting diode D8, whose

cathode is connected to the collector of an npn-transistor Tr5, is

optically coupled to transistor Tr4. By means of a potentiometer R11

the base of transistor Tr5 can be adjusted to a d.c. voltage which is

derived from the voltage V 0 of approximately 130 V across capacitor C6. The anode of diode D8 is connected to a d.c. v

In

parallel with winding L1 there is the series network of a 2.2 nF

tuning capacitor C8 and a 100 Ohm limiting resistor R8. The anode of a

diode D6 is connected to the junction of components R8 and C8, while

the cathode is connected to the other terminal of resistor R8. Winding

L1 and capacitor C8 form a resonant circuit across which an oscillation

is produced after windings L4, L5 and L6 have become currentless. At a

later instant the current through circuit L1, C8 reverses its

direction. As a result thereof a current is generated in winding L2

which flows via diode D2 and resistor R4 to the base of transistor Tr1

and makes this transistor conductive and maintains it in this state.

The dissipation in resistor R8 is reduced by means of diode D6. A

clamping network formed by the parallel arrangement of a 22 kOhm

resistor R9 and a 120 nF capacitor C9 is arranged in series with a

diode D7. This whole assembly is in parallel with winding L1 and

cuts-off parasitic oscillations which would be produced during the

period of time in which transistor Tr1 is non-conductive. The output

voltages of the supply circuit are kept substantially constant in spite

of variations of voltage V B and/or the loads, thanks to a

control of the turning-on instant of thyrisistor Tr2, Tr3. For this

purpose the emitter of a light-sensitive transistor Tr4 is connected to

the base of transistor Tr3. The collector of transistor Tr4 is

connected via a resistor R10 to the conductor which carries the voltage

V B and to a Zener diode Z1 which has a positive voltage

of approximately 7.5 V, while the base is unconnected. The other end of

diode Z1 is connected to ground. A light-emitting diode D8, whose

cathode is connected to the collector of an npn-transistor Tr5, is

optically coupled to transistor Tr4. By means of a potentiometer R11

the base of transistor Tr5 can be adjusted to a d.c. voltage which is

derived from the voltage V 0 of approximately 130 V across capacitor C6. The anode of diode D8 is connected to a d.c. v oltage V 1 of approximately 13 V. A resistor R12 is also connected to voltage V 1 ,

the other end of the resistor being connected to the emitter of

transistor Tr5, to the cathode of a Zener diode Z2 which has a voltage

of approximately 7.5 V and to a smoothing capacitor C10. The other ends

of diode Z2 and capacitor C10 are connected to ground. Voltage V1 can

be generated by means of a transformer connected to the electric AC

supply and a rectifier, which are not shown for the sake of simplicity,

more specifically for a remote control to which constantly supply

energy is always applied, even when the majority of the components of

the receiver in what is referred to as the stand-by state are not

supplied with supply energy.

oltage V 1 of approximately 13 V. A resistor R12 is also connected to voltage V 1 ,

the other end of the resistor being connected to the emitter of

transistor Tr5, to the cathode of a Zener diode Z2 which has a voltage

of approximately 7.5 V and to a smoothing capacitor C10. The other ends

of diode Z2 and capacitor C10 are connected to ground. Voltage V1 can

be generated by means of a transformer connected to the electric AC

supply and a rectifier, which are not shown for the sake of simplicity,

more specifically for a remote control to which constantly supply

energy is always applied, even when the majority of the components of

the receiver in what is referred to as the stand-by state are not

supplied with supply energy. A portion of voltage V 0 is compared with the voltage of diode Z2 by means of transistor Tr5. The measured difference determines the collector current of transistor Tr5 and consequently the emitter current of transistor Tr4. This emitter current produces across resistor R6 a voltage drop whose polarity is the opposite of the polarity of the voltage source formed by resistor R7 and capacitor C4. Under the influence of this voltage drop the turn-on instant of thyristor Tr2, Tr3 is controlled as a function of voltage V 0 . If, for example, voltage V 0 tends to decrease owing to an increasing load thereon and/or in response to a decrease in voltage V B , then the collector current of transistor Tr5 decreases and consequently also the said voltage drop. Thyristor Tr2, Tr3 is turned on at a later instant than would otherwise be the case, causing transistor Tr1 to be cut-off at a later instant. The final value of the collector current of this transistor is consequently higher. Consequently, the ratio of the time interval in which transistor Tr1 is conductive to the entire period, commonly referred to as the duty cycle, increases, while the frequency decreases.

The

circuit is protected from overvoltage. This is ensured by a thyristor

which is formed by a pnp-transistor Tr6 and an npn-transistor Tr7. The

anode of a diode D9 is connected to the junction of components R3 and

C2 and the cathode to the base of transistor Tr6 and to the collector

of transistor Tr7. The base of transistor Tr7, which base is connected

to the collector of transistor Tr6, is connected via a zener diode Z3

to a voltage which, by means of a potentiometer R13 is adjusted to a

value derived from the voltage across capacitor C7. The emitter of

transistor Tr6 also is connected to the voltage of capacitor C7, more

specifically via a resistor R14 and a diode D10. If this voltage

increases to above a predetermined value then thyristor Tr6, Tr7

becomes conductive. Since the emitter of transistor Tr7 is connected to

ground, the voltage at its collector becomes very low, as a result of

which diode D9 becomes conductive, which keeps transistor Tr1 in the

non-conducting state. This situation is maintained as long as thyristor

Tr6, Tr7 continues to conduct. This conduction time is predominantly

determined by the values of capacitor C7, resistor R14 and a resistor

R15 connected between the base and the emitter of transistor Tr6. A

thyristor is advantageously used here to render it possible to switch

off a large current even with a low level signal and to obtain the

required hysteresis.

The

circuit is protected from overvoltage. This is ensured by a thyristor

which is formed by a pnp-transistor Tr6 and an npn-transistor Tr7. The

anode of a diode D9 is connected to the junction of components R3 and

C2 and the cathode to the base of transistor Tr6 and to the collector

of transistor Tr7. The base of transistor Tr7, which base is connected

to the collector of transistor Tr6, is connected via a zener diode Z3

to a voltage which, by means of a potentiometer R13 is adjusted to a

value derived from the voltage across capacitor C7. The emitter of

transistor Tr6 also is connected to the voltage of capacitor C7, more

specifically via a resistor R14 and a diode D10. If this voltage

increases to above a predetermined value then thyristor Tr6, Tr7

becomes conductive. Since the emitter of transistor Tr7 is connected to

ground, the voltage at its collector becomes very low, as a result of

which diode D9 becomes conductive, which keeps transistor Tr1 in the

non-conducting state. This situation is maintained as long as thyristor

Tr6, Tr7 continues to conduct. This conduction time is predominantly

determined by the values of capacitor C7, resistor R14 and a resistor

R15 connected between the base and the emitter of transistor Tr6. A

thyristor is advantageously used here to render it possible to switch

off a large current even with a low level signal and to obtain the

required hysteresis. The circuit comprises a 1 MOhm starting resistor R16, one end of which is connected to the base of transistor Tr2 and the other end to the conductor which carries the voltage V B . Upon turn-on of the circuit current flows through resistors R16 and R5 and through capacitor C2, which has as yet no charge, to the base of transistor Tr1. The voltage drop thus produced across resistor R5 keeps transistor Tr2, and consequently also transistor Tr3, in the non-conductive state, while transistor Tr1 is made conductive and is maintained so by this current. Current also flows through winding L2. In this manner the circuit can start as energy is built up in transformer T.

The

supply circuit can be brought into the stand-by state by making an

npn-transistor Tr8, which is non-conductive in the operating state,

conductive. The emitter of transistor Tr8 is connected to ground while

the collector is connected to the collector of transistor Tr5 via a 1.8

kOhm resistor R17. A resistor R18 has one end connected to the base of

transistor Tr8 and the other end, either in the operating state to

ground, or in the stand-by state to a positive voltage of, for example, 5

V. Transistor Tr8 conducts in response to this voltage. An additional,

large current flows through diode D8 and consequently also through

transistor Tr4, resulting in thyristor Tr2, Tr3 being made conductive

and transistor Tr1 being made non-conductive and maintained so. So to

all appearances a large control current is obtained causing the duty

cycle to be reduced to zero. A condition for a correct operation is that

the emitter current of transistor Tr4 be sufficiently large in all

circumstances, which implies that the voltage drop produced across

resistor R6 by this current is always higher than the sum of the voltage

across voltage source R7, C4, of the base-emitter threshold voltage of

transistor Tr3 in the conductive state thereof, and of the voltage at

the emitter of transistor Tr1. So the said voltage drop must be higher

than the sum of the first two voltages, which corresponds to the worst

dimensioning case in which the stand-by state is initiated while

transistor Tr1 is in the non-conductive state.

The

supply circuit can be brought into the stand-by state by making an

npn-transistor Tr8, which is non-conductive in the operating state,

conductive. The emitter of transistor Tr8 is connected to ground while

the collector is connected to the collector of transistor Tr5 via a 1.8

kOhm resistor R17. A resistor R18 has one end connected to the base of

transistor Tr8 and the other end, either in the operating state to

ground, or in the stand-by state to a positive voltage of, for example, 5

V. Transistor Tr8 conducts in response to this voltage. An additional,

large current flows through diode D8 and consequently also through

transistor Tr4, resulting in thyristor Tr2, Tr3 being made conductive

and transistor Tr1 being made non-conductive and maintained so. So to

all appearances a large control current is obtained causing the duty

cycle to be reduced to zero. A condition for a correct operation is that

the emitter current of transistor Tr4 be sufficiently large in all

circumstances, which implies that the voltage drop produced across

resistor R6 by this current is always higher than the sum of the voltage

across voltage source R7, C4, of the base-emitter threshold voltage of

transistor Tr3 in the conductive state thereof, and of the voltage at

the emitter of transistor Tr1. So the said voltage drop must be higher

than the sum of the first two voltages, which corresponds to the worst

dimensioning case in which the stand-by state is initiated while

transistor Tr1 is in the non-conductive state. If thyristor Tr2, Tr3 conducts, either in the operating state or in the stand-by state, current flows through resistor R16 via the collector emitter path of transistor Tr3 to ground. This current is too small to have any appreciable influence on the behaviour of the circuit. Wh

en

thyristor Tr2, Tr3 does not conduct, the voltage on the left hand

terminal of capacitor C2 is equal to approximately 1 V, while the

voltage across the capacitor is approximately -4 V. So transistor Tr1

remains in the non-conductive state and a premature turn-on thereof

cannot occur. If in the operating state transistor Tr1 conducts while

thyristor Tr2, Tr3 is cut-off, then the current flows through resistor

R16 in the same manner as it flows during the start to the base of

transistor Tr1, but has relatively little influence as the base current

caused by the energy stored in winding L2 is many times larger. If

both transistor Tr1 and thyristor Tr2, Tr3 are non-conductive, then the

current through resistor R16 flows through components R5, C2, L2, R4,

C3 and R1. In this stand-by state capacitor C2 has indeed substa

en

thyristor Tr2, Tr3 does not conduct, the voltage on the left hand

terminal of capacitor C2 is equal to approximately 1 V, while the

voltage across the capacitor is approximately -4 V. So transistor Tr1

remains in the non-conductive state and a premature turn-on thereof

cannot occur. If in the operating state transistor Tr1 conducts while

thyristor Tr2, Tr3 is cut-off, then the current flows through resistor

R16 in the same manner as it flows during the start to the base of

transistor Tr1, but has relatively little influence as the base current

caused by the energy stored in winding L2 is many times larger. If

both transistor Tr1 and thyristor Tr2, Tr3 are non-conductive, then the

current through resistor R16 flows through components R5, C2, L2, R4,

C3 and R1. In this stand-by state capacitor C2 has indeed substa ntially

no negative charge any longer but, in spite thereof, transistor Tr1

cannot become conductive since no current flows to its base. It will

furthermore be noted that the circuit is protected in the event that

thyristor Tr2, Tr3 has an interruption. Namely, in such a case the

circuit cannot start.

ntially

no negative charge any longer but, in spite thereof, transistor Tr1

cannot become conductive since no current flows to its base. It will

furthermore be noted that the circuit is protected in the event that

thyristor Tr2, Tr3 has an interruption. Namely, in such a case the

circuit cannot start. In the foregoing a circuit is described which may be considered to be a switched-mode supply voltage circuit of the parallel ("flyback") type. It will be obvious that the invention may alternatively be used in supply voltage circuits of a different type, for example converters of the type commonly referred to as up-converters. It will also be obvious that transistor Tr1 may be replaced by an equivalent switch, for example a gate-turn-off switch.

TDA2579B Horizontal/vertical synchronization circuit

GENERAL DESCRIPTION

The TDA2579B generates and synchronizes horizontal and vertical signals. The device has a 3 level sandcastle output;

The TDA2579B generates and synchronizes horizontal and vertical signals. The device has a 3 level sandcastle output;a transmitter identification signal and also 50/60 Hz identification.

Features

· Horizontal phase detector, (sync to oscillator), sync separator and noise inverter

· Triple current source in the phase detector with automatic selection

· Second phase detector for storage compensation of the horizontal output

· Stabilized direct starting of the horizontal oscillator and output stage from mains supply

· Horizontal output pulse with constant duty cycle value of 29 ms

· Internal vertical sync separator, and two integration selection times

· Divider system with three different reset enable windows

· Synchronization is set to 628 divider ratio when no vertical sync pulses and no video transmitter is identified

· Vertical comparator with a low DC feedback signal

· 50/60 Hz identification output combined with mute function

· Automatic amplitude adjustment for 50 and 60 Hz and blanking pulse duration

· Automatic adaption of the burst-key pulsewidth

FUNCTIONAL DESCRIPTION

Vertical part (pins 1,2,3,4)

The IC embodies a synchronized divider system for generating

the vertical sawtooth at pin 3. The divider system has an

the vertical sawtooth at pin 3. The divider system has aninternal frequency doubling circuit, so the horizontal oscillator is working at its normal line frequency and one line period

equals 2 clock pulses. Due to the divider system no vertical frequency adjustment is needed. The divider has a

discriminator window for automatically switching over from the 60 Hz to 50 Hz system. The divider system operates with

3 different divider reset windows for maximum interference/disturbance protection.

The windows are activated via an up/down counter. The counter increases its counter value by 1 for each time the

separated vertical sync pulse is within the searched window. The count is decreased by 1 when the vertical sync pulse

is not present.

Large (search) window: divider ratio between 488 and 722

This mode is valid for the following conditions:

1. Divider is looking for a new transmitter.

2. Divider ratio found, not within the narrow window limits.

3. Up/down counter value of the divider system operating in the narrow window mode decreases below count 1.

4. Externally setting. This can be reached by loading pin 18 with a resistor of 220 kW to earth or connecting a 3.6 V

diode stabistor between pin 18 and ground.

Narrow window: divider ratio between 522-528 (60 Hz) or 622-628 (50 Hz).

The divider system switches over to this mode when the up/down counter has reached its maximum value of 12 approved

vertical sync pulses. When the divider operates in this mode and a vertical sync pulse is missing within the window the

divider is reset at the end of the window and the counter value is decreased by 1. At a counter value below count 1 the

divider system switches over to the large window mode.

Standard TV-norm

When the up/down counter has reached its maximum value of 12 in the narrow window mode, the information applied to

the up/down counter is changed such that the standard divider ratio value is tested. When the counter has reached a

the up/down counter is changed such that the standard divider ratio value is tested. When the counter has reached avalue of 14 the divider system is changed over to the standard divider ratio mode. In this mode the divider is always reset

at the standard value even if the vertical sync pulse is missing. A missed vertical sync pulse decreases the counter value

by 1. When the counter reaches the value of 10 the divider system is switched over to the large window mode.

The standard TV-norm condition gives maximum protection for video recorders playing tapes with anti-copy guards.

No-TV-transmitter found: (pin 18 < 1.2 V)

In this condition, only noise is present, the divider is rest to count 628. In this way a stable picture display at normal height

is achieved.

Video tape recorders in feature mode

It should be noted that some VTRs operating in the feature modes, such as picture search, generate such distorted

pictures that the no-TV-transmitter detection circuit can be activated as pin V18

drops below 1.2 V. This would imply a

drops below 1.2 V. This would imply arolling picture (see Phase detector, sub paragraph d). In general VTR-machines use a re-inserted vertical sync pulse in

the feature mode. Therefore the divider system has been made such that the automatic reset of the divider at count 628

when V18 is below 1.2 V is inhibited when a vertical sync pulse is detected.

The divider system also generates the anti-top-flutter pulse which inhibits the Phase 1 detector during the vertical sync.

pulse. The width of this pulse depends on the divider mode. For the divider mode a the start is generated at the reset of

the divider. In mode b and c the anti-top-flutter pulse starts at the beginning of the first equalizing pulse.

The anti-top-flutter pulse ends at count 8 for 50 Hz and count 10 for 60 Hz. The vertical blanking pulse is also generated

via the divider system. The start is at the reset of the divider while the pulse ends at count 34 (17 lines) for 60 Hz, and at

count 44 (22 lines) for 50 Hz systems. The vertical blanking pulse generated at the sandcastle output pin 17 is made by

adding the anti-top-flutter pulse and the blanking pulse. In this way the vertical blanking pulse starts at the beginning of

the first equalizing pulse when the divider operates in the b or c mode. For generating a vertical linear sawtooth voltage

a capacitor should be connected to pin 3. The recommended value is 150 nF to 330 nF (see Fig.1).

The capacitor is charged via an internal current source starting at the reset of the divider system. The voltage on the

capacitor is monitored by a comparator which is activated also at reset. When the capacitor has reached a voltage value

of 5.85 V for the 50 Hz system or 4.85 V for the 60 Hz system the voltage is kept constant until the charging period ends.

of 5.85 V for the 50 Hz system or 4.85 V for the 60 Hz system the voltage is kept constant until the charging period ends.The charge period width is 26 clock pulses. At clock pulse 26 the comparator is switched off and the capacitor is

discharged by an npn transistor current source, the value of which can be set by an external resistor between pin 4 and

ground (pin 9). Pin 4 is connected to a pnp transistor current source which determines the current of the npn current

source at pin 3. The pnp current source on pin 4 is connected to an internal zener diode reference voltage which has a

typical voltage of » 7.5 volts. The recommended operating current range is 10 to 75 mA. The resistance at pin R4 should

be 100 to 770 kW. By using a double current mirror concept the vertical sawtooth pre-correction can be set on the desired

value by means of external components between pin 4 and pin 3, or by connecting the pin 4 resistor to the vertical current

measuring resistor of the vertical output stage. The vertical amplitude is set by the current of pin 4. The vertical feedback

voltage of the output stage has to be applied to pin 2. For the normal amplitude adjustment the values are DC = 1 V and

AC = 0.8 V. Due to the automatic system adaption both values are valid for 50 Hz and 60 Hz.

The low DC voltage value improves the picture bounce beh

aviour as less parabola compensation is necessary. Even a

aviour as less parabola compensation is necessary. Even afully DC coupled feedback circuit is possible.

Vertical guard

The IC also contains a vertical guard circuit. This circuit monitors the vertical feedback signal on pin 2. When the level

on pin 2 is below 0.35 V or higher than 1.85 V the guard circuit inserts a continuous level of 2.5 V in the sandcastle output

signal of pin 17. This results in the blanking of the picture displayed, thus preventing a burnt-in horizontal line. The guard

levels specified refer to the zener diode reference voltage source level.

Driver output

The driver output is at pin 1, it can deliver a drive current of 1.5 mA at 5 V output. The internal impedance is approximately

170 W. The output pin is also connected to an internal current source with a sink current of 0.25 mA.

Sync separator, phase detector and TV-station identification (pins 5,6,7,8 and 18)

The video input signal is connected to pin 5. The sync separator is designed such that the slicing level is independent of

the amplitude of the sync pulse. The black level is measured and stored in the capacitor at pin 7. The slicing level value

is stored in the capacitor at pin 6.

Black level detector

A gating signal is used for the black level detector. This signal is composed of an internal horizontal reference pulse with

a duty factor of 50% and the flyback pulse at pin 12. In this way the TV-transmitter identification operates also for all DC

conditions at input pin 5 (no video modulation, plain carrier only).

During the frame interval the slicing level detector is inhibited by a signal which starts with the anti-top flutter pulse and

ends with the reset vertical divider circuit. In this way shift of the slicing level due to the vertical sync signal is reduced

and separation of the vertical sync pulse is improved.

Noise level detector

An internal noise inverter is activated when the video level at pin 5 decrea

ses below 0.7 V. The IC also embodies a

ses below 0.7 V. The IC also embodies abuilt-in sync pulse noise level detection circuit. This circuit is directly connected to pin 5 and measures the noise level at

the middle of the horizontal sync pulse. When a signal-to-noise level of 19 dB is detected a counter circuit is activated.

A video input signal is processed as “acceptable noise free” when 12 out of 15 sync pulses have a noise level below

19 dB for two successive frame periods. The sync pulses are processed during a 15 line width gating period generated

by the divider system. The measuring circuit has a built-in noise level hysteresis of approximately 3 dB. When the

“acceptable noise free” condition is found the phase detector of pin 8 is switched to not gated and normal time constant.

When a higher sync pulse noise level is found the phase detector is switched over to slow time constant and gated sync

pulse phase detection. At the same time the integration time of the vertical sync pulse separator is adapted.

Phase detector

The phase detector circuit is connected to pin 8. This circuit consists of 3 separate phase detectors which are activated

The phase detector circuit is connected to pin 8. This circuit consists of 3 separate phase detectors which are activateddepending on the voltage of pin 18 and the state of the sync pulse noise detection circuit. For normal and fast time

constants all three phase detectors are activated during the vertical blanking period, this with the exception of the

anti-top-flutter pulse period, and the separated vertical sync-pulse time. As a result, phase jumps in the video signal

related to the video head, take over of video recorders are quickly restored within the vertical blanking period. At the end

of the blanking period the phase director time constant is increased by 1.5 times. In this way there is no requirement for

external VTR time constant switching, and so all station numbers are suitable for signals from VTR, video games or home

computers.

For quick locking of a new TV station starting from a noise only signal condition (normal time constant) a special circuit

is incorporated. A new TV station which is not locked to the horizontal oscillator will result in a voltage decrease below

is incorporated. A new TV station which is not locked to the horizontal oscillator will result in a voltage decrease below0.1 V at pin 18. This will activate a frame period counter which switches the phase detector to fast for 3 frame periods

during the vertical scan period.

The horizontal oscillator will now lock to the new TV-station and as a result, the voltage on pin 18 will increase to

approximately 6.5 V. When pin 18 reaches a level of 1.8 V the mute output transistor of pin 13 is switched OFF and the

divider is set to the large window. In general the mute signal is switched OFF within 5 ms (pin C18 = 47 nF) after reception

of a new TV-signal. When the voltage on pin 18 reaches a level of 5 V, usually within 15 ms, the frame counter is switched

OFF and the time constant is switched from fast to normal during the vertical scan period.

If the new TV station is weak, the sync-noise detector is activated. This will result in a change over of pin 18 voltage from

6.5 V to »10 V. When pin 18 exceeds the level of 7.8 V the phase detector is switched to slow time constant and gated

sync pulse condition. The current is also reduced during the vertical blanking period by 1 mA. When desired, most

conditions of the phase detector can also be set by external means in the following way:

a. Fast time constant TV transmitter identification circuit not active, connect pin 18 to earth (pin 9).

b. Fast time constant TV transmitter identification circuit active, connect a resistor of 220 kW between pin 18 and ground.

This condition can also be set by using a 3.6 V stabistor diode instead of a resistor.

c. Slow time constant, (with exception of frame

blanking period), connect pin 18 via a resistor of 10 kW to + 12 V, pin 10.

blanking period), connect pin 18 via a resistor of 10 kW to + 12 V, pin 10.In this condition the transmitter identification circuit is not active.

d. No switching to slow time constant desired (transmitter identification circuit active), connect a 6.8 V zener diode

between pin 18 and ground.

Supply (pins 9, 10 and 16)

The IC has been designed such that the horizontal oscillator and output stage can start operating by application of a very

low supply current into pin 16.

The horizontal oscillator starts at a supply current of approximately 4 mA. The horizontal output stage is forced into the

non-conducting stage until the supply current has a typical value of 5 mA. The circuit has been designed so that after

starting the horizontal output function a current drop of » 1 mA is allowed. The starting circuit has the ability to derive the

main supply (pin 10) from the horizontal output stage. The horizontal output signal can also be used as the oscillator

signal for synchronized switched mode power supplies. The maximum allowed starting current is 9.7 mA (Tamb = 25 °C).

The main supply should be connected to pin 10, and pin 9 should be used as ground. When the voltage on pin 10

increases from zero to its final value (typically 12 V) a part of the supply current of

the starting circuit is taken from pin 10

the starting circuit is taken from pin 10via internal diodes, and the voltage on pin 16 will stabilize to a typical value of 9.4 V.

In a stabilized condition (pin V10 > 10 V) the minimum required supply current to pin 16 is » 2.5 mA. All other IC functions

are switched on via the main supply voltage on pin 10. When the voltage on pin 10 reaches a value of » 7 V the horizontal

phase detector circuit is activated and the vertical ramp on pin 3 is started. The second phase detector circuit and burst

pulse circuit are started when the voltage on pin 10 reaches the stabilized voltage value of pin 16 which is typically 9.4 V.

To close the second phase detector loop, a flyback pulse must be applied to pin 12. When no flyback pulse is detected

the duty factor of the horizontal output stage is 50%.

For remote switch-off pin 16 can be connected to ground (via a npn transistor with a series resistor of » 500 W) which

switches off the horizontal output.

Horizontal oscillator, horizontal output transistor, and second phase detector (pins 11, 12, 14 and 15)

The horizontal oscillator is connected to pin 15. The frequency is set by an external RC combination between pin 15 and

ground, pin 9. The open collector horizontal output stage is connected to pin 11. An internal zener diode configuration

limits the open voltage of pin 11 to » 14.5 V.

The horizontal output transistor at pin 11 is blocked until the current into pin 16 reaches a value of » 5 mA.

A higher current results in a horizontal output signal at pin 11, which starts with a duty factor of » 40% HIGH.

The duty factor is set by an internal current-source-loaded npn emitter follower stage connected to pin 14 during starting.

When pin 16 changes over to voltage stabilization the npn emitter follower and current source load at pin 14 are switched

OFF and the second phase detector circuit is activated, provided a horizontal flyback pulse is present at pin 12.

When no flyback pulse is detected at pin 12 the duty factor of the horizontal output stage is set to 50%.

The phase detector circuit at pin 14 compensates for storage time in the horizontal deflection output stage. The horizontal

output pulse duration is 29 ms HIGH for storage times between 1 ms and 17 ms (flyback pulse of 12 ms). A higher storage

time increases the HIGH time. Horizontal picture shift is possible by forcing an external charge or discharge current into

the capacitor at pin 14.

Mute output and 50/60 Hz identification (pin 13)

The collector of an npn transistor is connected to pin 13. When the voltage on pin 18 drops below 1.2 V

(no TV-transmitter) the npn transistor is switched ON.

When the voltage on pin 18 increases to a level of » 1.8 V (new TV-transmitter found) the npn transistor is switched OFF.

Pin 13 has also the possibility for 50/60 Hz identification. This function is available when pin 13 is connected to pin 10

(+ 12 V) via an external pull-up resistor of 10 to 20 kW. When no TV-transmitter is identified the voltage on pin 13 will be

LOW (< 0.5 V). When a TV-transmitter with a divider ratio > 576 (50 Hz) is detected the output voltage of pin 13 is HIGH

(+ 12 V).

When

a TV-transmitter with a divider ratio < 576 (60 Hz) is found an

internal pnp transistor with its emitter connected to

When

a TV-transmitter with a divider ratio < 576 (60 Hz) is found an

internal pnp transistor with its emitter connected topin 13 will force this pin output voltage down to » 7.6 V.

Sandcastle output (pin 17)

The sandcastle output pulse generated at pin 17, has three different voltage levels. The highest level, (10.4 V), can be

used for burst gating and black level clamping. The second level (4.5 V) is obtained from the horizontal flyback pulse at

pin 12, and is used for horizontal blanking. The third level (2.5 V) is used for vertical blanking and is derived via the

vertical divider system. For 50 Hz the blanking pulse duration is 44 clock pulses and for 60 Hz it is 34 clock pulses started

from the vertical divider reset. For TV-signals which have a divider ratio between 622 and 628 or between 522 and 528

the pulse is started at the first equalizing pulse. With the 50/60 Hz information the burst-key pulse width is switched to

improve the behaviour in multi-norm concepts.

- IF DEM + AMPL with TDA3541

DESCRIPTION

The TDA3541;Q are integrated IF

amplifier and demodulator circuits for colour or black/white

television receivers, the TDA8340;Q is for application with

n-p-n tuners and the TDA8341;Q for p-n-p tuners.

The TDA8340;Q and TDA8341;Q are pin-compatible

successors with improved performance to types

successors with improved performance to typesTDA2540/2541;Q and TDA3540/3541;Q.

Features

· Full range gain-controlled wide-band IF amplifier

· Linear synchronous demodulator with excellent

intermodulation performance

· White spot inverter

· Wide-band video amplifier with noise protection

· AFC circuit with AFC on/off switching and

sample-and-hold function

· Low impedance AFC output

· AGC circuit with noise gating

· Tuner AGC output for n-p-n tuners (TDA8340) or p-n-p

tuners (TDA8341)

· External video switch for switching-off the video output

· Reduced sensitivity for high sound carriers

· Integrated filter to limit second harmonic IF signals

· Wide supply voltage range

· Requires few external components

An

automatic fine tuning (AFT) circuit is provided which generates an

AFT control signal in response to a video intermediate frequency (I.F.)

signal. The I.F. signal is supplied to the inputs of two buffer

amplifiers, which couple signals of like phase relationship to two

inputs of a discriminator network. The discriminator network is tuned to

the desired frequency of the video I.F. signal, and is responsive to

the buffered I.F. signals for causing respective signal voltages to

be developed at its inputs which vary differentially in magnitude in

response to the frequency deviation of the I.F. signals from the

desired I.F. frequency. The differentially related signals are

detected by two peak detector networks for use as AFT control

signals. The buffer amplifiers and peak detectors may be conveniently

fabricated on a single I.C. chip. The discriminator network is

coupled to the buffer amplifiers by two external I.C. terminals.

An

automatic fine tuning (AFT) circuit is provided which generates an

AFT control signal in response to a video intermediate frequency (I.F.)

signal. The I.F. signal is supplied to the inputs of two buffer

amplifiers, which couple signals of like phase relationship to two

inputs of a discriminator network. The discriminator network is tuned to

the desired frequency of the video I.F. signal, and is responsive to

the buffered I.F. signals for causing respective signal voltages to

be developed at its inputs which vary differentially in magnitude in

response to the frequency deviation of the I.F. signals from the

desired I.F. frequency. The differentially related signals are

detected by two peak detector networks for use as AFT control

signals. The buffer amplifiers and peak detectors may be conveniently

fabricated on a single I.C. chip. The discriminator network is

coupled to the buffer amplifiers by two external I.C. terminals.------------------------------

CHASSIS CP90 TELETEXT UNIT 311910861001 4822 21222614

SAA

5231 PHILIPS

SAA5241P/B PHILIPS

TMM2016BP-15 TOSHIBA

The teletext Unit was generally an extra addon to purchase apart except for the TXT model which it have had included directly.

SAA5231 Teletext video processor:

GENERAL DESCRIPTION

The SAA5231 is a bipolar integrated circuit intended as a successor to the SAA5030. It extracts Teletext Data from the

video signal, regenerates Teletext Clock and synchronizes the text display to the television syncs. The integrated circuit

is intended to work in conjunction with CCT (Computer Controlled Teletext), EUROM or other compatible devices.

Features

· Adaptive data slicer

· Data clock regenerator

· Adaptive sync separator, horizontal phase detector and 6 MHz VCO forming display phase locked loop (PLL)

The function is quoted against the corresponding pin number.

1. Synch output to TV

Output with dual polarity buffer, a load resistor to 0 V or + 12 V selects positive-going or negative-going syncs.

2. Video input level select

When this pin is LOW a 1 V video input level is selected. When the pin is not connected it floats HIGH selecting a

2,5 V video input level.

3. HF filter

The video signal for the h.f.-loss compensator is filtered by a 15 pF capacitor connected to this pin.

4. Store h.f.

The h.f. amplitude is stored by a 1 nF capacitor connected to this pin.

5. Store amplitude

The amplitude for the adaptive data slicer is stored by a 470 pF capacitor connected to this pin.

6. Store zero level

The zero level for the adaptive data slicer is

stored by a 22 nF capacitor connected to this pin.

stored by a 22 nF capacitor connected to this pin.7. External data input

Current input for sliced teletext data from external device.

Active HIGH level (current), low impedance input.

8. Data timing

A 270 pF capacitor is connected to this pin for timing of the adaptive data slicer.

9. Store phase

The output signal from the clock phase detector is stored by a 100 pF capacitor connected to this pin.

10. Video tape recorder mode (VCR)

Signal input to command PLL into short time constant mode. Not used in application circuit Fig.4a or Fig.4b.

11. Crystal

A 13,875 MHz crystal, 2 x data rate, connected in series with a 15 pF capacitor is applied via this pin to the oscillator

and divide-by-two to provide the 6,9375 MHz clock signal.

12. Clock filter

A filter for the 6,9375 MHz clock signal is connected to this pin.

13. Ground (0 V)

14. Teletext clock output (TTC)

Clock output for CCT (Computer Controlled Teletext).

15. Teletext data output (TTD)

Data output for CCT.

16. Supply voltage VCC (+ 12 V typ.)

17. Clock output (F6)

6 MHz clock output for timing and sandcastle generation in CCT.

18. Oscillator output (6 MHz)

A series resonant circuit is connected between this pin and pin 20 to control the nominal frequency of the VCO.

19. Filter 2

A filter with a short time constant is connected to this pin for the horizontal phase detector. It is used in the video

recorder mode and while the loop is locking up.

20. Oscillator input (6 MHz)

See pin 18.

21. Filter 1

A filter with a long time constant is connected to this pin for the horizontal phase detector.

22. Sandcastle input pulse (PL/CBB)

This input accepts a sandcastle waveform, which is formed from PL and CBB from the CCT.

Signal timing is shown in Fig.5.

23. Pulse timing resistor

The current for the pulse generator is defined by a 68 W resistor connected to this pin.

24. Pulse timing capacitor

The timing of the pulse generator is determined by a 220 pF capacitor connected to this pin.

25. Video composite sync output (VCS)

The output signal is for CCT.

26. Black level

The black level for th

e adaptive sync separator is stored by a 68 nF capacitor connected to this pin.

e adaptive sync separator is stored by a 68 nF capacitor connected to this pin.27. Composite video input (CVS)

The composite video signal is input via a 2,2 mF clamping capacitor to the adaptive sync separator.

28. Text composite sync input (TCS)/Scan composite sync input (SCS)

TCS is input from CCT or SCS from external sync circuit. SCS is expected when there is no load resistor at pin 1.

If pin 28 is not connected the sync output on pin 1 will be the composite video input at pin 27, internally buffered.

GENERAL BASIC TRANSISTOR LINE OUTPUT STAGE OPERATION:

The basic essentials of a transistor line output stage are shown in Fig. 1(a). They comprise: a line output transformer which provides the d.c. feed to the line output transistor and serves mainly to generate the high -voltage pulse from which the e.h.t. is derived, and also in practice other supplies for various sections of the receiver; the line output transistor and its parallel efficiency diode which form a bidirectional switch; a tuning capacitor which resonates with the line output transformer primary winding and the scan coils to determine the flyback time; and the scan coils, with a series capacitor which provides a d.c. block and also serves to provide slight integration of the deflection current to compensate for the scan distortion that would otherwise be present due to the use of flat screen, wide deflection angle c.r.t.s. This basic circuit is widely used in small -screen portable receivers with little elaboration - some use a pnp output transistor however, with its collector connected to chassis.

Circuit Variations:

Variations to the basic circuit commonly found include: transposition of the scan coils and the correction capacitor; connection of the line output transformer primary winding and its e.h.t. overwinding in series; connection of the deflection components to a tap on the transformer to obtain correct matching of the components and conditions in the stage; use of a boost diode which operates in identical manner to the arrangement used in valve line output stages, thereby increasing the effective supply to the stage; omission of the efficiency diode where the stage is operated from an h.t. line, the collector -base junction of the line output transistor then providing the efficiency diode action without, in doing so, producing scan distortion; addition of inductors to provide linearity and width adjustment; use of a pair of series -connected line output transistors in some large -screen colour chassis; and in colour sets the addition of line convergence circuitry which is normally connected in series between the line scan coils and chassis. These variations on the basic circuit do not alter the basic mode of operation however.

Resonance

The most important fact to appreciate about the circuit is that when the transistor and diode are cut off during the flyback period - when the beam is being rapidly returned from the right-hand side of the screen to the left-hand side the tuning capacitor together with the scan coils and the primary winding of the line output transformer form a parallel resonant circuit: the equivalent circuit is shown in Fig. 1(b). The line output transformer primary winding and the tuning capacitor as drawn in Fig. 1(a) may look like a series tuned circuit, but from the signal point of view the end of the transformer primary winding connected to the power supply is earthy, giving the equivalent arrangement shown in Fig. 1(b).

The Flyback Period:

Since the operation of the circuit depends mainly upon what happens during the line flyback period, the simplest point at which to break into the scanning cycle is at the end of the forward scan, i.e. with the

beam deflected to the right-hand side of the screen, see Fig. 2. At

this point the line output transistor is suddenly switched off by the

squarewave drive applied to its base. Prior to this action a linearly

increasing current has been flowing in the line output transformer

primary winding and the scan coils, and as a result magnetic fields have

been built up around these components. When the transistor is switched

off these fields collapse, maintaining a flow of current which rapidly

decays to zero and returns the beam to the centre of the screen. This

flow of current charges the tuning capacitor, and the voltage at A rises

to a high positive value - of the order of 1- 2k V in large -screen

sets, 200V in the case of mains/battery portable sets. The e

beam deflected to the right-hand side of the screen, see Fig. 2. At

this point the line output transistor is suddenly switched off by the

squarewave drive applied to its base. Prior to this action a linearly

increasing current has been flowing in the line output transformer

primary winding and the scan coils, and as a result magnetic fields have

been built up around these components. When the transistor is switched

off these fields collapse, maintaining a flow of current which rapidly

decays to zero and returns the beam to the centre of the screen. This

flow of current charges the tuning capacitor, and the voltage at A rises

to a high positive value - of the order of 1- 2k V in large -screen

sets, 200V in the case of mains/battery portable sets. The e nergy

in the circuit is now stored in the tuning capacitor which next

discharges, reversing the flow of current in the circuit with the result

that the beam is rapidly deflected to the left-hand side of the screen -

see Fig. 3. When the tuning capacitor has discharged, the voltage at A

has fallen to zero and the circuit energy is once more stored in the

form of magnetic fields around the inductive components. One half -cycle

of oscillation has occurred, and the flyback is complete.

nergy

in the circuit is now stored in the tuning capacitor which next

discharges, reversing the flow of current in the circuit with the result

that the beam is rapidly deflected to the left-hand side of the screen -

see Fig. 3. When the tuning capacitor has discharged, the voltage at A

has fallen to zero and the circuit energy is once more stored in the

form of magnetic fields around the inductive components. One half -cycle

of oscillation has occurred, and the flyback is complete.Energy Recovery:

First Part of Forward Scan The circuit then tries to continue the cycle of oscillation, i.e. the magnetic fields again collapse, maintaining a current flow which this time would charge the tuning capacitor negatively (upper plate). When the voltage at A reaches about -0.6V however the efficiency diode becomes forward biased and switches on. This damps the circuit, preventing further oscillation, but the magnetic fields continue to collapse and in doing so produce a linearly decaying current flow which provides the first part of the forward s

can,

the beam returning towards the centre of the screen - see Fig. 4. The

diode shorts out the tuning capacitor but the scan correction capacitor

charges during this period, its right-hand plate becoming positive with

respect to its left-hand plate, i.e. point A. Completion of Forward Scan

When the current falls to zero, the diode will switch off. Shortly

before this state of affairs is reached however the transistor is

switched on. In practice this is usually about a third of the way

through the scan. The squarewave applied to its base drives it rapidly

to saturation, clamping the vol

can,

the beam returning towards the centre of the screen - see Fig. 4. The

diode shorts out the tuning capacitor but the scan correction capacitor

charges during this period, its right-hand plate becoming positive with

respect to its left-hand plate, i.e. point A. Completion of Forward Scan

When the current falls to zero, the diode will switch off. Shortly

before this state of affairs is reached however the transistor is

switched on. In practice this is usually about a third of the way

through the scan. The squarewave applied to its base drives it rapidly

to saturation, clamping the vol tage

at point A at a small positive value - the collector emitter saturation

voltage of the transistor. Current now flows via the transistor and the

primary winding of the line output transformer, the scan correction

capacitor discharges, and the resultant flow of current in the line scan

coils drives the beam to the right-hand side of the screen see Fig. 5.

tage

at point A at a small positive value - the collector emitter saturation

voltage of the transistor. Current now flows via the transistor and the

primary winding of the line output transformer, the scan correction

capacitor discharges, and the resultant flow of current in the line scan

coils drives the beam to the right-hand side of the screen see Fig. 5.Efficiency:

The transistor is then cut off again, to give the flyback, and the cycle of events recurs. The efficiency of the circuit is high since there is negligible resistance present. Energy is fed into the circuit in the form of the magnetic fields that build up when the output transistor is switched on. This action connects the line output transformer primary winding across the supply, and as a result a linearly increasing current flows through it. Since the width is

dependent on the supply voltage, this must be stabilised.

Harmonic Tuning: