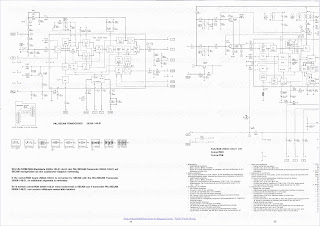

.TUNER UNIT

- IF ZF-MONO-TP 29504-102.21

- FARB/RGB 29504-105.21

- ABLENKUNG 29504.007.25

GRUNDIG SUPER COLOR P37-242 CHASSIS CUC2401 DESCRIPTION OF THE ZNT - LINE SUPPLY TRANSFORMER TECHNOLOGY, ONE TRANSFORMER FOR ALL SUPPLY FUNCTIONS :

Short Functional Description

The GRUNDIG line/power supply unit has two important features:

- the line/mains transformer (ZNT) with ferrite core.

This transformer is provided with windings for the power supply and line output stages:

- the supply frequency corresponds to the line frequency.

The ZNT is used for electrical isolation, horizontal deflection, and generation of the operating voltage. The ZNT windings are tightly and loosely coupled to ensure that the load capacity of the supplies is high enough and that back effects on the line transformer winding N-M are avoided.

Startup Circuit

The starting voltage for IC 655 PHILIPS TDA3640 is obtained from the bridge rectifier D 621 via R 641. lf the voltage on pin 2,

which is derived from the resistor network R 642, 643, and 644, reaches

a level of approximately 10 V, the IC 655 starts to drive T 6 61 via

pin 3 (precondition: pin ‘8>10V).

The starting voltage for IC 655 PHILIPS TDA3640 is obtained from the bridge rectifier D 621 via R 641. lf the voltage on pin 2,

which is derived from the resistor network R 642, 643, and 644, reaches

a level of approximately 10 V, the IC 655 starts to drive T 6 61 via

pin 3 (precondition: pin ‘8>10V).The line/power supply circuit starts to oscillate.

Simultaneously, the current consumption drawn via pin 2 rises and the winding E-D of

the ZNT takes over the operating voltage supply function (D 647, R 647, C 647).

Oscillator in IC PHILIPS TDA3640 The control pulses for the T 661 are generated by an oscillator which operates on the threshold principle where C 653 is an externaly connected frequency-determining component (oscillator retaining range 14-17 kHz approx.). The oscillator oscillates at a free-run frequency until the reference pulses from the ZNT exceed 1 Vp at pin 12.

ln full operating condition (ON) avoltage of

about +5 Vp is applied to pin 12.

about +5 Vp is applied to pin 12.Line 0utputStage

The deflection transistor T 521 is activated in stand-by mode. The cyclic line-frequency control of the deflection transistor corresponds to the “ON" operating mode.

The power for the horizontal sweep circuit is derived from the electromotive force of coil M-N that no additional operating voltage is necessary for T 521.

Voltage Stabil

isation

isationln stand-by mode the pulse from winding E-D (tightly coupled with winding A-B) is used as a reference for stahilisation. The controlled variation is +10.5 V on pin 2 TDA3640.

ln full operating condition, that is 'ON“. the voltage in the horizontal sweep circuit (transformer winding M-N) must be stabilised to a constant level. This is achieved by means of a reference pulse from winding C-D which is tightly coupled with winding M-N. The resulting direct voltage

obtained via D 633 is proportional to the width of the picture or high voltage and is applied to pin 10 and compared with the reference voltage (about 3 V) on pin 11. ln this part of the circuit the +C voltage is adjusted by means of R 637 to 196 V and 192Vf'or 25" receivers and 28" receivers.

respectively.

Protective Circuits of PHILIPS TDA3640

Protective Circuits of PHILIPS TDA3640The protective circuits respond immediately if:

- the operating voltage on pin 2 is too low (<7 V):

- ICE of T 521 is too high (more negative than -1 V at pin 7);

- the power supply voltage is too high (voltage at pin 18 is 2.8 V higher than at pin 2);

- the power supply voltage is too low (voltage at pin 18 is 1.4 V lower than at pin 2);

- the high voltage is excessivley high (line flyback pulses >6V at pin 12):

- the crystal temperature is too high (>135° C).

The inven

tion relates to a horizontal deflection circuit for a picture display apparatus, comprising:

tion relates to a horizontal deflection circuit for a picture display apparatus, comprising: a horizontal output stage provided with a switching element which is coupled to a horizontal output transformer for generating at least one voltage, and

a drive circuit for generating a drive signal for switching the switching element, and provided with a duty cycle control circuit for modulating a duty cycle, of the drive signal during changes of state of the horizontal deflection circuit.

The invention also relates to a method of horizontally deflecting a cathode ray of a picture display tube, and to a picture display apparatus provided with the horizontal deflection circuit.

2. Description of the Related Art

Such

a horizontal deflection circuit is known from German Patent Application

DE-A-4021940, corresponding to U.S. Pat. No. 5,381,329. This

Application describes a power supply circuit in which a switching

element (a transistor in this case) is coupled to a power supply

transformer and a horizontal output transformer. Such a power supply

circuit, which is known as Wessel circuit, supplies power supply

voltages by means of the power supply transformer and a horizontal

deflection current, fly-back voltages and/or scan voltages by means of

the horizontal output transformer. In normal operation, the power supply

circuit, further referred to as combined circuit, generates a drive

signal of which one edge is used for fixing a switch-off instant of the

switching element. This switch-off instant initiates a horizontal

fly-back, and is controlled in normal operation by what is generally

referred to as a phi2-control circuit. To this end, the drive circuit

compares instants of occurre

Such

a horizontal deflection circuit is known from German Patent Application

DE-A-4021940, corresponding to U.S. Pat. No. 5,381,329. This

Application describes a power supply circuit in which a switching

element (a transistor in this case) is coupled to a power supply

transformer and a horizontal output transformer. Such a power supply

circuit, which is known as Wessel circuit, supplies power supply

voltages by means of the power supply transformer and a horizontal

deflection current, fly-back voltages and/or scan voltages by means of

the horizontal output transformer. In normal operation, the power supply

circuit, further referred to as combined circuit, generates a drive

signal of which one edge is used for fixing a switch-off instant of the

switching element. This switch-off instant initiates a horizontal

fly-back, and is controlled in normal operation by what is generally

referred to as a phi2-control circuit. To this end, the drive circuit

compares instants of occurre nce of fly-back pulses supplied by the

horizontal output stage and related to the horizontal fly-back, on the

one hand, with instants of occurrence of the horizontal synchronizing

pulses, on the other hand. A possible difference in instants of

occurrence is corrected so that the video signal is displayed at the

correct horizontal position on the display tube.

nce of fly-back pulses supplied by the

horizontal output stage and related to the horizontal fly-back, on the

one hand, with instants of occurrence of the horizontal synchronizing

pulses, on the other hand. A possible difference in instants of

occurrence is corrected so that the video signal is displayed at the

correct horizontal position on the display tube. During a described change of state from stand-by operation to normal operation, a duty cycle of the drive signal is controlled so as to continuously increase an on-time of the switching element from a small value to a nominal value. With such a variation of the duty cycle, the switching element is protected from a too large dissipation. However, a duty cycle modulation, as used in the combined circuit, does not provide the possibility of having a variation of voltages generated by the combined circuit during the change of state to satisfy various requirements imposed by different components that are coupled to the scan and fly-back voltages.

SUMMARY OF THE INVENTION

It

is, inter alia, an object of the invention to provide a horizontal

deflection circuit and a method in which, during a change of state, a

duty cycle variation is influenced by at least one of the voltages

generated by the horizontal deflection circuit so as to satisfy the

various requirements which are imposed on a variation of different

voltages. The requirements referred to relate to, for example, a maximum

admissible current in components connected with the voltages or a

maximum admissible rate at which a voltage may vary around a specific

value.

It

is, inter alia, an object of the invention to provide a horizontal

deflection circuit and a method in which, during a change of state, a

duty cycle variation is influenced by at least one of the voltages

generated by the horizontal deflection circuit so as to satisfy the

various requirements which are imposed on a variation of different

voltages. The requirements referred to relate to, for example, a maximum

admissible current in components connected with the voltages or a

maximum admissible rate at which a voltage may vary around a specific

value. To this end, a first aspect of the invention provides a horizontal deflection circuit for a picture display apparatus, comprising a horizontal output stage provided with a switching element which is coupled to a horizontal output transformer for at least generating a voltage, and a drive circuit for generating a drive signal for switching the switching element, and provided with a duty cycle control circuit for modulating a duty cycle of the drive signal during changes of state of the horizontal deflection circuit, characterized in that the horizontal deflection circuit is provided with a feedback circuit having at least one feedback input which is coupled to an output of the horizontal output stage for receiving a DC signal which varie

s

during said changes of state, said feedback circuit having an output for

applying a control signal to a control input of the duty cycle control

circuit. By an arranged feedback with a voltage generated by the

horizontal output stage, a first rate of growth of the duty cycle of the

drive signal determined by the maximum admissible dissipation in the

switching element is changed at an instant when the variation of one of

the fed-back voltages tends to reach an unwanted range. According to the

invention, the control of the duty cycle variation provides the

possibility of inhibiting the rate at which voltages rise at the instant

when one of the components tends to violate an imposed requirement. It

consequently is not necessary to choose a constant, very slow increase

of the voltages, satisfying all requirements, but unnecessarily

extending the duration of the change of state.

s

during said changes of state, said feedback circuit having an output for

applying a control signal to a control input of the duty cycle control

circuit. By an arranged feedback with a voltage generated by the

horizontal output stage, a first rate of growth of the duty cycle of the

drive signal determined by the maximum admissible dissipation in the

switching element is changed at an instant when the variation of one of

the fed-back voltages tends to reach an unwanted range. According to the

invention, the control of the duty cycle variation provides the

possibility of inhibiting the rate at which voltages rise at the instant

when one of the components tends to violate an imposed requirement. It

consequently is not necessary to choose a constant, very slow increase

of the voltages, satisfying all requirements, but unnecessarily

extending the duration of the change of state. An embodiment of the horizontal deflection circuit having the characterizing feature that the DC signal is related to at lea

st a scan voltage generated by the

horizontal output transformer, provides the possibility of an accurately

defined desired variation of a scan voltage, with the advantage that

charging of the capacitors coupled to the scan voltage varies at a

chosen second rate. Consequently, too large currents and loads are not

produced in these capacitors and components arranged in series therewith

such as diodes, coils, resisters or fuses. In this way, the current in a

horizontal output transformer coupled to the switching element, can

also be maintained below a saturation value, and the peak lead of a

power supply circuit feeding the horizontal deflection circuit

decreases.

st a scan voltage generated by the

horizontal output transformer, provides the possibility of an accurately

defined desired variation of a scan voltage, with the advantage that

charging of the capacitors coupled to the scan voltage varies at a

chosen second rate. Consequently, too large currents and loads are not

produced in these capacitors and components arranged in series therewith

such as diodes, coils, resisters or fuses. In this way, the current in a

horizontal output transformer coupled to the switching element, can

also be maintained below a saturation value, and the peak lead of a

power supply circuit feeding the horizontal deflection circuit

decreases. An embodiment of the horizontal deflection circuit, with the characterizing feature that the DC signal s related to at le

ast

a fly-back voltage generated by the horizontal output transformer,

provides the possibility of an accurately defined desired variation of a

fly-back voltage. This also has the advantage that too large loads of

components arranged in series with the above-mentioned capacitors, such

as diodes, coils, resisters or fuses cannot be produced. To prevent

flash-over in display tubes which are sensitive thereto, a desired third

rate can be fixed at which the anode voltage of the display tube, which

is also a fly-back voltage, increases. To this end, a voltage derived

from the anode voltage or another fly-back voltage can be fed back. It

is alternatively possible to reduce or eliminate the noises which may

occur due to large current variations or due to a fast rise and fall of

the anode voltage during switching on and switching off the picture

display apparatus.

ast

a fly-back voltage generated by the horizontal output transformer,

provides the possibility of an accurately defined desired variation of a

fly-back voltage. This also has the advantage that too large loads of

components arranged in series with the above-mentioned capacitors, such

as diodes, coils, resisters or fuses cannot be produced. To prevent

flash-over in display tubes which are sensitive thereto, a desired third

rate can be fixed at which the anode voltage of the display tube, which

is also a fly-back voltage, increases. To this end, a voltage derived

from the anode voltage or another fly-back voltage can be fed back. It

is alternatively possible to reduce or eliminate the noises which may

occur due to large current variations or due to a fast rise and fall of

the anode voltage during switching on and switching off the picture

display apparatus. The embodiment of the

horizontal deflection

circuit, with the characterizing feature that the feedback circuit is

provided with change detector means coupled to the feedback input for

supplying output signals which are a measure of a change of the DC

signal, has the advantage that only the variation in DC signals is fed

back, with which in normal operation, in which the DC signals have

reached their final value, the feedback does not have any influence on

the duty cycle control.

horizontal deflection

circuit, with the characterizing feature that the feedback circuit is

provided with change detector means coupled to the feedback input for

supplying output signals which are a measure of a change of the DC

signal, has the advantage that only the variation in DC signals is fed

back, with which in normal operation, in which the DC signals have

reached their final value, the feedback does not have any influence on

the duty cycle control. An embodiment of the horizontal deflection circuit, with the characterizing feature that the feedback circuit is further provided with a threshold circuit arranged between the feedback input and the change detector means, provides the possibility of limiting the variation of a scan or fly-back voltage above a level determined by a threshold circuit at a fourth rate. This provides the advantage of obtaining an extra slow increase of the anode voltage above this level which is necessary for display tubes which are sensitive to flash-over during a rise of the anode voltage close to a final value.

GRUNDIG SUPER COLOR P37-242 CHASSIS CUC2401 Standby mode operation of a horizontal output stage combined with a switched-mode power supply unit. STANDBY-BETRIEB BEI EINER MIT EINEM SCHALTNETZTEIL KOMBINIERTEN HORIZONTALENDSTUFENSCHALTUNG:

1. Swi

tched-mode power supply with a combined horizontal output stage

circuit in television receivers, in which, as a point of electrical

isolation between mains and chassis side, only a transformer (1) is

provided, the primary winding (n1 ) of which is tightly coupled to at

least one chassis-side secondary winding (n3 ) and one mains-side

secondary winding (n5 ) and is loosely coupled to further secondary

windings (n2 , n4 , n6 , n7 ) which, in turn, are tightly coupled to

each other, in which arrangement one of the secondary windings (n2 )

tightly coupled to each other is electrically connected to the

deflection transistor (4) of the horizontal output stage (14), and in

which a primary-side regulating circuit (2), which is synchronized by

flyback pulses in normal operation, controls a regulating switch which

is arranged in series with the primary winding (n1 ) of the transformer

(1), characterized in that - the deflection transistor (4), which is

periodically triggered in normal operation, of the horizontal output

stage (14) is kept continuously conductive by the driver circuit (13) in

standby mode of operation, - the amount of energy transferred from the

mains-side to the chassis side is corrected in accordance with the

determination of the supply voltage of the regulating circuit (2), which

is obtained via the mains-side secondary winding (n5 ) tightly coupled

to the primary winding (n1 ), during the standby mode of operation

during which no flyback pulses are supplied to the regulating circuit, -

and the energy needed in standby mode of operation on the chassis side

for the driver circuit (13) and other loads is transferred via the

chassis-side secondary winding (n3 ) tightly coupled to the primary

winding (n1 ).

tched-mode power supply with a combined horizontal output stage

circuit in television receivers, in which, as a point of electrical

isolation between mains and chassis side, only a transformer (1) is

provided, the primary winding (n1 ) of which is tightly coupled to at

least one chassis-side secondary winding (n3 ) and one mains-side

secondary winding (n5 ) and is loosely coupled to further secondary

windings (n2 , n4 , n6 , n7 ) which, in turn, are tightly coupled to

each other, in which arrangement one of the secondary windings (n2 )

tightly coupled to each other is electrically connected to the

deflection transistor (4) of the horizontal output stage (14), and in

which a primary-side regulating circuit (2), which is synchronized by

flyback pulses in normal operation, controls a regulating switch which

is arranged in series with the primary winding (n1 ) of the transformer

(1), characterized in that - the deflection transistor (4), which is

periodically triggered in normal operation, of the horizontal output

stage (14) is kept continuously conductive by the driver circuit (13) in

standby mode of operation, - the amount of energy transferred from the

mains-side to the chassis side is corrected in accordance with the

determination of the supply voltage of the regulating circuit (2), which

is obtained via the mains-side secondary winding (n5 ) tightly coupled

to the primary winding (n1 ), during the standby mode of operation

during which no flyback pulses are supplied to the regulating circuit, -

and the energy needed in standby mode of operation on the chassis side

for the driver circuit (13) and other loads is transferred via the

chassis-side secondary winding (n3 ) tightly coupled to the primary

winding (n1 ).1. Schaltnetzteil mit kombinierter Horizontalendstufenschaltung in Fernsehempf·angern, bei dem als galvanische Trennstelle zwischen Netz- und Chassisseite nur ein Transformator vorgesehen ist, dessen Prim·arwicklung mit mindestens einer weiteren Wicklung fest und den anderen Wicklungen, die fest aneinandergekoppelt sind, lose gekoppelt ist, wobei eine der fest miteinander verkoppelten Sekund·arwicklungen mit dem Ablenktransistor der Horizontalendstufe elektrisch verbunden ist, d a d u r c h g e k e n n z e i c h n e t , dass der Ablenktransistor (4) der Horizontalendstufe und der Regelkreis (2), der von einer lose an die Prim·arwicklung (n1) angekoppelten Sekund·arwicklung (n4) mit R·uckschlagimpulsen versorgt wird, zur Steuerung des Standby-Betriebes verwendet werden.

2. Schaltnetzteil nach Anspruch 1, d a d u r c h g e k e n n z e i c h n e t , dass der Ablenktransistor (4) der Horizontalendstufe zum Einschalten und/oder zum Wiedereinschalten des Normalbetriebes verwendet wird.

3. Schaltnetzteil nach Anspruch 1 oder 2, d a d u r c h g e k e n n z e i c h n e t , dass zum Einschalten des Standby-Betriebes der Ablenktransistor (4) leitend geschaltet, zum Aufrechterhalten des Standby-Betriebes leitend gehalten und zum Wiedereinschalten des Normalbetriebes gesperrt wird.

4. Schaltnetzteil nach einem oder mehreren der vorhergehenden Anspr·uche, d a d u r c h g e k e n n z e i c h n e t , dass der Regelkreis (2) bei einem Kurzschluss der Wicklung infolge einer sekund·arseitigen St·orung zur·uckgeregelt wird bzw. in den Standby-Betrieb umschaltet. EMI11.1

Ein solches Schaltnetzteil wurde von derselben Anmelderin in der deutschen Patentanmeldung P 32 10 908 vorgestellt. Dieses Schaltnetzteil zeichnet sich aus durch einen prim·arseitigen frei anlaufenden Regelkreis zur Steuerung des Hauptstromweges und einen Regelschalter, ·uber den die aus dem Netz gewonnene, ungeregelte Gleichspannung der Prim·arwicklung n1 des Transformators zugef·uhrt wird. In der lose an die Prim·arwidiung n1 gekoppelten Sekund·arwicklung n2 wird ein Strom induziert, der zum Anlauf und zur Versorgung der Horizontalendstufe vorgesehen ist.

In einer zweiten, fest an die Prim·arwicklung n1 angekoppelten Wicklung n3 wird die Niedervoltspannung f·ur die Horizontalansteuerung, die einen internen Treiber enth·alt, und die Kleinsignalstufen erzeugt. Weiterhin sind Sekund·arwicklungen vorgesehen, die fest an n2 gekoppelt sind und die Spannungen f·ur die kGB-Endstufen, Heizung, usw. erzeugen.

·Uber

die Trennstelle n /n des Transformators wird 12 w·ahrend des

R·ucklaufintervalles des Ablenktransistors (4) eine Spannung auf die

Prim·arwicklung n1 ·ubertragen, die zur Ausschaltung des Regel schalters

verwendet wird. In der fest an die Wicklung n2 gekoppelten Wicklung n4

wird eine Spannung induziert, die zur Synchronisation und Steuerung des

Regelkreises 2 herangezogen wird. Der durch den Widerstand (6)

fliessende Strom kann als ·Uberlast-Referenzstrom zum Abschalten des

Regelschalters herangezogen werden.

·Uber

die Trennstelle n /n des Transformators wird 12 w·ahrend des

R·ucklaufintervalles des Ablenktransistors (4) eine Spannung auf die

Prim·arwicklung n1 ·ubertragen, die zur Ausschaltung des Regel schalters

verwendet wird. In der fest an die Wicklung n2 gekoppelten Wicklung n4

wird eine Spannung induziert, die zur Synchronisation und Steuerung des

Regelkreises 2 herangezogen wird. Der durch den Widerstand (6)

fliessende Strom kann als ·Uberlast-Referenzstrom zum Abschalten des

Regelschalters herangezogen werden.Belastungs·anderungen werden in der fest an n2 gekoppelten Wicklung n4 erfasst und ·uber eine Beeinflussung der Stromflusszeit des Hauptstromkreises ausgeregelt.

Die deutsche Anmeldung P 32 10 908 enth·alt jedoch keinen Hinweis auf einen Standby-Betrieb.

Weiterhin ist aus der DE-PS 24 58 302 ein Sperrwandler-Netzteil f·ur einen Fernsehempf·anger mit Ultraschall-Fernbedienung bekannt, der als Betriebszustand u. a. einen Bereitschaftsbetrieb aufweist. Bei dieser Schaltung sind der Fernsehempf·anger und der Ultraschallempf·anger an denselben Trenntransformator sekund·arseitig angeschlossen. Die Umschaltung zwischen Normalbetrieb und Bereitschaftsbetrieb wird auf der Sekund·arseite des Trenntransformators vorgenommen.

Bei dieser Schaltung ist jedoch ein zus·atzlicher Tr

ansformator f·ur die Horizontalendstufe n·otig.

ansformator f·ur die Horizontalendstufe n·otig.Die Aufgabe der Erfindung besteht darin, bei einem Schaltnetzteil mit kombinierter Horizontal-Endstufenschaltung der im Oberbegriff des Anspruchs 1 angegebenen Art auf besonders einfache Art und Weise den Standby-Betrieb zu erm·oglichen.

Diese Aufgabe wird durch das Kennzeichen des Patentanpsruchs 1 gel·ost. Besonders vorteilhafte Weiterbildungen der Erfindung sind in den Unteranspr·uchen gekennzeichnet.

Dic Vorteile der Erfindung liegen insbesondere darin, dass als galvanische Trennstelle nur ein Transformator f·ur die Erzeugung der Betriebsspannung, der Hochspannung, der Horizontalablenkung und der Heizspannung n·otig ist und aufgrund der gew·ahlten Wicklungsanordnung mit Hilfe des Horizontal-Ablenktransistors und der prim·arseitigen Regelschaltung auf besonders einfache Art und Weise eine Steuerung des Standby-Betriebes durchgef·uhrt werden kann.

Ein weiterer Vorteil besteht darin, dass im Falle einer sekund·arseitigen St·orung automatisch der Standby-Betrieb herbeigef·uhrt wird.

Die Erfindung wird nachfolgend unter Bezugnahme auf das aus der Figur 1 ersichtliche Ausf·uhrungsbeispiel n·aher erl·autert.

Die Erfindung wird nachfolgend unter Bezugnahme auf das aus der Figur 1 ersichtliche Ausf·uhrungsbeispiel n·aher erl·autert.Die Schaltung wird ·uber die Netzspannung UN mit nachgeschalteter Gleichrichterbr·ucke mit einer ungeregelten Gleichspannung versorgt und ist ·uber nur einen Transformator 1 vom Netz getrennt, wobei der Transformator die Stromversorgung f·ur das synchronisierte Schaltnetzteil sowie die Impuls- bzw. Hochspannungserzeugung ·ubernimmt. Wie durch die gestrichelte Linie zum Ausdruck kommt, ist die Netzseite v·ollig von der Schaltungsseite galvanisch getrennt.

In der Anlaufphase wird ·uber eine Startschaltung 7, die im einfachsten Fall aus einem hochohmigen Widerstand besteht, der Kondensator 11 aufgeladen. In dieser Phase gibt die Regelschaltung 2 keine Impulse an die Basis des Regelschalters 3 ab. Erst wenn die Spannung am Punkt A einen vorgegebenen Wert (z. B.

10 V) erreicht hat, wird ·uber eine regelschaltungsinterne Stabilisierungsschaltung die gesamte Schaltung in Betrieb genommen. Die Regelschaltung 2 liefert Impulse an die Basis des Regelschalters 3, tastet also den Regelschalter 3 auf. ueber den Regelschalter 3 fliesst somit ein pulsierender Strom in die Prim·arwicklung n1 des Transformators.

Die Wicklungen nl, n3 und n5 sind fest miteinander verkoppelt. Die Wicklungen n2, n4, n6 und n7 sind untereinander fest, aber lose an die vorgenannten Wicklungen nl, n3 und n5 gekoppelt. Ein Beispiel daf·ur, wie die genannten Kopplungsverh·altnisse erreicht werden k·onnen, zeigt die Figur 2.

Die Wicklu

ng n5 liefert ·uber eine Diode 10 einen gegen·uber der

Anlaufphase h·oheren Strom an den Kondensator 11, so dass in der

weiteren Folge die Versorgung der Regelschaltung 2 sichergestellt ist.

ng n5 liefert ·uber eine Diode 10 einen gegen·uber der

Anlaufphase h·oheren Strom an den Kondensator 11, so dass in der

weiteren Folge die Versorgung der Regelschaltung 2 sichergestellt ist.Durch die zweite, fest an n1 und lose an n2 angekoppelte Sekund·arwicklung n3 wird die Niedervoltspannung f·ur die Kleinsignalstufen und die NF-Stufe und den Horizontaloszillator bzw. die Treiberschaltung 13 der Horizontalendstufe 14 gewonnen, und damit die Ansteuerung des Ablenktransistors 4 sichergestellt. In die lose an n1 gekoppelte Sekund·arwicklung wird n2 In die lose an n1 gekoppelte Sekund·arwickl£ung n2 wird eine Spannung induziert, die nach Gleichrichtung mittels einer Diode 8 an den Kondensator 9 die ben·otigte Betriebsspannung f·ur den Ablenkkreis liefe

rt und somit den Anlauf der

Horizontalendstufe herbeif·uhrt.

rt und somit den Anlauf der

Horizontalendstufe herbeif·uhrt.·Uber die Trennstelle n 1/n2 wird ferner die an der Ablenkwicklung 15 stehende Spannung w·ahrend des K·ucklaufintervalls der Ablenkschaltung invertiert auf die Prim·arwicklung n1 betragen, um den Strom im Hauptstromweg w·ahrend der R·ucklaufzeit bei der Schaltung des Regelschalters 3 und damit die Abschaltverluste zu vermindern. Dieser Vorgang ist ausf·uhrlich beispielsweise in der DE-OS 28 35 946 dargestellt.

Aus einer fest an die Wicklung n2 und lose an n1 angekoppelten Wicklung n4 des Transformators wird eine R·ucklauf spannung gewonnen, die abh·angig von der Belastung der Wicklung n2 ist.

Strahlstrom·anderungen in der Hochspannungserzeugung ·uber die Wicklung n6 und der Hochspannungskaskade 12 (bzw. Split) werden ·uber die fest an n6 gekoppelte Wicklung n2 bzw. die fest an n2 ge

koppelte Wicklung n4 an die

Regelschaltung 2 weitergegeben, die die Stromflusszeit im

Hauptstromkreis bzw. den Regelschalter 3 beeinflusst. Somit werden ·uber

die Regelschaltung 2 Belastungsschwankungen ausgeregelt.

koppelte Wicklung n4 an die

Regelschaltung 2 weitergegeben, die die Stromflusszeit im

Hauptstromkreis bzw. den Regelschalter 3 beeinflusst. Somit werden ·uber

die Regelschaltung 2 Belastungsschwankungen ausgeregelt.Hingegen werden Belastungs·anderungen in der Wicklung n3, wie sie beispielsweise durch NF-Last·anderungen gegeben sind, fast nicht nachgeregelt, da die Wicklung n3 nur lose mit den Wicklungen n2 und n4 verkoppelt ist. Deshalb ist die Zeilenablenkschaltung weitgehend unabh·angig von Last·anderungen in der Sekund·arwicklung n3.

Die Netzspannungsnachregelung f·ur die Spannungen, die aus der Wicklung n3 gewonnen werden, erfolgt indirekt ·uber die Regelimpulse der Wicklung n4 So w·urde sich beispielsweise bei Netzunterspannung die R·ucklauf spannung ohne Nachregelung verringern.

Durch die Impulse der Wicklung n4 wird jedoch ·uber die Regelschaltung 2 die Leitzeit des Regelschalters 3 verl·angert. Damit wird mehr Energie von der Prim·arauf die Sekund·arseite ·ubertragen und demzufolge Netzspannungs·anderungen ausgeglichen.

Bei der Umschaltung vom Normalbetrieb in den Standby- Betrieb schaltet der Regelkreis 2 die Spannung ¢am Punkt A auf den vorgegebenen Wert von z. B. 10 V.

Diese Standby-Umschaltung steht in Verbindung mit einer Verk·urzung der Leitzeit des Regel schalters 3, die wie folgt ausgel·ost wird: ·Uber die

Wicklung n3 bzw.

eine Treiberschaltung 13 der Horizontalansteuerstufe wird die Basis des

Ablenk transistors 4 so gesteuert, dass der Ablenktransistor st·andig

leitet. Demzufolge kann sich im Kondensator 9 und damit auch in der

Sekund·arwicklung n2 keine Spannung aufbauen. Da die Wicklung n6 f·ur

die Hoch spannungs erzeugung, die Wicklung n7 f·ur die Erzeugung einer

Heizspannung und sonstige Impulsspannungen sowie die Wicklung n4 f·ur

die Synchronisation und Steuerung der Regelschaltung 2 fest mit der

Wicklung n2 verkoppelt sind, k·onnen weder Hochspannung noch Heizung

noch sonstige Impuls spannungen entstehen.

Wicklung n3 bzw.

eine Treiberschaltung 13 der Horizontalansteuerstufe wird die Basis des

Ablenk transistors 4 so gesteuert, dass der Ablenktransistor st·andig

leitet. Demzufolge kann sich im Kondensator 9 und damit auch in der

Sekund·arwicklung n2 keine Spannung aufbauen. Da die Wicklung n6 f·ur

die Hoch spannungs erzeugung, die Wicklung n7 f·ur die Erzeugung einer

Heizspannung und sonstige Impulsspannungen sowie die Wicklung n4 f·ur

die Synchronisation und Steuerung der Regelschaltung 2 fest mit der

Wicklung n2 verkoppelt sind, k·onnen weder Hochspannung noch Heizung

noch sonstige Impuls spannungen entstehen.Damit sind s·amtliche im Standby-Betrieb nicht ben·otigten Spannungen abgeschaltet, ziehen also keine Leistung aus dem Netz. Ausserdem schaltet wegen des Wegfalls der R·ucklauf spannungen an n4 die Regelschaltung im beschriebenen Sinne den Regel schalter 3 auf Standby-Betrieb um.

Dagegen ist die im Standby-Betrieb n·otige Versorgung der Sekund·arseite mit Niedervoltspannung weiterhin gew·ahrleistet, da die Wicklung n3, ·uber die diese Versorgung erfolgt, fest mit der Prim·arwicklung n1 und nur lose mit der Sekund·arwicklung n2 verkoppelt ist. Die Nachregelung der Niedervoltspannung kann - falls n·otig - mit Hilfe der Spannung erfolgen, die in die ebenfalls fest an n1 gekoppelte Wicklung n5 induziert wird, die ansonsten nur die Energie f·ur die Versorgung der Regelschaltung liefert.

Der ·Ubergang vom Standby-Betrieb auf den

Normalbetrieb geschieht durch die Sperrung des Ablenktransistors 4 und

dessen weitere periodische Ansteuerung. Die an der Wicklung n2

entstehende Spannung wird in der fest an n2 gekoppelten Wicklung n4

induziert. Diese R·uckschlagimpulse gelangen an den Triggereingang der

Regelschaltung 2. Diese f·uhrt einen internen Spannungsvergleich durch

und f·uhrt die Schaltung wieder in den geregelten Normalzustand ·uber.

Der ·Ubergang vom Standby-Betrieb auf den

Normalbetrieb geschieht durch die Sperrung des Ablenktransistors 4 und

dessen weitere periodische Ansteuerung. Die an der Wicklung n2

entstehende Spannung wird in der fest an n2 gekoppelten Wicklung n4

induziert. Diese R·uckschlagimpulse gelangen an den Triggereingang der

Regelschaltung 2. Diese f·uhrt einen internen Spannungsvergleich durch

und f·uhrt die Schaltung wieder in den geregelten Normalzustand ·uber.Die dargestellte Schaltung erm·oglicht es somit, den Ablenktransistor 4 der Horizontalendstufenschaltung in besonders einfacher Weise f·ur die Steuerung des Standby-Betriebes zu verwenden.

Ein besonderer Vorteil der erfindungsgem·assen Schaltung liegt darin, dass im Falle einer sekund·arseitigen St·orung, z. B. einem Kurzschluss der Diode oder des Kondensators 16, die Schaltung automatisch in den Standby-Betrieb ·ubergef·uhrt wird. Denn im Falle eines Kurzschlusses der Diode 8 oder des Kondensators 16 kann sich an n2 keine Spannung aufbauen. Dies gilt ebenso f·ur die Wicklung n4, die fest an n2 gekoppelt ist und die R·uckschlagimpulse an den Trigger

eingang der Regelschaltung 2 liefert.

Auch an der Wicklung n6 f·ur die Hochspannungserzeugung und der Wicklung

n7 f·ur die Erzeugung einer Heizspannung, die beide ebenfalls fest an

n2 gekoppelt sind, kann sich keine Spannung aufbauen.

eingang der Regelschaltung 2 liefert.

Auch an der Wicklung n6 f·ur die Hochspannungserzeugung und der Wicklung

n7 f·ur die Erzeugung einer Heizspannung, die beide ebenfalls fest an

n2 gekoppelt sind, kann sich keine Spannung aufbauen.--------------------------------------------------------------------------------

TDA8140 HORIZONTAL DEFLECTION POWER DRIVER

DESCRIPTION

The TDA 8140 is a monolithic integrated circuit designed

to drive the horizontal deflectionpower transistor.

The current source characteristic of this device is

adapted to the on-linear current gain behaviour of

the power transistor providing a minimum power

dissipation. The TDA8140 is internally protected

against short circuit and thermal overload.

During the active deflection phase the collector

current of the power transistor is linearly rising and

the driving circuitry mustbe adaptedto the required

base current in order to ensure the power transistor

saturation.

According to the limited components number the

typical approach of the present TVs provides only

a rough approximation of this objective ; in Figure 5

wegive a comparisonbetweenthe typical real base

current and the ideal base current waveform and

the collector waveform.

The marked area represents a useless base current

which gives an additional power dissipati

on on

on onthe power transistor.

Furthermoreduring the turn-ONand turn-OFFtransient

phase of the chassis the power transistor is

extremely stressed when the conventionalnetwork

cannot guarantee the saturation ; for this reason,

generally, the driving circuit must be carefully designed

and is different for each deflection system.

The new approach, using the TDA 8140, overcomes

these restrictions by means of a feedback

principle.

As shown in Figure 5, at each instant of time the

ideal base current of the power transistor results

from its collector current divided by such current

gain which ensure the saturation ; thus the required

base current Ib can be easily generated by a feedback

transconductanceamplifier gm which senses

the deflection current across the resistor Rs at the

emitter of the power transistor and delivers :

Ib = RS . gm . Ie

The transconductance must only fulfill the condition

:

1

1 + bmin V 1

RS

<>

RS

Where bmin is the minimum current gain of the

transistor. This method always ensures the correct

base current and acts time independent on principle.

For the turn-OFF, the base of the power transistor

For the turn-OFF, the base of the power transistormust be discharged by a quasi linear time decreasing

current as given in Figure 6.

Conventional driver systems inherently result into

a stable condition with a constant peak current

magnitude.

This is due to the constant base charge in the

turn-ON phase independent from the collector current

; hence a high peak current results into a low

storage time of the transistor because the excess

base charge is a minimum and vice versa. In the

active deflection the required function, high peak

current-fast switch-OFF and low peak current-slow

switch-OFF, is obtained by a controlled base discharge

current for the power transistor ; the negative

slope of this ramp is proportional to the actual

sensed current.

As a result, the active driving system even improves

the sharpnessof vertical lines on the screen

compared with the traditional solution due to the

increasedstability factor of the loop representedas

the variation of the storagetime versus the collector

peak current.

TUA

2000-4 (SIEMENS)

2000-4 (SIEMENS)Bipolar Television Tuner IC for Frequency Ranges up to 700 MHz

SIEMENS SDA3202-2

General Purpose Phase Locked Loop Device - VCO tuner combo PLL, I2C Bus

SDA2516 EAROM

Features- Word-organized reprogrammable nonvolatile memory

in n-channel floating-gate technology (E2PROM)

- 128 ´ 8-bit organization

- Supply volta

ge 5 V

ge 5 V- Serial 2-line bus for data input and output (I2C Bus)

- Reprogramming mode, 10 ms erase/write cycle

- Reprogramming by means of on-chip control (without

external control)

- Check for end of programming process

- Data retention > 10 years

- More than 104 reprogramming cycles per address

- Compatible with SDA 2516. Exception:

Conditions for total erase and current consumption.

I2C Bus Interface

The I2C Bus is a bidirectional 2-line bus for the transfer of data between various integrated circuits.

It consists of a serial data line SDA and a serial clock line SCL. The data line requires an external

pull-up resistor to VCC (open drain output stage).

The possible operational states of the I2C Bus are shown in figure 1. In the quiescent state, both

lines SDA and SCL are high, i.e. the output stage of the data line is disabled. As long a SCL remains

"1", information changes on the data bus indicate the start or the end of data transfer between two

components.

The transition on SDA from "1" to "0" is a start condition, the transition from "0" to "1" a stop

condition. During a data transfer the information on the data bus will only change while the clock line

SCL is "0". The information on SDA is valid as long as SCL is "1".

In conjunction with an I2C Bus system, the memory component can operate as a receiver and as a

transmitter (slave receiver or slave transmitter). Between a start and stop condition, information is

always transmitted in byte-organized form. Between the trailing edge of the eighth clock pulse and a ninth acknowledge clock pulse, the memory component sets the SDA line to low as a confirmation

of reception, if the chip select conditions have been met. During the output of data, the data output

of the memory is high in impedance during the ninth clock pulse (acknowledge master).

The signal timing required for the operation of the I2C Bus is summarized in figure 2.

Control Functions of the I2C Bus

The memory component is controlled by the controller (master) via the I2C Bus in two operating

modes: read-out cycle, and reprogramming cycle, including erase and write to a memory address.

In both operating modes, the controller, as transmitter, has to provide 3 bytes and an additional

acknowledge clock pulse to the bus after the start condition. During a memory read, at least nine

additional clock pulses are required to accept the data from the memory and the acknowledge

master, before the stop condition may follow. In the case of programming, the active programming

process is only started by the stop condition after data input (see figure 3).

The chip select word contains the

3 chip select bits CS0, CS1 and CS2, thus allowing 8 memory

3 chip select bits CS0, CS1 and CS2, thus allowing 8 memorychips to be connected in parallel. Chip select is achieved when the three control bits logically

correspond to the selected conditions at the select inputs.

Check for End of Programming or Abortion of Programming Process

If the chip is addressed during active reprogramming by entering CS/E, the programming process

is terminated. If, however, it is addressed by entering CS/A, the entry will be ignored. Only after

programming has been terminated will the chip respond to CS/A. This allows the user to check

whether the end of the programming process has been reached (see figure 3).

Memory Read

After the input of the first two control words CS/E and WA, the resetting of the start condition and the

input of a third control word CS/A, the memory is set ready to read. During acknowledge clock

nine, the memory information is transferred in parallel mode to the shift register. Subsequent to the

trailing edge of the acknowledge clock, the data output is low impedance and the first data bit can

be sampled, (see figure 4).

With every shift clock, an additional bit reaches the output. After reading a byte, the internal address

counter is automatically incremented when the master receiver switches the data line to “low” during

the ninth clock (acknowledge master). Any number of memory locations can thus be read one after

the other. At address 128, an overflow to address 0 is not initiated. With the stop condition, the data

the other. At address 128, an overflow to address 0 is not initiated. With the stop condition, the dataoutput returns to high-impedance mode. The internal sequence control of the memory component

is reset from the read to the quiescent with the stop condition.

Memory Reprogramming

The reprogramming cycle of a memory word comprises an erase and a subsequent write process.

During erase, all eight bits of the selected word are set into "1" state. During write, "0" states are

generated according to the information in the internal data register, i.e. according to the third input

control word.

After the 27th and the last clock of the control word input, the active programming process is started

by the stop condition. The active reprogramming process is executed under onchip control.

The time required for reprogramming depends on component deviation and data patterns.

Therefore, with rated supply voltage, the erase/write process extends over max. 20 ms, or more

typically, 10 ms. In the case of data word input without write request (write request is defined as data

bit in data register set to “0”), the write process is suppressed and the programming time is

shortened. During a subsequent programming of an already erased memory address, the erase

process is suppressed again, so that the reprogramming time is also shortened.

PHILIPS TDA3566A PAL/NTSC decoder,

GENERAL DESCRIPTION

GENERAL DESCRIPTIONThe TDA3566A is a decoder for the

PAL and/or NTSC colour television

standards. It combines all functions

required for the identification and

demodulation of PAL/NTSC signals.

Furthermore it contains a luminance

amplifier, an RGB-matrix and

amplifier. These amplifiers supply

output signals up to 4 V peak-to-peak

(picture information) enabling direct

drive of the discrete output stages.

The circuit also contains separate

inputs for data insertion, analog and

digital, which can be used for text

display systems.

FEATURES

• A black-current stabilizer which

controls the black-currents of the

three electron-guns to a level low

enough to omit the black-level

adjustment

• Contrast control of inserted RGB

signals

• No black-level disturbance when

non-synchronized external RGB

signals are available on the inputs

• NTSC capability with hue control.

APPLICATIONS

• Teletext/broadcast antiope

• Channel number display.

FUNCTIONAL DESCRIPTION

The TDA3566A is a further

development of the TDA3562A. It has

the same pinning and nearly the

same application. The differences

between the TDA3562A and the

TDA3566A are as follows:

• The NTSC-application has largely

been simplified. In the event of

NTSC the chrominance signal is

now internally coupled to the

demodulators, automatic

chrominance control (ACC) and

phase detectors. The chrominance

output signal (pin 28) is thus

suppressed. It follows that the

external switches and f

ilters which

ilters whichare required for the TDA3562A are

not required for the TDA3566A.

There is no difference between the

amplitudes of the colour output

signals in the PAL or NTSC mode.

• The clamp capacitor at pins 10, 20

and 21 in the black-level

stabilization loop can be reduced to

100 nF provided the stability of the

loop is maintained. Loop stability

depends on complete application.

The clamp capacitors receive a

pre-bias voltage to avoid coloured

background during switch-on.

• The crystal oscillator circuit has

been changed to prevent parasitic

oscillations on the third overtone of

the crystal. Consequently the

optimum tuning capacitance must

be reduced to 10 pF.

• The hue control has been improved

(linear).

Luminance amplifier

The luminance amplifier is voltage

driven and requires an input signal of

450 mV peak-to-peak (positive

video). The luminance delay line must

be connected between the IF

amplifier and the decoder.

The input signal is AC coupled to the

input (pin 8). After amplification, the

black level at the output of the

preamplifier is clamped to a fixed DC

level by the black level clamping

circuit. During three line periods after

vertical blanking, the luminance

signal is blanked out and the black

level reference voltage is inserted by

a switching circuit.

This black level reference voltage is

controlled via pin11 (brightness). At

the same time the RGB signals are

clamped. Noise and residual signals

have no influence during clamping

thus simple internal clamping circuitry

is used.

Chrominance amplifiers

The chrominance amplifier has an

asymmetrical input. The input signal

must be AC coupled (pin 4) and have

a minimum amplitude of

40 mV peak-to-peak.

The gain control stage has a control

range in excess of 30 dB, the

maximum input signal must not

exceed 1.1 V peak-to-

peak,

peak,otherwise clipping of the input signal

will occur.

From the gain control stage the

chrominance signal is fed to the

saturation control stage. Saturation is

linearly controlled via pin 5. The

control voltage range is 2 to 4 V, the

input impedance is high and the

saturation control range is in excess

of 50 dB.

The burst signal is not affected by

saturation control. The signal is then

fed to a gated amplifier which has a

12 dB higher gain during the

chrominance signal. As a result the

signal at the output (pin 28) has a

burst-to-chrominance ratio which is

6 dB lower than that of the input

signal when the saturation control is

set at −6 dB.

The chrominance output signal is fed

to the delay line and, after matrixing,

is applied to the demodulator input

pins (pins 22 and 23). These signals

are fed to the burst phase detector. In

the event of NTSC the chrominance

signal is internally coupled to the

demodulators, ACC and phase

detectors.

Oscillator and identification circuit

The burst phase detector is gated

with the narrow part of the sandcastle

pulse (pin 7). In the detector the

(R−Y) and (B−Y) signals are added to

provide the composite burst signal

again.

This composite signal is compared

with the oscillator signal

divided-by-2 (R−Y) reference signal.

The control voltage is available at

pins 24 and 25, and is also applied to

the 8.8 MHz oscillator. The 4.4

MHz

MHzsignal is obtained via the divide-by-2

circuit, which generates both the

(B−Y) and (R−Y) reference signals

and provides a 90° phase shift

between them.

The flip-flop is driven by pulses

obtained from the sandcastle

detector. For the identification of the

phase at PAL mode, the (R−Y)

reference signal coming from the PAL

switch, is compared to the vertical

signal (R−Y) of the PAL delay line.

This is carried out in the H/2 detector,

which is gated during burst.

When the phase is incorrect, the

flip-flop gets a reset from the

identification circuit. When the phase

is correct, the output voltage of the

H/2 detector is directly related to the

burst amplitude so that this voltage

can be used for the ACC.

To avoid 'blooming-up' of the picture

under weak input signal conditions

the ACC voltage is generated by peak

detection of the H/2 detector output

signal. The killer and identification

circuits receive their information from

a gated output signal of H/2 detector.

Killing is obtained via the saturation

control stage and the demodulators to

obtain good suppression.

The time constant of the saturation

control (pin 5) provides a delayed

switch-on after killing. Adjustment of

the oscillator is achieved by variation

of the burst phase detector load

resistance between pins 24 and 25

(see Fig.8).

With this application the trimmer

capacitor in series with the 8.8 MHz

crystal (pin 26) can be replaced by a

fixed value capacitor to compensate

for unbalance of the phase detector.

Demodulator

The (R−Y) and (B−Y) demodulators

are driven by the colour difference

signals from the delay-line matrix

circuit and the reference signals from

the 8.8 MHz divider circuit. The (R−Y)

reference signal is fed via the

PAL-switch. The output signals are

fed to the R and B matrix circuits and

to the (G−Y) matrix to p

rovide the

rovide the(G−Y) signal which is applied to the

G-matrix. The demodulation circuits

are killed and blanked by by-passing

the input signals.

NTSC mode

The NTSC mode is switched on when

the voltage at the burst phase

detector outputs (pins 24 and 25) is

adjusted below 9 V.

To ensure reliable application the

phase detector load resistors are

external. When the TDA3566A is

used only for PAL these two 33 kΩ

resistors must be connected to +12 V

(see Fig.8).

For PAL/NTSC application the value

of each resistor must be reduced to

20 kΩ (with a tolerance of 1%) and

connected to the slider of a

potentiometer (see Fig.9). The

switching transistor brings the voltage

at pins 24 and 25 below 9 V which

switches the circuit tot the NTSC

mode.

The position of the PAL flip-flop

ensures that the correct phase of the

(R−Y) reference signal is supplied to

the (R−Y) demodulator.

The drive to the H/2 detector is now

provided by the (B−Y) reference

signal. In the PAL mode it is driven by

the (R−Y) reference signal. Hue

control is realized by changing the

phase of the reference drive to the

burst phase detector.

This is achieved by varying the

voltage at pins 24 and 25 between

7.0 V and 8.5 V, nominal position

7.65 V. The hue control characteristic

is shown in Fig.6.

RGB matrix and amplifiers

The three matrix and amplifier circuits

are identical and only

one circuit will

one circuit willbe described.

The luminance and the colour

difference signals are added in the

matrix circuit to obtain the colour

signal, which is then fed to the

contrast control stage.

The contrast control voltage is

supplied to pin 6 (high-input

impedance). The control range is

+5 dB to −11.5 dB nominal. The

relationship between the control

voltage and the gain is linear (see

Fig.3).

During the 3-line period after blanking

a pulse is inserted at the output of the

contrast control stage. The amplitude

of this pulse is varied by a control

voltage at pin 11. This applies a

variable offset to the normal black

level, thus providing brightness

control.

The brightness control range is 1 V to

3.6 V. While this offset level is

present, the black-current input

impedance (pin 18) is high and the

internal clamp circuit is activated. The

clamp circuit then compares the

reference voltage at pin 19 with the

voltage developed across the

external resistor network RA and

RB(pin 18) which is provided by

picture tube beam current.

The output of the comparator is

stored in capacitors connected from

pins 10, 20 and 21 to ground which

controls the black level at the output.

The reference voltage is composed

by the resistor divider network and the

leakage current of the picture tube

into this bleeder. During vertical

blanking, this voltage is stored in the

capacitor connected to pin 19, which

ensures that the leakage current of

the CRT does not influence the black

current measurement.

The RGB output signals can never

exceed a level of 10.6 V. When the

signal tends to exceed this level the

output signal is clipped. The black

level at the outputs (pins 13, 15 and

17) will be approximately 3 V. This

level depends on t

he spread of the

he spread of theguns of the picture tube. If a beam

current stabilizer is not used it is

possible to stabilize the black levels at

the outputs, which in this application

must be connected to the black

current measuring input (pin 18) via a

resistor network.

Data insertion

Each colour amplifier has a separate

input for data insertion.

A 1 V peak-to-peak input signal

provides a 3.8 V peak-to-peak output

signal.

To avoid the black-level of the

inserted signal differing from the black

level of the normal video signal, the

data is clamped to the black level of

the luminance signal. Therefore AC

coupling is required for the data

inputs.

To avoid a disturbance of the blanking

level due to the clamping circuit, the

source impedance of the driver circuit

must not exceed 150 Ω. The data

insertion circuit is activated by the

data blanking input (pin 9). When the

voltage at this pin exceeds a level of

0.9 V, the RGB matrix circuits are

switched off and the data amplifiers

are switched on.

To avoid coloured edges, the data

blanking switching time is short. The

amplitude of the data output signals is

controlled by the contrast control at

pin 6. The black level is equal to the

video black level and can be varied

between 2 and 4 V (nominal

condition) by the brightness control

voltage at pin 11.

Non-synchronized data signals do not

disturb the black level of the internal

signals.

Blanking of RGB and data signals

Both the RGB and data signals can

be blanked via the sandcastle input

(pin 7). A slicing level of 1.5 V is used

for this blanking function, so that the

wide part of the sandcastle pulse is

separated from the remainder of the

pulse. During blanking a level of +1 V

is available at the output. To prevent

parasitic oscillations on the third

overtone of the crystal the optimum

tuning capacitance should be 10 pF.

THE PHILIPS TDA3562A Circuit arrangement for the control of a picture tube :

THE PHILIPS TDA3562A Circuit arrangement for the control of a picture tube :1. Circuit arrangement for the control of at least one beam current in a picture tube by a picture comprising

a control loop which in one sampling interval obtains a measuring signal from the value of the beam current on the occurrence of a given reference level in the picture signal, stores a control signal derived therefrom until the next sampling interval and thereby adjusts the beam current to a value preset by a reference signal.

and a trigger circuit which suppresses auxiliary pulses used to generate the beam current after the picture tube has been started up and issues a switching signal for the purpose of closing the control loop during the sampling intervals and for releasing the control of the beam current by the picture signal after the measuring signal has exceeded the threshold value,

a change detection arrangement which delivers a change signal when the stored signal has assumed a largely constant value, and

a logic network which does not release the control of the beam current by the picture signal outside the sampling intervals until the change signal has also been issued after the switching signal.

2. Circuit arrangement as set forth in claim 1, in which the picture signal comprises several color signals for the control of a corresponding number of beam currents for the display of a color picture in the picture tube and the control loop stores a part measuring signal or a part control signal derived therefrom for each color signal, characterized in that the change detection arrangement includes a change detector for each color signal which delivers a part change signal when the relevant stored signal has assumed a largely constant value, and the logic network does not release the control of the beam currents by the color signals outside the sampling intervals until the part change signals have been delivered by all change detectors.

3. Circuit arrangement as set forth in claim 1, including a comparator arrangement which compares the measuring signal with the reference signal and derives the control signal from this comparison, characterized in that the change detection arrangement detects a change in the control signal with respect to time and issues the change signal when the control signal has assumed a largely constant value.

4. Circuit arrangement as set forth in claims 1, 2, 3 including a control signal memory which contains at least one capacitor, characterized in that the change detection arrangement delivers the change signal when a charge-reversing current of the capacitor occuring during the starting up of the picture tube falls below a limit value.

5. Circuit arrangement as set forth in claim 2, including a comparator arrangement which compares the measuring signal with the reference signal and derives the control signal from this comparison, characterized in that the change detection arrangement detects a change in the control signal with respect to time and issues the change signal when the control signal has assumed a largely constant value.

The invention relates to a circuit arrangement for the control of at least one beam current in a picture tube by a picture signal with a control loop which in one sampling interval obtains a measuring signal from the value of the beam current on the occurrence of a given reference level in the picture signal, stores a control signal derived therefrom until the next sampling interval and by this means adjusts the beam current to a value preset by a reference signal, and with a trigger circuit which suppresses auxiliary pulses used to generate the beam current after the picture tube is turned on and issues a switching signal for the purpose of closing the control loop during the sampling intervals and releasing the control of the beam current by the picture signal after the measuring signal has exceeded a threshold value.

Such a circuit arrangement has been described in Valvo Technische Information 820705 with regard to the integrated color decoder circuit PHILIPS TDA3562A and is used in this as a so-called cut-off point control. In the known circuit arrangement, such a cut-off point control provides automatic compensation of the so-called cut-off point of the picture tube, i.e. it regulates the beam current in the picture tube in such a way that for a given reference level in the picture signal the beam current has a constant value despite tolerances and changes with time (aging, thermal modifications) in the picture tube and the circuit arrangement, thereby ensuring correct picture reproduction.

Such a blocking point control is particularly advantageous for the operation of a picture tube for the display of color pictures because in this case there are several beam currents for different color components of the color picture which have to be in a fixed ratio with one another. If this ratio changes, for example, as the result of manufacturing tolerances or ageing processes, distortions of the colors occur in the reproduction of the color picture. The bea

m currents, therefore, have to be very

accurately balanced. The said cut-off point control prevents expensive

adjustment and maintenance time which is otherwise necessary.

m currents, therefore, have to be very

accurately balanced. The said cut-off point control prevents expensive

adjustment and maintenance time which is otherwise necessary. Conventional picutre tubes are constructed as cathode-ray tubes with hot cathodes which require a certain time after being turned on for the hot cathodes to heat up. Not until a final operating temperature has been reached do these hot cathodes emit the desired beam currents to the full extent, while gradually rising beam currents occur in the time interval when the hot cathodes are heating up. The instantaneous values of these beam currents depend on the instantaneous temperatures of the hot cathodes and on the accelerating voltages for the picture tube which build up simultaneously with the heating process and are undefined until the end of the heating time. After the picture tube is turned on, these values initially produce a highly distorted picture until the beam currents have attained their final value. These picture distortions after the picture tube is turned on are even further intensified by the fact that the cut-off point control is not yet adjusted to the beam currents which flow after the heating time is over.

For the purpose of suppressing distorted pictures during the heating time of the hot cathodes, the known circuit arrangement has a turn-on delay element operating as a trigger circuit which, in essence, contains a bistable flip-flop. When the picture tube and the circuit arrangement controlling the beam currents flowing in it are turned on, the flip-flop is switched into a first state in which it interrupts the supply of the picture signal to the picture tube. Thus, during the heating time the beam currents are suppressed, and the picture tube does not yet display any picture. In sampling intervals which are provided subsequent to flybacks of the cathode beam into an initial position on the changeover from the display of one picture to the display of a subsequent picture and even within the changeover, that is outside the display of pictures, the picture tube is controlled for a short time in such a way that beam currents occur when the hot cathodes are sufficiently heated up and an accelerating voltage is resent. If these currents exceed a certain threshold value, the flip-flop circuit switches into a second state and releases the picture signal for the control of the beam currents and the cut-off point control.

It is found, however, that the picture displayed in the picture tube immediately after the switching over of the flip-flop is still not fault-free. Because, in fact, the beam currents are supported during the heating time of the hot cathodes, the cut-off point control cannot respond yet. This response of the cut-off point control takes place only after the beam currents are switched on, i.e. after the flip-flop is switched into the second state and therefore at a time in w

hich the picture signal already controls the beam

currents. In this way the response of the blocking point control makes

its presence felt in the picture displayed.

hich the picture signal already controls the beam

currents. In this way the response of the blocking point control makes

its presence felt in the picture displayed. With the known circuit arrangement the brightness of the picture gradually increases, during the response of the cut-off point control, from black to the final value.

This slow increase in the picture brightness after the tube is turned on is disturbing to the eyes of the viewer not only in the case of the black-and-white picture tubes with one hot cathode, but especially so in the case of colour picture tubes which usually have three hot cathodes. With a color picture tube, color purity errors can also occur in addition to the change in the picture brightness if, as a result of different speeds of response of the cut-off point control for the three beam currents, there are found to be intermittent variations from the interrelation between the beam currents required for a correct picture reproduction.

SUMMARY OF THE INVENTION

The aim of the invention is to create a circuit arrangement which suppresses the above-described disturbances of brightness and color of the displayed picture when the picture tube is being started.

The invention achieves this aim in that a circuit arrangement of the type mentioned in the preamble contains a change detection arrangement which emits a change signal when the stored signal has assumed an essentially constant value, and a logic network which does not release the control of the beam current by the picture signal until the change signal has also been emitted after the switching signal.

In the circuit arrangement according to the invention, therefore, the display of the picture is suppressed after the picture tube is turned on until the cut-off point control has responded. If the picture signal then starts to control the beam current, a perfect picture is displayed immediately. In this way, all the disturbances of the picture which affect the viewer's pleasure are suppressed. The circuit arrangement of the invention is of simple design and can be combined on one semiconductor wafer with the existing picture signal processing circuits and also, for example, with the known circuit arrangement for cut-off point control. Such an integrated circuit arrangement not only requires very little space on the semiconductor wafer, but also needs no additional external leads. Thus the circuit arrangement of the invention can be arranged, for example, in an integrated circuit which has precisely the same external connections as known integrated circuits. This means that an integrated circuit containing the circuit arrangement of the invention can be directly incorporated in existing equipment without the need for additional measures.

In one embodiment of the said circuit arrangement, in which the picture signal contains several color signals for the control of a corresponding number of beam currents for representing a color picture in the picture tube and, for each color signal, the control loop stores a part measuring signal or a part control signal derived from it, the change detection arrangement contains a change detector for each color signal which emits a part change signal when the relevant stored signal has assumed an essentially constant value, and the logic network does not release the control of the beam currents by the color signals outside the sampling intervals until the part change signals have been emitted from all change detectors.

In principle, therefore, such a circuit arrangement has three cut-off poi

nt controls for the three beam currents controlled

by the individual color signals. To reduce the cost of the circuitry,

the measuring stage is common to all the cut-off point controls, as in

the known circuit arrangement. All three beam currents are then measured

successively by this measuring stage. In this way, a part measuring

signal or a part control signal derived from it is obtained for each

beam current and is stored sesparately according to which of the beam

currents it belongs. Changes in the part measuring signal or part

control signal are detected for each beam current by one of the change

detectors each time. Each of these change detectors issues a part change

signal to the logic network. The latter does not release the control of

the beam currents by the picture signal outside the sampling intervals

until all the part change signals indicate that the part measuring

signal or the part control signal, as the case may be, remains constant.

This ensures that the cut-off point controls for the beam currents of

all color signals have responded when the picture appears in the picture

tube.

nt controls for the three beam currents controlled

by the individual color signals. To reduce the cost of the circuitry,

the measuring stage is common to all the cut-off point controls, as in

the known circuit arrangement. All three beam currents are then measured

successively by this measuring stage. In this way, a part measuring

signal or a part control signal derived from it is obtained for each

beam current and is stored sesparately according to which of the beam

currents it belongs. Changes in the part measuring signal or part

control signal are detected for each beam current by one of the change

detectors each time. Each of these change detectors issues a part change

signal to the logic network. The latter does not release the control of

the beam currents by the picture signal outside the sampling intervals

until all the part change signals indicate that the part measuring

signal or the part control signal, as the case may be, remains constant.

This ensures that the cut-off point controls for the beam currents of

all color signals have responded when the picture appears in the picture

tube. In a further embodiment of the circuit arrangement according to the invention with a comparator arrangement which compares the measuring signal with the reference signal and derives the control signal from this comparison, the change detection arrangement detects a change in the control signal with respect to time and issues the change signal when the control signal has assumed an essentially constant value. In the case of the representation of a color signal the comparator arrangement derives several part control signals, whose changes with time are detected by the change detectors, from a corresponding comparison of the part measuring signals with the reference signal. In this embodiment of the circuit arrangement of the invention, preference is given to storage of only the control signal or the part control signals for the purpose of controlling the beam currents.

In another embodiment of the circuit arrangement of the invention which includes a control signal memory which contains at least one capacitor in which a charge or voltage corresponding to the control signal is stored, the change detection arrangement issues the change signal when a charge-reversing current of the capacitor occurring during the turning on of the picture tube has fallen below a limit value and has thus at least largely decayed. Such a detection of the steady state of the cut-off point control is independent of the actual magnitude of the control signal and therefore independent of, for example, the level of the picture tube cut-off voltage, circuit tolerances or ageing processes in the circuit arrangement or the picture tube.

Detection of whether or not the charge-reversing current exceeds the limit value is performed preferentially by a current detector which is designed with a current mirror system which is arranged in a supply line to a capacitor acting as a control signal store. A current mirror arrangement of this kind supplies a current which coincides very precisely with the charging current of the capacitor. This current is then compared, preferably in a further device contained in the change detection arrangement, with a current representing a limit value or, after conversion into a voltage, with a voltage representing the limit value. The change signal is obtained from the result of this comparison.

On the other hand, digi

tal

memories may also be used as control signal memories, especially when

the picture signal is supplied as a digital signal and the blocking

point control is constructed as a digital control loop. In such a case,

the comparator arrangement, the change detection arrangement and the

trigger circuit are also designed as digital circuits. Then, the change

detection arrangement advantageously forms the difference of the signals

stored in the control signal memory in two successive sampling

intervals and compares this with the limit value formed by a digital

value. If the difference falls short of the limit value, the change

signal is issued.

tal

memories may also be used as control signal memories, especially when

the picture signal is supplied as a digital signal and the blocking

point control is constructed as a digital control loop. In such a case,

the comparator arrangement, the change detection arrangement and the

trigger circuit are also designed as digital circuits. Then, the change

detection arrangement advantageously forms the difference of the signals

stored in the control signal memory in two successive sampling

intervals and compares this with the limit value formed by a digital

value. If the difference falls short of the limit value, the change

signal is issued.BRIEF DESCRIPTION OF THE DRAWINGS

An embodiment of the invention is described in greater detail below with the aid of the drawings in which:

FIG. 1 shows a block circuit diagram of the embodiment,

FIG. 2 shows a somewhat more detailed block circuit diagram of the embodiment,

FIG. 3 shows time-dependency diagrams of some signals occurring in the circuit diagram shown in FIG. 2, and

FIG. 4 shows a somewhat moredetailed block circuit diagram of a part of the circuit diagram shown in FIG. 2.

DETAILED DESCRIPTION OF THE INVENTION