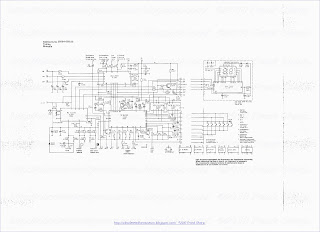

TUNING SYSTEM 96 PROGR. (ABSTIMMUNG BAUSTEIN 29504- 003.04)

96 Programs frequency synthesized tuning system based on SIEMENS uController and SIEMENS

synthesizer and memory.

- SDA2010 A013 uController

- SDA2112-3 (Uc controlled frequency systhesizer)

- SDA2006 (Memory x 3)512-Bit Nonvolatile EAROM SIEMENS SDA2006 MOS circuit

General features

• Nonvolatile memory of electrical, word-organized reprogrammability, in n channel floating gate technology

• 512-bit storage capacity (32 words of 16 bits, each)

• Serial word address, chip select, and instruction input via an 8-b1t or 12-bit control word (switchable by means of external components)

• Erase and write duration determined with the aid of chip-internal control

• Signal outputs with open-drain stages active signal inputs and outputs can be inverted by terminal wiring

• Number of reprogrammings > 104

• Unlimited number of read-out procedures without refresh

• Min. 10 years storage time

Circuit description

Data transfer

Data transfer with the SDA 2006 is performed serially via a 5-line bus, consisting of:

Data input D;

Data output D q/D;;"

Data input signal REC/REC (receive data)

Clock input <P/iP

Programming output signal [/L (load)

The active input or output levels, respectively, may be inverted via the input INV. They are switchable, as a group, in order to facilitate adaptation to different external circuits.

Read-out (figure 1a and 1b)

Prior to the read operation of the memory the 8-bit or 12-bit control word must be serially clocked into the data input D. 8 or 12 clock pulses, respectively, at the input <PIP are necessary for the input of the control word. During the input, the REC/REC input is active (active high for low at INV, active low for high at INV). The information input is closed by means of the trailing edge of the REC/REC signal and at chip select the read-out instruction is decoded. In this way, also the data output D ;/D 9 becomes low-ohmic. With the aid of a further clock pulse S, the read-out operation is initialized. The data is shifted with the trailing edge of further clock pulses. The LSB arrives at the data output with the first of these pulses. During the read-out operation via the control word either the first data bit D 1 or the ninth data bit D 9 can be chosen as LSB. The read-out operation can be discontinued after any number of shift pulses. Thus.every stored 16-bit data word can also be read split into two 8-bit data words.

Reprogramming (figure 2a and 2b)

Prior to programming, the 16-bit data word (D 1 as LSB, first), then the 8-bit or 12-bit control word at the data input D; must be clocked in by means of the active REC/REC signal. It is the trailing edge of the REC/REC signal which decodes the programming instruction at chip select. The reprogramming operation, however, only starts with the trailing edge of a further clock pulse and is recorded to the memory controller via the [/L signal.

The duration tprog of reprogramming is determined by chip-internal control. Independent of the external operating voltages VpH and Vp1the erase and the write operation are only finished after every memory has reached the desired state. During rewriting, the memory cannot be influenced externally, because the input REC/REC, PIP and D; remain blocked. Premature termination of the operation can only be caused by zero level at the input RES.

Reset function

A low level voltage at the input RES moves the memory into the reset status. A voltage divider is internally connected to the input. It reliably finishes the reset status for V00 >11 V.

Voltage supply

The SDA 2112-2 is fabricated in ASBC technology. In connection with a VCO (tuner) and a high-speed 1:64 divider, it forms a digitally programmable phase-locked loop for producing TV sets with PLL frequency-synthesis tuning. The PLL enables crystal-controlled setting of the tuner oscillator frequency for a 125 kHz rsolution in the frequency bands I/IIl, IV, and V.

A serial interface provides for simple connection to a microprocessor. The latter loads the programmable divider and the band-selection outputs with the appropriate information.

Features

@ No external integrator necessary

@ Internal buffer

@ Microprocessor compatible

SDA 2112-2 description (refer to block diagram) A switchable 16/17 counter is triggered by the ECL signal inputs F/F. The counter, in connection with a 4-bit and a 9-bit programmable, synchronous counter, forms a programmable, 13-bit synchronous divider using the dual-modulus technique, the 4-bit counter controlling the switchover from 16 to 17. Divider ratios of N = 256 to 8191 are possible. For test purposes the carry of the synchronous divider is available at the LDM output (open collector). The 16-bit shift register and latch is subdivided into 13 bits for storing the divider ratio N and 3 bits for controlling the three band-selection outputs. The telegram is shifted in via the serial data input IFO with the HL edge of the shift clock CPL when the enable input PLE is also on high level. First the complement of the divider ratio N, beginning with the LSB, is inserted in binary code, followed by the three control bits for the band-selection switching (see truth table). The 16-bit latch takes the data from the shift register when the enable input PLE is on low level. The IC includes a crystal-controlled, 3-MHz clock oscillator. The output signal is divided down to 1.953125 kHz (reference signal) by a 1/1536 reference divider. The oscillator frequency appears at the TTL output OSC. The clock of 62.5 kHz is available at the open-collector output CL. The divided input signal is compared with the reference signal in a digital phase detector. If the falling edge of the input signal appears prior to the falling edge of the reference signal, the DOWN output of the phase detector turns to high level for the duration of this phase difference. In the reverse case the UP output turns to high level. If the two signals are in phase, both outputs remain at low level. The UP/DOWN outputs control the two current sources I+ und! (charge pump). If the two outputs are low (PLL locked), the charge-pump output PD will turn to the high-impedance state (TRISTATE). An L signal appears at the LOCK IND output if frequency and phase are synchronous. The current sources I+ and I~ are then reduced from 300 to 100 pA. The current pulses generated by the charge pump are integrated to form the tuning voltage by means of an active lowpass filter (external pull-up resistor to supply Vso and external RC circuitry). The dc output signal appears at Viy, and serves as a tuning voltage for the VCO. The band-selection outputs (UHF, VHF, Bd I/II) contain current drains with open collectors. In this way PNP transistors working as band-selection switches can be connected directly without current-limiting resistors (see application circuit).

----------------------------------------------------------------------------------------------------------------------------------------

Features

@ 8 bit CPU, ROM, RAM, IN/OUT in a DIP 40 package

@ 4 analog outputs with 6 bit resolution

@ 30 digital IN/OUT lines

Two serial interfaces

Two 8 bit interfaces

Two 4 bit interfaces

Two test inputs

2 Kbyte ROM

64 byte RAM

10 ps cycle time — 1 or 2 cycles per instruction

Zero passage detector

Interface for mudulated digital signal

Interval timer/counter

5 V supply voltage

Instructions - subset of SAB 8048

Brief description

The SDA 2010 stresses application-specific control functions surpassing the former purely numeric computation performance. As a result, the use of additional hardware could be reduced and software operations have been simplified, optimizing cost savings during the developmental and production stages. Although the SDA 2010 was designed for electronic entertainment devices, it is equally suitable for mass-produced applications requiring highly economic components. The SDA 2010 includes a 2 Kbyte program memory (ROM), a 64 byte data memory (RAM) and four 6 bit D/A converters. The 30 digital IN/OUT lines are comprised of two 4 and 8 bit ports each, two test inputs and 2 serial interfaces consisting of one data and one clock line each. Test input TO processes signals modulated with approx. 30 kHz and is equipped with a digitai demoduiator, which derives the enveiope curve from the moduiaied digiiai signal. Since the digital demodulator forwards an unmodulated signal without changing it, test input TO can also function as a normal digital input during operations with standard H/L levels. Test input T1 includes a zero passage detector and can also serve as a normal digital input. The SDA 2010 is equipped with its own oscillator and timer/counter.

The instruction set includes 65 instructions (1-2 bytes), which can be processed in max. 2 cycles. Numerical problems can be processed in either binary or BCD arithmetic modes. The large number of available bit-handling instructions increases the efficiency of the controller functions. The program development and system testing for the SDA 2010 are carried out on the SME development system in conjunction with the SDA 2010 emulator board EMB U2. The EMB U2 emulator consists of one 2 K EPROM (SAB 2716) as well as a 40 pin plug which is used to insert an SAB 8035 type microprocessor or an ICE 48 plug. In addition, the EBM U2 contains all the necessary hardware to simulate the four analog outputs and the serial and parallel interfaces of the SDA 2010. A 40 wire cable is used to connect the U2 emulator with the user system. A version without the ROM (SDA 3010) is available for in-house software development on an SME system. Technical data of the SDA 2010

Maximum ratings must carefully be observed to prevent the IC from being permanently

damaged.

No comments:

Post a Comment

The most important thing to remember about the Comment Rules is this:

The determination of whether any comment is in compliance is at the sole discretion of this blog’s owner.

Comments on this blog may be blocked or deleted at any time.

Fair people are getting fair reply. Spam and useless crap and filthy comments / scrapers / observations goes all directly to My Private HELL without even appearing in public !!!

The fact that a comment is permitted in no way constitutes an endorsement of any view expressed, fact alleged, or link provided in that comment by the administrator of this site.

This means that there may be a delay between the submission and the eventual appearance of your comment.

Requiring blog comments to obey well-defined rules does not infringe on the free speech of commenters.

Resisting the tide of post-modernity may be difficult, but I will attempt it anyway.

Your choice.........Live or DIE.

That indeed is where your liberty lies.

Note: Only a member of this blog may post a comment.