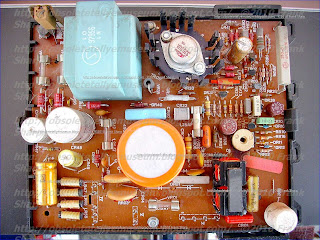

Video Luminance and chrominance unit : 592.601 with TDA3300B (Motorola)

(This is the first chassis from NORDMENDE employing the TDA3300B in the video processing, rendering possible the

automation of the catode cut - off adjustment and othe features in one ASIC)

automation of the catode cut - off adjustment and othe features in one ASIC)Video RGB Amplifiers unit : 592.500

If Video det - ampl unit : 492.089 / K WITH TDA2541 (PHILIPS)

Sound If dem + Amplifier unit : 492.319 / E with TDA2790 AND TDA1111

Frame deflection Unit : 492.308 / E

Synchronization Unit : 492.174

Line deflection Unit 492.309/D3 with TOSHIBA BU208

Power supply Unit with TOSHIBA S2530A

Tuner Prescaler + Synth Driver 592.389 with SAB1009B And ITT SAA1073

- VIDEO CHROMA PROCESSING WITH TDA3300 (MOTOROLA)

TDA3300 3301 TV COLOR PROCESSOR

This device will accept a PAL or NTSC composite video signal and output the

three color signals, needing only a simple driver amplifier to interface to the pic-

ture tube. The provision of high bandwidth on-screen display inputs makes it

suitable for text display, TV games, cameras, etc. The TDA3301 B has user con»

trol laws, and also a phase shift control which operates in PAL, as well as NTSC.

0 Automatic Black Level Setup

0 Beam Current Limiting

0 Uses Inexpensive 4.43 MHZ to 3.58 MHz Crystal

0 No Oscillator Adjustment Required

0 Three OSD Inputs Plus Fast Blanking Input

0 Four DC, High Impedance User Controls

0 lnterlaces with TDA33030B SECAM Adaptor

0 Single 12 V Supply

0 Low Dissipation, Typically 600 mW

The brilliance control operates by adding a pedestal to the output

signals. The amplitude of the pedestal is controlled by Pin 30.

During CRT beam current sampling a standard pedestal is

substituted, its value being equivalent tothe value given by V30 Nom

Brightness at black level with V30 Nom is given by the sum of three gun

currents at the sampling level, i.e. 3x20 |.1A with 100 k reference

resistors on Pins 16, 19, and 22.

During picture blanking the brilliance pedestal is zero; therefore, the

output voltage during blanking is always the minimum brilliance black

level (Note: Signal channels are also gain blanked).

Chrominance Decoder

The chrominance decoder section of the TDA3301 B

consists of the following blocks:

Phase-locked reference oscillator;

Phase-locked 90 degree servo loop;

U and V axis decoders

ACC detector and identification detector; .

Identification circuits and PAL bistable; .

Color difference filters and matrixes with fast blanking

Circuits.

The major design considerations apart from optimum

performance were:

o A minimum number of factory adjustments,

o A minimum number of external components,

0 Compatibility with SECAM adapter TDA3030B,

0 Low dissipation,

0 Use of a standard 4.433618 Mhz crystal rather

than a 2.0 fc crystal with a divider.

The crystal VCO is of the phase shift variety in which the

frequency is controlled by varying the phase of the feedback.

A great deal of care was taken to ensure that the oscillator loop

gain and the crystal loading impedance were held constant in

order to ensure that the circuit functions well with low grade

crystal (crystals having high magnitude spurious responses

can cause bad phase jitter). lt is also necessary to ensure that

the gain at third harmonic is low enough to ensure absence of

oscillation at this frequency.

It can be seen that the

necessary 1 45°C phase shift is obtained by variable addition

ol two currents I1 and I2 which are then fed into the load

resistance of the crystal tuned circuit R1. Feedback is taken

from the crystal load capacitance which gives a voltage of VF

lagging the crystal current by 90°.

The RC network in the T1 collector causes I1 to lag the

collector current of T1 by 45°.

For SECAM operation, the currents I1 and I2 are added

together in a fixed ratio giving a frequency close to nominal.

When decoding PAL there are two departures from normal

chroma reference regeneration practice:

a) The loop is locked to the burst entering from the PAL

delay line matrix U channel and hence there is no

alternating component. A small improvement in signal

noise ratio is gained but more important is that the loop

filter is not compromised by the 7.8 kHz component

normally required at this point for PAL identification

b) The H/2 switching of the oscillator phase is carried out

before the phase detector. This implies any error signal

from the phase detector is a signal at 7.8 kHz and not dc.

A commutator at the phase detector output also driven

from the PAL bistable coverts this ac signal to a dc prior

to the loop filter. The purpose ot this is that constant

offsets in the phase detector are converted by the

commutator to a signal at 7.8 kHz which is integrated to

zero and does not give a phase error.

When used for decoding NTSC the bistable is inhibited, and

slightly less accurate phasing is achieved; however, as a hue

control is used on NTSC this cannot be considered to be a

serious disadvantage.

90° Reference Generation

To generate the U axis reference a variable all-pass network

is utilized in a servo loop. The output of the all-pass network

is compared with the oscillator output with a phase detector of

which the output is filtered and corrects the operating point of

the variable all»pass network .

As with the reference loop the oscillator signal is taken after

the H/2 phase switch and a commutator inserted before the

filter so that constant phase detector errors are cancelled.

For SECAM operation the loop filter is grounded causing

near zero phase shift so that the two synchronous detectors

work in phase and not in quadralure.

The use of a 4.4 MHz oscillator and a servo loop to generate

the required 90° reference signal allows the use of a standard,

high volume, low cost crystal and gives an extremely accurate

90° which may be easily switched to 0° for decoding AM

SECAM generated by the TDA3030B adapter.

ACC and Identification Detectors

During burst gate time the output components of the U and

also the V demodulators are steered into PNP emitters. One

collector current of each PNP pair is mirrored and balanced

against its twin giving push-pull current sources for driving the

ACC and the identification filter capacitors.

The identification detector is given an internal offset by

making the NPN current mirror emitter resistors unequal. The

resistors are offset by 5% such that the identification detector

pulls up on its filter capacitor with zero signal.

Identification

See Figure 11 for definitions.

Monochrome I1 > I2

PAL ldent. OK I1 < lg

PAL ldent_ X l1 > I2

NTSC I3 > I2

Only for correctly identified PAL signal is the capacitor

voltage held low since I2 is then greater than I1.

For monochrome and incorrectly identified PAL signals l1>l2

hence voltage VC rises with each burst gate pulse.

When V,ef1 is exceeded by 0.7 V Latch 1 is made to conduct

which increases the rate of voltage rise on C. Maximum

current is limited by R1.

When Vref2 is exceeded by 0.7 V then Latch 2 is made to

conduct until C is completely discharged and the current drops

to a value insufficient to hold on Latch 2.

As Latch 2 turns on Latch 1 must turn off.

Latch 2 turning on gives extra trigger pulse to bistable to

correct identification.

The inhibit line on Latch 2 restricts its conduction to alternate

lines as controlled by the bistable. This function allows the

SECAM switching line to inhibit the bistable operation by firing

Latch 2 in the correct phase for SECAM. For NTSC, Latch 2

is fired by a current injected on Pin 6.

lf the voltage on C is greater than 1.4 V, then the saturation

is held down. Only for SECAM/NTSC with Latch 2 on, or

correctly identified PAL, can the saturation control be

anywhere but minimum.

NTSC Switch

NTSC operation is selected when current (I3) is injected into

Pin 6. On the TDA33O1 B this current must be derived

externally by connecting Pin 6 to +12 V via a 27 k resistor (as

on TDA33OOB). For normal PAL operation Pin 40 should be

connected to +12 V and Pin 6 to the filter capacitor.

4 Color Difference Matrixing, Color Killing,

and Chroma Blanking

During picture time the two demodulators feed simple RC

filters with emitter follower outputs. Color killing and blanking

is performed by lifting these outputs to a voltage above the

maximum value that the color difference signal could supply.

The color difference matrixing is performed by two

differential amplifiers, each with one side split to give the

correct values of the -(B-Y) and -(Ft-Y) signals. These are

added to give the (G-Y) signal.

The three color difference signals are then taken to the

virtual grounds of the video output stages together with

luminance signal.

Sandcastle Selection

The TDA3301B may be used with a two level sandcastle

and a separate frame pulse to Pin 28, or with only a three level

(super) sandcastle. In the latter case, a resistor of 1.0 MQ is

necessary from + 12 V to Pin 28 and a 70 pF capacitor from

Pin 28 to ground.

Timing Counter for Sample Control

In order to control beam current sampling at the beginning

of each frame scan, two edge triggered flip-flops are used.

The output K ofthe first flip-flop A is used to clock the second

tlip-flop B. Clocking of A by the burst gate is inhibited by a count

of A.B.

The count sequence can only be initiated by the trailing

edge of the frame pulse. ln order to provide control signals for:

Luma/Chroma blanking

Beam current sampling

On-screen display blanking

Brilliance control

The appropriate flip-flop outputs ar matrixed with sandcastle

and frame signals by an emitter-follower matrix.

Video Output Sections

Each video output stage consists of a feedback amplifier in A further drive current is used to control the DC operating

which the input signal is a current drive to the virtual earth from point; this is derived from the sample and hold stage which

the luminance, color difference and on-screen display stages. samples the beam current after frame flyback.

TDA2541 IF AMPLIFIER WITH DEMODULATOR AND AFC

DESCRIPTION

The TDA2540 and 2541 are IF amplifier and A.M.

demodulator circuits for colour and black and white

television receivers using PNP or NPN tuners. They

are intended for reception of negative or positive

modulation CCIR standard.

They incorporate the following functions : .Gain controlled amplifier .Synchronous demodulator .White spot inverter .Video preamplifier with noise protection .Switchable AFC .AGC with noise gating .Tuner AGC output (NPN tuner for 2540)-(PNP

tuner for 2541) .VCR switch for video output inhibition (VCR

play back).

.SUPPLYVOLTAGE : 12V TYP

.SUPPLYCURRENT : 50mATYP

.I.F. INPUT VOLTAGE SENSITIVITY AT

F = 38.9MHz : 85mVRMS TYP

.VIDEO OUTPUT VOLTAGE (white at 10% of

top synchro) : 2.7VPP TYP

.I.F. VOLTAGE GAIN CONTROL RANGE :

64dB TYP .SIGNAL TO NOISE RATIO AT VI = 10mV :

58dB TYP

.A.F.C. OUTPUT VOLTAGE SWING FOR

Df = 100kHz : 10V TYP

BU208(A)

Silicon NPNnpn transistors,pnp transistors,transistors

Category: NPN Transistor, Transistor

MHz: <1 MHz

Amps: 5A

Volts: 1500V

HIGH VOLTAGE CAPABILITY

JEDEC TO-3 METAL CASE.

DESCRIPTION

The BU208A, BU508A and BU508AFI are

manufactured using Multiepitaxial Mesa

technology for cost-effective high performance

and use a Hollow Emitter structure to enhance

switching speeds.

APPLICATIONS:

* HORIZONTAL DEFLECTION FOR COLOUR TV With 110° or even 90° degree of deflection angle.

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

VCES Collector-Emit ter Voltage (VBE = 0) 1500 V

VCEO Collector-Emit ter Voltage (IB = 0) 700 V

VEBO Emitter-Base Voltage (IC = 0) 10 V

IC Collector Current 8 A

ICM Collector Peak Current (tp < 5 ms) 15 A

TO - 3 TO - 218 ISOWATT218

Ptot Total Dissipation at Tc = 25 oC 150 125 50 W

Tstg Storage Temperature -65 to 175 -65 to 150 -65 to 150 oC

Tj Max. Operating Junction Temperature 175 150 150 °C

No comments:

Post a Comment

The most important thing to remember about the Comment Rules is this:

The determination of whether any comment is in compliance is at the sole discretion of this blog’s owner.

Comments on this blog may be blocked or deleted at any time.

Fair people are getting fair reply. Spam and useless crap and filthy comments / scrapers / observations goes all directly to My Private HELL without even appearing in public !!!

The fact that a comment is permitted in no way constitutes an endorsement of any view expressed, fact alleged, or link provided in that comment by the administrator of this site.

This means that there may be a delay between the submission and the eventual appearance of your comment.

Requiring blog comments to obey well-defined rules does not infringe on the free speech of commenters.

Resisting the tide of post-modernity may be difficult, but I will attempt it anyway.

Your choice.........Live or DIE.

That indeed is where your liberty lies.

Note: Only a member of this blog may post a comment.