The SHARP 70GS-61S chassiS GA-10 t's based on the VCT38XX DIGIT3000 from ITT/MICRONAS technology which was allowing to develop a complete digital television with one chip solution toghether with a one chip for digital audio processing.THEREFORE THE SHARP CHASSIS GA-10 is the highest integrated DIGITAL CHASSIS FOR CRT TUBE TELEVISION APPLICATION.

It's entirely based around the ITT/MICRONAS DIGIT3000 technology for VIDEO and AUDIO digital processing.

........ And it's highly complex ............ and very critical..............

It's Divided by 2 layers of parts:

- Componenents side : All Power signal parts....

- Componenents side : All Power signal parts....and some ROM.......... Tuner...........SCART Socket.

- Solder side: All signal processing parts + solder part for power parts.

- Solder side: All signal processing parts + solder part for power parts.Other signal acquisition IF stages are based around PHILIPS semiconductors technology.

Some parts like audio amplifier and Frame output stages are based on THOMSON semiconductors.

The chassis has a very unusual circuits development particularly in the power stages like:

- POWER SUPPLY

- LINE DEFLECTION + E/W CORRECTION + EHT

- FRAME DEFLECTION OUTPUT.

Repairing these it's a NIGHTMARE !!!! From the complexity of the circuits to the design of the layouts of the PCB and the critical general composition sometimes it's very hard to repair, and even because they were failing often with various frequent defects mainly caused by dry joints causing further faults in geometrical sequence .

IT RUNS DISCRETELY WARM !!!!

SHARP 70GS-61S CHASSIS GA-10 (F7315BMN6) CIRCUITS DESCRIPTIONS:

SHARP 70GS-61S CHASSIS GA-10 [GA10] Switching power supply unit:

SHARP 70GS-61S CHASSIS GA-10 [GA10] Switching power supply unit: An inexpensive power supply unit which may be used for video display devices is provided. The unit saves power when supplying power to a light load, such as during remote control standby. Power for a controller which controls each part of a video display device is supplied from the switching power supply. Power consumption of the switching power supply is reduced by extending an OFF period setting for the switching power supply when operation of a display drive circuit is turned off.

The present invention relates to switching circuitry wherein a low-loss "drive" inductance is "charged" and "discharged" to provide the energy for turning a power switch on and off. The drive-inductance and a tapped-winding transformer co-act in a novel manner to provide a large "sweep-out" current that quickly turns off the power switch, the sweep-out time being extremely short.

FIELD OF THE INVENTION

The present invention relates to the field of power supply units generally, and more specifically to exemplary power supply units which are used for video display devices including television sets and display monitors for computers.

BACKGROUND OF THE INVENTION

Conventional power supply units for video display devices, for example television sets, use a single converter for supplying the power necessary for heavy loads such as during watching TV and for light loads when the TV is turned off or in the remote control standby state by employing a self-excited power supply (hereafter referred to as "switching power supply"). This system, however, causes great loss in the remote control standby state because the energy continuously regenerates in the switching element and transformer. (Refer to Japanese Laid-open Patent H4-172090.)

One alternative system is to employ two power supplies: a main power supply and a power supply for a control means such as a microcomputer (hereafter referred to generically as the microcomputer).

1. A switching power supply unit comprising:

ON period control means for controlling an ON period;

minimum OFF period setting means for setting a minimum time amount for an OFF period; and

OFF period control means for controlling the setting of the OFF period;

wherein said ON period control means controls output voltage of said

switching power supply unit by controlling said ON period while said OFF

period control means fixes the OFF period to the minimum time amount

for the OFF period; and

wherein said ON period control means controls output voltage of said

switching power supply unit by controlling said ON period while said OFF

period control means fixes the OFF period to the minimum time amount

for the OFF period; and said OFF period control means controls output voltage of said switching power supply unit by controlling the OFF period while said ON period control means fixes the ON period to a fixed minimum time amount of said ON period responsive to the output voltage of said switching power supply unit dropping.

2. A power supply unit according to claim 1, wherein said controller for the main converter comprises an OFF period setting circuit, wherein said OFF period setting circuit determines an OFF period based on a specified minimum OFF period and a period controlled by a feedback signal.

3. A power supply unit according to claim 1, including a transformer and wherein said controller for the main converter comprises: a capacitor

an ON period controller which discharges voltage charged in said capacitor and controls an ON period based on the terminal voltage of said capacitor and a control voltage in response to a feedback signal;

an OFF period controller which charges said capacitor and controls the OFF period based on the terminal voltage of said capacitor and the control voltage in response to a feedback signal; and

a transformer reset detector which suppresses the turning on of a switching device during resonance of said transformer.

4. A power supply unit according to claim 1, wherein said controller for the main converter comprises: a capacitor;

means for setting a specified voltage; and

an OFF period controller which increases charge voltage of said capacitor to said specified voltage at a first rate of charge and then further increases voltage at a rate of charge less than the first rate of charge, to a voltage above said specified voltage to a control voltage, the control voltage being based on a feedback signal.

5. A power supply unit according to claim 1, wherein said controller for the main converter comprises an OFF period controller, the OFF period controller comprising: means for setting a specified voltage and

means for charging voltage of a capacitor to said specified voltage at substantially high speed,

wherein said means for charging voltage is used for determining a minimum OFF period.

6. A power supply unit according to claim 1 wherein the power supply unit is a power supply unit for a video display device, the power supply unit comprising: an output voltage terminal for outputting multiple levels of voltage;

a first output voltage terminal for outputting voltage applied to a display drive circuit of the video display device using a switching means; and

a second output voltage terminal for outputting voltage applied to a controller which controls on and off of said switching means;

whereby an OFF period setting of the power supply unit is extended when said switching means is turned off.

7. A power supply unit according to claim 1 wherein the power supply unit is a power supply unit for a video display device, the power supply unit comprising: a first switching power supply for supplying power supply voltage to a display drive circuit of the video display device and a second switching power supply for supplying power supply voltage to a signal processor and a range of controllers; whereby an OFF period setting of said second switching power supply is extended when said first switching power supply is turned off by a switching means.

8. A switching power supply unit comprising: i) a first switching power supply unit;

ii) a second switching power supply unit for supplying power for less load than said first switching power supply unit supplies, said second switching power supply unit comprising:

a) means for switching on or off power for said first switching power supply unit;

b) ON period control means for controlling ON period;

c) minimum OFF period setting means for setting a minimum time amount of an OFF period;

d) OFF period control means for controlling the setting of the OFF period;

wherein said ON period control means controls output voltage of said switching power supply unit by controlling the ON period when said ON period control means fixes the OFF period to said minimum time amount of said OFF period while said second switching power supply unit switches on power for said first switching power supply unit; and

said OFF period control means controls output voltage of said second switching power supply unit by controlling the OFF period when said ON period control means fixes the ON period to a fixed minimum ON period while said second switching power supply unit switches off power for said first switching power supply unit.

9. A power supply unit according to claim 8, wherein the power supply unit is a power supply unit for a video display device, and the first load is a display drive circuit of the video display device.

1. Switching circuitry comprising:

a control switch;

a drive circuit comprising a charge circuit and a discharge circuit;

a drive inductor;

a drive transformer;

said drive transformer having a charge primary winding, a discharge primary winding, and a secondary winding;

said charge circuit comprising said secondary winding and a series circuit of said drive inductor, said control switch, and said charge primary winding;

whereby when said control switch assumes its ON state, a charge current in said charge circuit charges said drive inductor, and produces an enabling signal in said secondary winding;

a power switch adapted to permit the flow of an electric current therethrough;

means for applying said enabling signal to s

aid power switch, for

causing said power switch to quickly and positively assume its ON state

and for permitting the flow of a load current;

aid power switch, for

causing said power switch to quickly and positively assume its ON state

and for permitting the flow of a load current; said discharge circuit comprising said secondary winding and a series circuit of said drive inductor and said discharge primary winding;

whereby, when said control switch assumes its OFF state, the energy of said charged drive inductor directly produces a discharge current, and said discharge current in said discharge circuit produces a disabling signal in said secondary winding;

means for applying said disabling signal to said power switch for causing said power switch to quickly and positively assume its OFF state, and for terminating the flow of the load current.

2. The invention of claim 1, wherein said control switch and said power switch are transistors.

3. The invention of claim 1, wherein said discharge circuit further comprises blocking diode means for blocking said charge current from flowing in said discharge circuit.

4. The invention of claim 1, including a second drive circuit; means for causing said power switch to function as a control switch for said second drive circuit,

whereby said drive circuits are cascaded.

5. The invention of claim 1, including a plurality of control switches, a corresponding plurality of drive circuits associated with respective ones of said control switches, and a corresponding plurality of power switches associated with respective ones of said drive circuits; means for causing said control-circuit means to conductivate said individual control switches of said plurality of control switches in a sequential timed manner;

whereby said individual drive circuits and said individual power switches are energized in a corresponding sequential timed manner.

6. Switching circuitry comprising: a control transistor;

control-

circuit means for controlling the ON/OFF state of said control transistor;

circuit means for controlling the ON/OFF state of said control transistor; a drive circuit comprising a charge circuit and a discharge circuit;

a drive inductor;

a drive transformer;

said drive transformer having a charge primary winding, a discharge primary winding, and a secondary winding;

said charge circuit comprising said secondary winding, blocking diode means for blocking said charge current from flowing in said discharge circuit and a series circuit of said drive inductor, said control switch, and said charge primary winding;

whereby, when said control transistor assumes its ON state, a charge current in said charge circuit charges said drive inductor, and produces an enabling signal in said secondary winding;

a power transistor adapted for the flow of an electric current therethrough;

means for applying said enabling signal to said power transistor, for causing said power transistor to quickly and positively assume its ON state;

said discharge circuit comprising said said secondary winding and a series circuit of said drive inductor and said discharge primary winding;

whereby, when said control transistor assumes its OFF state, the energy of said charged drive inductor directly produces a discharge current, and said discharge current in said discharge circuit produces an opposite-polarity disabling signal in said secondary winding;

said disabling signal being a short-interval, high-magnitude, sweep-out current;

means for applying said disabling signal to said power transistor for causing said power transistor to quickly and positively assume its OFF state.

7. The invention of claim 6, including means for controlling the timing of said control circuit means.

In the field of electronics, it is frequently necessary to "transform" one form of electricity to another form, such transformations taking place in circuits known as power sources, converters, inverters, rectifiers, etc. Some of these circuits function, for example, to transform AC to DC, DC to AC, DC of one voltage to DC of another voltage, etc. Such circuits often use switches of one type or another; but, unfortunately, switches tend to raise severe problems -- such as power loss, low efficiency, undesirable heating, transients, impaired lifetimes, and the like.

OBJECTIVES AND DRAWINGS

It is, therefore, the principal objective of the present invention to provide improved switching circuitry.

It is another objective of the present invention to provide improved switching circuitry that provides extremely fast turn-off.

It is still another objective of the present invention to provide improved switching circuitry wherein a low-power system controls a high-power system.

It is a further objective of the present invention to provide improved switching circuitry adapted to be used in a cascaded manner, in order to control the switching of even higher power systems.

It is a further objective of the present invention to provide improved switching circuitry adapted to be used in a timed manner, in order to provide higher-power and smoother-power systems.

VCT 3831A/B Video/Controller/Teletext IC Family:

Introduction

The VCT 38xxA/B is an IC family of high-quality singlechip

TV processors. Modular design and a submicron

technology allow the economic integration of features

in all classes of TV sets. The VCT 38xxA/B family is

based on functional blocks contained and approved in

existing products like VDP 3120B, TPU 3050S, and

CCZ 3005K.

Each member of the family contains the entire video,

display, and deflection processing for 4:3 and 16:9 50/

60-Hz TV sets. The integrated microcontroller is supported

by a powerful OSD generator with integrated

teletext acquisition which can be upgraded with onchip

page memory. With volume control and audio

input select the basic audio features for mono TV sets

are integrated. An overview of the VCT 38xxA/B single-

chip TV processor family is given in Fig. 1–1 on

page 7.

The VCT 38xxA/B family offers a rich feature set, covering

the whole range of state-of-the-art 50/60-Hz TV

applications.

In comparison to the VCT 38xxA the VCT 38xxB offers

the following features:

– one additional composite video input

– analog luma/chroma adder for video output

– closed caption module

– additional 12k character ROM.

1.1. Features

1.1.1. Video Features

– four composite video inputs (VCT 38xxA)

– five composite video inputs (VCT 38xxB)

– analog YCrCb input, two S-VHS inputs

– Y/C adder for video output (VCT 38xxB only!)

– composite video monitor

– multistandard color decoder (1 crystal)

– multistandard sync decoder

– black-line detector

– adaptive 2H comb filter Y/C separator

– horizontal scaling (0.25 to 4)

– Panorama

vision

vision– black-level expander

– dynamic peaking

– soft limiter (gamma correction)

– color transient improvement

– programmable RGB matrix

– analog RGB/Fastblank input

– half-contrast switch

– picture frame generator

– scan velocity modulation output

– high-performance H/V deflection

– angle and bow correction

– separate ADC for tube measurements

– EHT compensation

1.1.2. Microcontroller Features

– 8-bit, 10-MHz CPU (65C02)

– 96 kB program ROM on chip

– 1 kB program RAM on chip

– memory banking

– 16-input, 16-level interrupt controller

– patch module for 10 ROM locations

– two 16-bit reloadable timers

– capture compare module

– watchdog timer

– 14-bit PWM for voltage synthesis

– four 8-bit PWMs

– 10-bit ADC with 15:1 input MUX

– I2C bus master interface

– 24 programmable I/O ports

– closed caption module (VCT 38xxB only!)

1.1.3. OSD Features

– 3 kB OSD RAM on chip

– WST level 1.5 compliant

– WST level 2 parallel attributes

– 32 foreground/background colors

– programmable color look-up table

– 1024 mask programmable characters (VCT 38xxA)

– 2000 mask programmable characters (VCT 38xxB)

– 24 national languages

(Latin, Cyrillic, Greek, Arabic, Farsi, Hebrew)

– character matrix 8x8, 8x10, 8x13, 10x8, 10x10, 10x13

– vertical soft scroll

– 4-color mode for user font

1.1.4. Teletext Features

– four programmable video inputs (VCT 38xxA)

– five programmable video inputs (VCT 38xxB)

– acquisition is independent from display part

– adaptive data slicer

– signal quality detection

– WST, PDC, VPS, and WSS acquisition

– high-level command language

– EPG, FLOF, and TOP support

– 10 pages memory on chip

– up to 500 pages with external SRAM

1.1.5. Audio Features

– three mono inputs

– two mono outputs

– programmable channel select

– volume control for one mono channel

1.1.6. General Features

– submicron CMOS technology

– low-power standby mode

– single 20.25-MHz crystal

– 64-pin PSDIP package

– 128-pin PMQFP package

Video Processing

2.1. Introduction

The VCT 38xxA/B includes complete video, display,

and deflection processing. In the following sections the

video processing part of the VCT 38xxA/B will be

named VDP for short.

All processing is done digitally, the video front-end and

video back-end are interfacing to the analog world.

Most functions of the VDP can be controlled by software

via I2C bus slave interface (see Section 2.14. on

page 31).

2.2. Video Front-end

This block provides the analog interfaces to all video

inputs and mainly carries out analog-to-digital conversion

for the following digital video processing. A block

diagram is given in Fig. 2–1.

Most of the functional blocks in the front-end are digitally

controlled (clamping, AGC, and clock-DCO). The

control loops are closed by the Fast Processor (‘FP’)

embedded in the video decoder.

2.2.1. Input Selector

Up to eight analog inputs can be connected. Four

inputs (five in case of VCT 38xxB) are for input of composite

video or S-VHS luma signal. These inputs are

clamped to the sync back porc

h and are amplified by a

h and are amplified by avariable gain amplifier. Two chroma inputs can be

used for connection of S-VHS carrier-chrominance signal.

These inputs are internally biased and have a

fixed gain amplifier. For analog YCrCb signals (e.g.

from DVD players) one of the selected luminance

inputs is used together with CBIN and CRIN inputs.

2.2.2. Clamping

The composite video input signals are AC-coupled to

the IC. The clamping voltage is stored on the coupling

capacitors and is generated by digitally controlled current

sources. The clamping level is the back porch of

the video signal. S-VHS chrominance is also AC-coupled.

The input pin is internally biased to the center of

the ADC input range. The chrominance inputs for

YCrCb need to be AC-coupled by 220 nF clamping

capacitors. It is strongly recommended to use 5-MHz

anti-alias low-pass filters on each input. Each channel

is sampled at 10.125 MHz with a resolution of 8 bit and

a clamping level of 128.

2.2.3. Automatic Gain Control

A digitally working automatic gain control adjusts the

magnitude of the selected baseband by +6/–4.5 dB in

64 logarithmic steps to the optimal range of the ADC.

The gain of the video input stage including the ADC is

213 steps/V with the AGC set to 0 dB. The gain of the

chrominance path in the YCrCb mode is fix and

adapted to a nominal amplitude of 0.7 Vpp. However, if

an overflow of the ADC occurs an extended signal

range from 1 Vpp can be selected.

2.2.4. Analog-to-Digital Converters

Two ADCs are provided to digitize the input signals.

Each converter runs with 20.25 MHz and has 8 bit resolution.

An integrated bandgap circuit generates the

required reference voltages for the converters.

2.2.5. Digitally Controlled Clock Oscillator

The clock generation is also a part of the analog frontend.

The crystal oscillator is controlled digitally by the

control processor. The clock frequency can be

adjusted within ±150 ppm.

2.2.6. Analog Video Output

The input signal of the Luma ADC is available at the

analog video output pin. The signal at this pin must be

buffered by a source follower. The output voltage is

2 V, thus the signal can be used to drive a 75-Ω line.

The magnitude is adjusted with an AGC in 8 steps

together with the main AGC.

In case of VCT 38xxB it is possible to enable a Y/Cadder.

The analog sum of the selected luma and

chroma input signals is available at the video output

pin. This allows recording of S-VHS input signals via

video output.

2.3. Adaptive Comb Filter

The adaptive comb filter is used for high-quality luminance/

chrominance separation for PAL or NTSC signals.

The comb filter improves the luminance resolution

(bandwidth) and reduces interferences like

cross-luminance and cross-color artifacts. The adaptive

algorithm can eliminate most of the mentioned

errors without introducing new artifacts or noise.

A block diagram of the comb filter is shown in Fig. 2–2.

The filter uses two li

ne delays to process the information

ne delays to process the informationof three adjacent video lines. To have a fixed

phase relationship of the color subcarrier in the three

channels, the system clock (20.25 MHz) is locked to

the color subcarrier. This allows the processing of all

color standards and substandards using a single crystal

frequency.

The CVBS signal in the three channels is filtered at the

subcarrier frequency by a set of bandpass/notch filters.

The output of the three channels is used by the

adaption logic to select the weighting that is used to

reconstruct the luminance/chrominance signal from

the 4 bandpass/notch filter signals.The comb filter

uses the middle line as reference, therefore, the comb

filter delay is one line. If the comb filter is switched off,

the delay lines are used to pass the luma/ chroma signals

from the A/D converters to the luma/ chroma outputs.

Thus, the comb filter delay is always one line.

Various parameters of the comb filter are adjustable,

hence giving to the user the ability to adjust his own

desired picture quality.

Two parameters (K

Y, KC) set the global gain of luma

Y, KC) set the global gain of lumaand chroma comb separately; these values directly

weigh the adaption algorithm output. In this way, it is

possible to obtain a luma/chroma separation ranging

from standard notch/bandpass to full comb decoding.

The parameter KB allows to choose between the two

proposed comb booster modes. This so-called feature

widely improves vertical high-to-low frequency transitions

areas, the typical example being a multiburst to

DC change. For KB=0, this improvement is kept moderate,

whereas, in case of KB=1, it is maximum, but

the risk to increase the “hanging dots” amount for

some given color transitions is higher.

Using the default setting, the comb filter has separate

luma and chroma decision algorithms; however, it is

possible to switch the chroma comb factor to the current

luma adaption output by setting CC to 1.

Fig. 2–2: Block diagram of the adaptive comb filter (PAL mode)

1H Delay Line

1H Delay Line

CVBS Input

Chroma Input

Bandpass

Filter

Bandpass

Filter

Bandpass/

Notch

Filter

Luma / Chroma Mixers

Adaption Logic

Luma Output

Chroma Output

Another interesting feature is the programmable limitation

of the luma comb amount; proper limitation, associated

to adequate luma peaking, gives rise to an

enhanced 2-D resolution homogeneity. This limitation

is set by the parameter CLIM, ranging from 0 (no limitation)

to 31 (max. limitation).

The DAA parameter (1:off, 0:on) is used to disable/

enable a very efficient built-in “rain effect” suppressor;

many comb filters show this side effect which gives

some vertical correlation to a 2-D uniform random

area, due to the vertical filtering. This unnatural-looking

phenomenon is mostly visible on tuner images,

since they are always corrupted by some noise; and

this looks like rain.

2.4. Color Decoder

A block diagram of the color decoder is shown in Fig.

2–4. The luma as well as the chroma processing, is

shown here. The color decoder provides also some

special modes, e.g. wide band chroma format which is

intended for S-VHS wide bandwidth chroma.

If the adaptive comb filter is used for luma chroma separation,

the color decoder uses the S-VHS mode processing.

The output of the color decoder is YCrCb in a

4:2:2 format.

2.4.1. IF-Compensation

With off-air or mistuned reception, any attenuation at

higher frequencies or asymmetry around the color subcarrier

is compensated. Four different settings of the

IF-compensation are possible:

– flat (no compensation)

– 6 dB/octave

– 12 dB/octave

– 10 dB/MHz

The last setting gives a very large boost to high frequencies.

It is provided for SECAM signals that are

decoded using a SAW filter specified originally for the

PAL standard.

Fig. 2–3: Frequency response of chroma

IF-compensation

Fig. 2–4: Color decoder

ColorPLL/ColorACC

1 H Delay

MUX MUX

CrossSwitch

Notch

Filter

Luma / CVBS Luma

Chroma

Mixer

Low-pass Filter

Phase/Freq

Demodulator

ACC

Chroma

IF Compensation

DC-Reject

2.4.2. Demodulator

The subcarrier frequency in the demodulator is generated

by direct digital synthesis; therefore, substandards

such as PAL 3.58 or NTSC 4.43 can also be

demodulated.

2.4.3. Chrominance Filter

The demodulation is followed by a low-pass filter for

the color difference signals for PAL/NTSC. SECAM

requires a modified low-pass function with bell-filter

characteristic. At the output of the low-pass filter, all

luma information is eliminated.

The low-pass filters are calculated in time multiplex for

the two color signals. Three bandwidth settings (narrow,

normal, broad) are available for each standard.

For PAL/NTSC, a wide band chroma filter can be

selected. This filter is intended for high bandwidth

chroma signals, e.g. a non-standard wide bandwidth

S-VHS signal.

2.4.4. Burst Detection / Saturation Control

In the PAL/NTSC-system the burst is the reference for

the color signal. The phase and magnitude outputs of

the color demodulator are gated with the color key and

used for controlling the phase-locked-loop (APC) of the

demodulator and the automatic color control (ACC) in

PAL/NTSC.

The ACC has a control range of +30...−6 dB.

Color saturation can be selected once for all color

standards. In PAL/NTSC it is used as reference for the

ACC. In SECAM the necessary gains are calculated

automatically.

For SECAM decoding, the frequency of the burst is

measured. Thus, the current chroma carrier frequency

can be identified and is used to control the SECAM

processing. The burst measurements also control the

color killer operation; they are used for automatic standard

detection as well.

2.4.5. Color Killer Operation

The color killer uses the burst-phase/burst-frequency

measurement to identify a PAL/NTSC or SECAM color

signal. For PAL/NTSC, the color is switched off (killed)

as long as the color subcarrier PLL is not locked. For

SECAM, the killer is controlled by the toggle of the

burst frequency. The burst amplitude measurement is

used to switch-off the color if the burst amplitude is

below a programmable threshold. Thus, color will be

killed for very noisy signals. The color amplitude killer

has a programmable hysteresis.

2.4.6. Automatic Standard Recognition

The burst-frequency measurement is also used for

automatic standard recognition (together with the status

of horizontal and vertical locking) thus allowing a

completely independent search of the line and color

standard of the input signal. The following standards

can be distinguished:

– PAL B,G,H,I

– PAL M

– PAL N

– PAL 60

– NTSC M

– NTSC 44

– SECAM

For a preselection of allowed standards, the recognition

can be enabled/disabled via I2C bus for each standard

separately.

If at least one standard is enabled, the VCT 38xxA/B

regularly checks the horizontal and vertical locking of

the input signal and the state of the color killer. If an

error exists for several adjacent fields a new standard

search is started. Depending on the measured line

number and burst frequency, the current standard is

selected.

For error handling the recognition algorithm delivers

the following status information:

– search active (busy)

– search terminated, but failed

– found standard is disabled

– vertical standard invalid

– no color

found

found2.4.7. PAL Compensation/1-H Comb Filter

The color decoder uses one fully integrated delay line.

Only active video is stored.

The delay line application depends on the color standard:

– NTSC: 1-H comb filter or color compensation

– PAL: color compensation

– SECAM: crossover switch

In the NTSC compensated mode, (Fig. 2–6c), the color

signal is averaged for two adjacent lines. Thus,

cross-color distortion and chroma noise is reduced. In the NTSC comb filter mode, the delay line

is in the composite signal path, thus allowing reduction

of cross-color components, as well as cross-luminance.

The loss of vertical resolution in the luminance

channel is compensated by adding the vertical detail

signal with removed color information.

2.6. Black-line Detector

This function is available for versions with panorama

scaler only!

In case of a letterbox format input video, e.g. Cinemascope,

PAL+ etc., black areas at the upper and lower

part of the picture are visible. It is suitable to remove or

reduce these areas by a vertical zoom and/or shift

operation.

The VCT 38xxA/B supports this feature by a letterbox

detector. For every field the number of black lines at

the upper and lower part of the picture are measured

and stored in the I2C-register BLKLIN. To adjust the

picture amplitude, the CPU reads this register, calculates

the vertical scaling coefficient and transfers the

new settings, e.g. vertical sawtooth parameters, horizontal

scaling coefficient etc., to the scaler and the

deflection circuits.

Letterbox signals containing logos on the left or right

side of the black areas are processed as black lines,

while subtitles, inserted in the black areas, are processed

as non-black lines. Therefore, the subtitles are

visible on the screen. To suppress the subtitles, the

vertical zoom coefficient is calculated by selecting the

larger number of black lines only. Dark video scenes

with a low contrast level compared to the letterbox

area are indicated by the BLKPIC bit.

2.7. Test Pattern Generator

The YCrCb outputs can be switched to a test mode

where YCrCb data are generated digitally in the

VCT 38xxA/B. Test patterns include luma/chroma

ramps and flat fields.

2.8. Video Sync Processing

Fig. 2–10 shows a block diagram of the front-end sync

processing. To extract the sync information from the

video signal, a linear phase low-pass filter eliminates

all noise and video contents above 1 MHz. The sync is

separated by a slicer; the sync phase is measured. A

variable window can be selected to improve the noise

immunity of the slicer. The phase comparator measures

the falling edge of sync, as well as the integrated

sync pulse.

The sync phase error is filtered by a phase-locked loop

that is computed by the FP. All timing in the front-end

is derived from a counter that is part of this PLL, and it

thus counts synchronously to the video signal.

A separate hardware block measures the signal back

porch and also allows gathering the maximum/minimum

of the video signal. This information is processed

by the FP and used for gain control and clamping.

For vertical sync separation, the sliced video signal is

integrated. The FP uses the integrator value to derive

vertical sync and field information.

The information extracted by the video sync processing

is multiplexed onto the hardware front sync signal

(FSY) and is distributed to the rest of the video processing

system.

The data for the vertical deflection, the sawtooth, and

the East-West correction signal is calculated by the

VCT 38xxA/B. The data is buffered in a FIFO and

transferred to the back-end by a single wire interface.

Frequency and phase characteristics of the analog

video signal are derived from PLL1. The results are fed

to the scaler unit for data interpolation and orthogonalization

and to the clock synthesizer for line-locked

clock generation. Horizontal and vertical syncs are

latched with the line-locked clock.

2.9. Display Processing

In the display processing the conversion from digital

YCrCb to analog RGB is carried out. A block diagram

is shown in Fig. 2–18 on page 23. In the luminance

processing path, contrast and brightness adjustments

and a variety of features, such as black-level expansion,

dynamic peaking and soft limiting, are provided.

In the chrominance path, the CrCb signals are converted

to 4:4:4 format and filtered by a color transient

improvement circuit. The YCrCb signals are converted

by a programmable matrix to RGB color space.

The display processor provides separate control settings

for two pictures, i.e. different coefficients for a

‘main’ and a ‘side’ picture.

The digital OSD insertion circuit allows the insertion of

a 5-bit OSD signal. The color space for this signal is

controlled by a partially programmable color look-up

table (CLUT) and contrast adjustment.

The OSD signals and the display clock are synchronized

to the horizontal flyback. For the display clock, a

gate delay phase shifter is used. In the analog backend,

three 10-bit digital-to-analog converters provide

the analog output signals.

2.9.1. Luma Contrast Adjustment

The contrast of the luminance signal can be adjusted

by multiplication with a 6-bit contrast value. The contrast

value corresponds to a gain factor from 0 to 2,

where the value 32 is equivalent to a gain of 1. The

contrast can be adjusted separately for main picture

and side picture.

2.9.2. Black-Level Expander

The black-level expander enhances the contrast of the

picture. Therefore the luminance signal is modified

with an adjustable, non-linear function. Dark areas of

the picture are changed to black, while bright areas

remain unchanged. The advantage of this black-level

expander is that the black expansion is performed only

if it will be most noticeable to the viewer.

The black-level expander works adaptively. Depending

on the measured amplitudes ‘Lmin’ and ‘Lmax’ of the

low-pass-filtered luminance and an adjustable coefficient

BTLT, a tilt point ‘Lt’ is established by

Lt = Lmin + BTLT (Lmax - Lmin).

Above this value there is no expansion, while all luminance

values below this point are expanded according

to:

Lout = Lin + BAM (Lin - Lt)

A second threshold, Ltr, can be programmed, above

which there is no expansion.

2.9.3. Dynamic Peaking

Especially with decoded composite signals and notch

filter luminance separation, as input signals, it is necessary

to improve the luminance frequency characteristics.

With transparent, high-bandwidth signals, it is

sometimes desirable to soften the image.

In the VCT 38xxA/B, the luma response is improved by

‘dynamic’ peaking. The algorithm has been optimized

regarding step and frequency response. It adapts to

the amplitude of the high-frequency part. Small AC

amplitudes are processed, while large AC amplitudes

stay nearly unmodified.

The dynamic range can be adjusted from −14 to

+14 dB for small high-frequency signals. There is separate

adjustment for signal overshoot and for signal

undershoot. For large signals, the dynamic range is

limited by a non-linear function that does not create

any visible alias components. The peaking can be

switched over to “softening” by inverting the peaking

term by software.

The center frequency of the peaking filter is switchable

from 2.5 MHz to 3.2 MHz. For S-VHS and for notch filter

color decoding, the total system frequency responses

for both PAL and NTSC are shown in Fig. 2–14.

Transients, produced by the dynamic peaking when

switching video source signals, can be suppressed via

the priority bus.

2.9.4. Digital Brightness Adjustment

The DC-level of the luminance signal can be adjusted

by adding an 8-bit number in the luminance signal path

in front of the softlimiter.

With a contrast adjustment of 32 (gain+1) the signal

can be shifted by 100%. After the brightness addition,

the negative going signals are limited to zero. It is

desirable to keep a small positive offset with the signal

to prevent undershoots produced by the peaking from

being cut. The digital brightness adjustment works

separately for main and side picture.

2.9.5. Soft Limiter

The dynamic range of the processed luma signal must

be limited to prevent the CRT from overload. An appropriate

headroom for contrast, peaking and brightness

can be adjusted by the TV manufacturer according to

the CRT characteristics. All signals above this limit will

be ‘soft’-clipped. A characteristic diagram of the soft

limiter is shown in Fig. 2–15. The total limiter consists

of three parts:

Part 1 includes adjustable tilt point and gain. The gain

before the tilt value is 1. Above the tilt value, a part

(0...15/16) of the input signal is subtracted from the

input signal itself. Therefore, the gain is adjustable

from 16/16 to 1/16, when the slope value varies from

0 to 15. The tilt value can be adjusted from 0 to 511.

Part 2 has the same characteristics as part 1. The subtracting

part is also relative to the input signal, so the

total differential gain will become negative if the sum of

slope 1 and slope 2 is greater than 16 and the input

signal is above the both tilt values (see characteristics).

Finally, the output signal of the soft limiter will be

clipped by a hard limiter adjustable from 256 to 511.

2.9.6. Chroma Interpolation

A linear phase interpolator is used to convert the

chroma sampling rate from 10.125 MHz (4:2:2) to

20.25 MHz (4:4:4). All further processing is carried out

at the full sampling rate.

2.9.7. Chroma Transient Improvement

The intention of this block is to enhance the chroma

resolution. A correction signal is calculated by differentiation

of the color difference signals. The differentiation

can be selected according to the signal bandwidth,

e.g. for PAL/NTSC/SECAM or digital component signals,

respectively. The amplitude of the correction signal

is adjustable.

Small noise amplitudes in the correction signal are

suppressed by an adjustable coring circuit. To eliminate

‘wrong colors’, which are caused by over and

undershoots at the chroma transition, the sharpened

chroma signals are limited to a proper value automatically.

2.9.8. Inverse Matrix

A 6-multiplier matrix transcodes the Cr and Cb signals

to R-Y, B-Y, and G-Y. The multipliers are also used to

adjust color saturation in the range of 0 to 2. The coefficients

are signed and have a resolution of 9 bits.

There are separate matrix coefficients for main and

side pictures. The matrix computes:

R−Y= MR1*Cb+MR2*Cr

G−Y= MG1*Cb+MR2*Cr

B−Y= MB1*Cb+MR2*Cr

The initialization values for the matrix are computed

from the standard ITUR (CCIR) matrix:

For a contrast setting of CTM+32, the matrix values

are scaled by a factor of 64 (see Table 2–4 on

page 32).

2.9.9. RGB Processing

After adding th

e post-processed luma, the digital RGB

e post-processed luma, the digital RGBsignals are limited to 10 bits. Three multipliers are

used to digitally adjust the white drive. Using the same

multipliers an average beam current limiter is implemented

(see Section 2.10.1. on page 24).

2.9.10. OSD Color Look-up Table

The VCT 38xxA/B has five input lines for an OSD signal.

This signal forms a 5-bit address for a color

look-up table (CLUT). The CLUT is a memory with 32

words where each word holds a RGB value.

Bits 0 to 3 (bit 4=0) form the addresses for the ROM

part of the OSD, which generates full RGB signals (bit

0 to 2) and half-contrast RGB signals (bit 3).

Bit 4 addresses the RAM part of the OSD with 16

freely programmable colors, addressable with bit 0 to

3. The programming is done via the I2C bus.

The amplitude of the CLUT output signals can be

adjusted separately for R, G, and B via the I2C bus.

The switchover between video RGB and OSD RGB is

done via the priority decoder.

2.9.11. Picture Frame Generator

When the picture does not fill the total screen (height

or width too small) it is surrounded with black areas.

These areas (and more) can be colored with the picture

frame g

enerator. This is done by switching over

enerator. This is done by switching overthe RGB signal from the matrix to the signal from the

OSD color look-up table.

The width of each area (left, right, upper, lower) can be

adjusted separately. The generator starts on the right,

respectively lower side of the screen and stops on the

left, respectively upper side of the screen. This means,

it runs during horizontal, respectively vertical flyback.

The color of the complete border can be stored in the

programmable OSD color look-up table in a separate

address. The format is 3 x 4-bit RGB. The contrast can

be adjusted separately.

The picture frame generator includes a priority master

circuit. Its priority is programmable and the border is

generated only if the priority is higher than the priority

of the other sources (video/OSD). Therefore, the border

can be underlay or overlay depending on the picture

source.

CRT Measurement and Control

The display processor is equipped with an 8-bit

PDM-ADC for all measuring purposes. The ADC is

connected to the SENSE input pin, the input range is 0

to 1.5 V. The bandwidth of the PDM filter can be

selected; it is 40/80 kHz for small/large bandwidth setting.

The input impedance is more than 1 MΩ.

Cutoff and white-drive current measurement are carried

out during the vertical blanking interval. They

always use the small bandwidth setting. The current

range for the cutoff measurement is set by connecting

a sense resistor to the MADC input. For the white-drive

measurement, the range is set by using another sense

resistor and the range select switch 2 output pin

(RSW2). During the active picture, the minimum and

maximum beam current is measured. The measurement

range can be set by using the range select

switch 1 pin (RSW1) as shown in Fig. 2–19 and Fig. 2–

20. The timing window of this measurement is programmable.

The intention is, to automatically detect

letterbox transmission or to measure the actual beam

current. All control loops are closed via the external

control microprocessor.

In each field two sets of measurements can be taken:

a) The picture tube measurement returns results for

– cutoff R

– cutoff G

– cutoff B

– white-drive R or G or B (sequentially)

b) The picture measurement returns data on

– active picture maximum current

– active picture minimum current

The tube measurement is automatically started when

the cutoff blue result register is read. Cutoff control for

RGB requires one field only, whereas a complete

white-drive control requires three fields. If the measurement

mode is set to ‘offset check’, a measurement

cycle is run with the cutoff/white-drive signals set to

zero. This allows to compensate the MADC offset as

well as input the leakage currents. During cutoff and

white-drive measurements, the average beam current

limiter function (see Section 2.10.3. on page 26) is

switched off and a programmable value is used for the

brightness setting. The start line of the tube measurement

can be programmed via I2C bus, the first line

used for the measurement, i.e. measurement of cutoff

red, is 2 lines after the programmed start line.

The picture measurement must be enabled by the control

microprocessor after reading the min./max. result

registers. If a ‘1’ is written into bit 2 in subaddress 25,

the measurement runs for one field. For the next measurement

a ‘1’ has to be written again. The measurement

is always started at the beginning of active video.

The vertical timing for the picture measurement is programmable,

and may even be a single line. Also the

signal bandwidth is switchable for the picture measurement.

Two horizontal windows are available for the picture

measurement. The large window is active for the entire

active line. Tube measurement is always carried out

with the small window.

2.10.3. Average Beam Current Limiter

The average beam current limiter (BCL) uses the

SENSE input for the beam current measurement. The

BCL uses a different filter to average the beam current

during the active picture. The filter bandwidth is

approx. 2 kHz. The beam current limiter has an automatic

offset adjustment that is active two lines before

the first cutoff measurement line.

The beam current limiter function is located in the

front-end. The data exchange between the front-end

and the back-end is done via a single-wire serial interface.

The beam current limiter allows the setting of a threshold

current. If the beam current is above the threshold,

the excess current is low-pass filtered and used to

attenuate the RGB outputs by adjusting the white-drive

multipliers for the internal (digital) RGB signals, and

the analog contrast multipliers for the analog RGB

inputs, respectively. The lower limit of the attenuator is

programmable, thus a minimum contrast can always

be set. During the tube measurement, the ABL attenuation

is switched off. After the white-drive measurement

line it takes 3 lines to switch back to BCL limited

drives and brightness.

Typical characteristics of the ABL for different loop

gains are shown in Fig. 2–22; for this example the tube

has been assumed to have square law characteristics.

Fig. 2–22: Beam current limiter characteristics: beam

current output vs. drive BCL threshold: 1

2.10.4. Analog RGB Insertion

The VCT 38xxA/B allows insertion of external analog

RGB signals. The RGB signal is key-clamped and

inserted into the main RGB by the Fast-Blank switch.

The external RGB input can be overlaid or underlaid to

the digital picture. The external RGB signals can be

adjusted independently as regards DC level (brightness)

and magnitude (contrast).

All signals for analog RGB insertion (RIN, GIN, BIN,

FBLIN) must be synchronized to the horizontal flyback,

otherwise a horizontal jitter will be visible. The

VCT 38xxA/B has no means for timing correction of

the analog RGB input signals.

2.10.5. Fast-Blank Monitor

The presence of external analog RGB sources can be

detected by means of a Fast-Blank monitor. The status

of the Fast-Blank input can be monitored via an I2C

bus register. There is a 2 bit information, giving static

and dynamic indication of a Fast-Blank signal. The

static bit is directly reading the Fast-Blank input line,

whereas the dynamic bit is reading the status of a

flip-flop triggered by the negative edge of the Fast-

Blank signal.

With this monitor logic it is possible to detect if there is

an external RGB source active and if it is a full screen

insertion or only a box. The monitor logic is connected

directly to the FBLIN pin.

Synchronization and Deflection

The synchronization and deflection processing is distributed

over front-end and back-end. The video

clamping, horizontal and vertical sync separation and

all video related timing information are processed in

the front-end. Most of the processing that runs at the

horizontal frequency is programmed on the internal

Fast Processor (FP). Also the values for vertical and

East/West deflection are calculated by the FP software.

The generation of horizontal and vertical drive signals

can be synchronized to the video timing extracted in

the front-end or to a free running line counter in the

back-end.

2.11.1. Deflection Processing

The deflection processing generates the signals for the

horizontal and vertical drive (see Fig. 2–24). This block

contains two phase-locked loops:

– PLL2 generates the horizontal and vertical timing,

e.g. blanking, clamping and composite sync. Phase

and frequency are synchronized by the front sync

signal.

– PLL3 adjusts the phase of the horizontal drive pulse

and compensates for the delay of the horizontal output

stage. Phase and frequency are synchronized

by the oscillator signal of PLL2.

The horizontal drive circuitry uses a digital sine wave

generator to produce the exact (subclock) timing for

the drive pulse HOUT. The generator runs at 1 MHz.

Under control of the EHPLL bit and the internal voltage

supervision it is either synchronized by the deflection

PLL or it is free running. In the output stage the frequency

is divided down to give drive-pulse period and

width. The drive pulse width is programmable. The

horizontal drive uses an open drain output transistor.

After power on or during reset the HOUT generation is

switched to a free running mode with a fix duty cycle of

50%. For normal operation the EHPLL bit has to be set

first. During the switch the actual period of HOUT can

vary by up to 1 µs.

2.11.2. Angle and Bow Correction

The Angle and Bow correction is part of the horizontal

drive PLL. This feature allows a shift of the horizontal

drive pulse phase depending on the vertical position

on the screen. The phase correction has a linear

(angle) and a quadratic term (bow).

2.11.3. Horizontal Phase Adjustment

This section describes a simple way to align PLL

phases and the horizontal frame position.

1. With HDRV the duration of the horizontal drive pulse

has to be adjusted

2. With POFS2 the delay between input video and display

timing (e.g. clamping pulse for analog RGB)

has to be adjusted

3. With CSYDEL the delay between video and analog

RGB (OSD) has to be adjusted.

4. With CSYDEL and HPOS the horizontal position of

both, the digital and analog RGB signal (from

SCART) relative to the clamping pulse has to be

adjusted to the correct position, e.g. the pedestal of

the generator signal.

5. With POFS3 the position of horizontal drive/flyback

relative to RGB has to be adjusted

6. With NEWLIN the position of a scaled video picture

can be adjusted (left, middle, center, etc; versions

with panorama scaler only).

7. With HBST and HBSO, the start and stop values for

the horizontal blanking have to be adjusted.

Note: The processing delay of the internal digital video

path differs depending on the comb filter option of the

VCT 38xxA/B. The versions with comb filter have an

additional delay of 34 clock cycles.

Vertical and East/West Deflection

The calculations of the vertical and East/West deflection

waveforms is done by the internal Fast Processor

(FP). The algorithm uses a chain of accumulators to

generate the required polynomial waveforms. To produce

the deflection waveforms, the accumulators are

initialized at the beginning of each field. The initialization

values must be computed by the TV control processor

and are written to the front-end once. The

waveforms are described as polynomials in x, where x

varies from 0 to 1 for one field.

P: a + b(x-0.5) + c(x-0.5)2 + d(x-0.5)3 + e(x-0.5)4

The initialization values for the accumulators a0..a3 for

vertical deflection and a0..a4 for East/West deflection

are 12-bit values.

Fig. 2–25 shows several vertical and East/West deflection

waveforms. The polynomial coefficients are also

stated.

In order to get a faster vertical retrace timing, the output

impedance of the vertical D/A-converter can be

reduced by 50% during the retrace.

2.11.5. EHT Compensation

The vertical waveform can be scaled according to the

average beam current. This is used to compensate the

effects of electric high-tension changes due to beam

current variations. EHT compensation for East/West

deflection is do

ne with an offset corresponding to the

ne with an offset corresponding to theaverage beam current.

2.11.6. Protection Circuitry

Picture tube and drive stage protection is provided

through the following measures:

– Vertical flyback protection input:

This pin searches for a negative edge in every field,

otherwise the RGB drive signals are blanked.

– Drive shutoff during flyback:

This feature can be selected by software.

– Safety input pin:

This input has two thresholds. Between zero and

the lower threshold, normal functioning takes place.

Between the lower and the higher threshold, the

RGB signals are blanked. Above the higher threshold,

the RGB signals are blanked and the horizontal

drive is shut off. Both thresholds have a small hysteresis.

–

2.12. Reset Function

Reset of all VDP functions is performed by the RESQ

pin. When this pin becomes active, all internal registers

and counters are lost. The TV controller can activate

the RESQ pin by software (see Section 5.7.2. on

page 95).

When the RESQ pin is released, the internal reset is

still active for 4 µs. After that time, the initialization of

all required registers is performed by the internal Fast

Processor. This takes approximately 60 µs. During this

initialization procedure it is not possible to access the

VDP via the I2C interface.

The VDP voltage supervision activates an internal

reset signal when the supply for the digital circuits

(VSUPD) goes below ~2.5 V for more than 50 ns.

2.14. I2C Bus Slave Interface

Communication between the video processing part of

the VDP and the CPU is done via I2C bus. For detailed

information on the I2C bus please refer to the Philips

manual ‘I2C bus Specification’.

The VDP has two I2C bus slave interfaces (for compatibility

with VPC/DDP applications) − one in the

front-end and one in the back-end. Both I2C bus interfaces

use I2C clock synchronization to slow down the

interface if required. Both I2C bus interfaces use one

level of subaddress: the I2C bus chip address is used

to address the VDP and a subaddress selects one of

the internal registers. The I2C bus chip addresses are

given below:

The registers of the VDP have 8 or 16-bit data size;

16-bit registers are accessed by reading/writing two

8-bit data words.

Fig. 2–26 shows I2C bus protocols for read and write

operations of the interface; the read operation requires

an extra start condition and repetition of the chip

address with read command set.

2.14.1. Control and Status Registers

Table 2–3 gives definitions of the VDP control and status

registers. The number of bits indicated for each

register in the table is the number of bits implemented

in hardware, i.e. a 9-bit register must always be

accessed using two data bytes but the 7 MSB will be

‘don’t care’ on write operations and ‘0’ on read operations.

Write registers that can be read back are indicated

in Table 2–3.

Functions implemented by software in the on-chip control

microprocessor (FP) are explained in Table 2–7.

A hardware reset initializes all control registers to 0.

The automatic chip initialization loads a selected set of

registers with the default values given in Table 2–3.

The register modes given in Table 2–3 are

– w: write only register

– w/r: write/read data register

– r: read data from VDP

– v: register is latched with vertical sync

– h: register is latched with horizontal

3. Text and OSD Processing

3.1. Introduction

The VCT 38xxA/B includes a World System Teletext

(WST) decoder, whose display capabilities are also

used for OSD generation. In the following sections the

text and OSD processing part of the VCT 38xxA/B will

be named TPU for short.

With integrated CPU, RAM and ROM, an adaptive

data slicer, a display controller, and a number of interfaces,

the TPU offers acquisition and display of various

teletext and data services such as WST, PDC, VPS,

and WSS. Fig. 3–1 shows the functional block diagram

of the TPU.

The TPU operates independently from the TV controller

and can be controlled by software via I2C bus interface

(see Section 3.14. on page 85). The TV controller

is not burdened with the task of teletext decoding

and communicates with the TPU via a high-level command

language.

The TPU performs the following tasks:

– teletext data acquisition (hardware)

– teletext data decoding (software)

– page generation (software)

– page memory management (software)

– page display (hardware)

– user interface (software)

3.2. SRAM Interface

The SRAM interface connects a standard SRAM to the

internal bus structure. The address bus is 19 bit wide,

addressing SRAMs up to 4 Mbit. Smaller SRAMs can

also be connected.

The SRAM interface has to handle 3 asynchronous

data streams. The CPU needs access to every memory

location of the SRAM. During VBI the slicer writes

up to 22 teletext lines of 43 Bytes into the acquisition

scratch memory. During text display the display controller

copies teletext rows from

display memory into its

display memory into itsinternal row buffer.

On VCT 38xxA/B the SRAM interface of the TPU is

connected to the memory bus of the TV controller. This

is done to save pins and to give the TV controller faster

access to the display memory. Refer to DMA Interface

(chapter 5.9. on page 101) for more details.

After reset the TPU will not use the SRAM interface

until receiving the I2C command “DRAM_MODE” (see

Section 3.12. on page 70).

3.3. Text Controller

The TPU operates with its own 65C02 core running at

10.125 MHz. The core can address up to 64 kBytes of

memory.

The CPU memory contains 640 Bytes RAM, 12 kBytes

program ROM and 12 kBytes character ROM. The

VCT 38xxB contains additional 12kBytes character

ROM. The character ROM holds the font data and is

separated from the program ROM to save CPU time.

The CPU can still access the character ROM via a

DMA interface including wait cycles. The display controller

can also access the CPU memory via the same

DMA interface. By this means it is possible to locate

part of the character font in program ROM or part of

the program code in character ROM.

After Reset the CPU switches to external font memory

if the Font ID vector exists in the external font memory.

After Reset the CPU switches to external program

memory if the Prog ID vector exists in the external program

memory.

3.4. Teletext Acquisition

The only task of the slicer circuit is to extract teletext

lines from the incoming composite video signal and to

store them into the acquisition scratch buffer of the

internal/external SRAM. No page selection is done at

this hardware level.

Four analog sources can be connected, thus it is possible

to receive text from one channel while watching

another on the screen. After clamping and AGC amplifier

the analog video signal is converted into binary

data. Sync separation is done by a sync slicer and a

horizontal PLL, which generate the horizontal and vertical

timing. By these means, no external sync signals

are needed and any available signal source can be

used for teletext reception.

The teletext information itself is acquired using adaptive

slicers on bit and byte level with soft error detection

to decrease the bit error rate under bad reception

conditions. The slicer can be programmed to different

bit rates for reception of PAL, NTSC or MAC world

system teletext as well as VPS, WSS, or CAPTION

signals.

3.5. Teletext Page Management

As a state-of-the-art teletext decoder, the TPU is able

to store and manage a sufficient number of teletext

pages to absorb the annoying transmission cycle

times. The number of available pages is only limited by

the memory size. With an intelligent software and a

4-Mbit SRAM it is possible to store and to control more

than 500 teletext pages.

The management of such a data base is a typical software

task and is therefore performed by the 65C02.

Using a fixed length page table with one entry for

every possible page, the software distributes the content

of the acquisition scratch buffer among the page

memory. The page size is fixed to 1 kByte, only ghost

rows are chained in 128-Byte segments to avoid

unused memory space.

A stored teletext page cannot be displayed directly,

because of the row-adaptive transmission and the

level 2 enhancements (row 26−29). Therefore, the

CPU has to transfer the selected teletext page into a

display page buffer, adding extra data such as character

set extension and non-spacing attributes.

3.5.1. Memory Manager

The Memory manager is the core of the internal TPU

firmware. Most of the acquisition and display related

functions are controlled by this management.

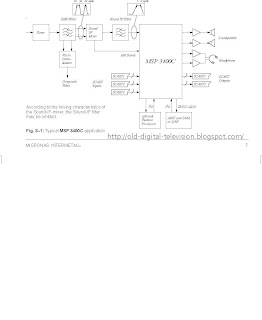

MSP3400CMultistandard Sound Processor

Release Notes:

The hardware description in this

The hardware description in thisdocument is valid for the MSP 3400C – C8 and newer

codes. Revision bars indicate significant changes

to the previous version.

1. Introduction

The MSP 3400C is designed as single-chip Multistandard

Sound Processor for applications in analog and

digital TV sets, satellite receivers and video recorders.

The MSP-family, which is based on the MSP 2400, demonstrates

the progressive development towards highly

integrated multi-functional ICs.

The MSP 3400C, again, improves function integration:

The full TV sound processing, starting with analog

sound IF signal-in, down to processed analog AF-out, is

performed in a single chip. The IC is produced in 0.8 mm

CMOS technology, combined with high performance

digital signal processing.

The MSP 3400C 0.8 m CMOS version is fully pin and

software compatible to the 1.0 m MSP 3400 and MSP

3410. The main difference between the MSP 3400C and

the MSP 3410, consists of the MSP 3410 being able to

decode NICAM signals.

2. Features of the MSP 3400C:

2.1. Features of the Demodulator and Decoder

Sections

The MSP 3400C is designed to perform demodulation

of FM-mono TV sound and two carrier FM systems according

to the German or Korean terrestrial specs. With

certain constraints, it is also possible to do AM-demodulation

according to the SECAM system. Alternatively, the

satellite specs can be processed with the MSP 3400C.

For FM carrier detection in satellite operation, the AMdemodulation

offers a powerful feature to calculate the

carrier field strength, which can be used for automatic

search algorithms. So, the IC facilitates a first step towards

multistandard capability with its very flexible

application and may be used in TV-sets, satellite tuners,

and video recorders.

The MSP 3400C facilitates profitable multistandard capability,

offering the following advantages:

– two selectable analog inputs (TV and SAT-IF sources)

– Automatic Gain Control (AGC) for analog input: input

range: 0.14 – 3 Vpp

– integrated A/D converter for sound-IF inputs

– all demodulation and filtering is performed on chip and

is individually programmable

– no external filter hardware is required

– only one crystal clock (18.432 MHz) is necessary

– FM carrier level calculation for automatic search algorithms

and carrier mute function

– high deviation FM-mono mode (max. deviation:

approx. 360 kHz)

2.2

. Features of the DSP-Section

. Features of the DSP-Section– flexible selection of audio sources to be processed

– digital input and output interfaces via I2S-Bus for external

DSP-processors, surround sound, ADR etc.

– digital interface to process ADR (Astra Digital Radio)

together with DRP 3510 A

– performance of all deemphasis systems including

adaptive Wegener Panda 1 without external components

or controlling

– digitally performed FM-identification decoding and dematrixing

– digital baseband processing: volume, bass, treble,

5-band equalizer, loudness, pseudostereo, and basewidth

enlargement

– simple controlling of volume, bass, treble, equalizer

etc.

– increased audio bandwidth for FM-Audio-signals

(20 Hz – 15 kHz, 1 dB)

2.3. Features of the Analog Section

– three selectable analog pairs of audio baseband inputs

(= three SCART inputs)

input level: 32 V RMS,

input impedance: .25 kW

– one selectable analog mono input (i.e. AM sound),

input level: 32 V RMS,

input impedance: .10 kW

– two high quality A/D converters, S/N-Ratio: .85 dB

– 20 Hz to 20 kHz Bandwidth for SCART-to-SCARTCopy

facilities

– MAIN (loudspeaker) and AUX (headphones): two

pairs of 4-fold oversampled D/A-converters

output level per channel: max. 1.4 V RMS

output resistance: max. 5 kW

S/N-Ratio: .85 dB at maximum volume

max. noise voltage in mute mode: 310 mV (BW: 20 Hz

...16 kHz)

– one pair of four-fold oversampled D/A-converters supplying

two selectable pairs of SCART-Outputs. Output

level per channel: max. 2 V RMS, output resistance:

max. 0.5 kW, S/N-Ratio: .85 dB

(20 Hz...16 kHz).

-----------------------------------------------------------------------

TDA9885; I2C-bus controlled single and multistandard alignment-free IF-PLL demodulatorsGENERAL DESCRIPTION

The TDA9885 is an alignment-free multistandard

(PAL and NT

SC) vision and sound IF signal PLL

SC) vision and sound IF signal PLLdemodulator for negative modulation only and

FM processing.

The TDA9886 is an alignment-free multistandard

(PAL, SECAM and NTSC) vision and sound IF signal PLL

demodulator for positive and negative modulation,

including sound AM and FM processing.

FEATURES

· 5 V supply voltage

· Gain controlled wide-band Vision Intermediate

Frequency (VIF) amplifier, AC-coupled

· Multistandard true synchronous demodulation with

active carrier regeneration: very linear demodulation,

good intermodulation figures, reduced harmonics, and

excellent pulse response

· Gated phase detector for L and L-accent standard

· Fully integrated VIF Voltage Controlled Oscillator

(VCO), alignment-free, frequencies switchable for all

negative and positive modulated standards via I2C-bus

· Digital acquisition help, VIF frequencies of 33.4, 33.9,

38.0, 38.9, 45.75, and 58.75 MHz

· 4 MHz reference frequency input: signal from

Phase-Locked Loop (PLL) tuning system or operating

as crystal oscillator

· VIF Automatic Gain Control (AGC) detector for gain

control, operating as peak sync detector for negative

modulated signals and as a peak white detector for

positive modulated signals

· External AGC setting via pin OP1

· Precise fully digital Automatic Frequency Control (AFC)

detector with 4-bit digital-to-analog converter, AFC bits

readable via I2C-bus

· TakeOver Point (TOP) adjustable via I2C-bus or

alternatively with potentiometer

· Fully integrated sound carrier trap for 4.5, 5.5,

6.0, and 6.5 MHz, controlled by FM-PLL oscillator

· Sound IF (SIF) input for single reference Quasi Split

Sound (QSS) mode, PLL controlled

· SIF-AGC for gain controlled SIF amplifier, single

reference QSS mixer able to operate in high

performance single reference QSS mode and in

intercarrier mode, switchable via I2C-bus

· AM demodulator without extra reference circuit

· Alignment-free selective FM-PLL demodulator with high

linearity and low noise

· Four selectable I2C-bus addresses

· I2C-bus control for all functions

· I2C-bus transceiver with pin programmable Module

Address (MAD).

APPLICATIONS

· TV, VTR, PC, and STB applications.

FUNCTIONAL DESCRIPTION

Figure 1 shows the simplified block diagram of the device

which comprises the following functional blocks:

· VIF amplifier

· Tuner AGC and VIF-AGC

· VIF-AGC detector

· Frequency Phase-Locked Loop (FPLL) detector

· VCO and divider

· AFC and digital acquisition help

· Video demodulator and amplifier

· Sound carrier trap

· SIF amplifier

· SIF-AGC detector

· Single reference QSS mixer

· AM demodulator

· FM demodulator and acquisition help

· Audio amplifier and mute time constant

· Internal voltage stabilizer

· I2C-bus transceiver and MAD (module address).

8.1 VIF amplifier

The VIF amplifier consists of three AC-cou

pled differential

pled differentialstages. Gain control is performed by emitter degeneration.

The total gain control range is typically 66 dB. The

differential input impedance is typically 2 kWin parallel with

3 pF.

8.2 Tuner AGC and VIF-AGC

This block adapts the voltages, generated at the VIF-AGC

and SIF-AGC detectors, to the internal signal processing

at the VIF and SIF amplifiers and performs the tuner AGC

control current generation. The onset of the tuner AGC

control current generation can be set either via the I2C-bus

(see Table 13) or optionally by a potentiometer at pin TOP

(in case that the I2C-bus information cannot be stored,

related to the device). The presence of a potentiometer is

automatically detected and the I2C-bus setting is disabled.

Furthermore, derived from the AGC detector voltage, a

comparator is used to test if the corresponding VIF input

voltage is higher than 200 mV. This information can be

read out via the I2C-bus (bit VIFLEV = 1).

8.3 VIF-AGC detector

Gain control is performed by sync level detection (negative

modulation) or peak white detection (positive modulation).

For negative modulation, the sync level voltage is stored at

an integrated capacitor by means of a fast peak detector.

This voltage is compared with a reference voltage

(nominal sync level) by a comparator which charges or

discharges the integrated AGC capacitor for the

generation of the required VIF gain. The time constants for

decreasing or increasing the gain are nearly equal and the

total AGC reaction time is fast to cope with ‘aeroplane

fluttering’.

For positive modulation, the white peak level voltage is

compared with a reference voltage (nominal white level)

by a comparator which charges (fast) or discharges (slow)

the external AGC capacitor directly for the generation of

the required VIF gain. The need of a very long time

constant for VIF gain increase is because the peak white

level may appear only once in a field. In order to reduce

this time constant, an additional level detector increases

the discharging current of the AGC capacitor (fast mode)

in the event of a decreasing VIF amplitude step controlled

by the detected actual black level voltage. The threshold

level for fast mode AGC is typically -6 dB video amplitude.

The fast mode state is also transferred to the SIF-AGC

detector for speed-up. In case of missing peak white

pulses, the VIF gain increase is limited to typically +3 dB

by comparing the detected actual black level voltage with

a corresponding reference voltage.

8.4 FPLL detector

The VIF amplifier output signal is fed into a frequency

detector and into a phase detector via a limiting amplifier

for removing the video AM.

During acquisition the frequency detector produces a

current proportional to the frequency difference between

the VIF and the VCO signals. After frequency lock-in the

phase detector produces a current proportional to the

phase difference between the VIF and the VCO signals.

The currents from the frequency and phase detectors are

charged into the loop filter which controls the VIF VCO and