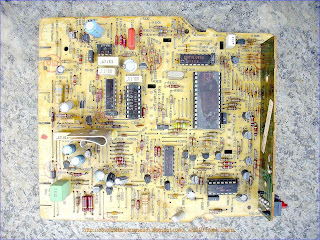

The METZ 7096 CLASSIC COLOR (CH679G) CHASSIS 679G has a completely modular approach, see pictures, and it's quite complex expecially in the power supply / horizontal deflection parts.

Was even first METZ TV COLOR CHASSIS ground isolated from mains and featuring PHILIPS 30AX CRT TUBE.

TDA2541 IF AMPLIFIER WITH DEMODULATOR AND AFC

DESCRIPTION

The TDA2540 and 2541 are IF amplifier and A.M.

demodulator circuits for colour and black and white

televisionreceiversusingPNPorNPNtuners. They

are intended for reception of negative or positive

modulation CCIR standard.

They incorporate the following functions : .Gain controlled amplifier .Synchronous demodulator .White spot inverter .Video preamplifier with noise protection .Switchable AFC .AGC with noise gating .Tuner AGC output (NPN tuner for 2540)-(PNP

tuner for 2541) .VCR switch for video output inhibition (VCR

play back).

SGS-THOMSON TDA2030 14W Hi-Fi AUDIO AMPLIFIER

DESCRIPTION

The TDA2030 is a monolithic integrated circuit in

Pentawatt package, intended for use as a low

frequency class AB amplifier. Typically it provides

14W output power (d = 0.5%) at 14V/4Ω;at ± 14V

the guaranteedoutput poweris 12W on a 4Ω load

and 8Won a 8Ω (DIN45500).

TheTDA2030provideshighoutputcurrentandhas

very lowharmonic and cross-over distortion.

Further the device incorporates an original (and

patented) short circuit protection system compris-

ing an arrangement for automatically limiting the

dissipated power so as to keep the working point

of the outputtransistorswithin their safe operating

area.A conventionalthermal shut-downsystem is

also included.

SHORT CIRCUIT PROTECTION

The TDA2030 has an originalc ircuitwhichlimitsthe

current of the output transistors.Fig.18 showsthat

the maximum output current is a function of the

collector emitter voltage; hence the output transis-

tors work within their safe operating area (Fig. 2).

This functioncan thereforebe consideredas being

peak power limiting rather than simple current lim-

iting.

It reducesthe possibility that the devicegetsdam-

aged during an accidental short circuit from AC

output to ground.

THERMAL SHUT-DOWN

The presenceof a thermallimiting circuit offersthe

following advantages:

1. An overload on the output (even if it is perma-

nent),oranabovelimitambienttemperaturecan

be easily supported since the Tj cannot be

higher than 150°C.

2. The heatsinkcan havea smaller factorof safety

compared with that of a conventional circuit.

There is no possibility of devicedamage due to

high junctiontemperature.If for any reason,the

junctiontemperatureincreasesup to 150°C, the

thermal shut-down simply reduces the power

dissipationat the current consumption.

The maximum allowable power dissipation de-

pendsuponthe sizeof the externalheatsink(i.e.its

thermal resistance); fig. 22 shows this dissipable

power as a function of ambient temperature for

differentthermalresistance.

METZ 7096 CLASSIC COLOR (CH679G) CHASSIS 679G AMBIENT LIGHT RESPONSIVE CONTROL OF BRIGHTNESS, CONTRAST AND COLOR SATURATION

1. In a color television apparatus, a circuit for varying color display characteristics in accordance with variations in ambient light comprising: 2. In a color picture display system having a display device comprising: 3. The display system of claim 2 with kinescope means having a first set of electrodes and a second set of electrodes, 4. The display system of claim 2 with said light sensing means being responsive to the intensity of the ambient light and said parameter varying in accordance with the intensity of ambient light. 5. The display system of claim 4 with said modifying means increasing the gain of said luminance amplifying means at a greater rate than the gain of said chroma amplifying means as said ambient light intensity is increased. 6. A color television apparatus comprising: 7. In a color television receiver: 8. The receiver of claim 7 with said modifying means comprising a light dependent resistor means, 9. The receiver of claim 8 with second impedance means coupling said light dependent resistor means to said luminance gain means to control the gain of said luminance gain means. 10. The receiver of claim 9 with said second impedance means comprising a parallel combination of capacitance and resistance. 11. The receiver of claim 7 with said modifying means varying the gain of the luminance gain means at a greater rate than the gain of the chroma gain means as ambient light is varied. 12. The receiver of claim 7 with said modifying means being responsive to the intensity of ambient light and said parameter being varied as the intensity of the ambient light is varied. 13. The receiver of claim 7 with said modifying means attenuating the gain of said luminance amplifying means approximately fifty percent more than the gain of said chroma amplifying means, when the attenuation is measured in decibels, as said ambient light intensity is decreased. 14. In a color television receiver:

The

present invention relates generally to a television receiver control

system and more particularly to a control system for maintaining

proper balance between room lighting conditions and the level of

picture tube excitation in a color television receiver. More

especially the present invention functions to increase contrast,

intensity and chroma signal strength when the room lighting level

increases to diminish these parameters when the level of room lighting

decreases.

The

present invention relates generally to a television receiver control

system and more particularly to a control system for maintaining

proper balance between room lighting conditions and the level of

picture tube excitation in a color television receiver. More

especially the present invention functions to increase contrast,

intensity and chroma signal strength when the room lighting level

increases to diminish these parameters when the level of room lighting

decreases.Conventional television receivers, of course, have manually operable controls by means of which a viewer may set the level of contrast, intensity, and chroma signal strength to what he feels to be an optimum level for given room lighting conditions. Under changed room lighting conditions, the viewer will obtain the optimum viewing situation by changing these manual controls to a new preferred level.

It is also known in the prior art to automate this process for a black and white television receiver, for example, as taught in the U.S. Pat. No. 3,165,582 to Korda, issued Jan. 12, 1965, and the French patent 1,223,058 issued in June of 1960.

It is accordingly an object of the present invention to provide an automatic color saturation control for a color television receiver by providing separate, predetermined gains for the luminance and chroma for a given change in ambient light. In the disclosed preferred embodiment, the luminance signal is attenuated 3.3 dB and the chroma signal is attenuated 2.1 dB for a change in ambient light from 100 footcandles to 0.1 footcandles, measured at the display face.

SUMMARY OF THE INVENTION

The

foregoing as well as numerous other objects and advantages of the

present invention are achieved by providing a light sensitive element in

a television receiver exposed to ambient light in the vicinity of the

receiver for separately controlling brightness, contrast and chroma

signal strength of the displayed picture in accordance with the level

of ambient light. The circuit of a preferred embodiment of the present

invention, in response to an increase of ambient light level,

functions to increase the gain of the luminance amplifier in a

relatively greater ratio than the increase in the gain of the

chrominance amplifier whereas when the ambient light level decreases

the respective gains of these two amplifiers are decreased, again,

with the change in the luminance signal being in a greater proportion

than the change in the chroma signal strength signal. By using the

teaching of this invention, other gain relationships between the

luminance components and chroma signal, for a given change in ambient

light, may be automatically attained to achieve a desired result of

luminance and color saturation.

The

foregoing as well as numerous other objects and advantages of the

present invention are achieved by providing a light sensitive element in

a television receiver exposed to ambient light in the vicinity of the

receiver for separately controlling brightness, contrast and chroma

signal strength of the displayed picture in accordance with the level

of ambient light. The circuit of a preferred embodiment of the present

invention, in response to an increase of ambient light level,

functions to increase the gain of the luminance amplifier in a

relatively greater ratio than the increase in the gain of the

chrominance amplifier whereas when the ambient light level decreases

the respective gains of these two amplifiers are decreased, again,

with the change in the luminance signal being in a greater proportion

than the change in the chroma signal strength signal. By using the

teaching of this invention, other gain relationships between the

luminance components and chroma signal, for a given change in ambient

light, may be automatically attained to achieve a desired result of

luminance and color saturation.BRIEF DESCRIPTION OF THE DRAWINGS

The aforementioned and other objects, features and advantages of the present invention will become more apparent from the following detailed description thereof when considered in conjunction with the drawings wherein:

FIG. 1 is a partial block diagram of a color television receiver employing the present invention;

FIG. 2 is a detailed schematic diagram of those portions of FIG. 1 embodying the present invention;

FIG. 3 illustrates chroma gain control characteristic curves for the circuit of FIG. 2; and

FIG. 4 is a graph showing changes in luminance and chroma signal strength according to changes in ambient light.

DESCRIPTION OF THE PREFERRED EMBODIMENT

Considering first FIG. 1 which

Considering first FIG. 1 which  illustrates

generally in block diagram form a color television receiver embodying

the present invention, this receiver is seen to comprise a tuner and

radio frequency amplifier 11 for detecting and amplifying incoming

signals received on the antenna 13 and supplying those signals through

an appropriate heterodyning process to an intermediate frequency

amplifier 15. After detection in the detector 17, the luminance signals

are passed through a delay 19 which compensates for the delays

experienced by the chroma signal strength signals and then to the

luminance amplifier 21, which, of course, corresponds to the video

amplifier of a black and white receiver, to then be supplied to the

cathode ray tube 23. The luminance or video amplifier may also be

provided with gain control circuitry 25. An appropriate band pass

amplifier 27 may be employed to separate out the chroma signal strength

signals which are demodulated by the demodulator 29 in well known

fashion to provide the three color difference signals to grids in the

color cathode ray tube 23. While the present invention will be described

with respect to such color difference signals, it is equally

applicable to direct RGB color separation systems. An ambient light

level detector 31 such as a light dependent resistor of the cadmium

sulphide variety is physically located on the front of the television

receiver in such a position as to be exposed to the light levels in the

vicinity of the receiver so that its resistance varies inversely in

accordance with variations in the ambient light levels around the

receiver. These resistance variations are then employed to control the

gain of the luminance amplifier 21 by way of gain control 25 and to

control the gain of the chroma signal strength amplifier circuitry.

illustrates

generally in block diagram form a color television receiver embodying

the present invention, this receiver is seen to comprise a tuner and

radio frequency amplifier 11 for detecting and amplifying incoming

signals received on the antenna 13 and supplying those signals through

an appropriate heterodyning process to an intermediate frequency

amplifier 15. After detection in the detector 17, the luminance signals

are passed through a delay 19 which compensates for the delays

experienced by the chroma signal strength signals and then to the

luminance amplifier 21, which, of course, corresponds to the video

amplifier of a black and white receiver, to then be supplied to the

cathode ray tube 23. The luminance or video amplifier may also be

provided with gain control circuitry 25. An appropriate band pass

amplifier 27 may be employed to separate out the chroma signal strength

signals which are demodulated by the demodulator 29 in well known

fashion to provide the three color difference signals to grids in the

color cathode ray tube 23. While the present invention will be described

with respect to such color difference signals, it is equally

applicable to direct RGB color separation systems. An ambient light

level detector 31 such as a light dependent resistor of the cadmium

sulphide variety is physically located on the front of the television

receiver in such a position as to be exposed to the light levels in the

vicinity of the receiver so that its resistance varies inversely in

accordance with variations in the ambient light levels around the

receiver. These resistance variations are then employed to control the

gain of the luminance amplifier 21 by way of gain control 25 and to

control the gain of the chroma signal strength amplifier circuitry.The entire color demodulation process is only generally depicted in the block diagram of FIG. 1 and is illustrated as a closed loop burst gain controlled chroma amplifier system with auxiliary chroma gain control introduced by way of the detector 33 from the ambient light level detector 31. A burst gain controlled chroma amplifier circuit is somewhat analogous to a black and white keyed AGC circuit and functions to set the gain level of the amplifier 27 in accordance with the color sync burst rather than the chroma signal level associated with a particular picture. While the present invention is being described with respect to this preferred type of gain control, it would, of course, be possible, in television circuits employing DC gain controls for chroma and/or contrast, to connect the ambient light tracking means to these direct current control circuits. The gain controlled chroma band pass amplifier, of course, supplies an output to a burst amplifier 35 which in turn drives an automatic phase control system 37 for synchronizing the 3.58 megacycle oscillator 39 the output of which is used in the color demodulation process.

Considering

now FIG. 2 which illustrates schematically in detail those portions

of the receiver of FIG. 1 necessary for a complete understanding of

the present invention, the light dependent resistor 41 is mounted near

the front of the television receiver in such a position as to

adequately receive the ambient lighting conditions in the vicinity of

the receiver. The resistance of this device is inversely proportional

to the intensity of light incident thereon. If the room ambient light

experiences an increase in level, the resistance of light dependent

resistor 41 will decrease which decrease in turn lowers the voltage at

the base of transistor 43 which in turn lowers the voltage at the

emitter due to increased conduction through that transistor. T

Considering

now FIG. 2 which illustrates schematically in detail those portions

of the receiver of FIG. 1 necessary for a complete understanding of

the present invention, the light dependent resistor 41 is mounted near

the front of the television receiver in such a position as to

adequately receive the ambient lighting conditions in the vicinity of

the receiver. The resistance of this device is inversely proportional

to the intensity of light incident thereon. If the room ambient light

experiences an increase in level, the resistance of light dependent

resistor 41 will decrease which decrease in turn lowers the voltage at

the base of transistor 43 which in turn lowers the voltage at the

emitter due to increased conduction through that transistor. T his in

turn increases the gain of the chroma amplifier transistor stage 45.

More precisely the lowering the voltage at the emitter of transistor 43

raises a threshold in the automatic chroma control detector 33 so

that the chroma signal strength signal, and hence the color saturation

level, to the picture tube is increased. In the absence of a chroma

signal with its synchronizing burst, the gain of the chroma amplifier

is set at a maximum by the voltage divider comprising resistors 47 and

49. At this time there is no output from the automatic chroma control

detector to the base of transistor 51 and that transistor is

non-conducting.

his in

turn increases the gain of the chroma amplifier transistor stage 45.

More precisely the lowering the voltage at the emitter of transistor 43

raises a threshold in the automatic chroma control detector 33 so

that the chroma signal strength signal, and hence the color saturation

level, to the picture tube is increased. In the absence of a chroma

signal with its synchronizing burst, the gain of the chroma amplifier

is set at a maximum by the voltage divider comprising resistors 47 and

49. At this time there is no output from the automatic chroma control

detector to the base of transistor 51 and that transistor is

non-conducting.When a color signal is received, the detector provides an output signal proportional to the color sync burst level which turns on the transistor 51 to control the gain of the chroma amplifier stage 45 so as to maintain the desired output level. The turn on level of transistor 51 represents a fairly well defined knee in the chroma gain control characteristic curves illustrated in FIG. 3. Operation beyond the knee or threshold of such a curve operates to maintain a nearly constant chroma output level while operation below the knee of the curve and its extension as the almost vertical dotted line represents the open loop characteristic wherein there is no automatic gain control to the chroma amplifier. Since transistor 51 is non-conducting below the knee of this curve, gain control is delayed until the output signal reaches this threshold point. Since variations in the potential at the emitter of transistor 43 cause corresponding variations in the potential at the base of transistor 51, it is clear that a variation in the resistance of the light dependent resistor 41 will, for example, cause the gain control characteristic curve to shift from that depicted by curve A to that depicted by curve B and that for a given burst level input as represented by the vertical dotted line, two different levels of chroma output which, in turn, cause two different levels of color saturation will be achieved by a change in the light intensity incident on the resistor 41.

To better understand the operation of detector 33, assume that the burst voltage induced across the top half of the secondary of transformer 34 is in phase with the 3.58 megacycle reference signal and that the burst voltage induced across the bo

ttom half of the secondary of transformer 34 is 180° out of

phase with this reference signal. Assuming further that the diodes 36

and 38 have equal characteristics, that the resistors 40 and 42 are

equal, that the capacitors 44 and 46 are equal, and that the two

portions of the secondary winding on transformer 34 are equal when no

burst is being received, diodes 36 and 38 will conduct equally but

during opposite portions of a cycle. Diode 36 conducts during negative

excursions of the reference signal whereas diode 38 conducts during

positive portions of that reference wave form. Thus during the

negative portions of the reference wave form diode 36 conducts to

charge capacitor 44 so that its right hand plate is negative and its

left hand plate is positive. During the positive excursions, diode 38

conducts to charge capacitor 46 with its right hand plate positive and

its left hand plate negative. Under this assumed no burst input

condition the net charge on these capacitors yields a voltage on line

48 which is zero. If noise is introduced into the system, it will be

of equal amplitude but opposite phase across the two diodes and both

diodes will

ttom half of the secondary of transformer 34 is 180° out of

phase with this reference signal. Assuming further that the diodes 36

and 38 have equal characteristics, that the resistors 40 and 42 are

equal, that the capacitors 44 and 46 are equal, and that the two

portions of the secondary winding on transformer 34 are equal when no

burst is being received, diodes 36 and 38 will conduct equally but

during opposite portions of a cycle. Diode 36 conducts during negative

excursions of the reference signal whereas diode 38 conducts during

positive portions of that reference wave form. Thus during the

negative portions of the reference wave form diode 36 conducts to

charge capacitor 44 so that its right hand plate is negative and its

left hand plate is positive. During the positive excursions, diode 38

conducts to charge capacitor 46 with its right hand plate positive and

its left hand plate negative. Under this assumed no burst input

condition the net charge on these capacitors yields a voltage on line

48 which is zero. If noise is introduced into the system, it will be

of equal amplitude but opposite phase across the two diodes and both

diodes will be affected to an equal extent resulting in no change in

the voltage on line 48. When during a color telecast a burst signal is

present, we may assume that the burst voltage induced across the two

portions of the secondary of transformer 34 are of equal amplitude to

the 3.58 megacycle reference signal. With this situation the diode 36

will not conduct since the burst voltage is equal in phase and

amplitude to the reference signal and its anode and cathode remain at

the same potential. The diode 38 will, however, conduct readily since

the burst and reference signals have an additive rather than a

cancelling effect on it resulting in the diode 38 conducting twice as

much as in the previous no burst example and resulting in the

capacitor 46 charging to about twice its previous voltage which

voltage is presented on line 48 as a control signal.

be affected to an equal extent resulting in no change in

the voltage on line 48. When during a color telecast a burst signal is

present, we may assume that the burst voltage induced across the two

portions of the secondary of transformer 34 are of equal amplitude to

the 3.58 megacycle reference signal. With this situation the diode 36

will not conduct since the burst voltage is equal in phase and

amplitude to the reference signal and its anode and cathode remain at

the same potential. The diode 38 will, however, conduct readily since

the burst and reference signals have an additive rather than a

cancelling effect on it resulting in the diode 38 conducting twice as

much as in the previous no burst example and resulting in the

capacitor 46 charging to about twice its previous voltage which

voltage is presented on line 48 as a control signal.Suppose now that the burst signal amplitude is reduced to one half that of the foregoing example. With this new assumption the phase relationships remain as before but now diode 36 will conduct about one half its previous amount while diode 38 conducts about one and one half times its previous amount resulting in a voltage on line 48 which is about one half the previous voltage.

The voltage on line 48 which is approximately proportional to the burst voltage is applied to the base of transistor 51 which biases the base of the chroma amplifier transistor 45 thereby controlling the gain of that chroma amplifier stage.

A variation in threshold can

be achieved by altering the conduction points of the diodes 36 and 38.

This is accomplished by applying a bias voltage to the junction of

these two diodes to alter their respective points of conduction

thereby changing the output voltage on line 48. For example, if a

positive 2-volt direct current bias is applied to the junction of the

two diodes, under a no burst input condition, diode 38 will conduct

sooner and turn off later than with no bias applied, while diode 36

will turn on later and off sooner than under the no bias condition.

This results in a control voltage on line 48 under the no burst

condition. In other words, a bias voltage applied to the junction of

the two diodes acts as an additional bias on the chroma amplifier

stage thereby affecting its gain.

A variation in threshold can

be achieved by altering the conduction points of the diodes 36 and 38.

This is accomplished by applying a bias voltage to the junction of

these two diodes to alter their respective points of conduction

thereby changing the output voltage on line 48. For example, if a

positive 2-volt direct current bias is applied to the junction of the

two diodes, under a no burst input condition, diode 38 will conduct

sooner and turn off later than with no bias applied, while diode 36

will turn on later and off sooner than under the no bias condition.

This results in a control voltage on line 48 under the no burst

condition. In other words, a bias voltage applied to the junction of

the two diodes acts as an additional bias on the chroma amplifier

stage thereby affecting its gain.The control of brightness (intensity) and contrast is achieved in the present invention by a second light dependent resistor 53 which is optically coupled to a light emitting diode 55. LIght emitting diode 55 and light dependent resistor 53 are encapsulated in a light impervious housing illustrated by the dotted line 57. As the room ambient light changes, the change in the resistance of light dependent resistor 41 causes a change in the current through light emitting diode 55. Variations in the current through the light emitting diode cause corresponding variations in the light emitted thereby which in turn cause variations in the resistance of the light dependent resistor 53. The luminance or video amplifier is here illustrated as a three transistor amplifier with the output of the first amplifier stage being across resistor 59. A diminution in the resistance of light dependent resistor 53 causes a lowering of this output impedance and thus a diminution in the gain of the luminance amplifier. In other words, if the light intensity in the room increases, the resistance of resistor 41 will decrease causing a decrease in the current through light emitting diode 55 and, therefore, a decrease in its light output level and this decreased light will cause an increase in the resistance of light dependent resistor 53 thus increasing the effective output load resistor for the transistor 61 thus increasing the gain of the video amplifier as desired.

Variable resistor 63 being effectively in series with the light dependent resistor 41 may be varied to compensate for differences in specific light dependent resistors so as to establish a desired level of picture brightness, contrast and color saturation for a given level of ambient light. Variable resistance 65 which is in parallel with the light dependent resistor 41 may be varied so as to effectively change the range of variation in brightness, contrast and color saturation for a specific range of variations in the ambient light conditions. The entire automatic control circuit of the present invention may be bypassed by closing the defeat switch 67.

Looking now at FIGS. 2 and

4, the relative attenuation of the chroma channel and luminance

channel will become apparent. Looking first at FIG. 4, the abscissa is

the measure of ambient illumination in foot candles on a log scale,

and the ordinate is the measure of attenuation of signal amplitude in

dB. At 100 footcandles there is 0 dB attenuation of luminance and

chroma signals and as the ambient illumination decreases to 0.1 foot

candles, it is seen that the chroma signal line 72 is down 2.1 dB

while the luminance signal line 72 is down 3.3 dB. This ratio has been

found to be a highly satisfactory ratio giving a very pleasing

picture at all ambient light levels between 0.1 footcandles and 100

footcandles of ambient light.

4, the relative attenuation of the chroma channel and luminance

channel will become apparent. Looking first at FIG. 4, the abscissa is

the measure of ambient illumination in foot candles on a log scale,

and the ordinate is the measure of attenuation of signal amplitude in

dB. At 100 footcandles there is 0 dB attenuation of luminance and

chroma signals and as the ambient illumination decreases to 0.1 foot

candles, it is seen that the chroma signal line 72 is down 2.1 dB

while the luminance signal line 72 is down 3.3 dB. This ratio has been

found to be a highly satisfactory ratio giving a very pleasing

picture at all ambient light levels between 0.1 footcandles and 100

footcandles of ambient light.The manner in which this variation in luminance attenuation is achieved may be seen by looking at FIG. 2. As mentioned, the chroma channel signal is varied by the conduction level of transistor 43. As light dependent resistor 41 changes in resistance, the conduction level of transistor 43 will also change with the degree of change being determined by divider resistances 75 and 76. Further the luminance channel gain is determined by resistor 77 since it is this resistor which will control the signal level of light emitting diode 55 which in turn will control the gain to luminance transistor 61. It is these resistors which determine the relative amount of attenuation of gain in the chroma and luminance channels as the ambient light is changed. In this embodiment, resistance 75 is 5.6 k ohms, resistance 76 is 4.3 k ohms, resistance 77 is 3.9 k ohms, resistance 78 is 7.5 k ohms, the voltage applied to the upper terminal of resistance 78 is 35 volts, resistance 63 is 500 ohms, resistance 65 is 25 k ohms, resistance 69 is 4.7 k ohms, capacitance 71 is 47 microfarads, resistance 59 is 1 k ohm, resistance 59a is 6.8 k ohms, resistance 62a is 1 k ohms, resistance 64a is 100 ohms, resistance 64b is 6.8 k ohms. Light dependent resistor 41 is a Clariex CL-11360, photocoupler unit 57 is Magnavox Part Number 701482. Transistors 43, 61, 62, and 64 are 2N3962, 2N4916, MPSA20 and 25C685A, respectively. This invention has been incorporated in a Magnavox Company T979 color television chassis.

The effective load resistance for the transistor 61 under direct current conditions is the parallel combination of the resistor 59 and the series pair of resistors 53 and 69 whereas due to the presence of capacitor 71 this effective load resistance under alternating current conditions is the parallel combination of resistors 59 and 53. Thus the ratio of AC to DC gain for this video amplifier stage may be selected by proper selection of these parameters so as to maintain the black level of the picture essentially constant.

Thus while the present invention has been described with respect to a specific embodiment, numerous modifications will suggest themselves to those of ordinary skill in the art. Since the luminance and chroma gains are individually controlled for a given change in ambient light, the gain ratios between the luminance and chroma channels may be selected as desired to achieve a desired effect for a given change in ambient light. Also, while the present invention has been described in the environment of a television receiver, the invention could equally well be used in television monitors as well as many other types of display devices. Accordingly the scope of the present invention is to be measured only by that of the appended claims.

In a color television receiver, first and second amplifiers are respectively included in the luminance and chrominance channels to permit control of contrast and saturation. The amplifiers have gain versus control voltage characteristics including linear portions extrapolated to cut off at predetermined voltages which may or may not be the same. A first potentiometer is coupled between a source of fixed voltage equal to the extrapolated cut off voltage of the first amplifier and a gain controlling voltage source. The gain controlling voltage may be produced by a circuit including an element responsive to ambient light. The wiper of the first potentiometer is coupled to the first amplifier to couple a voltage developed at a predetermined point of the first potentiometer to the first amplifier to control its gain. A second potentiometer is coupled between a source of voltage equal to the extrapolated cut off voltage of the second amplifier and the gain controlling voltage source to receive a portion of the gain controlling voltage in accordance with the ratio of the extrapolated cut off voltages of the first and second amplifiers. The wiper of the second po

tentiometer is coupled to the second amplifier to couple a

voltage developed at a predetermined point of the second potentiometer

to the second amplifier to control its gain. In this manner, the

contrast of the receiver may be varied over a relatively wide range

while saturation is maintained substantially constant.

tentiometer is coupled to the second amplifier to couple a

voltage developed at a predetermined point of the second potentiometer

to the second amplifier to control its gain. In this manner, the

contrast of the receiver may be varied over a relatively wide range

while saturation is maintained substantially constant.1. In a color television signal processing system of the type including luminance and chrominance signal processing channels, apparatus comprising:

first and second amplifiers respectively included in said luminance and chrominance channels, said amplifiers having gain versus control voltage characteristics including linear portions extrapolated to cut-off at predetermined voltages which may or may not be the same voltage;

a gain controlling voltage source;

means for coupling said gain controlling voltage to said first amplifier to control its gain;

potentiometer means coupled between a fixed voltage substantially equal to the extrapolated cut-off voltage of said second amplifier and to said gain controlling voltage source to recieve a portion of said gain controlling voltage in accordance with the ratio of the extrapolated cut-off voltages of said first and second amplifiers; and

means for coupling a voltage developed at a predetermined point on said potentiometer means to said second amplifier to control its gain.

2.

The apparatus recited in claim 1 wherein said means for coupling said

gain controlling voltage to said first amplifier includes another

potentiometer coupled between a source of fixed voltage substantially

equal to the extrapolated cut-off voltage of said first amplifier and

said gain controlling voltage source.

3. In a color television signal processing system of the type

including luminance and chrominance signal processing channels,

apparatus comprising:

2.

The apparatus recited in claim 1 wherein said means for coupling said

gain controlling voltage to said first amplifier includes another

potentiometer coupled between a source of fixed voltage substantially

equal to the extrapolated cut-off voltage of said first amplifier and

said gain controlling voltage source.

3. In a color television signal processing system of the type

including luminance and chrominance signal processing channels,

apparatus comprising:first and second amplifiers respectively included in said luminance and chrominance channels, said amplifiers having gain control voltage characteristics including linear portions extrapolated to cut-off at substantially the same predetermined voltage;

a source of gain controlling voltage; and

means for coupling said gain controlling voltage to said first and second amplifiers.

4. Apparatus comprising:

first variable gain amplifying means for

amplifying a first signal in

response to a first DC control signal, said first amplifying means

having a first gain versus DC control voltage characteristic including a

linear region, said linear region having a gain substantially equal

to 0 at a DC control voltage equal to VO ;

amplifying a first signal in

response to a first DC control signal, said first amplifying means

having a first gain versus DC control voltage characteristic including a

linear region, said linear region having a gain substantially equal

to 0 at a DC control voltage equal to VO ;second variable gain amplifying means for amplifying a second signal in response to a second DC control signal, said second amplifying means having a second gain versus DC control voltage characteristic including a linear region, said linear region having a gain substantially equal to 0 at a DC control voltage equal to AVO, where A is a number greater than 0;

a first source of fixed voltage substantially equal to VO ;

a second source of fixed voltage substantially equal to AVO ;

means for developing a third DC control voltage v;

means for developing a portion Av of said third control voltage v;

first means for deriving said first control voltage including means for providing the difference between said third control voltage v and said fixed voltage VO and means for adding a predetermined portion of the difference between said third control voltage v and said fixed voltage VO to said DC control voltage v; and

second means for deriving said second control voltage including means for providing the difference between a portion Av of said third control voltage v and said fixed voltage AVO and means for adding a predetermined portion of the difference between said portion Av and said fixed voltage AVO to said DC control voltage v.

5.

The apparatus recited in claim 4 wherein A is equal to 1.

6. The apparatus recited in claim 4 wherein

said first amplifying means is included in a luminance channel of a

televeision signal processing system and said second amplifying means

is included in a chrominance channel of said television signal

processing system. 7. The

apparatus recited in claim 6 wherein means for developing said third

control voltage includes means responsive to ambient light.

8. The apparatus recited in claim 4 wherein

said first means includes first voltage divider means coupled between

said fixed voltage VO and said third DC control voltage v;

and wherein said second means includes second voltage divider means

coupled between said fixed voltage AVO and said portion Av.

9. The apparatus recited in claim

8 wherein said first voltage divider means includes a first

potentiometer, said first potentiometer having a wiper coupled to said

first amplifying means; and wherein said second voltage divider means

includes a second potentiometer, said second potentiometer having a

wiper coupled to said amplifying means.

10. The apparatus recited in claim 4 wherein said second gain

versus DC control voltage characteristic includes a region between said

voltage AVO and a voltage VB where the gain is greater than 0, said voltage VB

being substantially equal to the voltage at which said second

amplifying means has a gain substantially equal to 0; and wherein said

second source of fixed voltage includes means for coupling said voltage

VB to said second amplifying means.

11. The apparatus recited in claim 10 wherein said

second source of said voltage AVO includes a third source of fixed voltage VB ; potentiometer means coupled between said third source of fixed voltage VB

and said means for developing said third DC control voltage; and

means coupled to said potentiometer means for developing said voltage

AVO at a point along said potentiometer means; said

potentiometer means including a wiper coupled to said second amplifier

means, said wiper being adjustable to couple a DC voltage VFB and said third control voltage to said second amplifying means.

5.

The apparatus recited in claim 4 wherein A is equal to 1.

6. The apparatus recited in claim 4 wherein

said first amplifying means is included in a luminance channel of a

televeision signal processing system and said second amplifying means

is included in a chrominance channel of said television signal

processing system. 7. The

apparatus recited in claim 6 wherein means for developing said third

control voltage includes means responsive to ambient light.

8. The apparatus recited in claim 4 wherein

said first means includes first voltage divider means coupled between

said fixed voltage VO and said third DC control voltage v;

and wherein said second means includes second voltage divider means

coupled between said fixed voltage AVO and said portion Av.

9. The apparatus recited in claim

8 wherein said first voltage divider means includes a first

potentiometer, said first potentiometer having a wiper coupled to said

first amplifying means; and wherein said second voltage divider means

includes a second potentiometer, said second potentiometer having a

wiper coupled to said amplifying means.

10. The apparatus recited in claim 4 wherein said second gain

versus DC control voltage characteristic includes a region between said

voltage AVO and a voltage VB where the gain is greater than 0, said voltage VB

being substantially equal to the voltage at which said second

amplifying means has a gain substantially equal to 0; and wherein said

second source of fixed voltage includes means for coupling said voltage

VB to said second amplifying means.

11. The apparatus recited in claim 10 wherein said

second source of said voltage AVO includes a third source of fixed voltage VB ; potentiometer means coupled between said third source of fixed voltage VB

and said means for developing said third DC control voltage; and

means coupled to said potentiometer means for developing said voltage

AVO at a point along said potentiometer means; said

potentiometer means including a wiper coupled to said second amplifier

means, said wiper being adjustable to couple a DC voltage VFB and said third control voltage to said second amplifying means.  Recently, the maximum brightness

available from television receivers has increased sufficiently so that a

pleasing image may be reproduced under conditions of high ambient

light as well as under conditions of low ambient light. Apparatus is

known for automatically controlling the contrast and brightness

properties of a television receiver in response to ambient light to

provide a pleasing image over a range of ambient light conditions. Such

apparatus is described in U.S. Pat. Nos. 3,027,421, entitled "Circuit

Arrangements For Automatically Adjusting The Brightness And The

Contrast In A Television Receiver," issued to H. Heijligers on Mar.

27, 1962 and 3,025,345, entitled "Circuit Arrangement For Automatic

Readjustment Of The Background Brightness And The Contrast In A

Television Receiver," issued to R. Suhrmann on Mar. 13, 1962.

Recently, the maximum brightness

available from television receivers has increased sufficiently so that a

pleasing image may be reproduced under conditions of high ambient

light as well as under conditions of low ambient light. Apparatus is

known for automatically controlling the contrast and brightness

properties of a television receiver in response to ambient light to

provide a pleasing image over a range of ambient light conditions. Such

apparatus is described in U.S. Pat. Nos. 3,027,421, entitled "Circuit

Arrangements For Automatically Adjusting The Brightness And The

Contrast In A Television Receiver," issued to H. Heijligers on Mar.

27, 1962 and 3,025,345, entitled "Circuit Arrangement For Automatic

Readjustment Of The Background Brightness And The Contrast In A

Television Receiver," issued to R. Suhrmann on Mar. 13, 1962.Apparatus is also known for automatically controlling the contrast and saturation properties of a color television receiver by controlling the gains of luminance and chrominance channel amplifiers, respectively, in response to ambient light. Such apparatus is described in U.S. Pat. Nos. 3,813,686 entitled "Ambient Light Responsive Control Of Brightness, Contrast And Color Saturation," issued to Eugene Peter Mierzwinski, on May 28, 1974 and 3,814,852 entitled "Ambient Light Responsive Control Of Brightness, Contrast and Color Saturation," issued to Eugene P. Mierzwinski on June 4, 1974.

Also of interest is apparatus for manually controlling the gains of luminance and chrominance channel amplifiers. Such apparatus is described in U.S. Pat. Nos. 3,374,310, entitled "Color Television Receiver with Simultaneous Brightness and Color Saturation Controls," issued to G.L. Beers on Mar. 19, 1968; 3,467,770, entitled "Dual Channel Automatic Control Circuit," issued to DuMonte O. Voigt on June 7, 1966; and 3,715,463, entitled "Tracking Control Circuits Using a Common Potentiometer," issued to Lester Tucker Matzek, on Feb. 6, 1973.

When

the gain of luminance channel is adjusted to control the contrast of

an image, either manually or automatically, in response to ambient

light, it is desirable to simultaneously control the gain of the

chrominance channel in such a manner that the ratio of the gains of the

luminance and chrominance channels is substantially constant over a

wide range of contrast control to maintain constant saturation. If the

proper ratio between the amplitudes of the chrominance and luminance

signals is not maintained incorrect color reproduction may result. For

instance, if the amplitude of the luminance signals are increased

without correspondingly increasing the amplitude of the chrominance

signals, colors may become desaturated, i.e., they will appear washed

out or pastel in shade. Furthermore, it may be desirable to provide

controls for presetting the gains of the luminance and chrominance

channels to compensate for tolerance variations in other portions of the

television signal processing apparatus.

When

the gain of luminance channel is adjusted to control the contrast of

an image, either manually or automatically, in response to ambient

light, it is desirable to simultaneously control the gain of the

chrominance channel in such a manner that the ratio of the gains of the

luminance and chrominance channels is substantially constant over a

wide range of contrast control to maintain constant saturation. If the

proper ratio between the amplitudes of the chrominance and luminance

signals is not maintained incorrect color reproduction may result. For

instance, if the amplitude of the luminance signals are increased

without correspondingly increasing the amplitude of the chrominance

signals, colors may become desaturated, i.e., they will appear washed

out or pastel in shade. Furthermore, it may be desirable to provide

controls for presetting the gains of the luminance and chrominance

channels to compensate for tolerance variations in other portions of the

television signal processing apparatus.In accordance with the present invention, apparatus is provided which may be utilized in a color television receiver to control contrast over a relatively wide range while maintaining constant saturation. The apparatus includes first and second amplifiers having gain versus control voltage characteristics including linear portions extrapolated to cut off at predetermined voltages which may or may not be the same. Means couple a gain controlling voltage source to the first amplifier to control its gain. Potentiometer means are coupled between a source of fixed voltage substantially equal to the extrapolated cut off voltage of the second amplifier and the source of gain controlling voltage to receive a portion of said gain controlling voltage in accordance with the ratio of the extrapolated cut off voltages of the amplifiers. A voltage developed at a predetermined point along the potentiometer means is coupled to the second amplifier to control its gain.

In accordance with another feature of the present invention, the means for coupling said gain controlling voltage to said first amplifier includes another potentiometer coupled between a source of fixed voltage substantially equal to the extrapolated cut off voltage of said first amplifier and said gain controlling voltage source.

In accordance with still another feature of the present invention the gain controlling voltage source includes an element responsive to ambient light .

These and other aspects of the present invention may best be understood by references to the following detailed description and accompanying drawing in which:

FIG. 1 shows the general arrangement, partly in block diagram form and partly in schematic diagram form, of a color television receiver employing an embodiment of the present invention;

FIG. 1A shows, in schematic form, a modification to the embodiment shown in FIG. 1;

FIG. 2 shows graphical representation of gain versus control voltage characteristics of amplifiers utilized in the embodiment shown in FIG. 1;

FIG. 3 shows graphical representations of gain versus control voltage characteristics of amplifiers which may be utilized in the receiver shown in FIG. 1;

FIG. 4 shows, in schematic form, another embodiment of the present invention which may be utilized to control the amplifiers whose gain versus control voltage characteristics are shown in FIG. 3;

FIG. 5 shows, in schematic form, an amplifier which may be utilized in the receiver shown in FIG. 1; and

FIG. 6 shows, in schematic form, another amplifier which may be utilized in the receiver shown in FIG. 1.

Referring now

to

FIG. 1, the general arrangement of a color television receiver

employing the present invention includes a video signal processing unit

112 responsive to radio frequency (RF) television signals for

generating, by means of suitable intermediate frequency (IF) circuits

(not shown) and detection circuits (not shown), a composite video signal

comprising chrominance, luminance, sound and synchronizing signals.

The output of signal processing unit 112 is coupled to chrominance

channel 114, luminance channel 116, a channel 118 for processing the

synchronizing signals and a channel (not shown) for processing sound

signals.

to

FIG. 1, the general arrangement of a color television receiver

employing the present invention includes a video signal processing unit

112 responsive to radio frequency (RF) television signals for

generating, by means of suitable intermediate frequency (IF) circuits

(not shown) and detection circuits (not shown), a composite video signal

comprising chrominance, luminance, sound and synchronizing signals.

The output of signal processing unit 112 is coupled to chrominance

channel 114, luminance channel 116, a channel 118 for processing the

synchronizing signals and a channel (not shown) for processing sound

signals. Chrominance

processing channel 114 includes chrominance processing unit 120 which

serves to remove chrominance signals from the composite video signal

and otherwise process chrominance signals. Chrominance signal

processing unit 120 may include, for example, automatic color control

(ACC) circuits for adjusting the amplitude of the chrominance channels

in response to amplitude variations of a reference signals, such as a

color burst signal, included in the commposite video signal.

Chrominance signal processing circuits of the type described in the

U.S. Pat. No. 3,740,462, entitled "Automatic Chroma Gain Control

System," issued to L.A. Harwood, on June 19, 1973 and assigned to the

same assignee as the present invention are suitable for use as

chrominance processing unit 120.

Chrominance

processing channel 114 includes chrominance processing unit 120 which

serves to remove chrominance signals from the composite video signal

and otherwise process chrominance signals. Chrominance signal

processing unit 120 may include, for example, automatic color control

(ACC) circuits for adjusting the amplitude of the chrominance channels

in response to amplitude variations of a reference signals, such as a

color burst signal, included in the commposite video signal.

Chrominance signal processing circuits of the type described in the

U.S. Pat. No. 3,740,462, entitled "Automatic Chroma Gain Control

System," issued to L.A. Harwood, on June 19, 1973 and assigned to the

same assignee as the present invention are suitable for use as

chrominance processing unit 120.The output of the chrominance signal processing unit 120 is coupled to chrominance amplifier 122 which serves to amplify chrominance signals in response to a DC signal vC generated by gain control network 142. As illustrated, chrominance amplifier 122 provides chrominance signals to a chroma demodulator 124. An amplifier suitable for use as chrominance amplifier 122 will subsequently be described with reference to FIG. 6.

Chroma demodulator 124 derives color difference signals representing, for example, R-Y, B-Y and G-Y information from the chrominance signals. Demodulator circuits of the general type illustrated by the chrominance amplifier CA 3067 integrated circuit manufactured by RCA Corporation are suitable for use as chrominance demodulator 124.

The color difference signals are applied to a video driver 126 where they are combined with the output signals -Y of luminance channel 116 to produce color signals of the appropriate polarity, representing for example, red (R), green (G) and blue (B) information. The color signals are coupled to kinescope 128.

Luminance channel 116 includes a first luminance signal processing unit 129 which relatively attenuates undesirable signals, such as chrominance or sound signals or both, present in luminance channel 116 and otherwise processes the luminance signals. The output of first luminance processing unit 129 is coupled to luminance amplifier 130 which serves to amplify the luminance signals in response to a DC control signal vL generated by gain control unit 142 to thereby determine the contrast of a reproduced image. An amplifier suitable for use as luminance amplifier 130 will subsequently be described with reference to FIG. 5. The output of luminance amplifier 130 is coupled to second luminance signal processing unit 132 which serves to further process luminance signals. A brightness control unit 131 is coupled to luminance signal processing unit 132 to control the DC content of the luminance signals. The output -Y of luminance processing unit 132 is coupled to kinescope driver 126.

Channel 118 includes a sync separator 134

which separates horizontal and vertical synchronizing pulses from the

composite video signal. The synchronizing pulses are coupled to

horizontal deflection circuit 136 and vertical deflection circuit 138.

Horizontal deflection circuit 136 and vertical deflection circuit 138

are coupled to kinescope 128 and to a high voltage unit 140 to

control the generation and deflection of one or more electron beams

generated by kinescope 128 in the conventional manner. Deflection

circuits 136 and 138 also generate horizontal and vertical blanking

signals which are coupled to luminance signal processing unit 132 to

inhibit its operation during the horizontal and vertical retrace

intervals.

Channel 118 includes a sync separator 134

which separates horizontal and vertical synchronizing pulses from the

composite video signal. The synchronizing pulses are coupled to

horizontal deflection circuit 136 and vertical deflection circuit 138.

Horizontal deflection circuit 136 and vertical deflection circuit 138

are coupled to kinescope 128 and to a high voltage unit 140 to

control the generation and deflection of one or more electron beams

generated by kinescope 128 in the conventional manner. Deflection

circuits 136 and 138 also generate horizontal and vertical blanking

signals which are coupled to luminance signal processing unit 132 to

inhibit its operation during the horizontal and vertical retrace

intervals.Gain control unit 142 is coupled to luminance amplifier 130 and to chrominance amplifier 122 to control their gains. Gain control unit 142 includes a PN

P transistor 152 arranged as an

emitter-follower amplifier. The collector of transistor 152 is coupled

to ground while its emitter is coupled through a series connection of

a potentiometer 156 and fixed resistor 154 to a source of positive

supply voltage VO. The wiper of potentiometer 156 is

coupled to luminance amplifier 130. The series connection of a

potentiometer 158 and a variable resistor 159 is coupled between the

source of positive supply voltage VO and the emitter of transistor 152. The wiper of potentiometer 158 is coupled to chrominance amplifier 122.

P transistor 152 arranged as an

emitter-follower amplifier. The collector of transistor 152 is coupled

to ground while its emitter is coupled through a series connection of

a potentiometer 156 and fixed resistor 154 to a source of positive

supply voltage VO. The wiper of potentiometer 156 is

coupled to luminance amplifier 130. The series connection of a

potentiometer 158 and a variable resistor 159 is coupled between the

source of positive supply voltage VO and the emitter of transistor 152. The wiper of potentiometer 158 is coupled to chrominance amplifier 122.The base of transistor 152 is coupled to the wiper of a potentiometer 146. One end of potentiometer 146 is coupled to the source of positive supply voltage VO through a fixed resistor 144. The other end of potentionmeter 146 is coupled to ground through a light dependent resistor (LDR) 148. LDR 148 is a resistance element whose impedance varies in inverse relationship with light which impinges on it. LDR 148 may comprise a simple cadmium sulfide type of light dependent element or other suitable light dependent device. LDR 148 is desirably mounted to receive ambient light in the vicinity of the screen of kinescope 128.

A single pole double-throw switch 150 has a pole coupled to the junction of potentiometer 146 and LDR 148. A resistor 151 is coupled between the wiper of potentiometer 146 and the other pole of switch 150. The arm of switch 150 is coupled to ground.

The general arrangement shown in FIG. 1 is suitable for use in a color television receiver of the type shown, for example, in RCA Color Television Service Data 1973 No. C -8 for a CTC-68 type receiver, published by RCA Corporation, Indianapolis, Indiana.

In

operation, gain control circuit 142 maintains the ratio of the gain

of chrominance amplifier 122 to the gain of amplifier 130 constant in

order to maintain constant saturation while providing for contrast

adjustment either manually by means of potentiometer 146 or

automatically by means of LDR 148. If the gain of luminance were

adjusted to control the contrast of an image without a corresponding

change in the gain of chrominance amplifier 122, the amplitudes of

luminance signals -Y and color difference signals R-Y, B-Y and G-Y would not, in general, be in the correct ratio when combined by

divider 126 to provide the desired color.

In

operation, gain control circuit 142 maintains the ratio of the gain

of chrominance amplifier 122 to the gain of amplifier 130 constant in

order to maintain constant saturation while providing for contrast

adjustment either manually by means of potentiometer 146 or

automatically by means of LDR 148. If the gain of luminance were

adjusted to control the contrast of an image without a corresponding

change in the gain of chrominance amplifier 122, the amplitudes of

luminance signals -Y and color difference signals R-Y, B-Y and G-Y would not, in general, be in the correct ratio when combined by

divider 126 to provide the desired color.When switch 140 is in the MANUAL position, the gains of chrominance amplifier 122 and luminance amplifier 130 are controlled by adjustment of the position of potentiometer 146. When switch 150 is in the AUTO position the gain of the chrominance amplifier 122 and luminance amplifier is automatically controlled by the response of LDR 148 to ambient light conditions. The voltage developed at the wiper of potentiometer 146 (base of transistor 152) when switch 150 is in the AUTO position is inversely related to the ambient light recieved by LDR 148. It is noted that the values of resistors 114, potentiometer 146, LDR 148 and resistor 151 are desirably selected such that the adjustment of the wiper arm of potentiometer 146 when switch 150 is in the MANUAL position does not substantially affect the voltage developed at the base of transister 152 when switch 150 is placed in the AUTO position.

The control voltage v developed at the wiper arm of potentiometer 146 is coupled through emitter-follower transistor 152 to the common junction of potentiometer 156 and variable resistor 159. A control voltage vL comprising v plus a predetermined portion of the difference VO -v developed across the series connection of fixed resistor 154 and potentiometer 156, depending on the setting of potentiometer 156, is coupled to luminance amplifier 130 to control its gain. Similarly, a control voltage vC comprising v plus a predetermined portion of the difference voltage VO -v developed across the series connection of potentiometer resistor 158 and variable resistor 159, depending on the setting of the wiper of potentiometer 158, is coupled to chrominance amplifier 122 to control its gain.

The gain of luminance amplifier 130 may be pre-set to a desired value by the factory adjustment of potentiometer 156. Similarly, variable resistor 159 is provided to allow factory pre-set of the gain of the chrominance amplifier 122. Potentiometer 158 is provided to allow customer control of saturation.

R

eferring to FIG. 2, the gain versus voltage characteristics of chroma amplifier 122 (gC) and luminance amplifier 130 (gL) are shown. The characteristic gC has a reversed S-shape including a linear portion 214. Extrapolated linear portion 214 of gC intersects the GAIN axis at GC and intersects the CONTROL VOLTAGE axis at VO. Similarly, the characteristics gL has a reverse S-shape characteristic including a linear portion 212. Extrapolated linear portion 214 of gL intersects the GAIN axis at GL and intersects the CONTROL VOLTAGE axis at VO.

eferring to FIG. 2, the gain versus voltage characteristics of chroma amplifier 122 (gC) and luminance amplifier 130 (gL) are shown. The characteristic gC has a reversed S-shape including a linear portion 214. Extrapolated linear portion 214 of gC intersects the GAIN axis at GC and intersects the CONTROL VOLTAGE axis at VO. Similarly, the characteristics gL has a reverse S-shape characteristic including a linear portion 212. Extrapolated linear portion 214 of gL intersects the GAIN axis at GL and intersects the CONTROL VOLTAGE axis at VO.From FIG. 2, the expression for linear portion 212 of gL is ##EQU1## The expression for linear portion 214 of gC is ##EQU2## From FIG. 1, the expression for vL is vL = v + (VO -v) K1 [3]

where K1 is determined by the voltage division of fixed resistor 154 and potentiometer 156 at the wiper of potentiometer 156. When the wiper of potentiometer 156 is at the emitter of transistor 152, K1 =0. The expression for vC is vC = v + (VO -v)K2 [4]

where K2 is determined by the voltage division of potentiometer 158 and fixed resistor 159 at the wiper of potentiometer 158. By combining equations [1] and [3], the equation for gL becomes ##EQU3## By combining equations [2] and [4], the equation for gC becomes ##EQU4## The ratio of gL to gC is thus ##EQU5## It is noted that this ratio is independent of DC control voltage v. Thus, although DC control voltage v may be varied either manually or in response to ambient light to control the contrast of an image reproduced by kinescope 128, the saturation remains constant.

With re

ference to FIG. 2, it is noted that although the linear portion 214 of gC has an extrapolated gain equal to 0 at a control voltage equal to VO, the non-linear portion of gC does not attain a gain equal to 0 until a control voltage equal to VB. That is, a control voltage of VO will not cut-off chrominance amplifier 122.

ference to FIG. 2, it is noted that although the linear portion 214 of gC has an extrapolated gain equal to 0 at a control voltage equal to VO, the non-linear portion of gC does not attain a gain equal to 0 until a control voltage equal to VB. That is, a control voltage of VO will not cut-off chrominance amplifier 122.In FIG. 1A there is shown, in schematic form, a modification to the arrangement of gain control network 142 of FIG. 1 with provisions which allow a viewer to cut off chrominance amplifier 122 to produce a more pleasing image under conditions of poor color reception due, for example, to noise or interference. The modifications to gain control unit 142 shown in FIG. 1A include coupling potentiometer resistor 158 between a source of positive supply voltage VB, the value of VB being greater than the value of VO, and coupling a resistor 160 from a tap-off point 162 along potentiometer 158 to ground. The value of potentiometer 158 and resistor 160 and the location of tap 162 are selected so that voltage VO is developed at tap 162.

The arrangement shown in FIG. 1A allows for the adjustment of contrast while constant saturation is maintained and additionally allows a viewer, by adjusting the wiper of potentiometer 158 to voltage VB, to cut off chrominance amplifier 122.

Referring to FIG. 3 there are shown gain versus DC control voltage characteristics of chrominance and luminance amplifiers which do not have the same extrapolated linear cut off control voltage. The gain versus control voltage characteristic gL ' of the luminance amplifier has a reverse S-shape characteristic including a linear portion 312. Extrapolated linear portion 312 of gL ' intersects the GAIN axis at a gain GL ' and intersects the CONTROL VOLTAGE axis at a voltage VO '. The gain versus control voltage characteristic gC ' of the chrominance amplifier has a reverse S-shape characteristic having a linear portion 314. Extrapolated linear portion 314 of gC ' intersects the GAIN axis at a gain GC ' and intersects the CONTROL VOLTAGE axis at a voltage AVO ', where A is a number greater than zero.

From FIG. 3, the expression for linear portion 312 of gL ' is ##EQU6## where vL ' is the DC conrol voltage coupled to the luminance amplifier. The expression for linear portion 314 of gC ' is ##EQU7## where vC ' is the DC control voltage coupled to the chrominance amplifier.

A modified form of the control network 142 of FIG. 1 suitable for controlling the gain of a chrominance and a luminance amplifier having characteristics such as shown in FIG. 3 is shown in FIG. 4. Similar portions of FIGS. 1 and 4 are identified by reference numbers having the same last two significant digits and primed (') designations. The modified portions of FIG. 1 shown in FIG. 4 include the series connection resistors 460 and 462 coupled between the emitter of transistor 452 to ground. The values of resistors 460 and 462 are selected so that a portion Av' of the DC control voltage v' developed at the emitter of transistor 452 is developed at the junction of resistors 460 and 462. Furthermore, the series connection of potentiometer 458 and variable resistor 459 is coupled between the junction of resistor 460 and 462 and a source of positive supply voltage AVO '.

From FIG. 4, the expression for control voltage vL ' developed at the wiper of potentiometer 456 is vL ' = v' + (vO '-v')K1 ' [10]

From FIG. 4, the expression for control voltage vL ' developed at the wiper of potentiometer 456 is vL ' = v' + (vO '-v')K1 ' [10]where K1 ' is determined by the voltage division at the wiper of potentiometer 456. The expression for control voltage vC ' developed at the wiper of potentiometer 458 is VC ' = Av' + (AVO ' - Av')K 2 ' [11]

where K2 ' is determined by the voltage division at the wiper of potentiometer 458. By combining equations [8] and [10], ##EQU8## By combining equations [9] and [11], ##EQU9## The ratio of gL ' to gC ' is given by the expression ##EQU10## It is noted that this ratio is independent of DC control voltage v'. Therefore, gain control network 442 of FIG. 4 also allows for the adjustment of contrast while maintaining constant saturation.

It is noted that if A were made equal to 1, the arrangement gain control unit 442 would be suitable to control the gains of chrominance and luminance amplifiers having the characteristics shown in FIG. 2.

In FIG. 5, there is shown an amplifier suitable for use as luminance amplifier 130 of FIG. 1. The amplifier includes a differential amplifier comprising NPN transistors 532 and 534. The commonly coupled emitters of transistors 532 and 534 are coupled to the collector of an NPN transistor 528. The emitter of transistor 528 is coupled via a resistor 530 to ground. The collector of transistor 532 and the collector of transistor 534, via load resistor 536, is coupled to a bias voltage provided by bias supply 546, illustrated as a series connection of batteries. The bases of transistors 532 and 534 are respectively coupled to a lower bias voltage through resistors 533 and 535 respectively.

An input signal, such as, for example, the output signal provided by first luminance processing circuit 129 of FIG. 1 is coupled to the base of transistor 532 via terminal 542. The output signal of the amplifier is developed at the collector of transistor 534 and coupled to output terminal 544.

A DC control voltage, such as vL

provided by gain control unit 142 of FIG. 1, is coupled to the base

of an NPN transistor 514, arranged as an emitter-follower, via

terminal 512. The collector of transistor 514 is coupled to bias

supply 546. The emitter of transistor 514 is coupled to ground through

the series connection of resistor 516, a diode connected transistor

518 and resistor 520.

A DC control voltage, such as vL

provided by gain control unit 142 of FIG. 1, is coupled to the base

of an NPN transistor 514, arranged as an emitter-follower, via

terminal 512. The collector of transistor 514 is coupled to bias

supply 546. The emitter of transistor 514 is coupled to ground through

the series connection of resistor 516, a diode connected transistor

518 and resistor 520.The anode of diode 520 is coupled to the base of an NPN transistor 538. The collector of transistor 538 is coupled to the collector of transistor 534 while its emitter is coupled to ground through resistor 540. Transistor 538, resistor 540, diode 518 and resistor 520 are arranged in a current mirror configuration.

The emitter of transistor 514 is coupled to the base of a PNP transistor 522. The emitter of transistor 522 is coupled to bias supply 546 while its collector is coupled to the base of transistor 528 and to ground through the series connection of a diode connected transistor 524 and resistor 526. Transistor 528, resistor 530, diode 524 and resistor 526 are arranged in a current mirror configuration

In operation, the DC control voltage coupled to

terminal 512 is coupled in inverted fashion to the anode of diode 524

by transistor 522. As a result, current directly related to the

voltage developed at the anode of diode 524 flows through diode 524

and resistor 526. Due to the operation of the current mirror

arrangement of diode 524, resistor 526, transistor 528 and resistor

530, a similar current flows through the emitter circuit of transistor

528. The gain of the differential amplifier comprising transistors

532 and 534 is directly related to this current flowing in the emitter

circuit of transistor 528, and therefore is inversely related to the

DC control voltage at terminal 512. The gain versus DC control voltage

characteristics of the differential is similar to gL shown in FIG. 2.

In operation, the DC control voltage coupled to

terminal 512 is coupled in inverted fashion to the anode of diode 524

by transistor 522. As a result, current directly related to the

voltage developed at the anode of diode 524 flows through diode 524

and resistor 526. Due to the operation of the current mirror

arrangement of diode 524, resistor 526, transistor 528 and resistor

530, a similar current flows through the emitter circuit of transistor

528. The gain of the differential amplifier comprising transistors

532 and 534 is directly related to this current flowing in the emitter

circuit of transistor 528, and therefore is inversely related to the

DC control voltage at terminal 512. The gain versus DC control voltage

characteristics of the differential is similar to gL shown in FIG. 2.Further, a current is developed through the series connection of resistor 516, diode 518 and resistor 520 in direct relationship to the DC control coupled to terminal 512. A similar current is developed through resistor 540 due to the operation of the current mirror comprising diode 518, resistor 520, transistor 538 and resistor 540. This current is of the opposite sense to that provided by the current mirror arrangement of diode 524, resistor 526, transistor 528 and resistor 530 and is coupled to the collector of transistor 534 so that the DC voltage at output terminal 544 does not substantially vary with the DC control voltage.

In FIG. 6, ther

e

is shown an amplifier suitable for use as chroma amplifier 120 of

FIG. 1. The amplifier shown in FIG. 6 is of the type described in U.S.

patent application Ser. No. 530,405 entitled "Controllable Gain

Signal Amplifier," fled by L.A. Harwood et al. on Dec. 6, 1974.

e

is shown an amplifier suitable for use as chroma amplifier 120 of

FIG. 1. The amplifier shown in FIG. 6 is of the type described in U.S.

patent application Ser. No. 530,405 entitled "Controllable Gain

Signal Amplifier," fled by L.A. Harwood et al. on Dec. 6, 1974.The amplifier comprises a differential amplifier including NPN transistors 624 and 625 having their bases coupled to terminal 603 via a resistor 626. Chrominance signals, provided by a source of chrominance signals such as chrominance processing unit 120 of FIG. 1, are coupled to terminal 603. The current conduction paths between the collectors and emitters of transistors 624 and 625 are respectively coupled to ground via resistors 628, 629 and 630.

A current splitter circuit comprising an NPN transistor 632 and a diode 634 is coupled to the collector of transistor 624. Diode 634 and the base-emitter junction of transistor 632 are poled in the same direction with respect to the flow of collector current in transistor 624. It desirable that conduction characteristics of transistor 632 and diode 635 be substantially matched. Similarly, the collector of transistor 625 is coupled to a second current splitter comprising a transistor 633 and a diode 635.

An output load circuit

comprising series connected resistors 636 and 638 is coupled between

the collector of transistor 632 and a source of operating voltage

provided by bias supply 610. Amplified chrominance signals are

provided at output terminal 640 for coupling, for example, to a chroma

demodulator such as chroma demodulator 124 of FIG. 1. Similarly,

series connected load resistors 637 and 639 are coupled between the

collector of transistor 633 and bias supply 610. An output terminal

641 at the junction of resistors 637 ad 639 provides oppositely phased

chrominance signals to those provided at terminal 640. The gain

associated with the cascode combination of transistors 624 and 632 is

controlled in response to a DC control voltage, such as, for example, vC

provided by gain control unit 142 of FIG. 1, coupled to the base of

an NPN transistor 646 via terminal 602. Direct control current is

supplied from the emitter of transistor 646 to diode 634 and 635 via a

series resistor 652. A signal by-pass circuit comprising a series