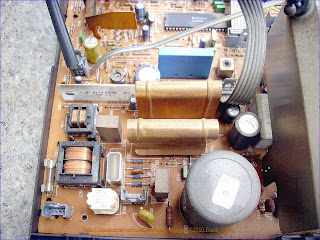

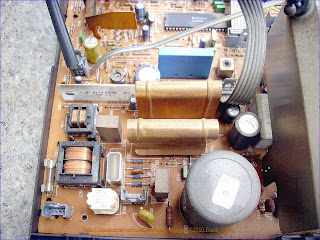

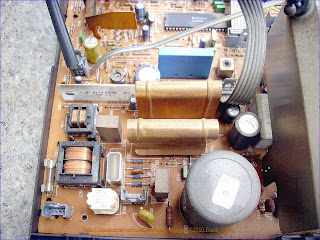

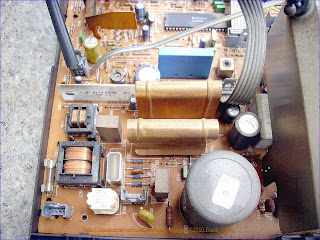

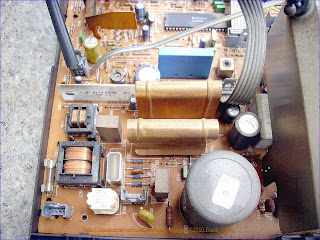

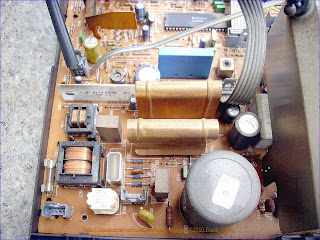

SALORA CHASSIS L is A monocarrier chassis contains all functions of the receiver.

Most important and interesting part is the power supply and line deflection output + EHT part.

It combines power supply and line deflection in one special transformer.

This circuit is called IPSALO (Integrated Power Supply Salora) and is delveloped around a sophisticated hybrid IC SALORA LF0059.

The Salora K and L chassis employ the Ipsalo-3 power supply/line deflection circuit. Its features include the use of a single chopper transistor and yet another hybrid chopper control chip, this time type SALORA LF0059. The chassis themselves are very different in physical appearance, though the circuits are similar. The K is an upright, hinge -back type that's akin to the H and J chassis. It's used in sets fitted with 20, 21, 22, 24, 26 and 28in. tubes - from the sizes you'll note that some are "traditional" while others are FS tubes. The L is a horizontal, slide - out chassis which, in addition to the larger screen sizes, is also used in 14 and 15in. models. Both chassis are found under other guises, such as Hitachi, Granada, Finlandia and Luxor. Many of them are thus used as rental sets.

The Ipsalo-3 Circuit:

Fig.

1 shows the Ipsalo-3 circuit used in the K chassis. We'll provide a

brief run-down on the circuit operation, starting with the action of the

start-up circuit. The mains input is rectified by the bridge rectifier

DB701-4 whose reservoir capacitor is CB707. Surge limiting is provided

by RB702 and filtering by RB703/ CB708. A d.c. supply of some 300V is

thus present across CB708. As with the previous chassis a diac, DTB705

in this circuit, is used to get things going. CB711 charges from the

300V line via RB704, and when the voltage across it reaches

approximately 30V the BR100 diac fires. The pulse produced in this way

at the base of the BU508 chopper transistor TB701 switches it on.

DTB705's conduction rapidly discharges CB711: when the voltage across it

drops to about 22V the diac switches off, removing TB701's base drive.

At this point the current flowing through the primary winding (pins 1-2)

of the Ipsalo transformer MB600 reverses. The voltage developed across

the secondary winding 17-18 brings rectifier diode DB603 into

conduction, charging CB604. Meanwhile CB711 charges again and the cycle

repeats. Thus the voltages across CB604 and CB621/2 gradually build up.

The PHILIPS TDA2579 timebase generator/sync chip ICB500 requires a

switch -on supply at pin 16. During normal operation it's powered by a

12V supply at pin 10. As the voltage across CB621/2 builds up, a point

is reached at which the voltage at pin 16 of ICB500 is sufficient for

the line oscillator to start up. The set will now come into operation.

The line -frequency pulses produced at pin 11 of the PHILIPS TDA2579

chip are fed to the line driver transistor TB502 and to pin 13 of the

hybrid chopper control chip HB600, which now takes over the provision of

drive for the chopper transistor. Once normal operation has been

established, DB706 and RB705 ensure that the voltage across CB711 never

reaches the level at which DTB705 will fire. During normal operation

HB600 provides a pulse - width modulated drive to the chopper transistor

to regulate the supplies derived from the Ipsalo transfor- mer. HB600

also incorporates overload protection cir- cuitry. The LF0059 has twenty

pins and the usual green and white appearance. 'It's driven by 2V peak

-to -peak line -frequency pulses at pin 13. For regulation, the voltage

developed at pin 14 of the Ipsalo transformer by the action of the line

output stage is sensed at either pin 5 (90° tubes) or pin 6 (110°

tubes). If an overload results in the voltage at pins 8 and 16 rising to

9.5V the protection circuit in HB600 operates and the set trips. In the

standby mode the control circuitry increases the voltage at pin 7 of

HB600 from OV to 5V. As a result of the action of the internal circuitry

the chopper is switched on when the negative -going edge of the line

pulse at pin 13 occurs. Thus the chopper and the line output transistors

are on at the same time. The latter continues to conduct until energy

has been drained from the secondary windings of the Ipsalo transformer.

The close -coupled windings 17-18 and 19-20 continue to develop

sufficient voltage however to keep the chopper circuit, the line

oscillator and the remote control circuitry in operation, so that the

set can be brought back from the standby mode. In the K and large

-screen L chassis the e.h.t. is derived from a diode -split winding on

the Ipsalo transformer. With small -screen L chassis sets a tripler is

used. K and L Chassis Compared The Ipsalo-3 circuit is the heart of

these sets and is common to the K and L chassis. There are considerable

variations in the rest of the circuitry however, and several different

control systems are used. We will consider these latter arrangements in a

subsequent instalment, when we give details of the enabling proce-

dures, which again vary with the different versions of these chassis.

The timebase and signal circuits used in the K chassis are fairly

conventional. There's a definite resemblance to the J chassis in fact.

The colour decoder for example is based on the use of a TDA3562A chip

(ICB200), and the notes on this device on pages 103-4 of the December

issue apply here as well. The line and field timebase generators and

sync circuitry are in a PHILIPS TDA2579 chip (ICB500) as previously

mentioned. A PHILIPS TDA3654 (ICB501) is used as the field output

device. A parallel system is used for the vision and sound i.f. signals.

The i.f. bandpass setting SAWF has two outputs, the sound i.f. going to

a PHILIPS TDA2545A chip

Fig.

1 shows the Ipsalo-3 circuit used in the K chassis. We'll provide a

brief run-down on the circuit operation, starting with the action of the

start-up circuit. The mains input is rectified by the bridge rectifier

DB701-4 whose reservoir capacitor is CB707. Surge limiting is provided

by RB702 and filtering by RB703/ CB708. A d.c. supply of some 300V is

thus present across CB708. As with the previous chassis a diac, DTB705

in this circuit, is used to get things going. CB711 charges from the

300V line via RB704, and when the voltage across it reaches

approximately 30V the BR100 diac fires. The pulse produced in this way

at the base of the BU508 chopper transistor TB701 switches it on.

DTB705's conduction rapidly discharges CB711: when the voltage across it

drops to about 22V the diac switches off, removing TB701's base drive.

At this point the current flowing through the primary winding (pins 1-2)

of the Ipsalo transformer MB600 reverses. The voltage developed across

the secondary winding 17-18 brings rectifier diode DB603 into

conduction, charging CB604. Meanwhile CB711 charges again and the cycle

repeats. Thus the voltages across CB604 and CB621/2 gradually build up.

The PHILIPS TDA2579 timebase generator/sync chip ICB500 requires a

switch -on supply at pin 16. During normal operation it's powered by a

12V supply at pin 10. As the voltage across CB621/2 builds up, a point

is reached at which the voltage at pin 16 of ICB500 is sufficient for

the line oscillator to start up. The set will now come into operation.

The line -frequency pulses produced at pin 11 of the PHILIPS TDA2579

chip are fed to the line driver transistor TB502 and to pin 13 of the

hybrid chopper control chip HB600, which now takes over the provision of

drive for the chopper transistor. Once normal operation has been

established, DB706 and RB705 ensure that the voltage across CB711 never

reaches the level at which DTB705 will fire. During normal operation

HB600 provides a pulse - width modulated drive to the chopper transistor

to regulate the supplies derived from the Ipsalo transfor- mer. HB600

also incorporates overload protection cir- cuitry. The LF0059 has twenty

pins and the usual green and white appearance. 'It's driven by 2V peak

-to -peak line -frequency pulses at pin 13. For regulation, the voltage

developed at pin 14 of the Ipsalo transformer by the action of the line

output stage is sensed at either pin 5 (90° tubes) or pin 6 (110°

tubes). If an overload results in the voltage at pins 8 and 16 rising to

9.5V the protection circuit in HB600 operates and the set trips. In the

standby mode the control circuitry increases the voltage at pin 7 of

HB600 from OV to 5V. As a result of the action of the internal circuitry

the chopper is switched on when the negative -going edge of the line

pulse at pin 13 occurs. Thus the chopper and the line output transistors

are on at the same time. The latter continues to conduct until energy

has been drained from the secondary windings of the Ipsalo transformer.

The close -coupled windings 17-18 and 19-20 continue to develop

sufficient voltage however to keep the chopper circuit, the line

oscillator and the remote control circuitry in operation, so that the

set can be brought back from the standby mode. In the K and large

-screen L chassis the e.h.t. is derived from a diode -split winding on

the Ipsalo transformer. With small -screen L chassis sets a tripler is

used. K and L Chassis Compared The Ipsalo-3 circuit is the heart of

these sets and is common to the K and L chassis. There are considerable

variations in the rest of the circuitry however, and several different

control systems are used. We will consider these latter arrangements in a

subsequent instalment, when we give details of the enabling proce-

dures, which again vary with the different versions of these chassis.

The timebase and signal circuits used in the K chassis are fairly

conventional. There's a definite resemblance to the J chassis in fact.

The colour decoder for example is based on the use of a TDA3562A chip

(ICB200), and the notes on this device on pages 103-4 of the December

issue apply here as well. The line and field timebase generators and

sync circuitry are in a PHILIPS TDA2579 chip (ICB500) as previously

mentioned. A PHILIPS TDA3654 (ICB501) is used as the field output

device. A parallel system is used for the vision and sound i.f. signals.

The i.f. bandpass setting SAWF has two outputs, the sound i.f. going to

a PHILIPS TDA2545A chip while the vision i.f. output goes to a

PHILIPS TDA2549. There are several options available as plug-in PCBs

with this chassis. Thus there appear to be several unused connectors and

you may find yourself going in all directions if you try tracing the

print connections. The options include teletext, a stereo sound decoder,

a satellite TV decoder, SECAM and NTSC decoders and an f.m. tuner for

radio reception. A pair of TDA2030 chips (ICE1/2) is used in sets with

stereo sound facilities, with processing (tone and balance control etc.)

carried out within a PHILIPS TDA1524A chip (ICE3). Non -stereo

versions have a single TDA2030. The 6MHz f.m. output from the previously

mentioned PHILIPS TDA2545A sound i.f. chip is fed to a TBA120T

intercarrier sound chip on the audio module. The arrangements used in

the L chassis are somewhat simpler. This is mainly due to the use of a

TDA4505 chip that includes the i.f. signal processing and also incorpo-

rates the sync circuits and timebase generators. The colour decoder is a

MOTOROLA TDA3301. Once again a PHILIPS TDA3654 is used for field

deflection.

while the vision i.f. output goes to a

PHILIPS TDA2549. There are several options available as plug-in PCBs

with this chassis. Thus there appear to be several unused connectors and

you may find yourself going in all directions if you try tracing the

print connections. The options include teletext, a stereo sound decoder,

a satellite TV decoder, SECAM and NTSC decoders and an f.m. tuner for

radio reception. A pair of TDA2030 chips (ICE1/2) is used in sets with

stereo sound facilities, with processing (tone and balance control etc.)

carried out within a PHILIPS TDA1524A chip (ICE3). Non -stereo

versions have a single TDA2030. The 6MHz f.m. output from the previously

mentioned PHILIPS TDA2545A sound i.f. chip is fed to a TBA120T

intercarrier sound chip on the audio module. The arrangements used in

the L chassis are somewhat simpler. This is mainly due to the use of a

TDA4505 chip that includes the i.f. signal processing and also incorpo-

rates the sync circuits and timebase generators. The colour decoder is a

MOTOROLA TDA3301. Once again a PHILIPS TDA3654 is used for field

deflection.Basic K Chassis Faults List:

To round off this initial instalment on these chassis, here's a brief faults list covering common problems with the basic K chassis. Faults relevant to the Ipsalo-3 circuit also apply to the L chassis (but note that the circuit reference numbers differ with the small -screen version). (1) No go. On several occasions we've found the chopper transistor TB701 to be short-circuit and the filter resistor RB703 open -circuit. DB707, which is in parallel with TB701, is usually also short-circuit. (2) Set does not start initially but if left switched on will start after a time ranging from half a minute to several minutes. You will usually find that the 1,000µF 8.5V supply reservoir capacitor CB604 is open -circuit or leaky. We try to fit a replacement rated at 25V if the physical size permits in a particular set. CB601 which is in parallel with CB604 can also cause this problem. Several different values have been used in this position. We find that the higher value 1/LF improves starting and cures any problems here. It's not unusual to have to replace both these capacitors for a no start condition. (3) No sound, no picture but two bars present on the display. Monitor pin 11 of the PHILIPS TDA2579 timebase chip ICB500. You will find that line -frequency pulses begin to appear then, shortly after switch -on, stop. The cause is that the BC557 transistor TB541 in the switch -on line is short-circuit. (4) Noise and "splashes" on the picture. Suspect CB101 (22nF) which decouples pin 4 (tuning voltage) of the tuner unit. (5) Height and/or width twitch up/down or in/out. First check whether the height control RTB543 and/or the line phase control RTB542 is noisy. Usually however the SALORA LF0059 chopper control chip HB600 is faulty. You may, if you don't hold this device in stock, be able to monitor its output with a scope: usually however the fault is not regular enough for this. (6) No sound or vision. On several occasions the PHILIPS TDA2579 chip ICB500 has been faulty. This chip can also sometimes load down the 12V rail with the result that the set trips. (7) Intermittent no picture or sound with the channel display pulsing. This can occur with sets that incorporate teletext. Remove the teletext panel to confirm that the fault has cleared. If so the fault is due to misoperation of the crystal oscillator on this panel. Replace all associated components - the crystal, transistor, capacitors, etc. Then recheck. If the fault is still present suspect the ITT DPU2540 chip.

The video section is developed with Motorola TDA3301 TV COLOR PROCESSOR

I.F. and synchronization with TDA4505E Small Signal combination IC for colour TV

Control and tuning search functions are developed around the ITT SAA1293 Tuning Voltage Processor for Analog TV-Set.

SALORA 17L61 CHASSIS L - VIDEO CHROMA PROCESSING WITH TDA3300 (MOTOROLA)

SALORA 17L61 CHASSIS L - VIDEO CHROMA PROCESSING WITH TDA3300 (MOTOROLA)TDA3300 3301 TV COLOR PROCESSOR

The Decoder IC The centre -piece of the decoder is the Motorola TDA3300B i.c. which carries out all the luminance and U V Inputs from PAL delay line 9V Frequency nlyv Z 2RV2 100k chroma signal processing required. Features of this 40 -pin chip include: (1) Automatic black -current control via feedback from the RGB output circuits. (2) Peak beam current limiting to prevent blooming on highlights - in addition to the normal beam current limit- ing action. (3) Separate R, G and B input pins for the injection of teletext/data signals (or on -screen display of the channel number with frequency synthesis tuning). These signals can be varied by means of the user brightness and con- trast controls. (4) Low dissipation - about 600mW. (5) By adding a small adaptor panel with a TDA3030A SECAM-to-PAL converter i.c. during production the receiver is given multistandard (PAL, SECAM and NTSC-4.43) capability.

A block diagram of the TDA3300B i.c. is shown in Fig. 3. As with the better known TDA3560 single -chip decoder, both the chroma and the burst pass through the chroma delay line. The U output from this enters the TDA3300B at pin 8, passing to the U detector and to the burst detector. The latter is part of a phase -locked loop, the detector's output being applied via an H/2 (half-line frequency) switch to the 4.43MHz voltage -controlled crystal oscillator. The 4.43MHz reference oscillator's output is applied for PAL switching, and to the U detector via a voltage -controlled 90° phase shifter. This shifter is under the control of the 90° detec- tor which compares its output with the oscillator's output coming via the PAL switch: when the phase shift is cor- rect, the output from the 90° phase detector is zero. The combined effect of the two H/2 switches in the reference oscillator control loop - the two shown on the right-hand side - cancels phase detector offsets. The outputs from the U and V detectors include burst "flag" pulses which are used for a.c.c., ident and colour -killing - there are two colour -killing actions. RGB Output Stages The RGB output stages are of the class AB type and incorporate extra circuitry for c.r.t. black -current sampl- ing and beam limiting. Fig. 4 shows the red output stage. Under most conditions transistor 2TR1 acts as a class A amplifier, driving the tube's cathode via 2D5 and 2TR7. A high -value collector load resistor (2R33) is used to reduce the dissipation in 2TR1. The stage gain is set by the ratio of 2R40 and 2R36 to 2R25 and 2RV3, the latter setting the drive level. For good transient response it's necessary for the tube/base capacitance to be rapidly charged/discharged in accordance with the signal swings. There is no problem when 2TR1 is being driven from off to on, since the capacitance is discharged rapidly via 2D5 and 2TR1. When 2TR1 is driven from on to off however 2D5 will become reverse biased. Under these conditions 2TR4 acts as an emitter -follower so that the capacitance charges rapidly. Black -level stability is critical for good results. As we've 2R46 5k6 2R51 120k 2TR7 BF493S 2C43l Sampling circuit L -J 1k5 Field blanking J Red cathode _Tube input T"and base 810capacitance nlrr Reference Line pedestal blanking Sample -and - hold amplifier-ws switched on rt- Video Urn seen, the TDA3300B chip incorporates circuitry for automatic black -current correction. Making use of this reduces service calls and ensures constant performance despite tube ageing or circuit misadjustment. Feedback is required, and this is provided by the sampling circuit shown in the box with the broken outline. Transistor 2TR7 acts as an emitter -follower between the video output stage and the c.r.t.'s cathode. It's a low leakage type, the components 2C40, 2D10 and 2C43 ensuring that the circuit has negligible effect on the video signal. Since the beam current flows via 2R51, a voltage proportional to the beam current is produced across this resistor. It's fed into the TDA3300B at pin 22. Black -current Control For automatic black -current control the important thing is the small beam current that flows when the tube is biased just above cut off. To enable this current to be sampled, the TDA3300B replaces the video signal with a fixed reference pedestal voltage for a couple of lines at the end of each field blanking period (this pedestal can be seen as a grey line at the top of the picture if the height control's setting is reduced). The sample voltage at pin 22 of the i.c. is fed to one input of a sample -and -hold amp- lifier which is switched on to sample the input for one line only of the reference pedestal period. 2C33 acts as the black -current control reservoir capacitor, holding the charge acquired during the sampling time for the whole field period. This charge is added to the video signal within the i.c., thus maintaining the correct red gun black current. It's interesting to notice that when a set is switched on from cold there's a momentary screen bright -up with flyback lines as the beam current begins to flow. This is because it takes several fields for 2C33 (and the corre- sponding capacitors in the green and blue channels) to charge fully. Since the voltage continuously available across 2R51 is proportional to beam current, it's used within the i.c. for peak beam current limiting during the active line periods. This is in addition to beam current limiting via the con- trast control - and a crowbar trip that operates should the beam current exceed 3mA.

A block diagram of the TDA3300B i.c. is shown in Fig. 3. As with the better known TDA3560 single -chip decoder, both the chroma and the burst pass through the chroma delay line. The U output from this enters the TDA3300B at pin 8, passing to the U detector and to the burst detector. The latter is part of a phase -locked loop, the detector's output being applied via an H/2 (half-line frequency) switch to the 4.43MHz voltage -controlled crystal oscillator. The 4.43MHz reference oscillator's output is applied for PAL switching, and to the U detector via a voltage -controlled 90° phase shifter. This shifter is under the control of the 90° detec- tor which compares its output with the oscillator's output coming via the PAL switch: when the phase shift is cor- rect, the output from the 90° phase detector is zero. The combined effect of the two H/2 switches in the reference oscillator control loop - the two shown on the right-hand side - cancels phase detector offsets. The outputs from the U and V detectors include burst "flag" pulses which are used for a.c.c., ident and colour -killing - there are two colour -killing actions. RGB Output Stages The RGB output stages are of the class AB type and incorporate extra circuitry for c.r.t. black -current sampl- ing and beam limiting. Fig. 4 shows the red output stage. Under most conditions transistor 2TR1 acts as a class A amplifier, driving the tube's cathode via 2D5 and 2TR7. A high -value collector load resistor (2R33) is used to reduce the dissipation in 2TR1. The stage gain is set by the ratio of 2R40 and 2R36 to 2R25 and 2RV3, the latter setting the drive level. For good transient response it's necessary for the tube/base capacitance to be rapidly charged/discharged in accordance with the signal swings. There is no problem when 2TR1 is being driven from off to on, since the capacitance is discharged rapidly via 2D5 and 2TR1. When 2TR1 is driven from on to off however 2D5 will become reverse biased. Under these conditions 2TR4 acts as an emitter -follower so that the capacitance charges rapidly. Black -level stability is critical for good results. As we've 2R46 5k6 2R51 120k 2TR7 BF493S 2C43l Sampling circuit L -J 1k5 Field blanking J Red cathode _Tube input T"and base 810capacitance nlrr Reference Line pedestal blanking Sample -and - hold amplifier-ws switched on rt- Video Urn seen, the TDA3300B chip incorporates circuitry for automatic black -current correction. Making use of this reduces service calls and ensures constant performance despite tube ageing or circuit misadjustment. Feedback is required, and this is provided by the sampling circuit shown in the box with the broken outline. Transistor 2TR7 acts as an emitter -follower between the video output stage and the c.r.t.'s cathode. It's a low leakage type, the components 2C40, 2D10 and 2C43 ensuring that the circuit has negligible effect on the video signal. Since the beam current flows via 2R51, a voltage proportional to the beam current is produced across this resistor. It's fed into the TDA3300B at pin 22. Black -current Control For automatic black -current control the important thing is the small beam current that flows when the tube is biased just above cut off. To enable this current to be sampled, the TDA3300B replaces the video signal with a fixed reference pedestal voltage for a couple of lines at the end of each field blanking period (this pedestal can be seen as a grey line at the top of the picture if the height control's setting is reduced). The sample voltage at pin 22 of the i.c. is fed to one input of a sample -and -hold amp- lifier which is switched on to sample the input for one line only of the reference pedestal period. 2C33 acts as the black -current control reservoir capacitor, holding the charge acquired during the sampling time for the whole field period. This charge is added to the video signal within the i.c., thus maintaining the correct red gun black current. It's interesting to notice that when a set is switched on from cold there's a momentary screen bright -up with flyback lines as the beam current begins to flow. This is because it takes several fields for 2C33 (and the corre- sponding capacitors in the green and blue channels) to charge fully. Since the voltage continuously available across 2R51 is proportional to beam current, it's used within the i.c. for peak beam current limiting during the active line periods. This is in addition to beam current limiting via the con- trast control - and a crowbar trip that operates should the beam current exceed 3mA.This device will accept a PAL or NTSC composite video signal and output the

three color signals, needing only a simple driver amplifier to interface to the pic-

ture tube. The provision of high bandwidth on-screen display inputs makes it

suitable for text display, TV games, cameras, etc. The TDA3301 B has user con»

trol laws, and also a phase shift control which operates in PAL, as well as NTSC.

0 Automatic Black Level Setup

0 Beam Current Limiting

0 Uses Inexpensive 4.43 MHZ to 3.58 MHz Crystal

0 No Oscillator Adjustment Required

0 Three OSD Inputs Plus Fast Blanking Input

0 Four DC, High Impedance User Controls

0 lnterlaces with TDA33030B SECAM Adaptor

0 Single 12 V Supply

0 Low Dissipation, Typically 600 mW

The brilliance control operates by adding a pedestal to the output

signals. The amplitude of the pedestal is controlled by Pin 30.

During CRT beam current sampling a standard pedestal is

substituted, its value being equivalent tothe value given by V30 Nom

Brightness at black level with V30 Nom is given by the sum of three gun

currents at the sampling level, i.e. 3x20 |.1A with 100 k reference

resistors on Pins 16, 19, and 22.

During picture blanking the brilliance pedestal is zero; therefore, the

output voltage during blanking is always the minimum brilliance black

level (Note: Signal channels are also gain blanked).

Chrominance Decoder

The chrominance decoder section of the TDA3301 B

consists of the following blocks:

consists of the following blocks:Phase-locked reference oscillator;

Phase-locked 90 degree servo loop;

U and V axis decoders

ACC detector and identification detector; .

Identification circuits and PAL bistable; .

Color difference filters and matrixes with fast blanking

Circuits.

The major design considerations apart from optimum

performance were:

o A minimum number of factory adjustments,

o A minimum number of external components,

0 Compatibility with SECAM adapter TDA3030B,

0 Low dissipation,

0 Use of a standard 4.433618 Mhz crystal rather

than a 2.0 fc crystal with a divider.

The crystal VCO is of the phase shift variety in which the

frequency is controlled by varying the phase of the feedback.

A great deal of care was taken to ensure that the oscillator loop

gain and the crystal loading impedance were held constant in

order to ensure that the circuit functions well with low grade

crystal (crystals having high magnitude spurious responses

can cause bad phase jitter). lt is also necessary to ensure that

the gain at third harmonic is low enough to ensure absence of

oscillation at this frequency.

It can be seen that the

It can be seen that thenecessary 1 45°C phase shift is obtained by variable addition

ol two currents I1 and I2 which are then fed into the load

resistance of the crystal tuned circuit R1. Feedback is taken

from the crystal load capacitance which gives a voltage of VF

lagging the crystal current by 90°.

The RC network in the T1 collector causes I1 to lag the

collector current of T1 by 45°.

For SECAM operation, the currents I1 and I2 are added

together in a fixed ratio giving a frequency close to nominal.

When decoding PAL there are two departures from normal

chroma reference regeneration practice:

a) The loop is locked to the burst entering from the PAL

delay line matrix U channel and hence there is no

alternating component. A small improvement in signal

noise ratio is gained but more important is that the loop

filter is not compromised by the 7.8 kHz component

normally required at this point for PAL identification

b) The H/2 switching of the oscillator phase is carried out

before the phase detector. This implies any error signal

from the phase detector is a signal at 7.8 kHz and not dc.

A commutator at the phase detector output also driven

from the PAL bistable coverts this ac signal to a dc prior

to the loop filter. The purpose ot this is that constant

offsets in the phase detector are converted by the

commutator to a signal at 7.8 kHz which is integrated to

zero and does not give a phase error.

When used for decoding NTSC the bistable is inhibited, and

slightly less accurate phasing is achieved; however, as a hue

control is used on NTSC this cannot be considered to be a

serious disadvantage.

90° Reference Generation

To generate the U axis reference a variable all-pass network

is utilized in a servo loop. The output of the all-pass network

is utilized in a servo loop. The output of the all-pass networkis compared with the oscillator output with a phase detector of

which the output is filtered and corrects the operating point of

the variable all»pass network .

As with the reference loop the oscillator signal is taken after

the H/2 phase switch and a commutator inserted before the

filter so that constant phase detector errors are cancelled.

For SECAM operation the loop filter is grounded causing

near zero phase shift so that the two synchronous detectors

work in phase and not in quadralure.

The use of a 4.4 MHz oscillator and a servo loop to generate

the required 90° reference signal allows the use of a standard,

high volume, low cost crystal and gives an extremely accurate

90° which may be easily switched to 0° for decoding AM

SECAM generated by the TDA3030B adapter.

ACC and Identification Detectors

During burst gate time the output components of the U and

also the V demodulators are steered into PNP emitters. One

collector current of each PNP pair is mirrored and balanced

against its twin giving push-pull current sources for driving the

ACC and the identification filter capacitors.

The identification detector is given an internal offset by

making the NPN current mirror emitter resistors unequal. The

resistors are offset by 5% such that the identification detector

pulls up on its filter capacitor with zero signal.

Identification

See Figure 11 for definitions.

Monochrome I1 > I2

PAL ldent. OK I1 < lg

PAL ldent_ X l1 > I2

NTSC I3 > I2

Only for correctly identified PAL signal is the capacitor

voltage held low since I2 is then greater than I1.

For monochrome and incorrectly identified PAL signals l1>l2

hence voltage VC rises with each burst gate pulse.

When V,ef1 is exceeded by 0.7 V Latch 1 is made to conduct

which increases the rate of voltage rise on C. Maximum

current is limited by R1.

When Vref2 is exceeded by 0.7 V then Latch 2 is made to

conduct until C is completely discharged and the current drops

to a value insufficient to hold on Latch 2.

As Latch 2 turns on Latch 1 must turn off.

Latch 2 turning on gives extra trigger pulse to bistable to

correct identification.

The inhibit line on Latch 2 restricts its conduction to alternate

lines as controlled by the bistable. This function allows the

SECAM switching line to inhibit the bistable operation by firing

Latch 2 in the correct phase for SECAM. For NTSC, Latch 2

is fired by a current injected on Pin 6.

lf the voltage on C is greater than 1.4 V, then the saturation

is held down. Only for SECAM/NTSC with Latch 2 on, or

correctly identified PAL, can the saturation control be

anywhere but minimum.

NTSC Switch

NTSC operation is selected when current (I3) is injected into

Pin 6. On the TDA33O1 B this current must be derived

externally by connecting Pin 6 to +12 V via a 27 k resistor (as

on TDA33OOB). For normal PAL operation Pin 40 should be

connected to +12 V and Pin 6 to the filter capacitor.

4 Color Difference Matrixing, Color Killing,

and Chroma Blanking

During picture time the two demodulators feed simple RC

filters with emitter follower outputs. Color killing and blanking

is performed by lifting these outputs to a voltage above the

maximum value that the color difference signal could supply.

The color difference matrixing is performed by two

differential amplifiers, each with one side split to give the

correct values of the -(B-Y) and -(Ft-Y) signals. These are

added to give the (G-Y) signal.

The three color difference signals are then taken to the

virtual grounds of the video output stages together with

luminance signal.

Sandcastle Selection

The TDA3301B may be used with a two level sandcastle

and a separate frame pulse to Pin 28, or with only a three level

(super) sandcastle. In the latter case, a resistor of 1.0 MQ is

necessary from + 12 V to Pin 28 and a 70 pF capacitor from

Pin 28 to ground.

Timing Counter for Sample Control

In order to control beam current sampling at the beginning

of each frame scan, two edge triggered flip-flops are used.

The output K ofthe first flip-flop A is used to clock the second

The output K ofthe first flip-flop A is used to clock the secondtlip-flop B. Clocking of A by the burst gate is inhibited by a count

of A.B.

The count sequence can only be initiated by the trailing

edge of the frame pulse. ln order to provide control signals for:

Luma/Chroma blanking

Beam current sampling

On-screen display blanking

Brilliance control

The appropriate flip-flop outputs ar matrixed with sandcastle

and frame signals by an emitter-follower matrix.

Video Output Sections

Each video output stage consists of a feedback amplifier in A further drive current is used to control the DC operating

which the input signal is a current drive to the virtual earth from point; this is derived from the sample and hold stage which

the luminance, color difference and on-screen display stages. samples the beam current after frame flyback.

SALORA 17L61 CHASSIS L Regulated power supply device for a line sweep circuit in a television receiver:

1. A regulated power supply device, in particular for a line sweep circuit in a television receiver, whose output stage (30) contains a first electronic switch of the bidirectional type (36, 35), controlled periodically so as to be closed during the forward sweep and open during the fly-back, connected in parallel with a first series assembly containing line deviation coils (31) and a first capacitor (32), called the forward capacitor, which feeds these coils (31) during the closing of the first switch (36, 35), with a second capacitor (34), called the return capacitor, which forms a parallel resonant circuit with the inductance in particular of the coils (31) during the opening of the first switch (36, 35) and with a second series assembly containing a first winding (22) of a transformer (20), called the line transformer, and a third capacitor (33), called the power supply capacitor, which feeds the first winding (22) with D.C. voltage while the first switch (36, 35) is closed, the power supply device containing a chopper circuit (10) connected between the terminals (6, 7) of a D.C. power supply voltage source (5) and containing an inductor, called the chopper inductor, (16) and a second electronic switch (15), which is controlled, mounted in series, this second switch (15) containing a chopper transistor (11) controlled on its base by means of a recurring control signal, which is produced by means of the line return pulses picked up on a secondary winding (25) of the line transformer (20), in order to be alternately conducting and cut off during each line period, this chopper inductor (16) containing a second winding (21), called the power supply winding, of this transformer (20), which is intended for the transfer of energy between the chopper circuit (10) and the line sweep output stage (30), and being characterized by the fact that, the second switch (15) being also of the bidirectional type and containing, apart from the chopper transistor (11), which is operating in the saturated and cut off mode, a diode (12) mounted in parallel and in opposition with this transistor, the chopper circuit (10) contains also a fourth capacitor (13), called the turning capacitor, which forms a resonant circuit with the chopper inductor (16) during the opening periods of the second switch (15) which works with a constant cyclic ratio, the periods being obtained by means of a control signal which causes the cutting off of the chopper transistor (11) and their lengths being constant and greater than a half period of resonance of this resonant circuit (13, 16) whose length may reach about a half of a line period, and by the fact that the regulation of the energy exchanged between the chopper circuit (10) and the output stage (30) is obtained by the variation of the delay between the respective opening instants of the first (36, 35) and second (15) switches.

2. A power supply device as in claim 1, characterized by the fact that the transistor (11) in the second switch (15) is controlled by means

of a regulation circuit (40) fed by an auxiliary winding (25) of the transformer (20) which supplies it with a signal one of whose peak amplitudes is proportional to the voltage at the terminals of the power supply capacitor (33) in the output stage (30), which is recharged by means of the chopper circuit (10), and whose peak to peak amplitude is proportional to a very high voltage supplied by another winding (23) of transformer (20), the regulation circuit (40) causing the delay in the instant of cut off of transistor (11) to vary with respect to the leading edge of the line return pulse produced by the opening of the first switch (36, 35).

of a regulation circuit (40) fed by an auxiliary winding (25) of the transformer (20) which supplies it with a signal one of whose peak amplitudes is proportional to the voltage at the terminals of the power supply capacitor (33) in the output stage (30), which is recharged by means of the chopper circuit (10), and whose peak to peak amplitude is proportional to a very high voltage supplied by another winding (23) of transformer (20), the regulation circuit (40) causing the delay in the instant of cut off of transistor (11) to vary with respect to the leading edge of the line return pulse produced by the opening of the first switch (36, 35).3. A power supply device as in claim 2, characterized by the fact that the regulation by the phase shift between the respective cut off instants is obtained as a function either of the peak to peak amplitude or of the peak amplitude during the fly back or forward sweep of the signal at the terminals of one of the windings (21 or 25) of line transformer (20) by comparing this amplitude to a reference voltage and by controlling the delay as a function of the difference between the voltage corresponding to one of these amplitudes and the reference voltage, in order to stabilize either the sweep amplitude or the power supply voltage obtained by rectifying the line return pulse.

4. A power supply device as in claim 2, characterized by the fact that the regulation circuit (40) contains an unstable multivibrator (48) whose output is coupled to the base of chopper transistor (11) by means of a control stage (50) and which operates independantly on starting up, a circuit generating a variable delay which contains a phase shift stage (46) triggered by the line return pulses and supplying to the multivibrator (48) triggering pulses which are delayed with respect to the leading edges of the line return pulses, which cause the cutting off of chopper transistor (11), and a regulator stage (47), which supplies the phase shift stage (46) with a regulation signal that makes it possible to vary the delay between the respective leading edges of the line return pulses and the triggering pulses as a function of one of the peak amplitudes or of the peak to peak amplitude of the signal supplied by the auxiliary winding (25) of the transformer (20).

4. A power supply device as in claim 2, characterized by the fact that the regulation circuit (40) contains an unstable multivibrator (48) whose output is coupled to the base of chopper transistor (11) by means of a control stage (50) and which operates independantly on starting up, a circuit generating a variable delay which contains a phase shift stage (46) triggered by the line return pulses and supplying to the multivibrator (48) triggering pulses which are delayed with respect to the leading edges of the line return pulses, which cause the cutting off of chopper transistor (11), and a regulator stage (47), which supplies the phase shift stage (46) with a regulation signal that makes it possible to vary the delay between the respective leading edges of the line return pulses and the triggering pulses as a function of one of the peak amplitudes or of the peak to peak amplitude of the signal supplied by the auxiliary winding (25) of the transformer (20).5. A power supply device as in claim 4, of the type in which the power supply capacitor (33) feeds a D.C. voltage to the whole line sweep circuit, characterized by the fact that the regulation circuit (40) is fed by means of an independant power supply circuit (51) which enables the chopper circuit (10) to be started up by the independant operation of the unstable multivibrator (48) in order to start up the power supply of the line sweep circuit with the chopper voltage induced in the first winding (22) of the transformer (20) and rectified by the diode (35) which is part of the first bidirectional switch (36, 35) which charges the power supply capacitor (33).

6. A power supply device as in one of claims 4 and 5, characterized by the fact that the phase shift stage (46) contains a delay generator which supplies a voltage, in the shape of recurrent saw teeth (460, 463) which are triggered by the leading edges of the line return pulses, to an analog voltage comparator stage (469, 4600, 4601), which supplies at its output negative pulses to the base of the transistor (483) in multivibrator (48) whose cutting off controls the cut off of chopper transistor (11) at instants at which the instantaneous saw tooth amplitude exceeds a fixed threshold voltage (VZ 4601), and by the fact that the regulator stage (47) contains an assembly (470, 471) rectifying the signal supplied by the auxiliary winding (25) which feeds a signal generator (476, 475) supplying a signal which modifies, from a predetermined threshold, the saw tooth slope as a function of one of the peak amplitudes or peak to peak amplitudes of this signal (v25).

7. A power supply device as in claim 6, of the type in which the free running operating frequency of the unstable multivibrator (48) is less than the line frequency, characterized by the fact that the unstable multivibrator (48) is controlled solely by the negative pulses coming from the comparator stage (469), which are applied to one (483) of the transistors in the multivibrator (48), whose cut off controls that of chopper transistor (11).

8. A power supply device as in one of claims 4 to 6, of the type in which the free running operating frequency of the unstable multivibrator (48) is greater than the line frequency in order to limit the peak voltage (V19max) on the collector of the chopper transistor (11), characterized by the fact that the transistor (480) in the multivibrator (48), whose state is complementary to that of the chopper transistor (11), is fed on its base through a diode (4803) by a synchronizing stage (49), which supplies negative pulses whose amplitude is equal to a predetermined fraction of that of the line return pulses, in order to lengthen the cut off state of this transistor (480) until the sum of these lengths is equal to the line period.

Description:

The present invention concerns a regulated power supply device, in particular for a line sweep circuit in a television receiver, which can also provide D.C. supplies to other circuits in this receiver by splitting up a D.C. supply voltage which is usually obtained by the rectification and filtering of the A.C. mains voltage by means of a chopper.

Known chopper converters of this type contain, generally connected in series between the output terminals of a D.C. power supply source (filtered rectifier), an electronic switch such as a switching transistor operating in the saturated and cut off mode and an inductor which includes the primary winding of a transformer in which at least one secondary winding supplies the A.C. energy obtained by the chopping, which is then rectified to provide the D.C. supply voltages with a ground insulated from the mains. In most of the known chopper power supplies, one can vary the output voltages by action on the cyclic ratio, i.e. the length of the saturated (closed) state of the switch, for example, by controlling periodically the transistor-chopper by means of a monostable flip-flop of variable length as a function of a voltage which may be picked up at the output of a rectifier fed by a secondary winding of the transformer so as to form a regulation loop.

Chopper power supplies have frequently been used in television receivers to eliminate the bulky and heavy mains supply transformer and make possible a regulation of the D.C. power supply voltage for this receiver. They have often been combined in particular at the output stage of the horizontal sweep circuit which supplies them with a pulse signal at the line frequency that can be used to control the chopping. Various combinations of sweep circuits and chopper power supplies have described, for example, in the French patents or patent applications with publication Nos. 2.040.217, 2.060.495, 2.167.549, 2.232.147 or 2.269.257, in which the regulation is also done by means of the variation in the cyclic ratio of the saturated and cut off states of the chopper transistor which, in some cases, is also used as the active element of the (final) output stage of the line sweep circuit or of the feeder stage which controls this circuit.

Chopper power supplies of the so called "pump" type in which the chopper transistor feeds one of the windings of the line transformer during the line return periods and in which the regulation is done by means of the variation of the internal resistance of this transistor or of a "ballast" transistor in series with this transistor are known, for example, from the French patents with publication Nos. 2.014.820, 2.025.365 or 2.116.335. A circuit of the "pump" type whose chopper transistor has a winding of the line transformer in its collector circuit and in which the sweep circuit is electrically insulated from the mains has been described in the article by Peruth and Schrenk in the German periodical, SIEMENS BAUTEILE REPORT Vol. 12 (1974), No. 4, pages 96-98. Its structure corresponds to the contents of the introduction to claim 1. In circuits of the "pump" type, the chopper transistor or the "ballast" transistor in series with it dissipates an amount of energy which is not negligable.

In the chopper device supplying power to the output stage of the line sweep circuit with which it is combined in accordance with the invention, one no longer uses regulation by variation of the internal resistance or of the length of the saturated state of the chopper transistor (or by variation of the cyclic ratio of the chopping with a constant periodicity) but one does the regulating by variation of the relative phase between the signals of the same frequency which are supplied respectively by the chop

per circuit with a constant cyclic ratio and by the output stage of the line sweep, each of which is connected to one of the windings of a transformer called the line transformer through which the transfer of energy between the chopper circuit and the sweep output stage takes place as well as in the direction of the other secondary windings of the line tranformer such as the very high tension (V.H.T.) winding.

per circuit with a constant cyclic ratio and by the output stage of the line sweep, each of which is connected to one of the windings of a transformer called the line transformer through which the transfer of energy between the chopper circuit and the sweep output stage takes place as well as in the direction of the other secondary windings of the line tranformer such as the very high tension (V.H.T.) winding.In accordance with the invention, a regulated power supply device, in particular for a line sweep circuit of a television receiver which contains an output stage fitted with a line transformer in which a first winding is connected in series with a supply capacitor, is connected in parallel with a first bidirectional switch controlled at the line frequency, the power supply device containing a chopper circuit with, connected in series between the terminals of a source of a D.C. power supply voltage, an inductor and a second electronic switch, which can also be controlled at the line frequency. The inductor in this circuit contains a second winding of the transformer which is intended for the transfer of energy between the chopper circuit and the output stage. This power supply device is in particular characterized by the fact that the second switch, which is also bidirectional and m

ounted in parallel with a tuning capacitor, is so controlled as to be alternately open and closed during each line period with a constant cyclic ratio and by the fact that the regulation of the power supplied and hence of the voltage at the terminals of the supply capacitor is done by variation of the phase delay between the respective opening instants of the first and second switch as a function of the peak amplitude of the line return pulse for example.

ounted in parallel with a tuning capacitor, is so controlled as to be alternately open and closed during each line period with a constant cyclic ratio and by the fact that the regulation of the power supplied and hence of the voltage at the terminals of the supply capacitor is done by variation of the phase delay between the respective opening instants of the first and second switch as a function of the peak amplitude of the line return pulse for example.In accordance with a preferred way of making the invention, a power supply device in accordance with the preceding paragraph, in which the second bidirectional switch, which contains a switching transistor, is controlled on its base by a regulation circuit in which one input is fed by an auxiliary secondary winding of the line transformer supplying line return pulses, is remarkable in particular for the fact that the regulation circuit contains an unstable multivibrator controlling the base of the chopper transistor and operating independantly on starting up, a circuit generating a variable delay containing a phase shift stage, which is triggered by the line return pulses and supplies the multivibrator with triggering pulses that are delayed with respect to the leading edges of the line return pulses, which cause the cut off of the chopper transistor, and a regulator stage fed with the line return pulses and supplying to the phase shift stage a regulation signal which enables the delay in the triggering pulses to be varied with respect to the line return pulses as a function of one of the peak amplitudes or of the peak to peak amplitude of the line return pulses.

The invention will be better understood and others of its characteristics and advantages will appear from the description which follows, which is given as an example, and the drawings attached, which refer to it. Among them:

FIG. 1 represents part of a theoretical schematic diagram of a chopper power supply device combined with the output stage of the line sweep circuit in accordance with the invention;

FIGS. 2a-2f and 3a-3f are diagrams of the voltage wave forms and/or current wave forms at various points in the circuit of FIG. 1 to explain the operation of this circuit;

FIGS. 2a-2f and 3a-3f are diagrams of the voltage wave forms and/or current wave forms at various points in the circuit of FIG. 1 to explain the operation of this circuit;FIG. 4 represents part of a synoptic schematic diagram of a simple production model (without a starter device) of regulation circuit 40 in FIG. 1;

FIG. 5 represents a block diagram of a preferred production model of regulation circuit 40 in FIG. 1 in accordance with the invention;

FIG. 6 represents a theoretical schematic diagram of the whole of the preferred production model of the regulation circuit in FIG. 5;

FIG. 6 represents a theoretical schematic diagram of the whole of the preferred production model of the regulation circuit in FIG. 5;FIGS. 7a and 7b represent voltage wave forms illustrating the slaving of the frequency of the unstable multivibrator 48 to that of the line oscillator; and

FIGS. 8a-8c represent voltage wave forms illustrating the operation of the regulation by the variation in phase shift.

In FIG. 1 is shown schematically a chopper power supply device of line sweep output stage 30 in accordance with the invention which is electrically insulated from the A.C. mains which feed rectifier 5 whose output voltage is chopped. This power supply device has two terminals 1, 2 which are connected respectively to the two poles of the A.C. distribution mains (220 V, 50 Hz) and feed rectifier diode 3 and filter capacitor 4, whose capacity is high, which are connected in series and form together a rectifier assembly or a source of D.C. voltage 5. The output of rectifier assembly 5 formed by the two terminals 6 and 7 (plates) of the (electro-chemical) capacitor 4 is intended to supply a D.C. power supply voltage V A of the order of 300 V to chopper circuit 10. This chopper circuit 10 contains a controlle

d, bidirectional electronic switch 15, which consists of a switching transistor 11 of the NPN type connected with its emitter common and a junction semiconductor diode 12, which are connected in parallel in such a way as to conduct respectively in opposite directions (anti-parallel), and an inductor 16 consisting of a choke 14 and a winding 21 of a transformer 20, called a line transformer, connected in series. This winding 21 of line transformer 20 whose primary winding is normally connected in parallel with the coils of the horiziontal deviation circuit in the circuit of line sweep output stage 30 to the supply, through secondary windings, supply voltages in particular to the cathode ray tube will be called in what follows the supply voltage winding, because the transfer of energy between chopper circuit 10 and output stage 30 will be done through it. Switch 15 is mounted in parallel with a capacitor 13 and it is connected in series with inductor 16 (choke 14 and power supply winding 21 in series) between the output terminals 6 and 7 of D.C. voltage source 5. This capacitor 13 forms, because of its low capacity with respect to that of filter capacitor 4, with inductor 16 a parallel, resonant (oscillatory) circuit when electronic switch 15 is opened by the cutting off of switching transistor 11 by means of a control signal applied to its base.

d, bidirectional electronic switch 15, which consists of a switching transistor 11 of the NPN type connected with its emitter common and a junction semiconductor diode 12, which are connected in parallel in such a way as to conduct respectively in opposite directions (anti-parallel), and an inductor 16 consisting of a choke 14 and a winding 21 of a transformer 20, called a line transformer, connected in series. This winding 21 of line transformer 20 whose primary winding is normally connected in parallel with the coils of the horiziontal deviation circuit in the circuit of line sweep output stage 30 to the supply, through secondary windings, supply voltages in particular to the cathode ray tube will be called in what follows the supply voltage winding, because the transfer of energy between chopper circuit 10 and output stage 30 will be done through it. Switch 15 is mounted in parallel with a capacitor 13 and it is connected in series with inductor 16 (choke 14 and power supply winding 21 in series) between the output terminals 6 and 7 of D.C. voltage source 5. This capacitor 13 forms, because of its low capacity with respect to that of filter capacitor 4, with inductor 16 a parallel, resonant (oscillatory) circuit when electronic switch 15 is opened by the cutting off of switching transistor 11 by means of a control signal applied to its base.Switching transistor 11 is here connected by its collector to one of the terminals of inductor 16, whose other terminal is connected to positive terminal 6 of source 5 which supplies D.C. power supply voltage V A , by its emitter to negative terminal 7 of source 5, which forms a ground, called the primary or hot ground, 8, which is connected to the A.C. mains but is insulated from that 39 of the television set. The base of transistor 11 is controlled by means of rect

angular signals supplied by a regulation circuit 40, which is described further on, in such a way as to be alternately saturated and cut off. Regulation circuit 40 is, for example, fed by a secondary winding 25 of transformer 20, that supplies signals whose peak to peak amplitude is proportional to the peak amplitude of the line return pulse. This peak amplitude is a function of the energy transfer from chopper circuit 10 to the line sweep output stage 30 which is connected to another winding 22 of transformer 20.

angular signals supplied by a regulation circuit 40, which is described further on, in such a way as to be alternately saturated and cut off. Regulation circuit 40 is, for example, fed by a secondary winding 25 of transformer 20, that supplies signals whose peak to peak amplitude is proportional to the peak amplitude of the line return pulse. This peak amplitude is a function of the energy transfer from chopper circuit 10 to the line sweep output stage 30 which is connected to another winding 22 of transformer 20.One may note here that chopper circuit 10 resembles a classical, transistorized, line sweep output stage and that switching transistor 11 has been chosen to withstand high collector-emitter voltages (of the order of 1500 V), and that diode 12 has to withstand the same inverse voltage while switch 15 is open. One may also note that the inductance of choke 14 may be formed partly or wholly by the leakage inductance of power supply winding 21 in transformer 20.

The line sweep output stage 30, which is arranged in classical fashion, contains horizontal deviation coils 31 mounted in parallel and connected by one of their terminals to a first capacitor 32, called the "forward" or "S effect" capacitor, which feeds them during the forward sweep. The s

eries mounting of coils 31 and forward capacitor 32 is connected in parallel, on the one hand, to a second controlled bidirectional switch containing a second switching transistor 36 and a second diode 35, called a "shunt" or "parallel" recuperation diode, which are connected in parallel to conduct in opposite directions, closed (conductor) during the forward sweep and open (cut off) during the return sweep, and, on the other hand, to a second capacitor 34, called the "return" capacitor, which forms, while the second switch is open, a parallel resonant circuit with the inductance of deviation coils 31. The common point of the collector of second transistor 36, of the NPN type, of the cathode of second diode 35 and return 34 and forward 32 capacitors is c

eries mounting of coils 31 and forward capacitor 32 is connected in parallel, on the one hand, to a second controlled bidirectional switch containing a second switching transistor 36 and a second diode 35, called a "shunt" or "parallel" recuperation diode, which are connected in parallel to conduct in opposite directions, closed (conductor) during the forward sweep and open (cut off) during the return sweep, and, on the other hand, to a second capacitor 34, called the "return" capacitor, which forms, while the second switch is open, a parallel resonant circuit with the inductance of deviation coils 31. The common point of the collector of second transistor 36, of the NPN type, of the cathode of second diode 35 and return 34 and forward 32 capacitors is c onnected to one of the terminals 220 of winding 22 of transformer 20, which normally forms the primary winding of this transformer. The other terminal 221 of winding 22 is connected to one of the terminals of a third capacitor 33 of high capacity, whose other terminal is connected to the common point of deviation coils 31, return capacitor 34, the anode of second diode 35 and the emitter of second transistor 36, which is also connected to the ground 39 of the chassis of the television receiver, called the "cold" ground, because it is insulated from the A.C. power supply mains. It is at the terminals of this third capacitor 33 that one obtains the D.C. voltage feeding this stage, whose value determines, on the one hand, the peak to peak amplitude of the line sweep current of sawtooth form and, on the other hand, the amplitude of the line return voltage pulse which, when rectified after being transformed, supplies the very high voltage that polarizes the anode of the cathode ray tube (not shown here). The second transistor 36, also a switching transistor, is controlled by rectangular shaped signals supplied to input terminals 37 and 38 of stage 30, which are respectively connected to its base and its emitter, by a feed stage (not shown and called a "driver" in anglo-american literature) so that it is alternately cut off, during the sweep return, and saturated, during the second part of the forward sweep.

onnected to one of the terminals 220 of winding 22 of transformer 20, which normally forms the primary winding of this transformer. The other terminal 221 of winding 22 is connected to one of the terminals of a third capacitor 33 of high capacity, whose other terminal is connected to the common point of deviation coils 31, return capacitor 34, the anode of second diode 35 and the emitter of second transistor 36, which is also connected to the ground 39 of the chassis of the television receiver, called the "cold" ground, because it is insulated from the A.C. power supply mains. It is at the terminals of this third capacitor 33 that one obtains the D.C. voltage feeding this stage, whose value determines, on the one hand, the peak to peak amplitude of the line sweep current of sawtooth form and, on the other hand, the amplitude of the line return voltage pulse which, when rectified after being transformed, supplies the very high voltage that polarizes the anode of the cathode ray tube (not shown here). The second transistor 36, also a switching transistor, is controlled by rectangular shaped signals supplied to input terminals 37 and 38 of stage 30, which are respectively connected to its base and its emitter, by a feed stage (not shown and called a "driver" in anglo-american literature) so that it is alternately cut off, during the sweep return, and saturated, during the second part of the forward sweep.In classical transistor line sweep circuits, a D.C. voltage source generally feeds either terminal 221 of winding 22 directly or an intermediate connection to this winding through a diode (see French Pat. Nos. 1.298.087 dated Aug. 11, 1961, 1.316.732 dated Feb. 15, 1962 or 1.361.201 dated June 27, 1963) which isolates the primary winding of the line transformer from the D.C. voltage source during the line return interval.

In the circuit of FIG. 1, it is the A.C. electrical energy transmitted by chopper circuit 10 through windings 21 and 22 of transformer 20 which charges capacitor 33 so that it supplies a regulated supply voltage to output stage 30. During the line sweep forward periods, when the second bidirectional switch 35, 36 of sweep output stage 30 is closed (conductor), the terminals of winding 22 of transformer 20 are directly connected to those of capacitor 33 which will then receive the energy supplied of by chopper circuit 10.

In the circuit of FIG. 1, it is the A.C. electrical energy transmitted by chopper circuit 10 through windings 21 and 22 of transformer 20 which charges capacitor 33 so that it supplies a regulated supply voltage to output stage 30. During the line sweep forward periods, when the second bidirectional switch 35, 36 of sweep output stage 30 is closed (conductor), the terminals of winding 22 of transformer 20 are directly connected to those of capacitor 33 which will then receive the energy supplied of by chopper circuit 10.In FIG. 1, line transformer 20 also has a very high voltage winding 23, one terminal 230 of which may be connected to the ground 39 (or to terminal 220 of winding 22) and whose other terminal 231 is connected to the input of the very high voltage rectifier assembly or voltage multiplier (not shown) in classical fashion, and an auxiliary winding 24 which may be used to feed either a low voltage rectifier assembly or a load regulator assembly or the filament of the cathode ray tube (not shown). These secondary windings 23, 24 will receive their energy mainly from output stage 30 of the line sweep circuit through winding 22 of transformer 20, i.e. the line return pulses, the coupling between the windings will hence be as close as possible.

The operation of the power supply device in FIG. 1 will be explained below with that of output stage 30 of the line sweep circuit, with reference to FIGS. 2 and 3 of the drawing attached, representing diagrams of the voltage wave forms and/or current wave forms at various points in the schematic diagram of FIG. 1.

In FIGS. 2 and 3, diagram (A) represents the saw tooth wave form of the sweep current i 31 (t) in the coils 31 of the horizontal deviation circuit. Diagram (B) represents the wave form of the voltage v 220 (t) on terminal 220 of winding 22, which is also that at the terminals of the second switch 35, 36. Diagram (C) is the wave form of the voltage v 21 (t) at the terminals of power supply winding 21 when its leakage inductance is negligable. It is obtained by the transforming of the A.C. component of voltage v 220 (t). Diagram (D) represents the wave form of the voltage v 19 (t) at the terminals of first switch 15 in chopper circuit 10, i.e. between the junction 19 of this chopper circuit with inductor 16 and primary ground 8, and diagram (E) represents as a dotted line the current i 16 (t) in inductor 16 when output stage 30 is not controlled and as a full line the current i 21 (t) resulting from the superimposition in winding 21 to current i 16 (t) on that induced by winding 22 when output stage 30 is working. Conversely, the current in winding 22 of transformer 20 results from the superimposition of the current induced by winding 21 on the current produced by the closing of the second switch 35, 36, which is analogous to i 31 (t) in diagram (A).

In FIGS. 2 and 3, diagram (A) represents the saw tooth wave form of the sweep current i 31 (t) in the coils 31 of the horizontal deviation circuit. Diagram (B) represents the wave form of the voltage v 220 (t) on terminal 220 of winding 22, which is also that at the terminals of the second switch 35, 36. Diagram (C) is the wave form of the voltage v 21 (t) at the terminals of power supply winding 21 when its leakage inductance is negligable. It is obtained by the transforming of the A.C. component of voltage v 220 (t). Diagram (D) represents the wave form of the voltage v 19 (t) at the terminals of first switch 15 in chopper circuit 10, i.e. between the junction 19 of this chopper circuit with inductor 16 and primary ground 8, and diagram (E) represents as a dotted line the current i 16 (t) in inductor 16 when output stage 30 is not controlled and as a full line the current i 21 (t) resulting from the superimposition in winding 21 to current i 16 (t) on that induced by winding 22 when output stage 30 is working. Conversely, the current in winding 22 of transformer 20 results from the superimposition of the current induced by winding 21 on the current produced by the closing of the second switch 35, 36, which is analogous to i 31 (t) in diagram (A).The wave forms of diagrams (D) and (E) in FIGS. 2 and 3 are out of phase respectively, one with respect to another, by a quarter of a line period T H /4 to allow the illustration of the regulation by the variation in the relative phase of the voltage v 21 and current i 21 waves in power supply winding 21.

The diagrams (F) represent the instantaneous energy E i transmitted by chopper circuit 10 to the output stage 30, which is equal to the product of the wave forms of current i 21 (t) and voltage v 21 (t) in winding 21, i.e. E i =-v 21 i 21 , for two different phase deviations between the voltage v 21 (t) and current i 21 (t) waves in power supply winding 21, which correspond respectively to a zero energy transfer in FIG. 2 and a maximum energy transfer in FIG. 3.

The operation of the line sweep output stage 30 is classical once the power supply capacitor 33 and forward capacitor 32 are charged to a D.C. voltage V 221 by means of a certain number of chopping cycles, which are

independant on starting up, during which the negative half-cycles of the chopped voltage wave are rectified by recuperation diode 35.

independant on starting up, during which the negative half-cycles of the chopped voltage wave are rectified by recuperation diode 35.During the forward sweep intervals t A , when the switch 35, 36 is closed from instant t 1 to instant t 3 , the current i 31 (see A) in the deviator varies roughly linearly between its negative peak values (at t 1 ) and positive ones (at t 3 ) with a passage through zero at instant t 2 , when current i 31 passes from diode 35 to transistor 36, which has previously been polarized to conduct. This corresponds to a roughly zero voltage v 220 (see B) at the terminals of switch 35, 36.

The line return interval t R is started by the cutting off of transistor 36 at instant t 3 , and the inductance of deviator 31 then acts as a parallel resonant circuit with the return capacitor 34 by causing the voltage v 220 (t) to pass through a positive half-sinusoid and reach its peak value at the instant t 4 (or t=0), called the line return pulse, and the current i 31 (t) to pass through a half-cosinusoid between the positive and negative peak values cited, with a passage through zero at the instant t 4 (or t=0). The mean value of the voltage wave form v 220 (t) at terminal 220 is equal to the D.C. power supply voltage V 221 at the terminals of power supply capacitor 33 and forward or S effect capacitor 32.

The respective peak to peak amplitudes of current i 31 (t) (hence the width of the screen sweep beam excursion) and of voltage v 220 (t) (hence the very high voltage) depend on the value of the D.C. voltage V 221 whic

h feeds the horizontal sweep output stage and which, in most of the chopper power supplies of preceding techniques, is regulated and stabilized by modulating the length of the saturated state (the cyclic ratio) of chopper transistor 11 as a function of the amplitude of the line return pulse picked up on an auxiliary winding of line transformer 20 (hence of the voltage at the terminals of capacitor 33) and later of the rectified and filtered voltage in the network.

h feeds the horizontal sweep output stage and which, in most of the chopper power supplies of preceding techniques, is regulated and stabilized by modulating the length of the saturated state (the cyclic ratio) of chopper transistor 11 as a function of the amplitude of the line return pulse picked up on an auxiliary winding of line transformer 20 (hence of the voltage at the terminals of capacitor 33) and later of the rectified and filtered voltage in the network.In accordance with the invention, the length t s of the saturated state of chopper transistor 11 and of the conducting state of diode 12 and, as a result, the ratio of this length to that of the complete cycle (line period T H ) or to that t B of the cut off state is constant and so chosen as to make the peak amplitude of voltage pulse v 19 , which is applied to the collector of transistor 11 during the cut off interval t B , considerably less than its collector-emitter D.C. breakdown voltage in the cut off state (V CEX ) which may exceed 1500 Volts. Thus, for a rectified voltage of 300 V, it is possible to limit the collector voltage V 19 to about 900 Volts by choosing a ratio t b /T H of about 0.5.

As a result, chopper circuit 10 must operate at the line frequency with conduction lengths t S (closed) and cut off lengths t B (open) of switch 15 preferably roughly equal (to a line half-period T H /2) and the regulation of the energy supplied to output stage 30 is done by causing the respective ph

ases of the line return pulse v 220 (t) and the current i 21 (t) flowing through the power supply winding 21 of transformer 20 to vary as will be shown further on.

ases of the line return pulse v 220 (t) and the current i 21 (t) flowing through the power supply winding 21 of transformer 20 to vary as will be shown further on.The operation of chopper circuit 10 (fed with D.C. voltage V A ) is in fact analogous to that of output stage 30, except as far as the form factor is concerned. This is determined mainly by the respective values of the inductance 16 (of choke 14 and the leakage inductance of winding 21 of transformer 20 connected in series) and of the capacity of tuning capacitor 13. The values L 16 and C 13 are chosen to obtain a half-period of oscillation slightly less than a line half-period, i.e.: ##EQU1## because the oscillation of the resonant circuit L 16 , C 13 occurs on one side and on the other of the D.C. voltage V A so that the cut off period of chopper switch 15 is greater than this half-period T D /2.

This operation of circuit 10 will first be explained with reference to diagrams D and E in FIG. 2. When, at the instant t=0, transistor 11 becomes saturated by a preliminary positive polarization of its base-emitter junction, it connects terminal 19 to ground 8 so that a current i 16 (t) (dotted on diagram E), which is increasing linearly, ##EQU2## passes through inductor 16 coming from positive terminal 6 of power supply 5.

When transistor 11 receives from regulation circuit 40 a cut off voltage at an in

stant preceding instant t 6 of the storage time of minority charge carries, switch 15 opens and the current stored in inductor 16, i 16 (t 6 )=V A t 6 /L=V A T H /4L, will flow through tuning capacitor 13 in oscillatory fashion, i.e. cosinusoidally, decreasing to a zero value, while voltage V 19 at junction 19 of inductor 16 and capacitor 13 will increase sinusoidally to a maximum value, these two values coinciding in time. Then, capacitor 13 discharges through inductor 16 also in oscillatory fashion until, at instant t 7 , voltage v 19 reaches a zero value, which corresponds to a minimum value, i.e. maximum negative, of current i 16 (t) whose absolute value is slightly less than the maximum positive value i 16 (t 6 ). The difference between the absolute peak values i 16 (t 6 ) and i 16 (t 7 ) is explained, on the one hand, by the ohmic losses in circuit 10 and, on the other, by the transfer of energy between this circuit and, in particular, output stage 30.

stant preceding instant t 6 of the storage time of minority charge carries, switch 15 opens and the current stored in inductor 16, i 16 (t 6 )=V A t 6 /L=V A T H /4L, will flow through tuning capacitor 13 in oscillatory fashion, i.e. cosinusoidally, decreasing to a zero value, while voltage V 19 at junction 19 of inductor 16 and capacitor 13 will increase sinusoidally to a maximum value, these two values coinciding in time. Then, capacitor 13 discharges through inductor 16 also in oscillatory fashion until, at instant t 7 , voltage v 19 reaches a zero value, which corresponds to a minimum value, i.e. maximum negative, of current i 16 (t) whose absolute value is slightly less than the maximum positive value i 16 (t 6 ). The difference between the absolute peak values i 16 (t 6 ) and i 16 (t 7 ) is explained, on the one hand, by the ohmic losses in circuit 10 and, on the other, by the transfer of energy between this circuit and, in particular, output stage 30.When oscillatory voltage v 19 (t) has exceeded the zero value slightly in the negative direction, diode 12 starts to cond