This is one of the PANASONIC DIGITAL CHASSIS versions Implementing DIGITAL SIGNAL PROCESSING and basing it on the ITT DIGIVISION DIGIT3000 family chipset.

It's a successor of EURO 2 L and a full successor of the PANASONIC EURO 1 DIGITAL CHASSIS

CIRCUITS DESCRIPTIONS:

CCU 3000, CCU 3000-I

CCU 3001, CCU 3001-I

MICRONAS INTERMETALL 4

1. Introduction

The CCU 3000, CCU 3000-I, CCU 3001, CCU 3001-I

are integrated circuits designed in 1.2 mm CMOS

technology, with the exception of CCU 3000, TC18 and

TC19, which is designed in 1 mm CMOS technology. The

CPU contained on the chips is a functionally unchanged

65C02-core, which means that for program development,

systems can be used which are on the market; including

high level language c

ompilers.

ompilers.The pin numbers mentioned in this data sheet refer to

the 68-pin PLCC package unless otherwise designated.

The CCU 3000-I is described separately in an addendum

on page 66.

1.1. Features of the CCU 3000, CCU 3000-I,

CCU 3001, CCU 3001-I

– CCU 3000 = ROM-less version of the CCU 3001

– 65C02 CPU with max. 8 MHz clock

– 32 kByte internal ROM (CCU 3001 only)

– 1344 internal Bytes RAM with stand-by option

– 51 I/O lines (CCU 3001)

– 26 I/O lines (CCU 3000)

– clock generator with programmable clock frequency

– 8 level interrupt controller

– CCU 3000, CCU 3001:

2 Multimaster IM bus interfaces

– CCU 3000-I, CCU 3001-I: 1I2C/IM bus and

1 Multimaster IM bus interface (see addendum)

– IR-input for software-decoded IR-systems

– on-chip power on, stand-by and clock supervision

logic

– on-chip watchdog

– 3 multifunctional timers

– supports memory banking (external 2MBytes)

– power down signal for external memory

– mask option: EMU mode

– programs can be written in Assembler or in “C”

– CCU 3000 TC 18/19: 1.0 mm CMOS technology, (see

addendum)

– application software available.

Functional Description

2.1. ROM

The chip is equipped with 32 kByte mask-programmable

ROM. The ROM uses up the address space from 8000H

to FFFFH. This ROM can be supplemented or replaced

externally. Only the CCU 3001 has an internal ROM.

2.2. RAM

The RAM

area is split into three parts:

area is split into three parts:– page 0 (address 0 to FFH)

– page 1 (address 100H to 1FFH)

– page 3, 4, 5, 6 (address 300H to 63FH)

Page 0 offers a particularly fast access to the 65C02 and

is therefore very valuable for fast, compact programs.

Page 1 contains the stack and must therefore also have

RAM. The remaining RAM-memory follows in pages 3,

4, 5, 6, as page 2 is reserved as I/O address space. The

RAM can be kept in the stand-by mode via stand-by pin.

2.3. CPU

The CPU core is fully compatible with the 65C02 microprocessor.

However, not all the pins of the 65C02 processor

are accessible for the user outside the chip. One

switch in the control register allows the CPU to be

switched off, so that an external processor can take over

its tasks. This external processor can of course also be

an in-circuit emulator, which makes near-hardware

emulation possible, even though the status and control

lines of the internal CPU are not accessible. If an external

processor is used, all hardware blocks of the chip are

as accessible to it as if it were the internal CPU.

2.4. Clock Generator

An integrated two-pin oscillator generates the clock for

the microcontroller. The frequency created by the oscillator

can be programmed to be reduced with a divider

by the factor 1 ... 255. This enables the user to decrease

the current consumption by the controller by reducing

the working frequency as well as to increase the access

time for the (slower) external memory. This divider contains

the value 4 after a reset, so that the system can also

start with a slow external memory. If the mask-option

OSC is set (EMU version), a switch in the control register

makes it possible to recei

ve the internal clock F2 at

ve the internal clock F2 atXTAL2. In this case the oscillator must be external and

the clock must be fed to the pin XTAL1. In this way, the

user gets a time reference for internal operations in the

microcomputer. This is especially important with the interrupt

controller. The production version of the CCU

does not have this function!

2.5. PORT 1 to PORT 3, PORT 6 to PORT 8

8 ports belong to the system, of which 5 are 8 bits wide,

one 6 bit, one 4 bit and one 1 bit wide. All port lines of

PORTS 1 to 3 and 6 to 8 can be used as inputs or outputs

independently from each other. One register per port

defines the direction. PORT1 to PORT3 have push-pull

outputs and PORT6 to PORT8 have open drain outputs.

Even a line defined as output can be read, the pin level

being important. This property makes it possible for the

software to find desired and undesired short circuits.

Each port reserves a byte for the direction register and

the data in the I/O page. If the corresponding bit in the

direction register is set to 0, the output mode is switched

on. After a reset, all bits of a direction register are set

to 1. The falling edge of bit 7 of PORT 8 generates interrupts

if the priority of the corresponding interrupt controller

source (7) is not set to 0.

2.6. PORT 4

PORT 4 consists of only one line (LSB, P40). After a reset,

PORT 4 operates as an input only. As soon as PORT

4 is written for the first time, it is switched to output mode

(push-pull). Later read accesses read the actual level at

port 4. If bit 3 in the control word is active, P4 is used as

an R/W-line. If the internal CPU is active, R/W is an output

line, otherwise it is an input. But P4 has another, very

important function during RESET. The level at P4 during

RESET decides whether the control word is read from

the internal ROM (FFF9H) or from the external memory.

It is therefore important that the desired level during RESET

is set at P4. An internal pull-down resistor of approx.

100 kW

is integrated in the CCU 3001, which ensures

is integrated in the CCU 3001, which ensuresthat the control word is read by the internal ROM. The

external control word access is obtained via an external

pull-up resistor of approx. 5 kW. The CCU 3000 has an

internal pull-up resistor at P4 (external ROM access).

The further mode of operation of the CCU 3000, CCU

3001 depends only on the control word though.

Please note that this mode is always necessary for

the CCU 3000 since this device does not have internal

ROM!

2.7. I/O-Lines P50 to P55

The 6 additional I/O-lines have a two-fold function:

– input or output line (open drain output) or

– fully decoded I/O-select lines (push-pull outputs)

As a rule these lines can be used as input or output lines.

As soon as ports 1 to 4 are used as system bus, they are

lost as I/O-channels. However, a total of 48 port lines (24

inputs and outputs each) can be reconstructed without

difficulties (1 housing for 8 lines), if the additional 6 I/Olines

of the CCU 3000, CCU 3001 are switched into the

port select mode. They then represent the select lines of

the original ports 1 to 3. Each line can be defined as I/O

or port select line separately. In the I/O-page three bytes

are needed.

ITT VDP3108 Single-Chip Video Processor

Preamble:

The ITT VDP3108 Is the evolution of the DIGIT2000 chipset.

1. Introduction

The entire video processing and controlling for a color

TV has been developed on a single chip in 0.8m CMOS

technology. Modular design and submicron technology

allow the economic integration of features in all classes

of TV sets.

Open architecture is the key word to the new DSP generation.

Flexible standard building blocks have been defined

that offer continuity and transparency of the entire

system.

One IC contains the entire video and deflection processing

and builds the heart of a modern color TV. Its performance

and complexity allow the user to standardize

his product development. Hardware and software applications

can profit from the modularity as well as manufacturing,

system support or maintenance. The main

features are:

– low cost, high performance

– all digital video processing

– multi-standard color decoder PAL/NTSC/SECAM

– 3 composite, 1 S–VHS input

– integrated high-quality AD/DA converters

– sync and deflection processing

– luminance and chrominance features, e.g.

peaking, color transient improvement

– programmable RGB matrix

– various digital interfaces

– embedded RISC controller (80 MIPS)

– one crystal, few external components

– one crystal, few external components– single power supply 5 V

– 0.8m CMOS Technology

– 68-pin PLCC or 64-pin Shrink DIL Package

1.1. System Architecture

Two main modules have been defined:

Video Processor and

Display Processor.

They are designed as silicon building blocks. Their partitioning

permits a variety of IC configurations with the aim

to satisfy the particular requirements of different applications.

Both, analog and digital interfaces, support

state of the art TV receivers as well as other environments.

Fig. 1–1 shows the block diagram of the singlechip

Video Processor which consists of both modules.

2. Functional Description

2.1. Analog Front End

This block provides the analog interfaces to all video inputs

and mainly carries out analog-to digital conversion

for the following digital video processing. A block diagram

is given in figure 2–1.

Most of the functional blocks in the front end are digitally

controlled (clamping, AGC and clock-DCO). The control

loops are closed by the Fast Processor (‘FP’) embedded

in the decoder.

2.1.1. Input Selector

Up to four analog inputs can be connected. Three inputs

are for input of composite video or S–VHS luma signal.

These inputs are clamped to the sync back porch and

are amplified by a variable gain amplifier. One input is

for connection of S–VHS carrier–chrominance signal.

This input is internally biased and has a fixed gain amplifier.

2.1.2. Clamping

The composite video input signals are AC coupled to the

IC. The clamping voltage is stored on the coupling capacitors

and is generated by digitally controlled current

sources. The clamping level is the back porch of the video

signal. S-VHS chroma is also AC coupled. The input

pin is internally bias

ed to the center of the ADC input

ed to the center of the ADC inputrange.

2.1.3. Automatic Gain Control

A digitally working automatic gain control adjusts the

magnitude of the selected baseband by +6/–4.5 dB in 64

logarithmic steps to the optimal range of the ADC .

The gain of the video input stage including the ADC is

213 steps/V for all three standards (PAL/NTSC/SECAM/

Y/C), with the AGC set to 0 dB.

2.1.4. Analog-to-Digital Converters

Two ADCs are provided to digitize the input signals.

Each converter runs with 20.25 MHz and has 8 bit resolution.

An integrated bandgap circuit generates the required

reference voltages for the converters.

The two ADCs are of a 2-stage subranging type.

---------------------------------------------------------------------------

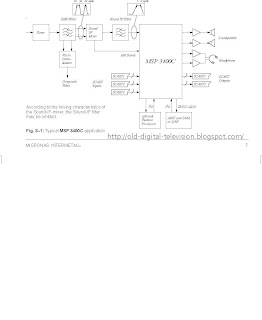

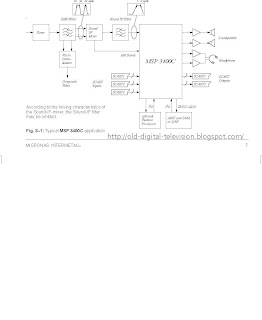

TOGHETHER WITH VIDEO PROCESSING THERE IS SOUND PROCESSING WITH MSP3400C

Multistandard Sound Processor

Release Notes: The hardware description in this

document is valid for the MSP 3400C – C8 and newer

codes. Revision bars indicate significant changes

to the previous version.

1. Introduction

The MSP 3400C is designed as single-chip Multistandard

Sound Processor for applications in analog and

digital TV sets, satellite receivers and video recorders.

The MSP-family, which is based on the MSP 2400, demonstrates

the progressive development towards highly

integrated multi-functional ICs.

The MSP 3400C, again, improves function integration:

The full TV sound processing, starting with analog

sound IF signal-in, down to processed analog AF-out, is

performed in a single chip. The IC is produced in 0.8 mm

CMOS technology, combined with high performance

digital signal processing.

The MSP 3400C 0.8 m CMOS version is fully pin and

software compatible to the 1.0 m MSP 3400 and MSP

software compatible to the 1.0 m MSP 3400 and MSP3410. The main difference between the MSP 3400C and

the MSP 3410, consists of the MSP 3410 being able to

decode NICAM signals.

2. Features of the MSP 3400C:

2.1. Features of the Demodulator and Decoder

Sections

The MSP 3400C is designed to perform demodulation

of FM-mono TV sound and two carrier FM systems according

to the German or Korean terrestrial specs. With

certain constraints, it is also possible to do AM-demodulation

according to the SECAM system. Alternatively, the

satellite specs can be processed with the MSP 3400C.

For FM carrier detection in satellite operation, the AMdemodulation

offers a powerful feature to calculate the

carrier field strength, which can be used for automatic

search algorithms. So, the IC facilitates a first step towards

multistandard capability with its very flexible

application and may be used in TV-sets, satellite tuners,

and video recorders.

The MSP 3400C facilitates profitable multistandard capability,

offering the following advantages:

– two selectable analog inputs (TV and SAT-IF sources)

– Automatic Gain Control (AGC) for analog input: input

range: 0.14 – 3 Vpp

– integrated A/D converter for sound-IF inputs

– all demodulation and filtering is performed on chip and

is individually programmable

– no external filter hardware is required

– only one crystal clock (18.432 MHz) is necessary

– FM carrier level calculation for automatic search algorithms

and carrier mute function

– high deviation FM-mono mode (max. deviation:

approx. 360 kHz)

2.2. Features of the DSP-Section

– flexible selection of audio sources to be processed

– digital input and output interfaces via I2S-Bus for external

DSP-processors, surround sound, ADR etc.

– digital interface to process ADR (Astra Digital Radio)

together with DRP 3510 A

– performance of all deemphasis systems including

adaptive Wegener Panda 1 without external components

or controlling

– digitally performed FM-identification decoding and dematrixing

– digital baseband processing: volume, bass, treble,

5-band equalizer, loudness, pseudostereo, and basewidth

enlargement

– simple controlling of volume, bass, treble, equalizer

etc.

– increased audio bandwidth for FM-Audio-signals

(20 Hz – 15 kHz, 1 dB)

2.3. Features of the Analog Section

– three selectable analog pairs of audio baseband inputs

(= three SCART inputs)

input level: 32 V RMS,

input impedance: .25 kW

– one selectable analog mono input (i.e. AM sound),

input level: 32 V RMS,

input impedance: .10 kW

– two high quality A/D converters, S/N-Ratio: .85 dB

– 20 Hz to 20 kHz Bandwidth for SCART-to-SCARTCopy

facilities

– MAIN (loudspeaker) and AUX (headphones): two

pairs of 4-fold oversampled D/A-converters

output level per channel: max. 1.4 V RMS

output resistance: max. 5 kW

S/N-Ratio: .85 dB at maximum volume

max. noise voltage in mute mode: 310 mV (BW: 20 Hz

...16 kHz)

– one pair of four-fold oversampled D/A-converters supplying

two selectable pairs of SCART-Outputs. Output

level per channel: max. 2 V RMS, output resistance:

max. 0.5 kW, S/N-Ratio: .85 dB

(20 Hz...16 kHz).

TOGHETHER WITH VIDEO PROCESSING THERE IS SOUND PROCESSING WITH MSP3400C

Multistandard Sound Processor

Release Notes: The hardware description in this

document is valid for the MSP 3400C – C8 and newer

codes. Revision bars indicate significant changes

to the previous version.

1. Introduction

The MSP 3400C is designed as single-chip Multistandard

Sound Processor for applications in analog and

digital TV sets, satellite receivers and video recorders.

The MSP-family, which is based on the MSP 2400, demonstrates

the progressive development towards highly

integrated multi-functional ICs.

The MSP 3400C, again, improves function integration:

The full TV sound processing, starting with analog

sound IF signal-in, down to processed analog AF-out, is

performed in a single chip. The IC is produced in 0.8 mm

CMOS technology, combined with high performance

digital signal processing.

The MSP 3400C 0.8 m CMOS version is fully pin and

software compatible to the 1.0 m MSP 3400 and MSP

3410. The main difference between the MSP 3400C and

the MSP 3410, consists of the MSP 3410 being able to

decode NICAM signals.

2. Features of the MSP 3400C:

2.1. Features of the Demodulator and Decoder

Sections

The MSP 3400C is designed to perform demodulation

of FM-mono TV sound and two carrier FM systems according

to the German or Korean terrestrial specs. With

to the German or Korean terrestrial specs. Withcertain constraints, it is also possible to do AM-demodulation

according to the SECAM system. Alternatively, the

satellite specs can be processed with the MSP 3400C.

For FM carrier detection in satellite operation, the AMdemodulation

offers a powerful feature to calculate the

carrier field strength, which can be used for automatic

search algorithms. So, the IC facilitates a first step towards

multistandard capability with its very flexible

application and may be used in TV-sets, satellite tuners,

and video recorders.

The MSP 3400C facilitates profitable multistandard capability,

offering the following advantages:

– two selectable analog inputs (TV and SAT-IF sources)

– Automatic Gain Control (AGC) for analog input: input

range: 0.14 – 3 Vpp

– integrated A/D converter for sound-IF inputs

– all demodulation and filtering is performed on chip and

is individually programmable

– no external filter hardware is required

– only one crystal clock (18.432 MHz) is necessary

– FM carrier level calculation for automatic search algorithms

and carrier mute function

– high deviation FM-mono mode (max. deviation:

approx. 360 kHz)

2.2. Features of the DSP-Section

– flexible selection of audio sources to be processed

– digital input and output interfaces via I2S-Bus for external

DSP-processors, surround sound, ADR etc.

– digital interface to process ADR (Astra Digital Radio)

together with DRP 3510 A

– performance of all deemphasis systems including

adaptive Wegener Panda 1 without external components

or controlling

– digitally performed FM-identification decoding and dematrixing

– digital baseband processing: volume, bass, treble,

5-band equalizer, loudness, pseudostereo, and basewidth

enlargement

– simple controlling of volume, bass, treble, equalizer

etc.

– increased audio bandwidth for FM-Audio-signals

(20 Hz – 15 kHz, 1 dB)

2.3. Features of the Analog Section

– three selectable analog pairs of audio baseband inputs

(= three SCART inputs)

input level: 32 V RMS,

input impedance: .25 kW

– one selectable analog mono input (i.e. AM sound),

input level: 32 V RMS,

input impedance: .10 kW

– two high quality A/D converters, S/N-Ratio: .85 dB

– 20 Hz to 20 kHz Bandwidth for SCART-to-SCARTCopy

facilities

– MAIN (loudspeaker) and AUX (headphones): two

pairs of 4-fold oversampled D/A-converters

output level per channel: max. 1.4 V RMS

output resistance: max. 5 kW

S/N-Ratio: .85 dB at maximum volume

max. noise voltage in mute mode: 310 mV (BW: 20 Hz

...16 kHz)

– one pair of four-fold oversampled D/A-converters supplying

two selectable pairs of SCART-Outputs. Output

level per channel: max. 2 V RMS, output resistance:

max. 0.5 kW, S/N-Ratio: .85 dB

(20 Hz...16 kHz).

PANASONIC TX-28XD3C QUINTRIX CHASSIS EURO-2M CHASSIS SMPS POWER Supply is based on TDA4600 (SIEMENS).

PANASONIC TX-28XD3C QUINTRIX CHASSIS EURO-2M Power supply Description based on TDA4601d (SIEMENS)

TDA4601 Operation. * The TDA4601 device is a single in line, 9 pin chip. Its predecessor was the TDA4600 device, the TDA4601 however has improved switching, better protection and cooler running. The (SIEMENS) TDA4601 power supply is a fairly standard parallel chopper switch mode type, which operates on the same basic principle as a line output stage. It is turned on and off by a square wave drive pulse, when switched on energy is stored in the chopper transformer primary winding in the form of a magnetic flux; when the chopper is turned off the magnetic flux collapses, causing a large back emf to be produced. At the secondary side of the chopper transformer this is rectified and smoothed for H.T. supply purposes. The advantage of this type of supply is that the high chopping frequency (20 to 70 KHz according to load) allows the use of relatively small H.T. smoothing capacitors making smoothing easier. Also should the chopper device go short circuit there is no H.T. output. In order to start up the TDA4601 I.C. an initial supply of 9v is required at pin 9, this voltage is sourced via R818 and D805 from the AC side of the bridge rectifier D801, also pin 5 requires a +Ve bias for the internal logic block. (On some sets pin 5 is used for standby switching). Once the power supply is up and running, the voltage on pin 9 is increased to 16v and maintained at this level by D807 and C820 acting as a half wave rectifier and smoothing circuit. PIN DESCRIPTIONS Pin 1 This is a 4v reference produced within the I.C. Pin 2 This pin detects the exact point at which energy stored in the chopper transformer collapses to zero via R824 and R825, and allows Q1 to deliver drive volts to the chopper transistor. It also opens the switch at pin 4 allowing the external capacitor C813 to charge from its external feed resistor R810. Pin 3 H.T. control/feedback via photo coupler D830. The voltage at this pin controls the on time of the chopper transistor and hence the output voltage. Normally it runs at Approximately 2v and regulates H.T. by sensing a proportion of the +4v reference at pin 1, offset by conduction of the photo coupler D830 which acts like a variable resistor. An increase in the conduction of transistor D830 and therefor a reduction of its resistance will cause a corresponding reduction of the positive voltage at Pin 3. A decrease in this voltage will result in a shorter on time for the chopper transistor and therefor a lowering of the output voltage and vice versa, oscillation frequency also varies according to load, the

higher the load the lower the frequency etc. should the voltage at pin 3 exceed 2.3v an internal flip flop is triggered causing the chopper drive mark space ratio to extend to 244 (off time) to 1 (on time), the chip is now in over volts trip condition. Pin 4 At this pin a sawtooth waveform is generated which simulates chopper current, it is produced by a time constant network R810 and C813. C813 charges when the chopper is on and is discharged when the chopper is off, by an internal switch strapping pin 4 to the internal +2v reference, see Fig 2. The amplitude of the ramp is proportional to chopper drive. In an overload condition it reaches 4v amplitude at which point chopper drive is reduced to a mark-space ratio of 13 to 1, the chip is then in over current trip. The I.C. can easily withstand a short circuit on the H.T. rail and in such a case the power supply simply squegs quietly. Pin 4 is protected by internal protection components which limit the maximum voltage at this pin to 6.5v. Should a fault occur in either of the time constant components, then the chopper transistor will probably be destroyed. Pin 5 This pin can be used for remote control on/off switching of the power supply, it is normally held at about +7v and will cause the chip to enter standby mode if it falls below 2v. Pin 6 Ground. Pin 7 Chopper switch off pin. This pin clamps the chopper drive voltage to 1.6v in order to switch off the chopper. Pin 8 Chopper base current output drive pin. Pin 9 L.T. pin, approximately 9v under start-up conditions and 16v during normal running, Current consumption of the I.C. is typically 135mA. The voltage at this pin must reach 6.7v in order for the chip to start-up.

higher the load the lower the frequency etc. should the voltage at pin 3 exceed 2.3v an internal flip flop is triggered causing the chopper drive mark space ratio to extend to 244 (off time) to 1 (on time), the chip is now in over volts trip condition. Pin 4 At this pin a sawtooth waveform is generated which simulates chopper current, it is produced by a time constant network R810 and C813. C813 charges when the chopper is on and is discharged when the chopper is off, by an internal switch strapping pin 4 to the internal +2v reference, see Fig 2. The amplitude of the ramp is proportional to chopper drive. In an overload condition it reaches 4v amplitude at which point chopper drive is reduced to a mark-space ratio of 13 to 1, the chip is then in over current trip. The I.C. can easily withstand a short circuit on the H.T. rail and in such a case the power supply simply squegs quietly. Pin 4 is protected by internal protection components which limit the maximum voltage at this pin to 6.5v. Should a fault occur in either of the time constant components, then the chopper transistor will probably be destroyed. Pin 5 This pin can be used for remote control on/off switching of the power supply, it is normally held at about +7v and will cause the chip to enter standby mode if it falls below 2v. Pin 6 Ground. Pin 7 Chopper switch off pin. This pin clamps the chopper drive voltage to 1.6v in order to switch off the chopper. Pin 8 Chopper base current output drive pin. Pin 9 L.T. pin, approximately 9v under start-up conditions and 16v during normal running, Current consumption of the I.C. is typically 135mA. The voltage at this pin must reach 6.7v in order for the chip to start-up. Semiconductor

circuit for supplying power to electrical equipment, comprising a

transformer having a primary winding connected, via a parallel

connection of a collector-emitter path of a transistor with a first

capacitor, to both outputs of a rectifier circuit supplied, in turn, by a

line a-c voltage; said transistor having a base controlled via a second

capacitor by an output of a control circuit acted upon, in turn by the

rectified a-c line voltage as actual value and by a reference voltage;

said transformer having a first secondary winding to which the

electrical equipment to be supplied is connected; said transformer

having a second secondary winding with one terminal thereof connected to

the emitter of said transistor and the other terminal thereof connected

to an anode of a first diode leading to said control circuit; said

transformer having a third secondary winding with one terminal thereof

connected, on the one hand, via a series connection of a third capacitor

with a first resistance, to the other terminal of said third secondary

winding and connected, on the other hand, to the emitter of said

transistor, the collector of which is connected to said primary winding;

a point between said third capacitor and said first resistance being

connected to the cathode of a second diode; said control circuit having

nine terminals including a first terminal delivering a reference voltage

and connected, via a voltage divider formed of a third and fourth

series-connected resistances, to the anode of said second diode; a

second terminal of said control circuit serving for zero-crossing

identification being connected via a fifth resistance to said cathode of

said second diode; a third terminal of said control-circuit serving as

actual value input being directly connected to a divider point of said

voltage divider forming said connection of said first terminal of said

control circuit to said anode of said second diode; a fourth terminal of

said control circuit delivering a sawtooth voltage being connected via a

sixth resistance to a terminal of said primary winding of said

transformer facing away from said transistor; a fifth terminal of said

control circuit serving as a protective input being connected, via a

seventh resistance to the cathode of said first diode and, through the

intermediary of said seventh resistance and an eighth resistance, to the

cathode of a third diode having an anode connected to an input of said

rectifier circuit; a sixth terminal of said control circuit carrying

said reference potential and being connected via a fourth capacitor to

said fourth terminal of said control circuit and via a fifth capacitor

to the anode of said second diode; a seventh terminal

of said control circuit establishing a potential for pulses controlling

said transistor being connected directly and an eighth terminal of said

control circuit effecting pulse control of the base of said transistor

being connected through the intermediary of a ninth resistance to said

first capacitor leading to the base of said transistor; and a ninth

terminal of said control circuit serving as a power supply input of said

control circuit being connected both to the cathode of said first diode

as well as via the intermediary of a sixth capacitor to a terminal of

said second secondary winding as well as to a terminal of said third

secondary winding.

Semiconductor

circuit for supplying power to electrical equipment, comprising a

transformer having a primary winding connected, via a parallel

connection of a collector-emitter path of a transistor with a first

capacitor, to both outputs of a rectifier circuit supplied, in turn, by a

line a-c voltage; said transistor having a base controlled via a second

capacitor by an output of a control circuit acted upon, in turn by the

rectified a-c line voltage as actual value and by a reference voltage;

said transformer having a first secondary winding to which the

electrical equipment to be supplied is connected; said transformer

having a second secondary winding with one terminal thereof connected to

the emitter of said transistor and the other terminal thereof connected

to an anode of a first diode leading to said control circuit; said

transformer having a third secondary winding with one terminal thereof

connected, on the one hand, via a series connection of a third capacitor

with a first resistance, to the other terminal of said third secondary

winding and connected, on the other hand, to the emitter of said

transistor, the collector of which is connected to said primary winding;

a point between said third capacitor and said first resistance being

connected to the cathode of a second diode; said control circuit having

nine terminals including a first terminal delivering a reference voltage

and connected, via a voltage divider formed of a third and fourth

series-connected resistances, to the anode of said second diode; a

second terminal of said control circuit serving for zero-crossing

identification being connected via a fifth resistance to said cathode of

said second diode; a third terminal of said control-circuit serving as

actual value input being directly connected to a divider point of said

voltage divider forming said connection of said first terminal of said

control circuit to said anode of said second diode; a fourth terminal of

said control circuit delivering a sawtooth voltage being connected via a

sixth resistance to a terminal of said primary winding of said

transformer facing away from said transistor; a fifth terminal of said

control circuit serving as a protective input being connected, via a

seventh resistance to the cathode of said first diode and, through the

intermediary of said seventh resistance and an eighth resistance, to the

cathode of a third diode having an anode connected to an input of said

rectifier circuit; a sixth terminal of said control circuit carrying

said reference potential and being connected via a fourth capacitor to

said fourth terminal of said control circuit and via a fifth capacitor

to the anode of said second diode; a seventh terminal

of said control circuit establishing a potential for pulses controlling

said transistor being connected directly and an eighth terminal of said

control circuit effecting pulse control of the base of said transistor

being connected through the intermediary of a ninth resistance to said

first capacitor leading to the base of said transistor; and a ninth

terminal of said control circuit serving as a power supply input of said

control circuit being connected both to the cathode of said first diode

as well as via the intermediary of a sixth capacitor to a terminal of

said second secondary winding as well as to a terminal of said third

secondary winding.Description:

The

invention relates to a blocking oscillator type switching power supply

for supplying power to electrical equipment, wherein the primary winding

of a transformer, in series with the emitter-collector path of a first

bipolar transistor, is connected to a d-c voltage obtained by

rectification of a line a-c voltage fed-in via two external supply

terminals, and a secondary winding of the transformer is provided for

supplying power to the electrical equipment, wherein, furthermore, the

first bipolar transistor has a base controlled by the output of a

control circuit which is acted upon in turn by the rectified a-c line

voltage as actual value and by a set-point transmitter, and wherein a

starting circuit for further control of the base of the first bipolar

transistor is provided.

The

invention relates to a blocking oscillator type switching power supply

for supplying power to electrical equipment, wherein the primary winding

of a transformer, in series with the emitter-collector path of a first

bipolar transistor, is connected to a d-c voltage obtained by

rectification of a line a-c voltage fed-in via two external supply

terminals, and a secondary winding of the transformer is provided for

supplying power to the electrical equipment, wherein, furthermore, the

first bipolar transistor has a base controlled by the output of a

control circuit which is acted upon in turn by the rectified a-c line

voltage as actual value and by a set-point transmitter, and wherein a

starting circuit for further control of the base of the first bipolar

transistor is provided.  Such a blocking oscillator switching

power supply is described in the German periodical, "Funkschau" (1975)

No. 5, pages 40 to 44. It is well known that the purpose of such a

circuit is to supply electronic equipment, for example, a television

set, with stabilized and controlled supply voltages. Essential for such

switching power supply is a power switching transistor i.e. a bipolar

transistor with high switching speed and high reverse voltage. This

transistor therefore constitutes an important component of the control

element of the control circuit. Furthermore, a high operating frequency

and a transformer intended for a high operating frequency are provided,

because generally, a thorough separation of the equipment to be supplied

from the supply naturally is desired. Such switching power supplies may

be constructed either for synchronized or externally controlled

operation or for non-synchronized or free-running operation. A blocking

converter is understood to be a switching power supply in which power is

delivered to the equipment to be supplied only if the switching

transistor establishing the connection between the primary coil of the

transformer and the rectified a-c voltage is cut off. The power

delivered by the line rectifier to the primary coil of the transformer

while the switching transistor is open, is interim-stored in the

transformer and then delivered to the consumer on the secondary side of

the transformer with the switching transistor cut off.

Such a blocking oscillator switching

power supply is described in the German periodical, "Funkschau" (1975)

No. 5, pages 40 to 44. It is well known that the purpose of such a

circuit is to supply electronic equipment, for example, a television

set, with stabilized and controlled supply voltages. Essential for such

switching power supply is a power switching transistor i.e. a bipolar

transistor with high switching speed and high reverse voltage. This

transistor therefore constitutes an important component of the control

element of the control circuit. Furthermore, a high operating frequency

and a transformer intended for a high operating frequency are provided,

because generally, a thorough separation of the equipment to be supplied

from the supply naturally is desired. Such switching power supplies may

be constructed either for synchronized or externally controlled

operation or for non-synchronized or free-running operation. A blocking

converter is understood to be a switching power supply in which power is

delivered to the equipment to be supplied only if the switching

transistor establishing the connection between the primary coil of the

transformer and the rectified a-c voltage is cut off. The power

delivered by the line rectifier to the primary coil of the transformer

while the switching transistor is open, is interim-stored in the

transformer and then delivered to the consumer on the secondary side of

the transformer with the switching transistor cut off. In the blocking converter described in the aforementioned reference in the literature, "Funkschau" (1975), No. 5, Pages 40 to 44, the power switching transistor is connected in the manner defined in the introduction to this application. In addition, a so-called starting circuit is provided. Because several diodes are generally provided in the overall circuit of a blocking oscillator according to the definition provided in the introduction hereto, it is necessary, in order not to damage these diodes, that due to the collector peak current in the case of a short circuit, no excessive stress of these diodes and possibly existing further sensitive circuit parts can occur.

Considering

the operation of a blocking oscillator, this means that, in the event of

a short circuit, the number of collector current pulses per unit time

must be reduced. For this purpose, a control and regulating circuit is provided.

Simultaneously, a starting circuit must bring the blocking converter

back to normal operation when the equipment is switched on, and after

disturbances, for example, in the event of a short circuit. The starting

circuit shown in the literature reference "Funkschau" on Page 42

thereof, differs to some extent already from the conventional d-c

starting circuits. It is commonly known for all heretofore known

blocking oscillator circuits, however, that a thyristor or an equivalent

circuit replacing the thyristor is essential for the operation of the

control circuit.

Considering

the operation of a blocking oscillator, this means that, in the event of

a short circuit, the number of collector current pulses per unit time

must be reduced. For this purpose, a control and regulating circuit is provided.

Simultaneously, a starting circuit must bring the blocking converter

back to normal operation when the equipment is switched on, and after

disturbances, for example, in the event of a short circuit. The starting

circuit shown in the literature reference "Funkschau" on Page 42

thereof, differs to some extent already from the conventional d-c

starting circuits. It is commonly known for all heretofore known

blocking oscillator circuits, however, that a thyristor or an equivalent

circuit replacing the thyristor is essential for the operation of the

control circuit. It is accordingly an object of the invention to provide another starting circuit. It is a further object of the invention to provide a possible circuit for the control circuit which is particularly well suited for this purpose. It is yet another object of the invention to provide such a power supply which is assured of operation over the entire range of line voltages from 90 to 270 V a-c, while the secondary voltages and secondary load variations between no-load and short circuit are largely constant.

With the foregoing and other objects in view, there is

provided, in accordance with the invention, a blocking oscillator-type

switching power supply for supplying power to electrical equipment

wherein a primary winding of a transformer, in series with an

emitter-collector path of a first bipolar transistor, is connected to a

d-c voltage obtained by rectification of a line a-c voltage fed-in via

two external supply terminals, a secondary winding of the transformer

being connectible to the electrical equipment for supplying power

thereto, the first bipolar transistor having a base controlled by the

output of a control circuit acted upon, in turn, by the rectified a-c

line voltage as actual value and by a set-point transmitter, and

including a starting circuit for further control of the base of the

first bipolar transistor, including a first diode in the starting

circuit having an anode directly connected to one of the supply

terminals supplied by the a-c line voltage and a cathode connected via a

resistor to an input serving to supply power to the control circuit,

the input being directly connected to a cathode of a second diode, the

second diode having an anode connected to one terminal of another

secondary winding of the transformer, the other secondary winding having

another terminal connected to the emitter of the first bipolar

transmitter.

With the foregoing and other objects in view, there is

provided, in accordance with the invention, a blocking oscillator-type

switching power supply for supplying power to electrical equipment

wherein a primary winding of a transformer, in series with an

emitter-collector path of a first bipolar transistor, is connected to a

d-c voltage obtained by rectification of a line a-c voltage fed-in via

two external supply terminals, a secondary winding of the transformer

being connectible to the electrical equipment for supplying power

thereto, the first bipolar transistor having a base controlled by the

output of a control circuit acted upon, in turn, by the rectified a-c

line voltage as actual value and by a set-point transmitter, and

including a starting circuit for further control of the base of the

first bipolar transistor, including a first diode in the starting

circuit having an anode directly connected to one of the supply

terminals supplied by the a-c line voltage and a cathode connected via a

resistor to an input serving to supply power to the control circuit,

the input being directly connected to a cathode of a second diode, the

second diode having an anode connected to one terminal of another

secondary winding of the transformer, the other secondary winding having

another terminal connected to the emitter of the first bipolar

transmitter.  In

accordance with another feature of the invention, there is provided a

second bipolar transistor having the same conduction type as that of the

first bipolar transistor and connected in the starting circuit with the

base thereof connected to a cathode of a semiconductor diode, the

semiconductor diode having an anode connected to the emitter of the

first bipolar transistor, the second bipolar transistor having a

collector connected via a resistor to a cathode of the first diode in

the starting circuit, and having an emitter connected to the input

serving to supply power to the control circuit and also connected to the

cathode of the second diode which is connected to the other secondary

winding of the transformer.

In

accordance with another feature of the invention, there is provided a

second bipolar transistor having the same conduction type as that of the

first bipolar transistor and connected in the starting circuit with the

base thereof connected to a cathode of a semiconductor diode, the

semiconductor diode having an anode connected to the emitter of the

first bipolar transistor, the second bipolar transistor having a

collector connected via a resistor to a cathode of the first diode in

the starting circuit, and having an emitter connected to the input

serving to supply power to the control circuit and also connected to the

cathode of the second diode which is connected to the other secondary

winding of the transformer. In accordance with a further feature of the invention, the base of the second bipolar transistor is connected to a resistor and via the latter to one pole of a first capacitor, the anode of the first diode being connected to the other pole of the first capacitor.

In accordance with an added feature of the invention, the input serving to supply power to the control circuit is connected via a second capacitor to an output of a line rectifier, the output of the line rectifier being directly connected to the emitter of the first bipolar transistor.

In accordance with an additional feature of the invention, the other secondary winding is connected at one end to the emitter of the first bipolar transistor and to a pole of a third capacitor, the third capacitor having another pole connected, on the one hand, via a resistor, to the other end of the other secondary winding and, on the other hand, to a cathode of a third diode, the third diode having an anode connected via a potentiometer to an actual value input of the control circuit and, via a fourth capacitor, to the emitter of the first bipolar transistor.

In accordance with yet another feature of the invention, the control circuit has a control output connected via a fifth capacitor to the base of the first bipolar transistor for conducting to the latter control pulses generated in the control circuit.

In accordance with a concomitant feature of the invention, there is provided a sixth capacitor shunting the emitter-collector path of the first transistor.

Other features which are considered as characteristic for the invention are set forth in the appended claim.

Although

the invention is illustrated and described herein as embodied in a

blocking oscillator type switching power supply, it is nevertheless not

intended to be limited to the details shown, since various modifications

and structural changes may be made therein without departing from the

spirit of the invention and within the scope and range of equivalents of

the claims.

Although

the invention is illustrated and described herein as embodied in a

blocking oscillator type switching power supply, it is nevertheless not

intended to be limited to the details shown, since various modifications

and structural changes may be made therein without departing from the

spirit of the invention and within the scope and range of equivalents of

the claims. The construction and method of operation of the invention, however, together with additional objects and advantages thereof will be best understood from the following description of specific embodiments when read in connection with the accompanying drawings, in which:

FIGS. 1 and 2 are circuit diagrams of the blocking oscillator type switching power supply according to the invention; and

FIG. 3 is a circuit diagram of the control unit RS of FIGS. 1 and 2.

Referring now to the drawing and, first, particularly to FIG. 1 thereof, there is shown a rectifier circuit G in the form of a bridge current, which is acted upon by a line input represented by two supply terminals 1' and 2'. Rectifier outputs 3' and 4' are shunted by an emitter-collector path of an NPN power transistor T1 i.e. t

he

series connection of the so-called first bipolar transistor referred to

hereinbefore with a primary winding I of a transformer Tr. Together

with the inductance of the transformer Tr, the capacitance C1 determines

the frequency and limits the opening voltages of the switch embodied by

the first transistor T1. A capacitance C2, provided between the base of

the first transistor T1 and the control output 7,8 of a control circuit

RS, separates the d-c potentials of the control or regulating circuit

RS and the switching transistor T1 and serves for addressing this

switching transistor T1 with pulses. A resistor R1 provided at the

control output 7,8 of the control circuit RS is the negative-feedback

resistor of both output stages of the control circuit RS. It determines

the maximally possible output pulse current of the control circuit RS. A

secondary winding II of the transformer Tr takes over the power supply

of the control circuit, in steady state operation, via the diode D1. To

this end, the cathode of this diode D1 is directly connected to a power

supply input 9 of the control circuit RS, while the anode thereof is

connected to one terminal of the secondary winding II. The other

terminal of the secondary winding II is connected to the emitter of the

power switching transistor T1.

he

series connection of the so-called first bipolar transistor referred to

hereinbefore with a primary winding I of a transformer Tr. Together

with the inductance of the transformer Tr, the capacitance C1 determines

the frequency and limits the opening voltages of the switch embodied by

the first transistor T1. A capacitance C2, provided between the base of

the first transistor T1 and the control output 7,8 of a control circuit

RS, separates the d-c potentials of the control or regulating circuit

RS and the switching transistor T1 and serves for addressing this

switching transistor T1 with pulses. A resistor R1 provided at the

control output 7,8 of the control circuit RS is the negative-feedback

resistor of both output stages of the control circuit RS. It determines

the maximally possible output pulse current of the control circuit RS. A

secondary winding II of the transformer Tr takes over the power supply

of the control circuit, in steady state operation, via the diode D1. To

this end, the cathode of this diode D1 is directly connected to a power

supply input 9 of the control circuit RS, while the anode thereof is

connected to one terminal of the secondary winding II. The other

terminal of the secondary winding II is connected to the emitter of the

power switching transistor T1.The cathode of the diode D1 and, therewith, the power supply terminal 9 of the control circuits RS are furthermore connected to one pole of a capacitor C3, the other pole of which is connected to the output 3' of the rectifier G. The capacitance of this capacitor C3 thereby smoothes the positive half-wave pulses and serves simultaneously as an energy storage device during the starting period. Another secondary windi

ng

III of the transformer Tr is connected by one of the leads thereof

likewise to the emitter of the first transistor T1, and by the other

lead thereof via a resistor R2, to one of the poles of a further

capacitor C4, the other pole of which is connected to the

first-mentioned lead of the other secondary winding III. This second

pole of the capacitor C4 is simultaneously connected to the output 3' of

the rectifier circuit G and, thereby, via the capacitor C3, to the

cathode of the diode D1 driven by the secondary winding II of the

transformer Tr as well as to the power supply input 9 of the control

circuit RS and, via a resistor R9, to the cathode of a second diode D4.

The second pole of the capacitor C4 is simultaneously connected directly

to the terminal 6 of the control circuit RS and, via a further

capacitor C 6, to the terminal 4 of the control circuit RS as well as,

additionally, via the resistor R6, to the other output 4' of the

rectifier circuit G. The other of the poles of the capacitor C4 acted

upon by the secondary winding II is connected via a further capacitor C5

to a node, which is connected on one side thereof, via a variable

resistor R4, to the terminals 1 and 3 of the control circuit RS, with

the intermediary of a fixed resistor R5 in the case of the terminal 1.

On the other side of the node, the latter and, therefore, the capacitor

C5 are connected to the anode of a third diode D2, the cathode of which

is connected on the one hand, to the resistor R2 mentioned hereinbefore

and leads to the secondary winding III of the transformer Tr and, on the

other hand, via a resistor R3 to the terminal 2 of the control circuit

RS.

ng

III of the transformer Tr is connected by one of the leads thereof

likewise to the emitter of the first transistor T1, and by the other

lead thereof via a resistor R2, to one of the poles of a further

capacitor C4, the other pole of which is connected to the

first-mentioned lead of the other secondary winding III. This second

pole of the capacitor C4 is simultaneously connected to the output 3' of

the rectifier circuit G and, thereby, via the capacitor C3, to the

cathode of the diode D1 driven by the secondary winding II of the

transformer Tr as well as to the power supply input 9 of the control

circuit RS and, via a resistor R9, to the cathode of a second diode D4.

The second pole of the capacitor C4 is simultaneously connected directly

to the terminal 6 of the control circuit RS and, via a further

capacitor C 6, to the terminal 4 of the control circuit RS as well as,

additionally, via the resistor R6, to the other output 4' of the

rectifier circuit G. The other of the poles of the capacitor C4 acted

upon by the secondary winding II is connected via a further capacitor C5

to a node, which is connected on one side thereof, via a variable

resistor R4, to the terminals 1 and 3 of the control circuit RS, with

the intermediary of a fixed resistor R5 in the case of the terminal 1.

On the other side of the node, the latter and, therefore, the capacitor

C5 are connected to the anode of a third diode D2, the cathode of which

is connected on the one hand, to the resistor R2 mentioned hereinbefore

and leads to the secondary winding III of the transformer Tr and, on the

other hand, via a resistor R3 to the terminal 2 of the control circuit

RS.The nine terminals of the control circuit RS have the following purposes or functions:

Terminal 1 supplies the internally generated reference voltage to ground i.e. the nominal or reference value required for the control or regulating process;

Terminal 2 serves as input for the oscillations provided by the secondary winding III, at the zero point of which, the pulse start of the driving pulse takes place;

Terminal 3 is the control input, at which the existing actual value is communicated to the control circuit RS, that actual value being generated by the rectified oscillations at the secondary winding III;

Terminal 4 is responsive to the occurrence of a maximum excursion i.e. when the largest current flows through the first transistor T1 ;

Terminal 5 is a protective input which responds if the rectified line voltage drops too sharply; Terminal 6 serves for the power supply of the control process and, indeed, as ground terminal;

Terminal 7 supplies the d-c component required for charging the coupling capacitor C2 leading to the base of the first transistor T1 ;

Terminal 8 supplies the control pulse required for the base of the first transistor T1 ; and

Terminal 9 serves as the first terminal of the power supply of the control circuit RS.

Further details of the control circuit RS are described hereinbelow.

The capacity C3 smoothes the positive half-wave pulses which are provided by the secondary winding II, and simultaneously serves as an energy storage device during the starting time. The secondary winding III generates the control voltage and is simultaneously used

as

feedback. The time delay stage R2 /C4 keeps harmonics and fast

interference spikes away from the control circuit RS. The resistor R3 is

provided as a voltage divider for the second terminal of the control

circuit RS. The diode D2 rectifies the control pulses delivered by the

secondary winding III. The capacity C5 smoothes the control voltage. A

reference voltage Uref, which is referred to ground i.e. the potential

of terminal 6 is present at the terminal 1 of the control circuit RS.

The resistors R4 and R5 form a voltage divider of the input-difference

control amplifier at the terminal 3. The desired secondary voltage can

be set manually via the variable resistor R4. A time-delay stage R6 /C6

forms a sawtooth rise which corresponds to the collector current rise of

the first bipolar transistor T1 via the primary winding I of the

transformer Tr. The sawtooth present at the terminal 4 of the control

circuit RS is limited there between the reference voltage 2 V and 4 V.

The voltage divider R7 /R8 (FIG. 2), brings to the terminal 5 of the

control circuit RS the enabling voltage for the drive pulse at the

output 8 of the control circuit RS.

as

feedback. The time delay stage R2 /C4 keeps harmonics and fast

interference spikes away from the control circuit RS. The resistor R3 is

provided as a voltage divider for the second terminal of the control

circuit RS. The diode D2 rectifies the control pulses delivered by the

secondary winding III. The capacity C5 smoothes the control voltage. A

reference voltage Uref, which is referred to ground i.e. the potential

of terminal 6 is present at the terminal 1 of the control circuit RS.

The resistors R4 and R5 form a voltage divider of the input-difference

control amplifier at the terminal 3. The desired secondary voltage can

be set manually via the variable resistor R4. A time-delay stage R6 /C6

forms a sawtooth rise which corresponds to the collector current rise of

the first bipolar transistor T1 via the primary winding I of the

transformer Tr. The sawtooth present at the terminal 4 of the control

circuit RS is limited there between the reference voltage 2 V and 4 V.

The voltage divider R7 /R8 (FIG. 2), brings to the terminal 5 of the

control circuit RS the enabling voltage for the drive pulse at the

output 8 of the control circuit RS.The diode D4, together with the resistor R9 in cooperation with the diode D1 and the secondary winding II, forms the starting circuit provided, in accordance with the invention. The operation thereof is as follows:

After the switching power supply is switched on, d-c voltages build up at the collector of the switching transistor T1 and at the input 4 of the control circuit RS, as a function in time of the predetermined time constants. The positive sinusoidal half-waves charge the capacitor C3 via the starting diode D4 and the starting resistor R9 in dependence upon the time constant R9.C3. Via the protective input terminal 5 and the resisto

r

R11 not previously mentioned and forming the connection between the

resistor R9 and the diode D1, on the one hand, and the terminal 5 of the

control circuit RS, on the other hand, the control circuit RS is biased

ready for switching-on, and the capacitor C2 is charged via the output

7. When a predetermined voltage value at the capacitor C3 or the power

supply input 9 of the control circuit RS, respectively, is reached, the

reference voltage i.e. the nominal value for the operation of the

control voltage RS, is abruptly formed, which supplies all stages of the

control circuit and appears at the output 1 thereof. Simultaneously,

the switching transistor T1 is switched into conduction via the output

8. The switching of the transistor T1 at the primary winding T of the

transformer Tr is transformed to the second secondary winding II, the

capacity C3 being thereby charged up again via the diode D1. If

sufficient energy is stored in the capacitor C3 and if the re-charge via

the diode D1 is sufficient so that the voltage at a supply input 9 does

not fall below the given minimum operating voltage, the switching power

supply then remains connected, so that the starting process is

completed. Otherwise, the starting process described is repeated several

times.

r

R11 not previously mentioned and forming the connection between the

resistor R9 and the diode D1, on the one hand, and the terminal 5 of the

control circuit RS, on the other hand, the control circuit RS is biased

ready for switching-on, and the capacitor C2 is charged via the output

7. When a predetermined voltage value at the capacitor C3 or the power

supply input 9 of the control circuit RS, respectively, is reached, the

reference voltage i.e. the nominal value for the operation of the

control voltage RS, is abruptly formed, which supplies all stages of the

control circuit and appears at the output 1 thereof. Simultaneously,

the switching transistor T1 is switched into conduction via the output

8. The switching of the transistor T1 at the primary winding T of the

transformer Tr is transformed to the second secondary winding II, the

capacity C3 being thereby charged up again via the diode D1. If

sufficient energy is stored in the capacitor C3 and if the re-charge via

the diode D1 is sufficient so that the voltage at a supply input 9 does

not fall below the given minimum operating voltage, the switching power

supply then remains connected, so that the starting process is

completed. Otherwise, the starting process described is repeated several

times.In FIG. 2, there is shown a further embodiment of the circuit for a blocking oscillator type switching power supply, according to the invention, as shown in FIG. 1. Essential for this circuit of FIG. 2 is the presence of a second bipolar transistor T2 of the type of the first bipolar transistor T1 (i.e. in the embodiments of the invention, an npn-transistor), which forms a further component of the starting circuit and is connected with the collector-emitter path thereof between the resistor R9 of the starting circuit and the current supply input 9 of the control circuit RS. The base of this second transistor T2 is connected to a node which leads, on the one hand, via a resistor R10 to one electrode of a capacitor C7, the other electrode of which is connected to the anode of the diode D4 of the starting circuit and, accordingl

y,

to the terminal 1' of the supply input of the switching power supply G.

On the other hand, the last-mentioned node and, therefore, the base of

the second transistor T2 are connected to the cathode of a Zener diode

D3, the anode of which is connected to the output 3' of the rectifier G

and, whereby, to one pole of the capacitor C3, the second pole of which

is connected to the power supply input 9 of the control circuit RS as

well as to the cathode of the diode D1 and to the emitter of the second

transistor T2. In other respects, the circuit according to FIG. 2

corresponds to the circuit according to FIG. 1 except for the resistor

R11 which is not necessary in the embodiment of FIG. 2, and the missing

connection between the resistor R9 and the cathode of the diode D1,

respectively, and the protective input 5 of the control circuit RS.

y,

to the terminal 1' of the supply input of the switching power supply G.

On the other hand, the last-mentioned node and, therefore, the base of

the second transistor T2 are connected to the cathode of a Zener diode

D3, the anode of which is connected to the output 3' of the rectifier G

and, whereby, to one pole of the capacitor C3, the second pole of which

is connected to the power supply input 9 of the control circuit RS as

well as to the cathode of the diode D1 and to the emitter of the second

transistor T2. In other respects, the circuit according to FIG. 2

corresponds to the circuit according to FIG. 1 except for the resistor

R11 which is not necessary in the embodiment of FIG. 2, and the missing

connection between the resistor R9 and the cathode of the diode D1,

respectively, and the protective input 5 of the control circuit RS.Regarding the operation of the starting circuit according to FIG. 2,

it can be stated that the positive sinusoidal half-wave of the line

voltage, delayed by the time delay stage C7, R10 drives the base of the

transistor T2 in the starting circuit. The amplitude is limited by the

diode D3 which is provided for overvoltage protection of the control

circuit RS and which is preferably incorporated as a Zener diode. The

second transistor T2 is switched into conduction. The capacity C3 is

charged, via the serially connected diode D4 and the resistor R9 and the

collector-emitter path of the transistor T2, as soon as the voltage

between the terminal 9 and the terminal 6 of the control circuit RS i.e.

the voltage U9, meets the condition U9 <[UDs -UBE (T2)].

it can be stated that the positive sinusoidal half-wave of the line

voltage, delayed by the time delay stage C7, R10 drives the base of the

transistor T2 in the starting circuit. The amplitude is limited by the

diode D3 which is provided for overvoltage protection of the control

circuit RS and which is preferably incorporated as a Zener diode. The

second transistor T2 is switched into conduction. The capacity C3 is

charged, via the serially connected diode D4 and the resistor R9 and the

collector-emitter path of the transistor T2, as soon as the voltage

between the terminal 9 and the terminal 6 of the control circuit RS i.e.

the voltage U9, meets the condition U9 <[UDs -UBE (T2)].Because of the time constant R9.C3, several positive half-waves are necessary in order to increase the voltage U9 at the supply terminal 9 of the control circuit RS to such an extent that the control circuit RS is energized. During the negative sine half-wave, a partial energy chargeback takes place from the capacitor C3 via the emitter-base path of the transistor T2 of the starting circuit and via the resistor R10 and the capacitor C7, respectively, into the supply network. At approximately 2/3 of the voltage U9, which is limited by the diode D3, the control circuit RS is switched on. At the terminal 1 thereof, the reference voltage Uref then appears. In addition, the voltage divider R5 /R4 becomes effective. At the terminal 3, the control amplifier receives the voltage forming the actual value, while the first bipolar transistor T1 of the blocking-oscillator type switching power supply is addressed pulsewise via the terminal 8.

Because the capacitor C6 is charged via the resistor R6, a higher voltage than Uref is present at the terminal 4 if the control circuit RS is activated. The control voltage then discharges the capacitor C6 via the terminal 4 to half the value of the reference voltage Uref, and immediately cuts off the addressing input 8 of the control circuit RS. The first driving pulse of the switching transistor T1 is thereby limited to a minimum of time. The power for switching-on the control circuit RS and for driving the transistor T1 is supplied by the capacitor C3. The voltage U9 at the capacitor C3 then drops. If the voltage U9 drops below the switching-off voltage value of the control circuit RS, the latter is then inactivated. The next positive sine half-wave would initiate the starting process again.

By switching the transistor T1, a voltage is transformed in the secondary winding II of the transformer Tr. The positive component is rectified by the diode D1, recharing of the capacitor C3 being thereby provided. The voltage U9 at the output 9 does not, therefore, drop below the minimum value required for the operation of the control circuit RS, so that the control circuit RS remains activated. The power supply continues to operate in the rhythm of the existing conditions. In operation, the voltage U9 at the supply terminal 9 of the control circuit RS has a value which meets the condition U9 >[UDs -UBE (T2)], so that the transistor T2 of the starting circuit remains cut off.

For the internal layout of the control circuit RS, the construction shown, in particular, from FIG. 3 is advisable. This construction is realized, for example, in the commercially available type TDA 4600 (Siemens AG).

The block diagram of the control circuit according to FIG. 3

shows

the power supply thereof via the terminal 9, the output stage being

supplied directly whereas all other stages are supplied via Uref. In the

starting circuit, the individual subassemblies are supplied with power

sequentially. The d-c output voltage potential of the base current gain

i.e. the voltage for the terminal 8 of the control circuit RS, and the

charging of the capacitor C2 via the terminal 7 are formed even before

the reference voltage Uref appears. Variations of the supply voltage U9

at terminal 9 and the power fluctuations at the terminal 8/terminal 7

and at the terminal 1 of the control circuit RS are leveled or smoothed

out by the voltage control. The temperature sensitivity of the control

circuit RS and, in particular, the uneven heating of the output and

input stages and input stages on the semiconductor chip containing the

control circuit in monolithically integrated form are intercepted by the

temperature compensation provided. The output values are constant in a

specific temperature range. The message for blocking the output stage,

if the supply voltage at the terminal 9 is too low, is given also by

this subassembly to a provided control logic.

shows

the power supply thereof via the terminal 9, the output stage being

supplied directly whereas all other stages are supplied via Uref. In the

starting circuit, the individual subassemblies are supplied with power

sequentially. The d-c output voltage potential of the base current gain

i.e. the voltage for the terminal 8 of the control circuit RS, and the

charging of the capacitor C2 via the terminal 7 are formed even before

the reference voltage Uref appears. Variations of the supply voltage U9

at terminal 9 and the power fluctuations at the terminal 8/terminal 7

and at the terminal 1 of the control circuit RS are leveled or smoothed

out by the voltage control. The temperature sensitivity of the control

circuit RS and, in particular, the uneven heating of the output and

input stages and input stages on the semiconductor chip containing the

control circuit in monolithically integrated form are intercepted by the

temperature compensation provided. The output values are constant in a

specific temperature range. The message for blocking the output stage,

if the supply voltage at the terminal 9 is too low, is given also by

this subassembly to a provided control logic.The outer voltage divider of the terminal 1 via the r

esistors

R5 and R4 to the control tap U forms, via terminal 3, the variable side

of the bridge for the control amplifier formed as a differential

amplifier. The fixed bridge side is formed by the reference voltage Uref

via an internal voltage divider. Similarly formed are circuit portions

serving for the detection of an overload short circuit and circuit

portions serving for the "standby" no-load detection, which can be

operated likewise via terminal 3.

esistors

R5 and R4 to the control tap U forms, via terminal 3, the variable side

of the bridge for the control amplifier formed as a differential

amplifier. The fixed bridge side is formed by the reference voltage Uref

via an internal voltage divider. Similarly formed are circuit portions

serving for the detection of an overload short circuit and circuit

portions serving for the "standby" no-load detection, which can be

operated likewise via terminal 3.Within a provided trigger circuit, the driving pulse length is determined as a function of the sawtooth rise at the terminal 4, and is transmitted to the control logic. In the control logic, the commands of the trigger circuit are processed. Through the zero-crossing identification at input 2 in the control circuit RS, the control logic is enabled to start the control input only at the zero point of the frequency oscillation. If the voltages at the terminal 5 and at the terminal 9 are too low, the control logic blocks the output amplifier at the terminal 8. The output amplifier at the terminal 7 which is responsible for the base charge in the capacitor C2, is not touched thereby.

The base current gain for the transistor T1 i.e. for the first transistor in accordance with the definition of the invention, is formed by two amplifiers which mutually operate on the capacitor C2. The roof inclination of the base driving current for the transistor T1 is impressed by the collector current simulation at the terminal 4 to the amplifier at the terminal 8. The control pulse for the transistor T1 at the terminal 8 is always built up to the potential present at the terminal 7. The amplifier working into the terminal 7 ensures that each new switching pulse at the terminal 8 finds the required base level at terminal 7.

Supplementing the comments regarding FIG. 1, it should also be mentioned that the cathode of the diode D1 connected by the anode thereof to the one end of the secondary winding II of the transformer Tr is connected via a resistor R11 to the protective input 5 of the control circuit RS whereas, in the circuit according to FIG. 2, the protective input 5 of the control circuit RS is supplied via a voltage divider R8, R7 directly from the output 3', 4' of the rectifier G delivering the rectified line a-c voltage, and which obtains the voltage required for executing its function. It is evident that the first possible manner of driving the protective input 5 can be used also in the circuit according to FIG. 2, and the second possibility also in a circuit in accordance with FIG. 1.

The control circuit RS which is shown in FIG. 3 and is realized in detail by the building block TDA 4600 and which is particularly well suited in conjunction with the blocking oscillator type switching power supply according to the invention has 9 terminals 1-9, which have the following characteristics, as has been explained in essence hereinabove:

Terminal 1 delivers a reference voltage Uref which serves as the constant-current source of a voltage divider R5.R4 which supplies the required d-c voltages for the differential amplifiers provided for the functions control, overload detection, short-circuit detection and "standby"-no load detection. The dividing point of the voltage divider R5 -R4 is connected to the terminal 3 of the control circuit RS. The terminal 3 provided as the control input of RS is controlled in the manner described hereinabove as input for the actual value of the voltage to be controlled or regulated by the secondary winding III of the transformer Tr. With this input, the lengths of the control pulses for the switching transistor T1 are determined.

Via the input provided by the terminal 2 of the control circuit RS, the zero-point identification in the control circuit is addressed for detecting the zero-point o

f

the oscillations respectively applied to the terminal 2. If this

oscillation changes over to the positive part, then the addressing pulse

controlling the switching transistor T1 via the terminal 8 is released

in the control logic provided in the control circuit.

f

the oscillations respectively applied to the terminal 2. If this

oscillation changes over to the positive part, then the addressing pulse

controlling the switching transistor T1 via the terminal 8 is released