. BS990 MAIN CHASSIS DESCRIPTION

. BS990 MAIN CHASSIS DESCRIPTIONGENERAL This chassis was developed to be employed with stereo and mono audio decoder circuits and to drive CRT with deflection angles of 110°, with E-W and N-S pin cushion correction. The circuit can handle normal reception for B/G standards and standards I and OIRT, PAL and SECAM/PAL, with few modifications. The tuning system, completely automatic, is a frequency synthesizer with remote control and memorization of 40 programs. The remote control allows the control of all TV function, teletext, mono and/or stereo sound and, moreover, PIP function. On front control panel, instead, there are only push- button required for emergency operations of the TV set. This chassis is completed with SCART (PERITELEVISION) socket and can, also, handle teletext module in CCT (Computer Cont- rolled Teletext) system and PIP (Picture In Picture) module. The stereo sets are normally equipped with teletext module.

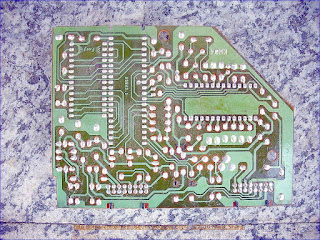

SELECO 25SS653 CHASSIS BS990.0 CHASSIS

BLOCK DIAGRAM DESCRIPTION

BLOCK DIAGRAM DESCRIPTION

TUNER The signal coming from the antenna socket, is converted in the tuner section, after filtering and amplification, in the IF (Intermediate Frequency) signal. The varicap voltage, to tune the incoming signal, is obtained from a frequency synthesizer system.

SELECO 25SS653 CHASSIS BS990.0 VIDEO CIRCUIT BLOCK

In this block is coming the IF Signal from the tuner, trough an impedance adapter amplifier,that, after passing an SAW (Surface Acoustic Wave) filter (giving proper selectivity and attenuation to the carriers); the Signal is applied to the IC TDA4504 performing: --IF signal amplification. - IF signal detection. ~ Supply video signal to the Scart socket. - Supply IF audio signal to the audio circuits. - Supply video signal to the teletext circuit. ~ Supply the signal to the video/chroma circuits. - Selection of the signal coming from antenna/scart socket. ~ Supply the AGC and delayed AGC voltages. - Supply the sync separation circuit. - Generation of horizontal and vertical sync. - Supply of muting voltage. - Generation of vertical signal for the vertical output stage. - Generation of the sand-castle signal. . - Generation of the horizontal signal to drive the horizontal output stage.

VIDEO/CHROMA CIRCUIT BLOCK The video/chroma circuits elaborates the 1 V p.p. incoming composite video signal to obtain the three R -G - B signals necessary to drive the power output amplifiers connected to the picture tube. The other main functions related to this block are: - Black level control on the three guns. - Beam current peack limiter. - Fast blanking for signals coming from Scart socket or teletext circuit. - Analog controls for brightness, contrast -and colour saturation. - Secam interface via a proper transcoder. - Luminance delay line drive. - Chroma signals decoding.

R - G - B OUTPUT BLOCK This circuit performs the following functions: - R-G - B signals amplification. - Signal amplification to obtain , automatically, the exact working point of R -~- G-B output amplifiers.

- Tracking amplification for best colour temperature high/low brightness.

SECAM/PAL TRANSCODER BLOCK This block recognize and demodulates SECAM colour signal and, subsequently, perform PAL codification to permit normal elaboration in video(chroma PAL circuits. POWER SUPPLY BLOCK The power supply block is composed of: - Main filter circuit. - Automatic CRT degaussing circuit. - Full wave rectifier with normal filtering. - Switch mode power supply with electrical separation from the mains and stabilisation against mains and load varia- tions. - Stand-by circuit. - Secondary winding outputs for 145 V; 24,5 V; 12,6 V; 15,5 V; 7 V and 5 V.

SELECO 25SS653 CHASSIS BS990.0 HORIZONTAL DEFLECTION BLOCK This block is composed of a power output stage, with proper linearity correction, to drive the horizontal beam deflection; EHT generation; focusing voltage generation (from which G2 bias is derived) and, from EHT winding, beam current reading for beam limiter circuits. The output stages power supply voltage is obtained adding up the normal power supply voltage with fly-back rectified voltage. From EHT secondary windings are, also, obtained: - CRT filament voltage. - Various voltages to supply other circuits.

SELECO 25SS653 CHASSIS BS990.0 VERTICAL DEFLECTION BLOCK The vertical saw-tooth coming from the video circuit. is amplified in this block to obtain proper current for vertical deflection. This circuit is composed, also of fly-back generation, amplitude adjustment, linearity and shift compensation for CRT and related components tolerances.

SELECO 25SS653 CHASSIS BS990.0 IF AND LF STEREO AUDIO BLOCK In this block there are the following functions: - Amplification, Limitation and deenphasis. - Demodulation for 5.5 and 5,74 MHz Signal with selection of stereo and bilingual transmission. - Scart socket Switching for sound low frequency signals. ~ Different volume control for loudspeakers and earphone. The muting’ control acts only on the loudspeakers. = The double power output stage, works in class B configuration for loudspeakers and in class A configuration for earphone output.

SELECO 25SS653 CHASSIS BS990.0 IF AND LF MONO AUDIO BLOCK This configuration is equipped with the same stages of the stereo block, without, naturally, the stereo decoder and the power output stage can handle only mono Signals. The earphone output can not be adjusted separately.

SELECO 25SS653 CHASSIS BS990.0 OIRT CONVERTER The already described functions can be improved inserting a 6,5/5,5 MHz converter to adapt sound circuits to different standards. TUNING BLOCK The tuning system used is a frequency synthesizer. It is possible to tune all CCIR channels, italian channels, OIRT channels, CATV channels and hyperband channels. The system can store 40 programs (AV minus 39) and, calling program 0 (AU), the TV set will work as a monitor. REMOTE CONTROL BLOCK The remote control utilizes infrared light pulses and, with 28 different commands, can handle all TV set features.

SELECO 25SS653 CHASSIS BS990.0 TELETEXT AND PIP (PICTURE IN PICTURE) BLOCKS It is possible to insert a teletext module decoder, CCT (Computer Controlled Teletext) type, that can handle 2 or 4 pages memorization and is factory mounted on stereo sets. The PIP module can be factory mounted Or retro fittable.

SELECO 25SS653 CHASSIS BS990.0 SWITCH MODE POWER SUPPLY MAIN FUNCTIONS :

The . switch mode power supply receives the 220 a.c. voltage and supplies seven d.c. output voltages: 145 V; + and - 24,5 V; 15,5 V: 12,6 V: 7 V and 5 V. These voltages are supplied to the other TV sections and are stabilized against mains and load variations and are electrically separated from mains voltage. The power supply is always on, stand-by condition included.

CIRCUIT DESCRIPTION Power supply is of asynchronous flyback, switch mode type and has an operating frequency ranging from 25 to 70 KHz. Basically, the power supply consist of an IC (TDA 4601/D), a switch (BUSO8AF), and a power transformer. FUNCTIONS OF IC TDA 4601/D ~ Directly drives switching transistor T401. - Enables correct adjustment of the circuits output voltages from minimum to maximum load. . ot - Output voltages remains constant within 1% during changes in mains ranging from 170 to 260 a.c. voltage. - The operation is not syncronized. - Gives protection against short circuits. The transformer secondary windings provides two stabilized and filtered voltages that can be adjusted with P401.

OUTPUT VOLTAGES NOMINAL VALUES - 145 V (143 V for Videocolor picture tube)) to supply horizontal circuit and, during switching-on, video outputs. ~ 24,5 V to supply sound stages. . - 12,6 V to supply the tuning circuits, TDA4504/B IC and sound circuits. - 5 V to supply remote control receiver, microprocessor and stand-by circuit. - 15,5 V to supply the horizontal driver and the delayed 12,6 V supply. - 7 V to supply the PIP circuits.

OPERATING PRINCIPLE The switch mode converter is a v

ariable frequency oscillator whose frequency depends on mains voltage and on load applied at the output. It is supplied with voltage V which is obtained by rectifying directly the mains voltage. The power transistor T operates as a switch and in the saturated condition it conducts for a Tl period and remains cut- off for a T2 period. The transistor load is represented by the primary of a transformer having an LP inductance. ‘ During Tl energy is absorbed and stored in the primary, thus forming a magnetic field. During T2 in which the transistor is cut-off, the-energy is transfered to the loads (capacitors) connected to the secondary windings. To simplify things, we will take in consideration only a Single secondary winding (Ls). By appropriately adjusting the charging time Tl and the dis- charging time T2, energy transfer is adjusted to the varying conditions of mains and of the load. The converter simplified diagram is:

ariable frequency oscillator whose frequency depends on mains voltage and on load applied at the output. It is supplied with voltage V which is obtained by rectifying directly the mains voltage. The power transistor T operates as a switch and in the saturated condition it conducts for a Tl period and remains cut- off for a T2 period. The transistor load is represented by the primary of a transformer having an LP inductance. ‘ During Tl energy is absorbed and stored in the primary, thus forming a magnetic field. During T2 in which the transistor is cut-off, the-energy is transfered to the loads (capacitors) connected to the secondary windings. To simplify things, we will take in consideration only a Single secondary winding (Ls). By appropriately adjusting the charging time Tl and the dis- charging time T2, energy transfer is adjusted to the varying conditions of mains and of the load. The converter simplified diagram is:The transistor base is connected to the IC through an LC group. V is the rectified mains voltage, Vo is the voltage across the secondary winding and is, also, the voltage applied to the load. Voltage drop on the diode D and VCE voltage (saturation) of transistor during conduction are negligible. Capacitor C is sufficiently large to mantain the Vo voltage constant for a period considerably longer than period Tl - T2. Tl period:The transistor conducts and V will be on the Lp winding. The collector current Ic flowing through the Lp winding varies according to:

V 1) Ic = —— x Tl Lp . Voltage applied to Ls is -Vn and, consequently, during this phase, diode D is inversely biased and thus no current flows in the secondary winding. Being capacitor C considered considerably large, voltage Vo remains constant. A - positive voltage supplied by the IC is applied to the transistor base (the transistor switch is NPN) and will conduct for the time necessary to store the energy which will be required at. the output. The transistor will be cut-off after the Tl conduction period. Vv 2) Current reaches max. value Ic = x Ti Lp Energy stored in the magnetic field will be: 2 - 3) Wi = 1/2 Lp x Ic 2 period: When the transistor is cut-off, the flux variation of the magnetic field is inverted and it decreases according to a constant gradient. Voltage on windings will have an inverse polarity compared to that present during the Tl period. Voltage applied on Ls biases directly diode D and will charge capacitor C. The current flowing on the secondary winding is: _ Vo 4) Is = Is x xt Ls and will go to zero after the time: Is x Ls 5) T2 = — : Vo being n = turns ratio between windings and 2 Is = Ic xn and Lp = n x Ls we can obtain 6) VT1 = n x Vo x T2 This last equation relates times and voltages. When the field is nullified, a positive voltage is supplied by the IC to the transistor base that start to conduct and a new cycle will start. From the above equation follows that the voltage applied to the load is a function of main voltage V and of the ratio between transistor conduction and cut-off times. 7) V Tl V = — x — n T2 From this relation it is possible to find that the output voltage can be stabilized against main vol- tage variations changing the time ratio. If “f" is the cycle frequency repetition,-<Pd the load power and n the transformer ratio, we will have: Po 8) Wx f = n Taking in consideration equation n* 4) we obtain: 1 2Po 1 1 9) — =T1+tT2 = x Lp x: ( f n n Vo Vv To hold Vo output voltage constant, frequency will fall when Po load increases, and will rise when supply voltage V increases. Let us consider circuit operation when V voltage changes. If V voltage increases, V/Lp slope of primary Ic current increases. This means that, if equal times are considered, energy stored W per cycle is greater and thus also power involved. Since Vo voltage and power absorbed by load Po remain unchanged, time conduction Ti will be reduced. T2 cut-off time and T1/T2 ratio will be also reduced. Collector peak current Ic decreases as V increases. : Figure below shows trend of Ic collector current and of secondary current induced on primary during two operating cycles

1 and 2 with mains voltage V and VsV. Values of frequency and of times Tl and T2 can be obtained from equations 5 to 8. - If power absorbed by load Po increases, mantaining unchanged V and Vo, frequency will fall, as can be seen from equat. 8. Peek current will increase proportionally according to power forwarded to the load.

SELECO 25SS653 CHASSIS BS990.0 FUNCTIONAL DESCRIPTION WITH REFERENCE TO THE SCHEMATIC DIAGRAM

START (TV IN STAND BY) At start, supply voltage on pin 9 (TDA4601 IC), is taken from mains; this voltage is rectified and filtered by PTC401 and C409. When voltage on pin 9 up to 11,8 V, a reference voltage is supplied by the IC to pin 1 and all parts of the circuit are enabled.

TV SET IN OPERATION The supply voltage of the IC (after start) is provided by transformer winding 1-15; this voltage is rectified and filtered with D405 and C409 a

nd it is then stabilized inside the IC itself. Voltage on pin 9 is proportional to the mains voltage because D405 conducts during T401 conduction. When supply voltage on pin 9 falls below 7 V, the IC will be cut-off. The IC base current amplifier will supply a saw-tooth waveform on pins 7 and 8. The pulse coming from pins 7 and 8 are a.c. coupled with C410 to T401 base; CH403 determines the discharging time of T401 base current to reduce power absorbed during the switching phase. Pin 8 provides the driving saw-tooth current of T401 base and pin 7 supplies the switching-off pulse to discharge the T401 base. The saw-tooth shaper consist of an RC network (R412 and C416); maximum transistor peak current is simulated on pin 4 by means of the integrator which is discharged (on pin 4) during T401 cutoff phase. When voltage on pin 4 over 4 V threshold, the protection circuit cuts-off T401. C416 is charged exponentially through R402 till the C416 charge is interrupted and falls to zero when it's short circuited by a switch-off pulse supplied by or a circuit inside the IC and going out on pin 4. Between pins 7 and 8 is included resistor R405; the value of this resistor determines the maximum amplitude of switching driving current. STABILIZATION Changes in output voltages are detected by winding 1-11, and subsequentially rectified and filtered by D407 and.C413, and added to the reference voltage present on pin 1;. the result is applied to pin 3 of the’ controlling IC that will determines the conduction time of T401. R409 and C418 form an integrator circuit provided for sup- pressing ringing on square wave. When energy is completely off, a voltage inversion takes places which is detected on pin 2 of the IC: from this istant, the IC control logic starts driving in conduction T401 for the time deter- mined by the control voltage on pin 3.

nd it is then stabilized inside the IC itself. Voltage on pin 9 is proportional to the mains voltage because D405 conducts during T401 conduction. When supply voltage on pin 9 falls below 7 V, the IC will be cut-off. The IC base current amplifier will supply a saw-tooth waveform on pins 7 and 8. The pulse coming from pins 7 and 8 are a.c. coupled with C410 to T401 base; CH403 determines the discharging time of T401 base current to reduce power absorbed during the switching phase. Pin 8 provides the driving saw-tooth current of T401 base and pin 7 supplies the switching-off pulse to discharge the T401 base. The saw-tooth shaper consist of an RC network (R412 and C416); maximum transistor peak current is simulated on pin 4 by means of the integrator which is discharged (on pin 4) during T401 cutoff phase. When voltage on pin 4 over 4 V threshold, the protection circuit cuts-off T401. C416 is charged exponentially through R402 till the C416 charge is interrupted and falls to zero when it's short circuited by a switch-off pulse supplied by or a circuit inside the IC and going out on pin 4. Between pins 7 and 8 is included resistor R405; the value of this resistor determines the maximum amplitude of switching driving current. STABILIZATION Changes in output voltages are detected by winding 1-11, and subsequentially rectified and filtered by D407 and.C413, and added to the reference voltage present on pin 1;. the result is applied to pin 3 of the’ controlling IC that will determines the conduction time of T401. R409 and C418 form an integrator circuit provided for sup- pressing ringing on square wave. When energy is completely off, a voltage inversion takes places which is detected on pin 2 of the IC: from this istant, the IC control logic starts driving in conduction T401 for the time deter- mined by the control voltage on pin 3. ADJUSTMENT OF OUTPUT VOLTAGE Adjusting IC voltage pin 3, by means of P401, the switching frequency will be changed and, consequently, the voltages on secondary windings of transformer TR402 will also change.

PROTECTION CIRCUIT In cases of power supply short-circuits, the output of IC Pin 8 will be interrupted; this will occur when the supply on pin 9 falls below 7 V. The protection function will work, also, when an Overload is detected; for instance collector current of T401 exceeding the predetermined value. DAMPING CIRCUIT The damping circuit consist of C411 and has the function of damping voltage rise on T401 collector to reduce transistor dissipation. The collector voltage/current cross-point, consequently, will be at a very low level.

OUTPUT CIRCUITS

The two voltages available at the outputs, are applied to low pass filters to eliminate converter frequency in the 25 to 70 KHz range and the ripple due to load changes. STAND BY CONDITION In this condition the switch mode power supply operates in a normal manner, but with a reduced load (3 watt). The secondary voltages are slightly higher (approx 10 %) than the rated value due to the reduced load at the outputs. In the stand-by mode it is necessary to take care not to touch circuit parts, described below, as they bear following voltages: 145 V; 24,5 V; 15,5 V: 7 V and 5 V for:

- Electronic tuning circuit.

- Microprocessor.

- Line output stages and relevant circuits.

- Video output stages.

- Audio circuits.

- PIP circuit.

5 V AND 12,6 V STABILIZER These voltages are stabilized by means of TDA8139 IC. - The 1 output (pin 9) supplies 5 V stabilizing the 7 V in- put applied on pin 1. This line is always present and can not be switched. - The 2 output (pin 8) supplies 12,6 V stabilizing the 15,5 V input applied on pin 2. The output voltage is related to the reference voltage value applied to pin 7; resistance network R421, R422 and R423 fix the reference. voltage. The 12,6 V supply is switchable depending on pin 4 voltage: 12,6 V will be on with pin 4 H level (about 5 V).

VIDEO SIGNAL PROCESSING CIRCUITS (TDA _4504B)

INTRODUCTION Tda 4504B functions: IC processes the video signal performing the following Video IF amplification and synchronous demodulation. If and delayed AGC. Video preamplifier. Video switching for signal coming from antenna/Scart (peritelevision) socket. “= Horizontal oscillator sine circuit provided with: two control loops. Vertical oscillator sync obtained from frequency division of horizontal oscillator Signal (when the vertical oscillator coincides with the incoming Signal), or from vertical sync (when out of coincidence). Vertical for saw tooth 50 and 60 generation Hz reception. with automatic amplitude adjustment : Signal reception identification with muting in case of no reception. Sand-castle pulse generation (used in luminance/croma circuits).

CIRCUIT DESCRIPTION IF AMPLIFIER

The IF amplifier, with symmetric inputs on pins 9 and 10, has an input impedance adapter for SAW (Superficial Acoustic Wave) filter. The synchronous demodulator circuit works with the tuned circuit (adjustable to 38,9 MHz) connected to pins 23 and 24. The tuned circuit is parallel/series type (notch type) to improve video re

sponse and. this characteristic is useful for teletext signals and damping of higher frequencies (1,8 x 3; 2,75 x 2 MHz) that can produce noises on demodulation of sound low frequencies. The IF signal coming from the tuner, is applied to the SAW filter to obtain the correct band-pass characteristic. From this filter the signal is applied to the symmetric in- puts of the IF amplifier inside the TDA 4504/B IC. AGC circuit The AGC circuit is of “gated" type and the AGC voltage, output from pin 6, has the correct value to control R. F. stages amplification.

sponse and. this characteristic is useful for teletext signals and damping of higher frequencies (1,8 x 3; 2,75 x 2 MHz) that can produce noises on demodulation of sound low frequencies. The IF signal coming from the tuner, is applied to the SAW filter to obtain the correct band-pass characteristic. From this filter the signal is applied to the symmetric in- puts of the IF amplifier inside the TDA 4504/B IC. AGC circuit The AGC circuit is of “gated" type and the AGC voltage, output from pin 6, has the correct value to control R. F. stages amplification.The correct value for better amplification can be preset by means of P502 connected on pin 2 of TDA 4504 IC. The AGC voltage is not working with signals coming from the Scart socket. VIDEO AMPLIFICATION AND SWITCHING The complete video signal containing video/croma and 5,5 MHz sound information is obtained with inter carrier system and is coming out from TDA 4504 IC on two pins: - pin 20 output, always connected to the IF demodulator, is applied to pin 5 of the mono audio module (not used with stereo module). The same output is applied to the Scart socket via L501 and the emitter-follower T501 and to pin 16 of TDA4504 IC. - pin 15 output can be switched from tuner to Scart signal. When the video switch, internal to C1501, is switched to ex- ternal (Scart) signal, the sync circuits are controlled by this signal and, meanwhile, IF video amplifier works in normal way being not switched.

During this condition (signal from Scart), the AGC gated system is switched to black level control. In the same time will be inserted a lower time constant: on the first PHl horizontal phase detector network by means of an H logical level coming from Pin 28 of micro TVP2066: this voltage will drive VIR switch connected to pin 17 of TDA 4504/B IC. This switching will be automatically obtained calling AU function. 7 The switching voltage for the internal and external video switch, are obtained from CI? microprocessor with proper logic levels on pin 18 of TDA4504/B IC: H = AV L = TV. SYNC SEPARATOR The video signal coming from emitter-follower T502 or from teletext module (TTXT), is applied, via C512, to the sync separator circuit (pin 28 of TDA 4504/B). The sync separator clips the signal to 30% of the sync top; this level is set by means of R514. HORIZONTAL SYNC CIRCUIT - Circuit of the 1” phase comparator. It's provided to hold synchronized the horizontal oscillator with the sync signal. This circuit, gated, operates comparing the sync signal coming from the sync separator with the oscillator signal and the error voltage coming out from Pin 27 is applied, via R516, to pin 26 to control the horizontal oscillator. The error voltage is filtered with C513, R515 and C514. During “catching” Periods, or VTR insertion (applied to Pin 17), the comparator current will be increased 7 times; in this way it is increased the sync-in range and, also, an higher gain of the 1* phase comparator. ~ Circuit of the 2” phase comparator. This circuit enables correct phasing between scanning and video information. This is obtained comparing the oscillator frequency against the fly-back signal (applied to Pin 30) thus Producing a feed-back voltage which is applied to the phase control circuit. Phase correction can be obtained changing current on pin 31 by means of P60I1C.

COINCIDENCE DETECTOR (MUTING) This circuit supply 9 or 6 V (respectively for 50 or 60 Hz) on pin 14 when sync signal are present. This voltage is used, in this application, to: - Muting control, via Dl, applied to pin 6 of the audio module. - Search stop, during automatic search, giving information to micro pin 13. HORIZONTAL CIRCUITS LINE OSCILLATOR The line oscillator is R - C type and is composed of R517: P501 and C515 connected to pin 26. With P501 it is possible to adjust the oscillator frequency. The oscillator generates an 15.625 Hz signal controlled by the the 1” phase comparator error voltage coming in on pin 26 via R516. OUTPUT CIRCUIT This circuit amplifies the line oscillator signal to enable direct drive of line drive transistor. The amplifier output, in push-pull configuration, can be found on pin 29. VERTICAL SYNC CIRCUITS VERTICAL OSCILLATOR This circuit is composed of one saw-tooth generator with external RC network (C518 and R525) connected on pin 3. This network determines the shape of the waveform not the frequency. . The frequency, instead, depend on horizontal frequency di- vision driving directly the oscillator: in this condition it is not necessary to adjust externally the oscillator. The output voltage is on pin 4 and is applied to the output stage (TDA 8170); this output is kept constant by means of internal comparator that compares the output voltage with the voltage on pin 5 (feed-back) either with 50 or 60 Hz signal.

VERTICAL SYNC The vertical sine signal is obtained dividing the line oscillator frequency (15.625 x 2 Hz) and generates pulses, 50 or 60 Hz, depending on information coming from the coincidence demodulator that decodify video transmission standards. With sync signal not standard, the

line frequency divider is disabled and the saw-tooth generator will be synchronized by the vertical sync signal coming from the video signal (via the sync separator). SAND-CASTLE GENERATION This circuit is giving on Pin 30 output, a Sand-Castle signal (15.625 Hz frequency) with 3 voltage levels that will be used in the digital circuits in the luminance/chrominance process.

line frequency divider is disabled and the saw-tooth generator will be synchronized by the vertical sync signal coming from the video signal (via the sync separator). SAND-CASTLE GENERATION This circuit is giving on Pin 30 output, a Sand-Castle signal (15.625 Hz frequency) with 3 voltage levels that will be used in the digital circuits in the luminance/chrominance process. VERTICAL OUTPUT It is formed by TDA 8170 IC; receives on pin 1 the saw-tooth Signal coming from the oscillator and adjust this signal to drive the vertical deflection joke. Through pin 5, current goes to joke vertical section and part of the signal returns as feed-back in the vertical driver (pin 5 of TDA 4504 IC). Inside the TDA 8170 a flyback generator supplies a vertical frequency pulse at pin 2 and, via D601, increase the supply voltage to pin 6 during fly-back. In this way it determines fast inversion of joke current, obtaining the correct fly-back of the electronic beam. The joke is grounded via C608 and R608. LINEARITY AND VERTICAL AMPLITUDE Linearity is determined by network R609, P601A and C609: with the potentiometer P601B it is possible to adjust linearity. The vertical amplitude is determined with P601A that adjust the feed-back coming on pin 5 and applied at the vertical driver internal to CI501. VERTICAL SHIFT Picture centering is obtained with P602 potentiometer that permits the correct shift of the vertical deflection.

HORIZONTAL SECTION This stage amplifies the horizontal frequency signal coming from pin 29 of TDA 4504/B and drives a circuit that works as On/Off switch for horizontal deflection joke current during the scanning. The power output is supplied with 145 V and the driver circuit with 15,5 V. DRIVER CIRCUIT The driver circuit is composed by transistor T301 which am- plifies the horizontal square wave signal coming from the line oscillator.

POWER OUTPUT CIRCUIT The square wave pulses coming from the driver circuit are applied, via transformer TR302, to the power transistor T302 that will be conducting for a period larger than half of the sca

nning; during T302 cut-off time, the scanning will be com- pleted by the diodes D304 and D303. C306-C307: horizontal stage tuning condenser. C304: ground for primary winding of EHT transformer. R307: EHT stage protection and horizontal amplitude compensation.

nning; during T302 cut-off time, the scanning will be com- pleted by the diodes D304 and D303. C306-C307: horizontal stage tuning condenser. C304: ground for primary winding of EHT transformer. R307: EHT stage protection and horizontal amplitude compensation.EHT TRANSFORMER EHT voltage of 24,5 KV is obtained adding up the voltages in- duced on transformer windings and rectified by the relevant diodes. These are three diodes connected in series between the three secondary windings included in the TR301. Moreover the transformer supplies the service pulses; among them there are filament voltage, drawn from pin 2 via R 727 and R728 that reduces it to the rated value. From one of the secondary windings of EHT transformer,is obtained a voltage proportional to the average beam current, used by the limiter circuit (inside the TDA 4504/B). The beam limiter circuit is composed of C312, R315, DZ301 and C313. R315 closes the secondary winding being connected to the 145 V power supply. Adjustments: - L301 : horizontal linearity adjustment. - P601F : horizontal amplitude adjustment.

PIN CUSHION CORRECTION CIRCUIT This circuit enables Pin cushion and keystone corrections on CTV's provided with 110° type CRT. The circuit consists, basically of IC C1351 (TDA8145) that is mainly composed of: - One square wave generator. - Integration circuit. - Comparator. The IC supplies a signal to the modulator diodes center ac- cording a law that is depending on correction quantity re- quired by each line. It is important to hold constant LC products in the - circuit to prevent damaging effect of EHT increase. This signal, consisting in variable width Pulses (narrow at the beginning and, progressively, wider till the center, and subsequently, narrowing towards the bottom of the screen), is a line correcting signal depending on vertical frequency.

CIRCUIT DESCRIPTION The frame pulse, saw-tooth shaped, enters in the IC on pins il and 2 and is first converted in a triangular shaped wave- form and later in a parabola signal. The parabola symmetry, and the related keystone correction, is obtained adjusting the reference voltage with potentiometer P601-E. . Flyback line pulses, coming from the line output transformer, are applied to R359; this signal is applied to pin 8 of the IC via zener DZ351 and diode D351 that are eliminating noise on the signal itslf. P601-F (amplitude) adjust the line frequency amplitude and, consequently, the output level of the comparator (inside the integrated circuit). The crossing point between parabola and the line frequency pulse, can be adjusted with P601-D. The correction signal is sent, via CH351, to diode modulator (D303 - D304) center. A particular feature of this circuit is a low power absorption and dissipation due to the fact that energy not used will be returned to the supply. This is possible since energy, supplied by the modulator diodes and stored in CH351 will, at line frequency, forwarded to the supply by means of a diode, mounted inside the IC, connected between pins 5 and 6. The small energy absorption, and so dissipation, was obtained with the working procedure of the IC that is not drawing current steadily but, instead, conducts for short periods only during corrections. This will reduce the current requirements on EHT transformer.

LUMINANCE/CHROMINANCE PROCESSING CIRCUITS (TDA 3301/B) INTRODUCTION TDA

3301/B processes luminance and chroma signal doing the following functions: - Decodes chroma signal either in PAL and NTSC system: sui- table, also, to insertion of SECAM transcoder. = Automatic black level adjustment. - Beam current peak limiter. . ~ Analogical control*for brightness, contrast and saturation. - Three digital inputs for R-G-B Signals and one for fast blanking. - Drive of luminance delay line and chroma delay line. - Subcarrier oscillator (4,43 MHz with PLL circuit). The main feature of the TDA 3301 IC, consist of the internal circuit which ensures automatic alignment of black level of the CRT three electron beams. This is obtained by changing the d.c. level of the three driving signals or, in other words, the beams cut-off points. This function is operating in a continuous base, with field frequency, giving out one pulse which measures, in the same moment, the current of the three beams during vertical fly- back (time intervals in which the picture is missing). This pulse correspond with an artificial black level and the current of each gun measured during this period is compared against a fixed standard value produced inside the IC itself. The comparison between this standard value and the value effectively measured gives a d.c. voltage, one for each gun, which is added to the d.c. component of the three video signals applied to the three R-G and B output stages. Relevant cathode currents are thus adjusted so that the difference between the standard value and the effective one’s is reduced until coincidence of the three cut-off points of the three electron guns is reached. This d.c. adjusting voltages are stored in three relevant condensers and thus shifting of d.c. level of the driving Signals may be hold during the whole time in which the Picture is present. Advantages offered by this alignment produced inside TDA 3301 may be summarized as follow: . - Elimination of normal alignment of the cut-off points and consequently elimination of the relevant potentiometers. - Automatic compensation of the inevitable drifts, during set life, of the three electron beams due to aging of components and, particularly, of the picture tube. ~ Compensation of the-shift of the cut-off points happening during receiver warm-up (after switching on of the set).

3301/B processes luminance and chroma signal doing the following functions: - Decodes chroma signal either in PAL and NTSC system: sui- table, also, to insertion of SECAM transcoder. = Automatic black level adjustment. - Beam current peak limiter. . ~ Analogical control*for brightness, contrast and saturation. - Three digital inputs for R-G-B Signals and one for fast blanking. - Drive of luminance delay line and chroma delay line. - Subcarrier oscillator (4,43 MHz with PLL circuit). The main feature of the TDA 3301 IC, consist of the internal circuit which ensures automatic alignment of black level of the CRT three electron beams. This is obtained by changing the d.c. level of the three driving signals or, in other words, the beams cut-off points. This function is operating in a continuous base, with field frequency, giving out one pulse which measures, in the same moment, the current of the three beams during vertical fly- back (time intervals in which the picture is missing). This pulse correspond with an artificial black level and the current of each gun measured during this period is compared against a fixed standard value produced inside the IC itself. The comparison between this standard value and the value effectively measured gives a d.c. voltage, one for each gun, which is added to the d.c. component of the three video signals applied to the three R-G and B output stages. Relevant cathode currents are thus adjusted so that the difference between the standard value and the effective one’s is reduced until coincidence of the three cut-off points of the three electron guns is reached. This d.c. adjusting voltages are stored in three relevant condensers and thus shifting of d.c. level of the driving Signals may be hold during the whole time in which the Picture is present. Advantages offered by this alignment produced inside TDA 3301 may be summarized as follow: . - Elimination of normal alignment of the cut-off points and consequently elimination of the relevant potentiometers. - Automatic compensation of the inevitable drifts, during set life, of the three electron beams due to aging of components and, particularly, of the picture tube. ~ Compensation of the-shift of the cut-off points happening during receiver warm-up (after switching on of the set). CIRCUIT DESCRIPTION put The is pin composite 3

7 and via video to R105 chroma signal and input R106, coming pin and from 1. applied emitter-follower to luminance -T502 in- splitted, The inside signal the IC is applied it is amplified to the luminance by a factor input 3 and through is, then, C112: outputted on pin 35 and from here applied to the luminance and, delay at line. the "This same delay time, the line delay give to line the gives signal a 20 270 dB ns attenuation- delay The signal to the is, signal subsequentially, by means of an applied internal to pin trap. 36 and u pass reinserted through a and stage a further where the stage black for brightness level d.c. and voltage contrast is adjustment. On pin 29, via resistor R128, will be fixed the point for the CRT peak beam current. contrast The average control, beam current Pin 32, limiting on which value is applied, will be via determined D104, a by voltage Proportional to the average beam current. This beam current is the same that is flowing in the line transformer ken windings on junction producing R311 the and EHT C313. itself. The measuring point is ta- is C312 connected is the ground to 145 reference V, referring, for secondary in this windings way, the while limiting R312 and voltage; C313. this voltage . is, subsequently, filtered with R311 current stabilizing DZ301 is conditions. connected loop of to the avoid cut-off the current possibility in particular of. bouncing beam of the direction also, The to colour luminance field in signals; and three signal line equal to blanking is, the stages , luminance pulses. to be divided signal added,in will in matrix three be different added, circuit, The - output output amplifiers stages of to the drive IC features video power other output. four main function: ~ Beam current reading. ~ Clamping circuits. ~ module Additional or Scart inputs socket. for R-G-B signals coming from teletext voltage or pins The On R-G-B 24, Screen (fast 25 signals and Display blanking) 26 coming through signal, to from switch 100 are external nF inputs applied, condenser: inputs, is respectively, applied the like switching without teletext to condenser to pin 23. clamping The The impedance above logic and circuit mentioned (75 burst ohm), that separation inputs to determines allow are insertion is closed drive automatic on of and their long cut-off, clocked connections.

7 and via video to R105 chroma signal and input R106, coming pin and from 1. applied emitter-follower to luminance -T502 in- splitted, The inside signal the IC is applied it is amplified to the luminance by a factor input 3 and through is, then, C112: outputted on pin 35 and from here applied to the luminance and, delay at line. the "This same delay time, the line delay give to line the gives signal a 20 270 dB ns attenuation- delay The signal to the is, signal subsequentially, by means of an applied internal to pin trap. 36 and u pass reinserted through a and stage a further where the stage black for brightness level d.c. and voltage contrast is adjustment. On pin 29, via resistor R128, will be fixed the point for the CRT peak beam current. contrast The average control, beam current Pin 32, limiting on which value is applied, will be via determined D104, a by voltage Proportional to the average beam current. This beam current is the same that is flowing in the line transformer ken windings on junction producing R311 the and EHT C313. itself. The measuring point is ta- is C312 connected is the ground to 145 reference V, referring, for secondary in this windings way, the while limiting R312 and voltage; C313. this voltage . is, subsequently, filtered with R311 current stabilizing DZ301 is conditions. connected loop of to the avoid cut-off the current possibility in particular of. bouncing beam of the direction also, The to colour luminance field in signals; and three signal line equal to blanking is, the stages , luminance pulses. to be divided signal added,in will in matrix three be different added, circuit, The - output output amplifiers stages of to the drive IC features video power other output. four main function: ~ Beam current reading. ~ Clamping circuits. ~ module Additional or Scart inputs socket. for R-G-B signals coming from teletext voltage or pins The On R-G-B 24, Screen (fast 25 signals and Display blanking) 26 coming through signal, to from switch 100 are external nF inputs applied, condenser: inputs, is respectively, applied the like switching without teletext to condenser to pin 23. clamping The The impedance above logic and circuit mentioned (75 burst ohm), that separation inputs to determines allow are insertion is closed drive automatic on of and their long cut-off, clocked connections.Sand-Castle pulses, available on pin 27, and with vertical blanking, available on pin 28, coming out from monostable composed of T102 and T103. - On inputs 22, 19 and 16 are coming in the cut-off current signals measured during cut-off and coming from output stages. The condensers connected to pins 21, 18 and 15 are provided for memorizing the adjustment voltages of the cut-off points of red, blue and green guns. The chrominance signal is extracted from composite video signal available on emitter-follower T502 and, via R105, applied to filter FC101 that gives a reduced response around 2,5 MHz to reduce cross-colour effect (inter modulation of. luminance signal on chroma signal). The signal thus filtered is coupled to chroma amplifier input pin 1 , and controlled by ACC (Automatic Colour Control) who- se filter is connected on pin 2. There are, moreover, two additional stages: _ The first one controls the Hue (c.c. control), pin 40, al- lowing chroma signal phase shift (only for NTSC system). - The second one links together contrast and saturation controls allowing constant chroma matrixing to various picture contrast levels. From this stage the chroma signal is going to delay line driver stage, pins 3 and 4, where it is separated in the two components R - Y and B - Y (PAL dematrixing circuit). The 90° shifter of 4,43 MHz sub-carrier, needed for B - Y demodulator, is of active type and is controlled by a comparator that is giving out a voltage (1/2 line frequency) externally filtered with C125. G - Y signal is extracted from a colour difference matrix circuit and, with R - Y and B - Y signals, applied to circuits where luminance signal is subtracted. From pins 20, 17 and 14 are coming out R, G and B signals, already pre amplified, to drive directly colour output stages.

VIDEO OUTPUT STAGES The video output stages are made up with a integrated circuit (TEA 5110A), whose main feature are:

- MOS technology.

- 190 V supply.

- 10 MHz bandpass with 50 V P.Pp. signal output.

- 8 MHz bandpass with 100 V P.p. signal output.

- 50 ns signal rise and fall times.

- Automatic CRT cut-off adjustment.

- CRT flash-over circuit protection.

The three output stages are, , equals; the following description will be related only to the red output stage.

The red video signal, coming from TDA3301 pin 20, is applied to the operational amplifier input (differential amplifier); this operational amplifier is composed of transistor Tl, T2 and T4. This last transistor is a common base amplifier and allows a very large bandpass characteristic. T3 will bias the the non-inverting input of the operational giving, in the same time, thermal compensation. The operational amplifier gain will be set with the resistance values of feedback external resistors R702 and R703. T5 and T6, MOS transistors with high impedance inputs and low impedance outputs, supplied with 190 V, are used only to transfer the video signal from the the operational amplifier output to the CRT cathode.

Working condition with positive going input

signal With positive going input signals, T5 will be in conduction and T6 will be cut-off: the T5 “source” will be positive allowing the conduction of the external diode D702. This diode will drive directly the “red" cathode charging the high CRT capacitance. Working condition with negative going input signals With negative going input signals, T6 will be in conduction and T5 and D702 will be cut-off; in this condition the Signal can go through only by means of TS8. This transistor is used, in the same time, for cut-off beam current reading; on pin 6 are connected, externally, R704 and R705 that are fixing the correct value of the reading voltage needed by TDA3301 IC. With negative component of the signal, the CRT capacity can discharge through T8 and Dl. T7 is used to decrease the Signal falling edge time; when T6 is conducting, the positive voltage drop on R2 will drive in conduction T7 that will help the decrease of the input voltage to T8.

signal With positive going input signals, T5 will be in conduction and T6 will be cut-off: the T5 “source” will be positive allowing the conduction of the external diode D702. This diode will drive directly the “red" cathode charging the high CRT capacitance. Working condition with negative going input signals With negative going input signals, T6 will be in conduction and T5 and D702 will be cut-off; in this condition the Signal can go through only by means of TS8. This transistor is used, in the same time, for cut-off beam current reading; on pin 6 are connected, externally, R704 and R705 that are fixing the correct value of the reading voltage needed by TDA3301 IC. With negative component of the signal, the CRT capacity can discharge through T8 and Dl. T7 is used to decrease the Signal falling edge time; when T6 is conducting, the positive voltage drop on R2 will drive in conduction T7 that will help the decrease of the input voltage to T8.SELECO 25SS653 CHASSIS BS990.0

FREQUENCY SYNTHESIZER ELECTRONIC TUNING CONTROL UNIT

The system control in this analog chassis, is obtained with a microprocessor (TVPO 2066) mounted in the central CCU unit. The central control unit is made up with a 8 bit microprocessor of the 8048 family with 10 Kbyte ROM and 256 Kbyte RAM.

On the block diagram can be- recognized: - Clock oscillator. - Reset and On/Off circuits. - Remote control decoder. - On Screen Display. - IM bus interface. - D/A (Digital/Analog) converter. - I/O (Input/Output) gates. Clock oscillator: the internal oscillator, with the 4 MHz quartz connected on Pin 12, generates the internal clock used inside as micro- processor clock and externally as the FM bus clock.

Reset circuit: this block receives an external signal: if this signal is L (Low) level, the microprocessor will be cut-off. On-Off circuit: in stand-by condition the microprocessor receives the normal supply and, therefore, can receive commands coming”from remote control or from local pushbutton. A switch-on information will bring to L level this output that will switch-on, consequently, the 12,6 V supply. A switch-off information, instead, will bring to H level this output cutting down the 12,6 V supply. Remote control decoder: decoding of remote control codes, is obtained with hardware components instead of software system that is better for signal decoding and permits faster control of pheripheral circuits. The CCU is always waiting the reception of remote control inf- rared information and the internal hardware decoder will consider only the certified commands deleting interfering signals. The valid information will be written down on two internal register, one for address and one for data, and the registers will be read by the remote control software procedure and reset, giving the possibility to start again with the reception of other infrared information. The tuning system is a frequency synthesizer and the command signal is made up with data information sent to the PLL c- cuit via the IM bus. On Screen Display: the operation requested with remote control are displayed on the TV screen; to obtain this, the system uses an internal hardware circuit that generates 32 character on R-G-B configuration. IM bus interface: through these lines the CCU can "talk" with NVM3060 memory. D/A converters: the analogical controls for brightness, contrast and saturation are made with 3 DAC lines, with PWM modulation, control- led by the software. The volume control for TAST sets is realized with IM bus and for TAM sets with the 4* DAC line.

In the block diagram that can be seen in the following page, can be recognized: "

1) Remote control. The remote control is used to send information to the TV set using infrared signals.

2) IR remote control receiver. This circuit will amplify the infrared signals to the proper level requested for CCU input.

3) TV set front controls (local commands). It is possible, by means of short circuits of some CCU inputs, to obtain local commands already memorized in the microprocessor software.

4) On/Off. This information allows switching on and switching off of the TV set.

5) Reset. The reset pulse will start CCU function.

6) Memory. Informations regarding Programs and Analogical settings, are memorized in a non-volatile memory (NVM 3060) that has 512 x 8 bits capacity.

7) Analogical commands. The analogical commands allows analogical (brightness, contrast, saturation and volume) setting of the TV set.

8) OSD (On Screen Display). This circuit generates the character information that will be displayed on the TV screen.

9) PLL (Phase Locked Loop). The PLL circuit will allows channel tuning. Input/Output (I/O) ports: the microprocessor has 16 lines; of these lines, the ones related to port 2 can be used as input/output lines while the lines related to port 3 are only output lines. The output configuration are: - TTL compatib

le. ~ 5 V max. or 12 V max. Open Collector.

le. ~ 5 V max. or 12 V max. Open Collector.Very important are the two lines dedicated to the integrated circuit protocol realizing the IIC bus for communication of informations between microprocessor and the teletext IC, the stereo IC and the PLL IC. The microprocessor (CCU) main features are: - User adjustment processing. - Pheripherical circuits control. The dedicated software developed specifically for this chassis, to obtain user adjustment control and connected circuits control, has: N° 2 lines for IIC bus for CCT teletext, Stereo sound, PLL and various pheripherical IC; one line is only output port and the other is input/output port. N° input lines for port 2. o N° e line not connected to port 2. N° 8 output lines for port 3.

REMOTE CONTROL INFRARED TRANSMITTER

This system was developed to send CTV command informations. With this command transmission, obtained with infrared light coded transmission, it is possible to send as much as 1

024 different commands. The information is defined by the variation of the distance between two consecutive pulses that are very short (pulse duration about 10 usec) and allows the driving of the infra- red light emitting diode with a high current: (till 2 A) obtaining, in this way, commands from long distances, noise immunity and long life to the battery of the remote control. In the CTV, a photo diode converts the received infrared light into a electric signal that, after pre amplification, will be sent to the microprocessor that will decode the received information.

024 different commands. The information is defined by the variation of the distance between two consecutive pulses that are very short (pulse duration about 10 usec) and allows the driving of the infra- red light emitting diode with a high current: (till 2 A) obtaining, in this way, commands from long distances, noise immunity and long life to the battery of the remote control. In the CTV, a photo diode converts the received infrared light into a electric signal that, after pre amplification, will be sent to the microprocessor that will decode the received information.Each transmission “word” is composed of 10 bits of information and is divided in 4 ‘address bits and 6 data bits. It is possible in this way to obtain maximum 16 address and 64 data totaling 1024 commands as already said. To transmit 10 bits are used 14 pulses; the first one is cal- led “preliminary” and is followed by a start pulse, in sequence they are 11 pulses for the transmission of the 10 data and, at the end, the stop pulse. The binary informations "1" and "0" is’ obtained with the time interval between two consecutive pulses. If we define as T (about 100 usec.) as base for the transmitted code, the time equal to 1T corresponds to the binary information 0 and the time 2T to the binary information 1. The time interval between the “preliminary” pulse and the start is equal to 3T as for the stop pulse.

’ The RC oscillator frequency is determined by components connected to pins 2 and 3 and these components must be choose keeping in mind the clock used in the receiver. - The oscillator start working only when the monitoring circuit find the presence of a transmission command. In idle condition, the oscillator is cut-off and the power absorbed by the system (CMOS technology) is almost zero. Connecting together one of the line pin (line a, h correspon- ding to pins 8 to 15) with one the column pin (column A, H corresponding to pins 16 to 23) starts the transmission of the command word. If the pushing is related to more than one pushbutton, the transmission will be blocked. The pulse sequence will be repeated every 130 msec. till the release of the pushbutton. With two pins it is possible to choose the transmission ad- dress that, in this case, is address 1-16. The meaning of this address code 1-16 can be explained as follows: when one pushbutton is pressed, only one command with address 1 will be sent and, subsequently, will be

transmitted every 130 msec. commands with address equal to 16. The parallel to serial converter is made up with a shift register that will receive in the input the parallel infor- mation coming from the decoder and will give in the output eircuit the same information in a serial way.

transmitted every 130 msec. commands with address equal to 16. The parallel to serial converter is made up with a shift register that will receive in the input the parallel infor- mation coming from the decoder and will give in the output eircuit the same information in a serial way.INFRARED (IR) PREAMPLIFIER The purpose of the IR preamplifier, is the amplification of the infrared signal received from the photo diode (with an amplitude of few uV), till the proper level adapt to drive the following decoder (in this application the microprocessor). The IC used, TBA 2800, as can be seen on the block diagram, is made up with 4 main stages: ° - Amplifier 1 with a controlled gain. - Amplifier 2. - Amplifier 3 that is, also, acting as a separator. - Inverter 4. The 1° amplifier has a very large dynamic range and this feature will improve the feature of the input stage in presence of interfering infrared lights coming, for instance, from

neon lamps. Capacitor connected on pin 2 will affect the stage gain; must be remembered, anyhow, that are not accepted commands from distances below 30-50 cm.. Amplifier n° 2 will, further on, amplify the signal and will drive the following separator. Noise immunity can be improved inserting a resistor between Pin 16 and ground; in this case sensibility will be, naturally, decreased. The output inverter give the possibility to obtain positive pulses on pin 8 and- negative -one's on: pin 7.

LOCAL COMMAND

The local commands are using a 3 x 2 matrix: this combination will permit six command but one is not used and the five command left, are used for: P- ; Pt ; VOL- ; VOL+ ; OSD.

The micro generates on pins 25, 31 and 32, multiplexed pulses when some of the local pushbutton will be pushed; these pulses are transferred on the two input pins 7 and 8 where the micro will read the relevant data to recognize which pushbutton was pressed and . later, execute the desired command.

ON-OFF CIRCUIT In stand-by condition, which correspond in this application with the integrated. circuit: completely supplied but with reset signal equal to zero, only part of the IC is waiting for commands that can be, in these conditions, only a switch on command. The switch-on can be reached in two way: A - via remote control; in this case a code 0...9 will start the switching-on procedure and pin 16 will be forced from inside to L level. B - forcing to L level from outside the On-Off pin 16; really this pin is acting like a input/output pin. If it is H level will be acting like an input and, afterward, it will switch to output pin holding to L level the pin itself. Previously was said that in stand by condition pin 32 was corresponding to bit 7 of gate 3 and was to logical level H; pushing pushbutton P+, T2, and consequently Tl, will start conduction, forcing to L level the On-Off pin 16. In consequence of L level of pin 16, the 12,6 V will be On and the TV set will switched On.

RESET CIRCUIT

This circuit checks the power supplies allowing CCU procedures only if power supplies are correct. C423 condenser was inserted to obtain delay on CCU procedure start and to mute sound (on mono CTV's) during switch on of the set. The reset pulse is generated on pin 16 of CI402 IC (TDA8170), that is, also, the IC stabilizing the 5 V and 12,6 V power supply. As can be seen on the following diagram, the reset pulse will be present only when the output voltage on pin 9 is higher than 4,9 V. The internal generator will start to charge C423 and for the time of the condenser charge (TD) the reset output will remain to L level; when C423 will be completely charged, the reset output will go to H level. If and when the 5 V supply is going below 4,85 V, the reset output will return to L level blocking, in this way, the CCU process; the system will start to work again when the output will increase higher than 4,9 V.

MEMORY The main task of the memory consist in the memorization of the tuning programs data and of the normalized analogical sound and video data. j The memorization of information regarding Teletext insertion, PIP and of OSD colour, amplitude and position can be stored,also, in this memory. The Kbyte, chip used in this chassis (NVM3060) has a capacity of and is controlled corresponding through to the 512 microprocessor memory location IM of bus. 8 bit ‘each

way. “slaves", Being the CCU it is the not only important "master" and the other circuits only the common bus. to solve priority Problems on The IM bus comprises three lines: - ID Identification - CK Clock - D Data The by the first micro, two while lines are the only Data line in one is direction and controlled L The In level idle bus logical condition, information condition. all starts lines when are the in ID H bidirectional. level and CK logical signal state. are in After this Procedure will be transferred 1] address byte that.

At this point the ID signal will go to H level and on the slave circuits will start comparison with the address received. The pheripherical addressed circuit will be activated and will switch his IM bus circuit for data reading or wr ting. The data writing or reading will be correlated to the proper address and, in this way, microprocessor and “slave” circuit will always know the function required. The CCU will send, now, 8 or 16 clock pulses to write or to read 1 or 2 bytes on the “slave" circuit and the operation will be executed, also in this case, during the L to H (Low to High level) clock transition. Stop to this interchange of information will. be reached with a short negative pulse on the ID line; this pulse is, also, used to memorize data on the “slave“ or CCU circuit. The bidirectional signal flow is obtained using the output with Open Drain configuration; the pull-up resistors are in- side the CCU itself.

ANALOGICAL COMMANDS To adjust brightness, contrast, colour and volume levels, it is necessary to give to the relevant circuits a d.c. voltage variable from minimum to maximum to cover the entire range of the adjustments. This is obtained generating a square wave, with a 64 steps PWM modulation, on four CCU outputs. The PWM (Pulse Wide Modulation) information is obtained pushing the relevant pushbutton on the local pushbutton unit or the

corresponding remote control pushbutton. The volume control is working as described only for mono CTV sets.

ON SCREEN DISPLAY (OSD) GENERATION The TV user has the necessity to visualize the "STATUS" of the set itself; he will need to know, for instance, what program he has called for or are looking at and needs to know the analogical adjustment he will be doing. These informations can be given by means of one Display mounted on the pushbutton unit or can be visualized, as in this application, directly on the CTV screen. It is necessary, therefore, to

generate R-G-B informations, completed with the necessary Fast blanking signal, with the proper screen position, in sync with the normal deflections signals H and V (Horizontal and Vertical). The interface H, V and R-G-B blocks, must adapt the sync and R-G-B signal levels in respect to the used pheriferical circuits. ;

generate R-G-B informations, completed with the necessary Fast blanking signal, with the proper screen position, in sync with the normal deflections signals H and V (Horizontal and Vertical). The interface H, V and R-G-B blocks, must adapt the sync and R-G-B signal levels in respect to the used pheriferical circuits. ;R - G - B SIGNALS SWITCHING

The R - G - B signals coming in, can be coming from various different directions; for instance from Teletext, from PIP, from the CCU and from Scart socket. It is necessary, there- fore, to avoid that the incoming signals can reach in the same time the output circuits. The interface R - G - B switching circuit ‘has the purpose of proper selection of these inputs. The proper selection is realized using the the fast blanking signal with the following priority: 1) OSD (On Screen Display) coming from the CCU. 2) OSD from Teletext or from PIP (Picture In Picture). 3) OSD from Scart socket.

The 74HC4053 IC (CI21), is an analogical switch with four internal path; one of this section is not used. Every switch has in one input the OSD R - G ~ B signal - and in the other input the PIP or Teletext R - G - B signal added together in one resistor network. The Fast Blanking signal, inputted to pins 9, 10 and ll, is generated in the CCU and will select the proper inputs. On pins 14, 15 and 4 will appear the PIP or Teletext OSD R - G - B signal that are sent to the TEA5114A IC that is working also as a switch for these Signals and the signal coming from the Scart socket. : The switch command for C122 IC is coming from the logic- OR circuit composed of Fast Blanking/CCU and Fast Blanking/Teletext added on the emitter line of T21. The internal TEA5114A switches are switched with signals applied to pins 10, 12 and 15. The R - G - B output signals are present on pins 11,13 and 16 and these signals will be displayed on the TV screen via the TDA3301 IC: the switching signal for the TDA3301 IC is the Fast Blanking signal outputted from pin 9 of CI22 IC.

CIRCUIT DESCRIPTION

The PLL circuit is composed, mainly, of the TVPO2066 microprocessor and the TSA5511T IC mounted inside the tuner.

TSA5511T IC exchange information with the microprocessor via Pins 4 and 5. The data line receives 5 bytes serial data to select the tuner oscillator frequency (or the programmable divider), to program the 8 output ports (pins 6 + 13) and to control the programmable current amplifier. The reference frequency (7,8125 KHz) of the PLL circuit is obtained dividing by 512 the 4 MHz of the quartz oscillator. The tuner local oscillator Signal is applied to the symmetric inputs, pins 15 and 16, and, after amplification, divided for 8 and, subsequently, divided with the Programmable divider (controlled by microprocessor data) to obtain 7,8125 KHz equal to the reference frequency. This last signal, obtained with the two consecutive division, will be compared with the reference frequency and the output of

the comparator will control a current programmable amplifier and the result will be amplified with a voltage amplifier. . The programmable current amplifier is controlled continuosly by the phase comparator to mantain stabilized the varicap voltage and will be programmed by data coming from the microprocessor every channel change, via input pins 4 and 5 coming from_the IM bus trans codification. The output signal, pin 18, is applied to transistor Tl: the conduction of this transistor will give a voltage drop on R56 that will control the.varicap..voltage. Pin 1 controls, also, the varicap line giving output pulses directly generated by the programmable current amplifier; this will happen only during channel change to speed-up the tuning. Of the 8 output ports PO...P7, only 3 are used for band se- lection: band A, B and C. Band A >: 48,25 + 168,25 MHz (video carrier). Band B : 175,25 + 463,25 MHz (video carrier). Band C : 455,25 + 855,25 MHz (video carrier). The 3 used ports have output pins 7, 8 and 9 and are selec- ting, respectively, band C, B and A. The output with H logical value will select the related band and will take. in conduction one of the three RF amplifier: Fl or F2 or F3. Two of these three ports, pins 7 and 8, are used, also, to select one of the three oscillators of the tuner; these oscillators are inside TDA5331T IC. Depending on the logical level of the pins, will be selected different resistor networks (made up with R51, R52, R55, R56 and R57) giving to pin 17 of TDA5331T three different voltage levels: 0 V : selects band A. 2,5 V : selects band B. 5 Vv selects band C.

STEREO SOUND DECODING SOUND IF AND AUDIO SIGNAL PROC

ESSING The IF audio signal coming out from the tuner, Properly amplified, is applied to the IF {Intermediate Frequency) filter. The IF filter (FC201) is composed of a SAW (Surface Acoustic Wave) filter and will control the total selectivity of the TV receiver and, specifically, the response of the received channel in comparison of the adjacent channels. u The output of the tuner is symmetrical with:50 y impedance. The output of the SAW filter is, purposely, kept to a low value to minimize direct and three times reflections, and to obtain a correct video response. IF composite Signal, will be “filtered” and separated in the two main components, video and audio, by means of a SAW “quasi split sound" filter. This filter is composed with two sections with different Amplitude/Frequency response that can separate the IF video and sound signals. The two signals obtained in this way, are applied to the relevant decoders to draw the low frequency output signals.

ESSING The IF audio signal coming out from the tuner, Properly amplified, is applied to the IF {Intermediate Frequency) filter. The IF filter (FC201) is composed of a SAW (Surface Acoustic Wave) filter and will control the total selectivity of the TV receiver and, specifically, the response of the received channel in comparison of the adjacent channels. u The output of the tuner is symmetrical with:50 y impedance. The output of the SAW filter is, purposely, kept to a low value to minimize direct and three times reflections, and to obtain a correct video response. IF composite Signal, will be “filtered” and separated in the two main components, video and audio, by means of a SAW “quasi split sound" filter. This filter is composed with two sections with different Amplitude/Frequency response that can separate the IF video and sound signals. The two signals obtained in this way, are applied to the relevant decoders to draw the low frequency output signals. QUASI PARALLEL SOUND PROCESSOR The Quasi Parallel Sound processor acts, also, like a double FM decoder. TDA3857 IC, block diagram below, will process the audio signal; the main features of this IC are:

- Large band, gain controlled amplifier.

- Peak AGC. = Reference amplifier for video carrier regeneration,

- Inter carrier mixer for FM sound signal. ~

- Separated decoding for 5.5 and 5,74 MHZ inter carrier frequency.

The IF signal is simmetrically applied to TDA3857 input pins l and 20; the audio amplifier, three stages, will amplify the signal to the value apt to obtain perfect detection. The output level of the third stage, is kept constant, also for large variation of the input signal (gain reduction till 60 dB), by means of one error voltage amplifier that acts on all of the three amplifying stages. Subsequently, the amplified signal is demodulated with a synchronous demodulator that will multiply the IF signal with the 38,9 MHz reference frequency (different for other TV standard, 39,5 MHz for instance, for I standard) with a $=90°, obtained from the same signal by means of the tuned circuit L203- C207.

The multiplying demodulator eliminates the components of the double side bands and cut-off harmonic frequencies and the inter modulation products. In this way the noise level (buzz) generated from the video modulation will be reduced to mini- mum. The signal, so obtained and internally filtered, is outputted from C1201 IC pin 15 and, subsequently, is filtered and separated with two passband ceramic filters (5,5 and 5,74 MHz), and applied to pins 13 and 17. The two analogical carriers, 5,5 and 5,74 MHz, frequency modulated with stereo or bilingual signals, are decoded in two separate section of the sound processor circuit. Both of demodulators are made up with a limiting amplifier followed by a coincidence detector with an high AM rejection and with a negligible inter modulation. The cross-talk between FM demodulators will be very low due to high separation. The composite audio signal AF1, main channel (L+R)/2 in band base or mono compatible, and the AF2, (right channel or second language + pilot signal for identification) will sup- ply the audio decoder via two second order low pass active filters. The pilot carrier, amplitude modulated, is filtered with the passband filtered composed of L204 and C218. The circuit selectivity was developed to leave the lateral band (specially in the 274,1 MHz range) to get through with attenuation less than 1dB; due to this reason, the tuned circuit has a bandpass larger than 1 KHz (Q * 40). C1202 IC (MC44130) works as audio decoder. This IC was specially developed to solve all functions and controls for stereo transmission with two analogical carriers. It combines de enphasis, de matrixing, identification of broad- cast characteristics and the relevant matrix switching; it can switch, moreover, an external incoming signal. Three two way outputs, independent one from each other, are giving signals to Scart (Peritelevision) socket, to the power output amplifiers and to earphone preamplifier. The outputs for power output circuits (for loudspeaker) is volume, balance, treble and bass tone controlled and, furthermore it is possible (only for this output) to select pseudo-stereo and “spatial stereo" effects. The earphone output is provided only with volume control that is independent from the one working in the power output stage. . All described functions, are carried out under IIC bus control.

PILOT CARRIER IDENTIFICATION

The broadcast audio contents will be identified with pilot carrier demodulation. The pilot carrier frequency (transmitted with AF2 audio signal) is 54,6875 KHz and is AM modulated (50 %) with 117,5 Hz during stereo transmission and 274,1 Hz during bilingual transmission while is not modulate

d in case of mono transmission. The pilot carrier will be filtered with a passband filter (Q x 10) to obtain good separation from audio signal; the result will be going to a synchronous demodulator for AM demodulation. The demodulator works on the multiplying mode,and the reference frequency carrier is obtained from the local oscillator frequency working on PLL concept.

d in case of mono transmission. The pilot carrier will be filtered with a passband filter (Q x 10) to obtain good separation from audio signal; the result will be going to a synchronous demodulator for AM demodulation. The demodulator works on the multiplying mode,and the reference frequency carrier is obtained from the local oscillator frequency working on PLL concept.The decoded signal will be sent to two passband filters that will supply two identification bits related to the transmission received. The two bits will have the values shown- in the following table.

Frequency 117,5 Hz 274,

1 Hz MONO 0 0

STEREO 1 0

DUAL SOUND

ERROR 1 1

If the pilot carrier is not present, the VCO frequency will be fixed using the ceramic filter FC204 (f=437 KHz = 8 x f Pilot). The two identification bit, via interface circuit, are controlled all time by the microprocessor and, in this way, the matrix circuit automatic working will be Simplified. The fast switching of the matrix during broadcast switch-over is not recommended and to avoid mistake the microprocessor will check many times the identification signal before allowing the system to switch the matrix circuit. All procedures are carried out with “digital” filters that are counting the four possible states of the two identification bits (see preceeding table). The four “counting” filters used are:

1) Mono (FIM).

2) Stereo (FIS).

3) Dual sound (FID).

4) Error (FIE).

The FIA filter (Adaptive Delay Filter) will fix the counting time that can be 1,5 X 8 sec.. Every 50 msec., the microprocessor will increment one of the four filter in relation to the result coming out from the identification circuit. After every reading, the addition of these four filters will be compared with the actual value of FIA filter. When parity is achieved, the microprocessor will define the necessary switching. To switch the matrix circuit, it is necessary to obtain different filter percentage in relation t@rthe working matrix.

The matrix can be modified only if the transmission identification allows the following switching:

Mono €{------- > Stereo Mono {------- > Dual sound Stereo <------- > Dual sound

As already reported, the counting percentage needed to switch from one condition to another one (and, consequently, switch the relevant matrix) will be different in different modes depending on the actual transmission mode. - From Mono condition (actual identification): To switch the matrix circuit it is necessary to reach 87% of the total counting to select other matrix. The system will be forced to Mono also if the Error filter reach 12% of the counting, and this will be not influenced independently from values reached by other filters. - From Stereo to Dual sound: The identification circuit needs 62% of the counting to select other matrix. The system will be forced to Mono if the Error filter will reach 50%. If none of the filters will reach the switching threshold, the actual working matrix will not be switched off. - From every one of the selected matrix: If the running selection will not receive 100% of the counting, part of the remaining counting coming from the other counters will be added in the FIA filter to increment the “decision time” (pratically, the counting number will be increased). Due to the fact that these filters are working in a “percent” basis, the increment or decrement of the FIA filter counting will be exponential. The maximum added value will be limited to 36. j If the actual selection, anyhow, receives 100% of the counting, equal to the preceding selection, the FIA filter will be decremented 12% of the actual value. To sum up, the FIA filter, in relation to the values obtained on the four filters, can reach values in between 15 (minimum) and 99 (maximum). This will give a "decision time" in between 1,5 sec (15 minimum) and 8 sec (99 maximum). In case of system forced to Mono by Error counter overflow, the FIA filter will be brought back to maximum value.

Noisy antenna signal or no modulated pilot carrier transmission, can produce uncertain situations. In these cases the Mono matrix must be selected fastly than in normal conditions; for this reason the Error filter FIA has a lower threshold. ,

AUDIO LOW FREQUENCY CIRCUIT

AUDIO LOW FREQUENCY CIRCUIT The two low frequency audio signals, L and R, outputted from audio processor circuit, are applied to the TDA2009 (CI202) relevant sections to be power amplified. . The 24,5 V (unloaded) power supply is applied to pin 9 and the d.c. output of the two amplifiers will be V/2. The a.c. negative feedback is determined with resistor divi- der R232/R231 and the circuit gain will be: R231 + R232 R232 corresponding, in this case, with 32 dB. R230 and C247 are working as “Boucherot cell“. Integrated circuit CI204 will amplify the headphone signal (with impedence 2 16 u) and can output a R.M.S. power of about 20 mW (16 u) with standard modulation. AUDIO MUTING - Audio muting in stand-by On/Off. With the set in stand-by condition, or during On/off, the amplifiers are going in Mute condition via diodes D202 and D203 and transistors T205 and T206; the last transistor will receive H level from microprocessor pin 36. - Muting from remote control. Also in this condition, the command signal will be coming from microprocessor pin 36. - Muting without signal, during channel search or program/channel switching. In these cases, the muting signal will be coming from microprocessor (via software) to MC44130 IC, pins 19 and 21, through IM bus lines. The audio muting will,also, be effective on the audio output signals of the Scart socket.

MONO SIGNALS AUDIO CIRCUIT TDA3827 IC,

performs following functions:

- IF amplifier.

- Scart input audio switch.

- Limiter.

- Low frequency amplifier.

- FM demodulator.