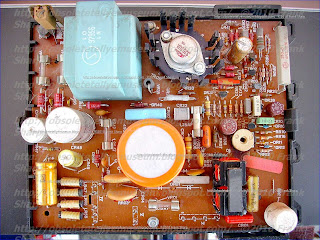

The NORDMENDE CHASSIS F7 here in this execution is the most advanced version of itself.

It's the first NORDMENDE featuring PROGRAMMABLE 6 DAYS CLOCK TIMER plus PLL SYNTHESIZER CHANNEL SEARCH usining a uCONTROLLER.

It's the first NORDMENDE featuring PROGRAMMABLE 6 DAYS CLOCK TIMER plus PLL SYNTHESIZER CHANNEL SEARCH usining a uCONTROLLER.Further Special Sound features are present with AV and sound connectors.

These circuits are based on a Fairchild Semiconductors Chipset which was barely used in that era of time.

The control board carrying all logical functions was employing 2 battreryes, one for clock and on for the channel memory RAM.

These series are rare because NORDMENDE in few months was passing under the control THOMSON CSF brand going to re-developing a completely new chassis design even with the same external models design.

The chassis design is modular and it's complex.

NORDMENDE DeLuxe COLORSONIC 2400 PRESTIGE SK3 COLOR CHASSIS F7 AMBIENT LIGHT RESPONSIVE CONTROL OF BRIGHTNESS, CONTRAST AND COLOR SATURATION Gain control arrangement useful in a television signal processing system

entiometer to the first amplifier to control its gain. A second potentiometer is coupled between a source of voltage equal to the extrapolated cut off voltage of the second amplifier and the gain controlling voltage source to receive a portion of the gain controlling voltage in accordance with the ratio of the extrapolated cut off voltages of the first and second amplifiers. The wiper of the second potentiometer is coupled to the second amplifier to couple a voltage developed at a predetermined point of the second potentiometer to the second amplifier to control its gain. In this manner, the contrast of the receiver may be varied over a relatively wide range while saturation is maintained substantially constant.

entiometer to the first amplifier to control its gain. A second potentiometer is coupled between a source of voltage equal to the extrapolated cut off voltage of the second amplifier and the gain controlling voltage source to receive a portion of the gain controlling voltage in accordance with the ratio of the extrapolated cut off voltages of the first and second amplifiers. The wiper of the second potentiometer is coupled to the second amplifier to couple a voltage developed at a predetermined point of the second potentiometer to the second amplifier to control its gain. In this manner, the contrast of the receiver may be varied over a relatively wide range while saturation is maintained substantially constant.1. In a color television signal processing system of the type including luminance and chrominance signal processing channels, apparatus comprising:

first and second amplifiers respectively included in said luminance and chrominance channels, said amplifiers having gain versus control voltage characteristics including linear portions extrapolated to cut-off at predetermined voltages which may or may not be the same voltage;

a gain controlling voltage source;

means for coupling said gain controlling voltage to said first amplifier to control its gain;

potentiometer means coupled between a fixed voltage substantially equal to the extrapolated cut-off voltage of said second amplifier and to said gain controlling voltage source to recieve a portion of said gain controlling voltage in accordance with the ratio of the extrapolated cut-off voltages of said first and second amplifiers; and

2. The apparatus recited in claim 1 wherein said means for coupling said gain controlling voltage to said first amplifier includes another potentiometer coupled between a source of fixed voltage substantially equal to the extrapolated cut-off voltage of said first amplifier and said gain controlling voltage source. 3. In a color television signal processing system of the type including luminance and chrominance signal processing channels, apparatus comprising:

first and second amplifiers respectively included in said luminance and chrominance channels, said amplifiers having gain control voltage characteristics including linear portions extrapolated to cut-off at substantially the same predetermined voltage;

a source of gain controlling voltage; and

means for coupling said gain controlling voltage to said first and second amplifiers.

4. Apparatus comprising:

first variable gain amplifying means for amplifying a first signal in response to a first DC control signal, said first amplifying means having a first gain versus DC control voltage characteristic including a linear region, said linear region having a gain substantially equal to 0 at a DC control voltage equal to VO ;

second variable gain amplifying means for amplifying a second signal in response to a second DC control signal, said second amplifying means having a second gain versus DC control voltage characteristic including a linear region, said linear region having a gain substantially equal to 0 at a DC control voltage equal to AVO, where A is a number greater than 0;

a first source of fixed voltage substantially equal to VO ;

a second source of fixed voltage substantially equal to AVO ;

means for developing a third DC control voltage v;

means for developing a portion Av of said third control voltage v;

first means for deriving said first control voltage including means for providing the difference between said third control voltage v and said fixed voltage VO and means for adding a predetermined portion of the difference between said third control voltage v and said fixed voltage VO to said DC control voltage v; and

second means for deriving said second control voltage including means for providing the difference between a portion Av of said third control voltage v and said fixed voltage AVO and means for adding a predetermined portion of the difference between said portion Av and said fixed voltage AVO to said DC control voltage v.

5. The apparatus recited in claim 4 wherein A is equal to 1. 6. The apparatus recited in claim 4 wherein said first amplifying means is included in a luminance channel of a televeision signal processing system and said second amplifying means is included in a chrominance channel of said television signal processing system. 7. The apparatus recited in claim 6 wherein means for developing said third control voltage includes means responsive to ambient light. 8. The apparatus recited in claim 4 wherein said first means includes first voltage divider means coupled between said fixed voltage VO and said third DC control voltage v; and wherein said second means includes second voltage divider means coupled between said fixed voltage AVO and said portion Av. 9. The apparatus recited in claim 8 wherein said first voltage divider means includes a first potentiometer, said first potentiometer having a wiper coupled to said first amplifying means; and wherein said second voltage divider means includes a second potentiometer, said second potentiometer having a wiper coupled to said amplifying means. 10. The apparatus recited in claim 4 wherein said second gain versus DC control voltage characteristic includes a region between said voltage AVO and a voltage VB where the gain is greater than 0, said voltage VB being substantially equal to the voltage at which said second amplifying means has a gain substantially equal to 0; and wherein said second source of fixed voltage includes means for coupling said voltage VB to said second amplifying means. 11. The apparatus recited in claim 10 wherein said second source of said voltage AVO includes a third source of fixed voltage VB ; potentiometer means coupled between said third source of fixed voltage VB and said means for developing said third DC control voltage; and means coupled to said potentiometer means for developing said voltage AVO at a point along said potentiometer means; said potentiometer means including a wiper coupled to said second amplifier means, said wiper being adjustable to couple a DC voltage VFB and said third control voltage to said second amplifying means.

Recently, the maximum brightness available from television receivers has increased sufficiently so that a pleasing image may be reproduced under conditions of high ambient light as well as under conditions of low ambient light. Apparatus is known for automatically controlling the contrast and brightness properties of a television receiver in response to ambient light to provide a pleasing image over a range of ambient light conditions. Such apparatus is described in U.S. Pat. Nos. 3,027,421, entitled "Circuit Arrangements For Automatically Adjusting The Brightness And The Contrast In A Television Receiver," issued to H. Heijligers on Mar. 27, 1962 and 3,025,345, entitled "Circuit Arrangement For Automatic Readjustment Of The Background Brightness And The Contrast In A Television Receiver," issued to R. Suhrmann on Mar. 13, 1962.

Apparatus is also known for automatically controlling the contrast and saturation properties of a color television receiver by controlling the gains of luminance and chrominance channel amplifiers, respectively, in response to ambient light. Such apparatus is described in U.S. Pat. Nos. 3,813,686 entitled "Ambient Light Responsive Control Of Brightness, Contrast And Color Saturation," issued to Eugene Peter Mierzwinski, on May 28, 1974 and 3,814,852 entitled "Ambient Light Responsive Control Of Brightness, Contrast and Color Saturation," issued to Eugene P. Mierzwinski on June 4, 1974.

Also of interest is apparatus for manually controlling the gains of luminance and chrominance channel amplifiers. Such apparatus is described in U.S. Pat. Nos. 3,374,310, entitled "Color Television Receiver with Simultaneous Brightness and Color Saturation Controls," issued to G.L. Beers on Mar. 19, 1968; 3,467,770, entitled "Dual Channel Automatic Control Circuit," issued to DuMonte O. Voigt on June 7, 1966; and 3,715,4

63, entitled "Tracking Control Circuits Using a Common Potentiometer," issued to Lester Tucker Matzek, on Feb. 6, 1973.

63, entitled "Tracking Control Circuits Using a Common Potentiometer," issued to Lester Tucker Matzek, on Feb. 6, 1973.When the gain of luminance channel is adjusted to control the contrast of an image, either manually or automatically, in response to ambient light, it is desirable to simultaneously control the gain of the chrominance channel in such a manner that the ratio of the gains of the luminance and chrominance channels is substantially constant over a wide range of contrast control to maintain constant saturation. If the proper ratio between the amplitudes of the chrominance and luminance signals is not maintained incorrect color reproduction may result. For instance, if the amplitude of the luminance signals are increased without correspondingly increasing the amplitude of the chrominance signals, colors may become desaturated, i.e., they will appear washed out or pastel in shade. Furthermore, it may be desirable to provide controls for presetting the gains of the luminance and chrominance channels to compensate for tolerance variations in other portions of the television signal processing apparatus.

In accordance with another feature of the present invention, the means for coupling said gain controlling voltage to said first amplifier includes another potentiometer coupled between a source of fixed voltage substantially equal to the extrapolated cut off voltage of said first amplifier and said gain controlling voltage source.

In accordance with still another feature of the present invention the gain controlling voltage source includes an element responsive to ambient light .

These and other aspects of the present invention may best be understood by references to the following detailed description and accompanying drawing in which:

FIG. 1 shows the general arrangement, partly in block diagram form and partly in schematic diagram form, of a color television receiver employing an embodiment of the present invention;

FIG. 1A shows, in schematic form, a modification to the embodiment shown in FIG. 1;

FIG. 2 shows graphical representation of gain versus control voltage characteristics of amplifiers utilized in the embodiment shown in FIG. 1;

FIG. 3 shows graphical representations of gain versus control voltage characteristics of amplifiers which may be utilized in the receiver shown in FIG. 1;

FIG. 4 shows, in schematic form, another embodiment of the present invention which may be utilized to control the amplifiers whose gain versus control voltage characteristics are shown in FIG. 3;

FIG. 5 shows, in schematic form, an amplifier which may be utilized in the receiver shown in FIG. 1; and

FIG. 6 shows, in schematic form, another amplifier which may be utilized in the receiver shown in FIG. 1.

Referring now

to FIG. 1, the general arrangement of a color television receiver employing the present invention includes a video signal processing unit 112 responsive to radio frequency (RF) television signals for generating, by means of suitable intermediate frequency (IF) circuits (not shown) and detection circuits (not shown), a composite video signal comprising chrominance, luminance, sound and synchronizing signals. The output of signal processing unit 112 is coupled to chrominance channel 114, luminance channel 116, a channel 118 for processing the synchronizing signals and a channel (not shown) for processing sound signals.

to FIG. 1, the general arrangement of a color television receiver employing the present invention includes a video signal processing unit 112 responsive to radio frequency (RF) television signals for generating, by means of suitable intermediate frequency (IF) circuits (not shown) and detection circuits (not shown), a composite video signal comprising chrominance, luminance, sound and synchronizing signals. The output of signal processing unit 112 is coupled to chrominance channel 114, luminance channel 116, a channel 118 for processing the synchronizing signals and a channel (not shown) for processing sound signals.Chrominance processing channel 114 includes chrominance processing unit 120 which serves to remove chrominance signals from the composite video signal and otherwise process chrominance signals. Chrominance signal processing unit 120 may include, for example, automatic color control (ACC) circuits for adjusting the amplitude of the chrominance channels in response to amplitude variations of a reference signals, such as a color burst signal, included in the commposite video signal. Chrominance signal processing circuits of the type described in the U.S. Pat. No. 3,740,462, entitled "Automatic Chroma Gain Control System," issued to L.A. Harwood, on June 19, 1973 and assigned to the same assignee as the present invention are suitable for use as chrominance processing unit 120.

The output of the chrominance signal processing unit 120 is coupled to chrominance amplifier 122 which serves to amplify chrominance signals in response to a DC signal vC generated by gain control network 142. As illustrated, chrominance amplifier 122 provides chrominance signals to a chroma demodulator 124. An amplifier suitable for use as chrominance amplifier 122 will subsequently be described with reference to FIG. 6.

Chroma demodulator 124 derives color difference signals representing, for example, R-Y, B-Y and G-Y information from the chrominance signals. Demodulator circuits of the general type illustrated by the chrominance amplifier CA 3067 integrated circuit manufactured by RCA Corporation are suitable for use as chrominance demodulator 124.

The color difference signals are applied to a video driver 126 where they are combined with the output signals -Y of luminance channel 116 to produce color signals of the appropriate polarity, representing for example, red (R), green (G) and blue (B) information. The color signals are coupled to kinescope 128.

Luminance channel 116 includes a first luminance signal processing unit 129 which relatively attenuates undesirable signals, such as chrominance or sound signals or both, present in luminance channel 116 and otherwise proces ses the luminance signals. The output of first luminance processing unit 129 is coupled to luminance amplifier 130 which serves to amplify the luminance signals in response to a DC control signal vL generated by gain control unit 142 to thereby determine the contrast of a reproduced image. An amplifier suitable for use as luminance amplifier 130 will subsequently be described with reference to FIG. 5. The output of luminance amplifier 130 is coupled to second luminance signal processing unit 132 which serves to further process luminance signals. A brightness control unit 131 is coupled to luminance signal processing unit 132 to control the DC content of the luminance signals. The output -Y of luminance processing unit 132 is coupled to kinescope driver 126.

Channel 118 includes a sync separator 134 which separates horizontal and vertical synchronizing pulses from the composite video signal. The synchronizing pulses are coupled to horizontal deflection circuit 136 and vertical deflection circuit 138. Horizontal deflection circuit 136 and vertical deflection circuit 138 are coupled to kinescope 128 and to a high voltage unit 140 to control the generation and deflection of one or more electron beams generated by kinescope 128 in the conventional manner. Deflection circuits 136 and 138 also generate horizontal and vertical blanking signals which are coupled to luminance signal processing unit 132 to inhibit its operation during the horizontal and vertical retrace intervals.

The base of transistor 152 is coupled to the wiper of a potentiometer 146. One end of potentiometer 146 is coupled to the source of positive supply voltage VO through a fixed resistor 144. The other end of potentionmeter 146 is coupled to ground through a light dependent resistor (LDR) 148. LDR 148 is a resistance element whose impedance varies in inverse relationship with light which impinges on it. LDR 148 may comprise a simple cadmium sulfide type of light dependent element or other suitable light dependent device. LDR 148 is desirably mounted to receive ambient light in the vicinity of the screen of kinescope 128.

A single pole double-throw switch 150 has a pole coupled to the junction of potentiometer 146 and LDR 148. A resistor 151 is coupled between the wiper of potentiometer 146 and the other pole of switch 150. The arm of switch 150 is coupled to ground.

The general arrangement shown in FIG. 1 is suitable for use in a color television receiver of the type shown, for example, in RCA Color Television Service Data 1973 No. C -8 for a CTC-68 type receiver, published by RCA Corporation, Indianapolis, Indiana.

In operation, gain control circuit 142 maintains the ratio of the gain of chrominance amplifier 122 to the gain of amplifier 130 constant in order to maintain constant saturation while providing for contrast adjustment either manually by means of potentiometer 146 or automatically by means of LDR 148. If the gain of luminance were adjusted to control the contrast of an image without a corresponding change in the gain of chrominance amplifier 122, the amplitudes of luminance signals -Y and color difference signals R-Y, B-Y and G-Y would not, in general, be in the correct ratio when combined by divider 126 to provide the desired color.

When switch 140 is in the MANUAL position, the gains of chrominance amplifier 122 and luminance amplifier 130 are controlled by adjustment of the position of potentiometer 146. When switch 150 is in the AUTO position the gain of the chrominance amplifier 122 and luminance amplifier is automatically controlled by the response of LDR 148 to ambient light conditions. The voltage developed at the wiper of potentiometer 146 (base of transistor 152) when switch 150 is in the AUTO position is inversely related to the ambient light recieved by LDR 148. It is noted that the values of resistors 114, potentiometer 146, LDR 148 and resistor 151 are desirably selected such that the adjustment of the wiper arm of potentiometer 146 when switch 150 is in the MANUAL position does not substantially affect the voltage developed at the base of transister 152 when switch 150 is placed in the AUTO position.

The control voltage v developed at the wiper arm of potentiometer 146 is coupled through emitter-follower transistor 152 to the common junction of potentiometer 156 and variable resistor 159. A control voltage vL comprising v plus a predetermined portion of the difference VO -v developed across the series connection of fixed resistor 154 and potentiometer 156, depending on the setting of potentiometer 156, is coupled to luminance amplifier 130 to control its gain. Similarly, a control voltage vC comprising v plus a predetermined portion of the difference voltage VO -v developed across the series connection of potentiometer resistor 158 and variable resistor 159, depending on the setting of the wiper of potentiometer 158, is coupled to chrominance amplifier 122 to control its gain.

The gain of luminance amplifier 130 may be pre-set to a desired value by the factory adjustment of potentiometer 156. Similarly, variable resistor 159 is provided to allow factory pre-set of the gain of the chrominance amplifier 122. Potentiometer 158 is provided to allow customer control of saturation.

R

eferring to FIG. 2, the gain versus voltage characteristics of chroma amplifier 122 (gC) and luminance amplifier 130 (gL) are shown. The characteristic gC has a reversed S-shape including a linear portion 214. Extrapolated linear portion 214 of gC intersects the GAIN axis at GC and intersects the CONTROL VOLTAGE axis at VO. Similarly, the characteristics gL has a reverse S-shape characteristic including a linear portion 212. Extrapolated linear portion 214 of gL intersects the GAIN axis at GL and intersects the CONTROL VOLTAGE axis at VO.

eferring to FIG. 2, the gain versus voltage characteristics of chroma amplifier 122 (gC) and luminance amplifier 130 (gL) are shown. The characteristic gC has a reversed S-shape including a linear portion 214. Extrapolated linear portion 214 of gC intersects the GAIN axis at GC and intersects the CONTROL VOLTAGE axis at VO. Similarly, the characteristics gL has a reverse S-shape characteristic including a linear portion 212. Extrapolated linear portion 214 of gL intersects the GAIN axis at GL and intersects the CONTROL VOLTAGE axis at VO.From FIG. 2, the expression for linear portion 212 of gL is ##EQU1## The expression for linear portion 214 of gC is ##EQU2## From FIG. 1, the expression for vL is vL = v + (VO -v) K1 [3]

where K1 is determined by the voltage division of fixed resistor 154 and potentiometer 156 at the wiper of potentiometer 156. When the wiper of potentiometer 156 is at the emitter of transistor 152, K1 =0. The expression for vC is vC = v + (VO -v)K2 [4]

where K2 is determined by the voltage division of potentiometer 158 and fixed resistor 159 at the wiper of potentiometer 158. By combining equations [1] and [3], the equation for gL becomes ##EQU3## By combining equations [2] and [4], the equation for gC becomes ##EQU4## The ratio of gL to gC is thus ##EQU5## It is noted that this ratio is independent of DC control voltage v. Thus, although DC control voltage v may be varied either manually or in response to ambient light to control the contrast of an image reproduced by kinescope 128, the saturation remains constant.

With re

ference to FIG. 2, it is noted that although the linear portion 214 of gC has an extrapolated gain equal to 0 at a control voltage equal to VO, the non-linear portion of gC does not attain a gain equal to 0 until a control voltage equal to VB. That is, a control voltage of VO will not cut-off chrominance amplifier 122.

ference to FIG. 2, it is noted that although the linear portion 214 of gC has an extrapolated gain equal to 0 at a control voltage equal to VO, the non-linear portion of gC does not attain a gain equal to 0 until a control voltage equal to VB. That is, a control voltage of VO will not cut-off chrominance amplifier 122.In FIG. 1A there is shown, in schematic form, a modification to the arrangement of gain control network 142 of FIG. 1 with provisions which allow a viewer to cut off chrominance amplifier 122 to produce a more pleasing image under conditions of poor color reception due, for example, to noise or interference. The modifications to gain control unit 142 shown in FIG. 1A include coupling potentiometer resistor 158 between a source of positive supply voltage VB, the value of VB being greater than the value of VO, and coupling a resistor 160 from a tap-off point 162 along potentiometer 158 to ground. The value of potentiometer 158 and resistor 160 and the location of tap 162 are selected so that voltage VO is developed at tap 162.

The arrangement shown in FIG. 1A allows for the adjustment of contrast while constant saturation is maintained and additionally allows a viewer, by adjusting the wiper of potentiometer 158 to voltage VB, to cut off chrominance amplifier 122.

Referring to FIG. 3 there are shown gain versus DC control voltage characteristics of chrominance and luminance amplifiers which do not have the same extrapolated linear cut off control voltage. The gain versus control voltage characteristic gL ' of the luminance amplifier has a reverse S-shape characteristic including a linear portion 312. Extrapolated linear portion 312 of gL ' intersects the GAIN axis at a gain GL ' and intersects the CONTROL VOLTAGE axis at a voltage VO '. The gain versus control voltage characteristic gC ' of the chrominance amplifier has a reverse S-shape characteristic having a linear portion 314. Extrapolated linear portion 314 of gC ' intersects the GAIN axis at a gain GC ' and intersects the CONTROL VOLTAGE axis at a voltage AVO ', where A is a number greater than zero.

From FIG. 3, the expression for linear portion 312 of gL ' is ##EQU6## where vL ' is the DC conrol voltage coupled to the luminance amplifier. The expression for linear portion 314 of gC ' is ##EQU7## where vC ' is the DC control voltage coupled to the chrominance amplifier.

A modified form of the control network 142 of FIG. 1 suitable for controlling the gain of a chrominance and a luminance amplifier having characteristics such as shown in FIG. 3 is shown in FIG. 4. Similar portions of FIGS. 1 and 4 are identified by reference numbers having the same last two significant digits and primed (') designations. The modified portions of FIG. 1 shown in FIG. 4 include the series connection resistors 460 and 462 coupled between the emitter of transistor 452 to ground. The values of resistors 460 and 462 are selected so that a portion Av' of the DC control voltage v' developed at the emitter of transistor 452 is developed at the junction of resistors 460 and 462. Furthermore, the series connection of potentiometer 458 and variable resistor 459 is coupled between the junction of resistor 460 and 462 and a source of positive supply voltage AVO '.

From FIG. 4, the expression for control voltage vL ' developed at the wiper of potentiometer 456 is vL ' = v' + (vO '-v')K1 ' [10]

From FIG. 4, the expression for control voltage vL ' developed at the wiper of potentiometer 456 is vL ' = v' + (vO '-v')K1 ' [10]where K1 ' is determined by the voltage division at the wiper of potentiometer 456. The expression for control voltage vC ' developed at the wiper of potentiometer 458 is VC ' = Av' + (AVO ' - Av')K 2 ' [11]

where K2 ' is determined by the voltage division at the wiper of potentiometer 458. By combining equations [8] and [10], ##EQU8## By combining equations [9] and [11], ##EQU9## The ratio of gL ' to gC ' is given by the expression ##EQU10## It is noted that this ratio is independent of DC control voltage v'. Therefore, gain control network 442 of FIG. 4 also allows for the adjustment of contrast while maintaining constant saturation.

It is noted that if A were made equal to 1, the arrangement gain control unit 442 would be suitable to control the gains of chrominance and luminance amplifiers having the characteristics shown in FIG. 2.

In FIG. 5, there is shown an amplifier suitable for use as luminance amplifier 130 of FIG. 1. The amplifier includes a differential amplifier comprising NPN transistors 532 and 534. The commonly coupled emitters of transistors 532 and 534 are coupled to the collector of an NPN transistor 528. The emitter of transistor 528 is coupled via a resistor 530 to ground. The collector of transistor 532 and the collector of transistor 534, via load resistor 536, is coupled to a bias voltage provided by bias supply 546, illustrated as a series connection of batteries. The bases of transistors 532 and 534 are respectively coupled to a lower bias voltage through resistors 533 and 535 respectively.

An input signal, such as, for example, the output signal provided by first luminance processing circuit 129 of FIG. 1 is coupled to the base of transistor 532 via terminal 542. The output signal of the amplifier is developed at the collector of transistor 534 and coupled to output terminal 544.

A DC control voltage, such as vL provided by gain control unit 142 of FIG. 1, is coupled to the base of an NPN transistor 514, arranged as an emitter-follower, via terminal 512. The collector of transistor 514 is coupled to bias supply 546. The emitter of transistor 514 is coupled to ground through the series connection of resistor 516, a diode connected transistor 518 and resistor 520.

The anode of diode 520 is coupled to the base of an NPN transistor 538. The collector of transistor 538 is coupled to the collector of transistor 534 while its emitter is coupled to ground through resistor 540. Transistor 538, resistor 540, diode 518 and resistor 520 are arranged in a current mirror configuration.

The emitter of transistor 514 is coupled to the base of a PNP transistor 522. The emitter of transistor 522 is coupled to bias supply 546 while its collector is coupled to the base of transistor 528 and to ground through the series connection of a diode connected transistor 524 and resistor 526. Transistor 528, resistor 530, diode 524 and resistor 526 are arranged in a current mirror configuration

In operation, the DC control voltage coupled

to terminal 512 is coupled in inverted fashion to the anode of diode 524 by transistor 522. As a result, current directly related to the voltage developed at the anode of diode 524 flows through diode 524 and resistor 526. Due to the operation of the current mirror arrangement of diode 524, resistor 526, transistor 528 and resistor 530, a similar current flows through the emitter circuit of transistor 528. The gain of the differential amplifier comprising transistors 532 and 534 is directly related to this current flowing in the emitter circuit of transistor 528, and therefore is inversely related to the DC control voltage at terminal 512. The gain versus DC control voltage characteristics of the differential is similar to gL shown in FIG. 2.

to terminal 512 is coupled in inverted fashion to the anode of diode 524 by transistor 522. As a result, current directly related to the voltage developed at the anode of diode 524 flows through diode 524 and resistor 526. Due to the operation of the current mirror arrangement of diode 524, resistor 526, transistor 528 and resistor 530, a similar current flows through the emitter circuit of transistor 528. The gain of the differential amplifier comprising transistors 532 and 534 is directly related to this current flowing in the emitter circuit of transistor 528, and therefore is inversely related to the DC control voltage at terminal 512. The gain versus DC control voltage characteristics of the differential is similar to gL shown in FIG. 2.Further, a current is developed through the series connection of resistor 516, diode 518 and resistor 520 in direct relationship to the DC control coupled to terminal 512. A similar current is developed through resistor 540 due to the operation of the current mirror comprising diode 518, resistor 520, transistor 538 and resistor 540. This current is of the opposite sense to that provided by the current mirror arrangement of diode 524, resistor 526, transistor 528 and resistor 530 and is coupled to the collector of transistor 534 so that the DC voltage at output terminal 544 does not substantially vary with the DC control voltage.

In FIG. 6, ther

e is shown an amplifier suitable for use as chroma amplifier 120 of FIG. 1. The amplifier shown in FIG. 6 is of the type described in U.S. patent application Ser. No. 530,405 entitled "Controllable Gain Signal Amplifier," fled by L.A. Harwood et al. on Dec. 6, 1974.

e is shown an amplifier suitable for use as chroma amplifier 120 of FIG. 1. The amplifier shown in FIG. 6 is of the type described in U.S. patent application Ser. No. 530,405 entitled "Controllable Gain Signal Amplifier," fled by L.A. Harwood et al. on Dec. 6, 1974.The amplifier comprises a differential amplifier including NPN transistors 624 and 625 having their bases coupled to terminal 603 via a resistor 626. Chrominance signals, provided by a source of chrominance signals such as chrominance processing unit 120 of FIG. 1, are coupled to terminal 603. The current conduction paths between the collectors and emitters of transistors 624 and 625 are respectively coupled to ground via resistors 628, 629 and 630.

A current splitter circuit comprising an NPN transistor 632 and a diode 634 is coupled to the collector of transistor 624. Diode 634 and the base-emitter junction of transistor 632 are poled in the same direction with respect to the flow of collector current in transistor 624. It desirable that conduction characteristics of transistor 632 and diode 635 be substantially matched. Similarly, the collector of transistor 625 is coupled to a second current splitter comprising a transistor 633 and a diode 635.

In operation, a quiescent operating current is provided through resistor 630. In the absence of an input signal at terminal 603, this current will divide substantially equally between the similarly biased transistors 624 and 625. If the DC control voltage at terminal 602 is near ground potential, transistor 646 will be effectively cut off and no current will flow in resistor 652 and diodes 634 and 635. In that case, neglecting the normally small difference betweeen collector and emitter currents of NPN transistors, the collector currents of transistors 624 and 625 will flow, respectively, in transistors 632 and 633. The transistors 632 and 633 are operated in common base mode and form cascode signal amplifiers with respective transistors 624 and 625. With the DC control voltage near ground potential, one-half of the quiescent current from resistor 630 flows in each of the load circuits and maximum gain for chrominance signals supplied from terminal 603 is provided.

Transistor 646 will conduct when the DC control voltage approaches the bias voltage supplied to the bases of transistors 632 and 633 of the current splitters. By selection of the circuit parameters, diodes 634 and 635 may be arranged to operate in a range between cut off to the conduction of all of the quiescent operating current supplied via resistor 630, thereby cutting off transistors 632 and 633 to provide no output signals at terminals 640 and 641.

At a DC control voltage intermediate to that corresponding to cut off of transistors 632 and 633 on the one hand and cut off of diodes 634 and 635 on the other hand, the voltage gain of the illustrated amplifier will vary in a substantially linear manner with the DC control voltage.

It is noted that although the characteristics shown in FIGS. 2 and 3 were reversed S-shaped characteristics, the characteristics could have other shapes including linear portions. For example, the characteristics could be substantially linear. Furthermore, with reference to FIG. 3, although gC ' was shown as having a linear portion that had a cut off control voltage lower than the cut off control voltage of the linear portion of gL ', the cut off control voltage of the linear portion of gC ' could be greater than the cut off voltage for the linear region of gL '. In addition, the gain control units and associate amplifiers could be arranged to utilize voltages opposite in polarity to those shown. These and other modifications are intended to be within the scope of the invention.

It is noted that although the characteristics shown in FIGS. 2 and 3 were reversed S-shaped characteristics, the characteristics could have other shapes including linear portions. For example, the characteristics could be substantially linear. Furthermore, with reference to FIG. 3, although gC ' was shown as having a linear portion that had a cut off control voltage lower than the cut off control voltage of the linear portion of gL ', the cut off control voltage of the linear portion of gC ' could be greater than the cut off voltage for the linear region of gL '. In addition, the gain control units and associate amplifiers could be arranged to utilize voltages opposite in polarity to those shown. These and other modifications are intended to be within the scope of the invention.

A Cockcroft-Walton cascade circuit comprises an input voltage source and a pumping and storage circuit with a series array of capacitors with pumping and storage portions of the circuit being interconnected by silicon rectifiers, constructed and arranged so that at least the capacitor nearest the voltage source, and preferably one or more of the next adjacent capacitors in the series array, have lower tendency to internally discharge than the capacitors in the array more remote from the voltage source.

1. An improved voltage multiplying circuit comprising,

2. An improved voltage multiplying circuit in accordance with claim 1 wherein said first pumping capacitor is a self-healing impregnated capacitor which is impregnated with a high voltage impregnant.

3. An improved voltage multiplying circuit in accordance with claim 1 wherein said first pumping capacitor comprises a foil capacitor.

Description:

BACKGROUND OF THE INVENTION

The invention relates in general to Cockcroft-Walton cascade circuits for voltage multiplication and more particularly to such circuits with a pumping circuit and a storage circuit composed of capacitors connected in series, said pumping circuits and storage circuit being linked with one another by a rectifier circuit whose rectifiers are preferably silicon rectifiers, especially for a switching arrangement sensitive to internal discharges of capacitors, and more especially a switching arrangement containing transistors, and especially an image tube switching arrangement.

Voltage multiplication cascades composed of capacitors and rectifiers are used to produce high D.C. voltages from sinusoidal or pulsed alternating voltages. All known voltage multiplication cascades and voltage multipliers are designed to be capacitance-symmetrical, i.e., all capacitors used have the same capacitance. If U for example is the maximum value of an applied alternating voltage, the input capacitor connected directly to the alternating voltage source is charged to a D.C. voltage with a value U, while all other capacitors are charged to the value of 2U. Therefore, a total voltage can be obtained from the series-connected capacitors of a capacitor array.

In voltage multipliers, internal resistance is highly significant. In order to obtain high load currents on the D.C. side, the emphasis in the prior art has been on constructing voltage multipliers with internal resistances that are as low as possible.

Internal resistance of voltage multipliers can be reduced by increasing the capacitances of the individual capacitors by equal amounts. However, the critical significance of size of the assembly in the practical application of a voltage multiplier, limits the extent to which capacitance of the individual capacitors can be increased as a practical matter.

In television sets, especially color television sets, voltage multiplication cascades are required whose internal resistance is generally 400 to 500 kOhms. Thus far, it has been possible to achieve this low internal resistance with small dimensions only by using silicon diodes as rectifiers and metallized film capacitors as the capacitors.

When silicon rectifiers are used to achieve low internal resistance, their low forward resistance produces high peak currents and therefore leads to problems involving the pulse resistance of the capacitors. Metallized film capacitors are used because of space requirements, i.e., in order to ensure that the assembly will have the smallest possible dimensions, and also for cost reasons. These film capacitors have a self-healing effect, in which the damage caused to the capacitor by partial evaporation of the metal coating around the point of puncture (pinhole), which develops as a result of internal spark-overs, is cured again. This selfhealing effect is highly desirable as far as the capacitors themselves are concerned, but is not without its disadvantages as far as the other cirucit components are concerned, especially the silicon rectifiers, the image tubes, and the components which conduct the image tube voltage.

It is therefore an important object of the invention to improve voltage multiplication cascades of the type described above.

It is a further object of the invention to keep the size of the entire assembly small and the internal resistance low.

It is a further object of the invention to increase pulse resistance of the entire circuit.

It is a further object of the invention to avoid the above-described disadvantageous effects on adjacent elements.

It is a further object of the invention to achieve multiples of the foregoing objects and preferably all of them consistent with each other.

SUMMARY OF THE INVENTION

In accordance with the invention, the foregoing objects are met by making at least one of the capacitors in the pumping circuit, preferably including the one which is adjacent to the input voltage source, one which is less prone to internal discharges than any of the individual capacitors in the storage circuit.

The Cockcroft-Walton cascade circuit is not provided with identical capacitors. Instead, the individual capacitors are arranged according to their loads and designed in such a way that a higher pulse resistance is attained only in certain capacitors. It can be shown that the load produced by the voltage in all the capacitors in the multiplication circuit is approximately the same. But the pulse currents of the capacitors as well as their forward flow angles are different. In particular, the capacitors of the pumping circuit are subjected to very high loads in a pulsed mode. In the voltage multiplication cascade according to the invention, these capacitors are arranged so that they exhibit fewer internal discharges than the capacitors in the storage circuit.

The external dimensions of the entire assembly would be unacceptably large if one constructed the entire switching arrangement using such capacitors.

The voltage multiplication cascade according to the invention also makes it possible to construct a reliably operating

arrangement which has no tendency toward spark-overs, consistent with satisfactory internal resistance of the voltage multiplication cascade and small dimensions of the entire assembly. This avoids the above cited disadvantages with respect to the particularly sensitive components in the rest of the circuit and makes it possible to design voltage multiplication cascades with silicon rectifiers, which are characterized by long lifetimes. Hence, a voltage multiplication cascade has been developed particularly for image tube circuits in television sets, especially color television sets, and this cascade satisfies the highest requirements in addition to having an average lifetime which in every case is greater than that of the television set.

A further aspect of the invention is that at least one of the capacitors that are less prone to internal discharges is a capacitor which is impregnated with a high-voltage impregnating substance, especially a high-voltage oil such as polybutene or silicone oil, or mixtures thereof. In contrast to capacitors made of metallized film which have not been impregnated, this allows the discharge frequency due to internal discharges or spark-overs to be reduced by a factor of 10 to 100.

According to a further important aspect of the invention, at least one of the capacitors that are less prone to internal discharges is either a foil capacitor or a self-healing capacitor. In addition, the capacitor in the pumping circuit which is adjacent to the voltage source input can be a foil capacitor which has been impregnated in the manner described above, while the next capacitor in the pumping circuit is a self-healing capacitor impregnated in the same fashion.

Other objects, features and advantages of the invention will be apparent from the following detailed description of preferred embodiments, taken in connection with the accompanying drawing, the single FIGURE of which:

BRIEF DESCRIPTION OF THE DRAWING

is a schematic diagram of a circuit made according to a preferred embodiment of the invention.

DETAILED DESCRIPTION OF PREFERRED EMBODIMENTS

The voltage multiplier comprises capacitors C1 to C5 and rectifiers D1 to D5 connected in a cascade. An alternating voltage source UE is connected to terminals 1 and 2, said voltage source supplying for example a pulsed alternating voltage. Capacitors C1 and C2 form the pumping circuit while capacitors C3, C4 and C5 form the storage circuit.

In the steady state, capacitor C1 is charged to the maximum value of the alternating voltage UE as are the other capacitors C2 to C5. The desired high D.C. voltage UA is picked off at terminals 3 and 4, said D.C. voltage being composed of the D.C. voltages from capacitors C3 to C5. Terminal 3 and terminal 2 are connected to one pole of the alternating voltage source UE feeding the circuit, which can be at ground potential. In the circuit described here, a D.C. voltage UA can be picked off whose voltage value is approximately 3 times the maximum value of the pulsed alternating voltage UE. By using more than five capacitors, a correspondingly higher D.C. voltage can be obtained.

The individual capacitors are discharged by disconnecting D.C. voltage UA. However, they are constantly being recharged by the electrical energy supplied by the alternating voltage source UE, so that the voltage multiplier can be continuously charged on the output side.

According to the invention, in this preferred embodiment, capacitor C1 and/or C2 in the pumping circuit are designed so that they have a lower tendency toward internal discharges than any of the individual capacitors C3, C4 and C5 in the storage circuit.

It is evident that those skilled in the art, once given the benefit of the foregoing disclosure, may now make numerous other uses and modifications of, and departures from the specific embodiments described herein without departing from the inventive concepts. Consequently, the invention is to be construed as embracing each and every novel feature and novel combination of features present in, or possessed by, the apparatus and techniques herein disclosed and limited solely by the scope and spirit of the appended claims.

Inventors:Petrick, Paul (Landshut, DT)

Schwedler, Hans-peter (Landshut, DT)

Holzer, Alfred (Schonbrunn, DT)

ERNST ROEDERSTEIN SPEZIALFABRIK

US Patent References:

3714528 ELECTRICAL CAPACITOR WITH FILM-PAPER DIELECTRIC 1973-01-30 Vail

3699410 SELF-HEALING ELECTRICAL CONDENSER 1972-10-17 Maylandt

3463992 ELECTRICAL CAPACITOR SYSTEMS HAVING LONG-TERM STORAGE CHARACTERISTICS 1969-08-26 Solberg

3457478 WOUND FILM CAPACITORS 1969-07-22 Lehrer

3363156 Capacitor with a polyolefin dielectric 1968-01-09 Cox

2213199 Voltage multiplier 1940-09-03 Bouwers et al.

NORDMENDE DeLuxe COLORSONIC 2400 PRESTIGE SK3 COLOR CHASSIS F7 Frequency synthesizer tuning system for television receivers:

" A method for tuning a television receiver having automatic frequency control to the carrier frequency of a selected broadcast channel with an associated channel number including generating a variable frequency signal by means of a local oscillator, generating a reference frequency signal by means of a reference oscillator, and generating a local oscillator correction signal for matching an intermediate frequency signal derived from said local oscillator signal and the carrier frequency signal with a predetermined nominal intermediate frequency signal, said method being characterized by the use of a microcomputer and comprising:

generating binary signals representing first and second digital tune words, said digital tune words representing a selected channel;

storing said first and second digital tune words in a first data memory in said microcomputer;

reading said first and second digital tune words from said first memory and generating a divided-down local oscillator frequency by the use of said first digital tune word and a divided-down reference oscillator frequency by the use of said second digital tune word;

comparing said divided-down local oscillator and reference frequencies and generating a control signal representative of the difference in frequency of said divided-down local oscillator and reference frequencies;

coupling said control signal to said local oscillator for causing it to be locked to the frequency of said received carrier signal;

mixing the local oscillator frequency signal and the carrier frequency signal to generate an intermediate frequency signal;

comparing said intermediate frequency signal with said predetermined nominal intermediate frequency signal and providing a tuning voltage to said microcomputer, said tuning voltage being indicative of the magnitude and direction of a tuning error between said intermediate frequency signal and said predetermined nominal intermediate frequency signal;

incrementally adjusting the reference oscillator frequency by means of a tuning signal provided to said reference oscillator by said microcomputer in response to said tuning voltage;

detecting when the incrementally changing, divided-down reference oscillator frequency causes the intermediate frequency signal to pass said predetermined nominal intermediate frequency signal; and

incrementally stepping the divided-down reference oscillator frequency back a predetermined number of steps following the passage of said predetermined nominal intermediate frequency signal by said intermediate frequency signal in tuning said television receiver to the selected channel.

"

1. A tuning system for the tuner of a television receiver capable of receiving a composite television signal and including frequency discriminator (AFT) circuit means, said system including in combination:

a reference oscillator providing a reference signal at a predetermined frequency;

a local oscillator in the tuner providing a variable output frequency in response to the application of a control signal thereto;

a programmable frequency divider means having first and second inputs coupled respectively to the output of said reference oscillator and said local oscillator for producing signals on first and second outputs having frequencies which are a programmable fraction of the frequency of the signals applied to the inputs thereto;

phase comparator means having one input coupled with the first output of said programmable frequency divider means and having another input coupled with the second output of said programmable frequency divider means for developing a control signal and applying such control signal to said local oscillator for controlling the output frequency thereof;

counter circuit means coupled with said programmable frequency divider means for initially setting said divider means to a predetermined division ratio and operating to change the programmable fraction of division thereof in accordance with changes in the count in said counter circuit means;

control circuit means coupled with the output of said frequency discriminator means and further coupled with said counter circuit means for causing said counter circuit means to count at a first rate in a predetermined direction determined by the state of the output signal from said discriminator means in the absence of a predetermined signal output from said frequency discriminator means until a predetermined maximum count is attained, thereupon resetting said counter circuit means to a count which is a predetermined amount less than said maximum predetermined count and continuing to count at said first rate in the same predetermined direction from said new count to continuously change the programmable fraction of said frequency divider means in accordance with the state of operation of said counter circuit means, said control means operating in response to said predetermined signal output from the frequency discriminator means for terminating operation of said counter circuit means; and

further means for terminating operation of said counter circuit means at said first rate and causing operation thereof at a second slower rate.

2. The combination according to claim 1 wherein said further means includes timing means initiated into operation simultaneously with the setting of said divider means to a predetermined division ratio, and after a predetermined time interval said timing means producing an output signal applied to said counter circuit means to cause operation thereof to take place at said second slower rate. 3. The combination according to claim 1 wherein said counter circuit means includes a reversible digital counter coupled with said programmable frequency divider, means and said control circuit means causes said counter circuit means to count in said predetermined direction when the output of said frequency discriminator is of a first state and to count in the opposite direction when the output of said frequency discriminator is of second state; and said further means comprises means coupled with the output of said frequency discriminator and with said counter circuit means to take place at said second slower rate in response to a predetermined number of changes of state of frequency discriminator. 4. The combination according to claim 3 further including means responsive to the selection of a new channel in said television receiver for resetting said further means to an initial condition of operation. 5. The combination according to claim 4 wherein said further means comprises a search termination counter means operative to provide an output signal applied to said counter circuit means in response to a count thereby of a predetermined number of changes of state of said frequency discriminator to cause said counter circuit means to be operated at said second slower rate.

Both of the above mentioned patents are directed to frequency synthesizer tuning systems for use with television receivers to enable operation of the receivers with minimal viewer fine tuning adjustments. By the utilization of the frequency synthesizer tuning systems of these patents, the fine tuning adjustment which is necessary with conventional types of television receiver tuning systems has been substantially eliminated. The system employed in the '953 patent permits utilization of a frequency synthesizer tuning system which correctly tunes to a desired television station or channel even if the transmitted signals from that station are not precisely maintained at the proper frequencies. The '535 patent is directed to a signal seek tuning system adaptation of the frequency synthesizer tuning system of the '953 patent which still permits implementation of all of the desired wide-band pull in range of the frequency synthesizer system of the '953 patent.

The systems of the foregoing patents operate effectively to correct automatically for frequency offsets in a frequency synthesizer tuning system without affecting the operation of the conventional frequency synthesizer used in the system. The systems of these patents are in widespread use commercially and permit direct selection, with automatic fine tuning adjustment, of any desired VHF channel which the viewer wishes to observe. In addition, the signal seek adaptation disclosed in the '535 patent couples all of the advantages of the frequency synthesizer tuning system of the '953 patent with the desirability of providing bidirectional signal seek operation.

While the systems disclosed in the foregoing patents operate in a highly satisfactory manner to accomplish the desired results of accurate tuning without the necessity of fine tuning adjustments, the circuitry for accomplishing the desired results is somewhat complex. It is desirable to reduce the circuit complexity and the number of signal detectors for accomplishing these results without compromising the accuracy of operation of the system.

SUMMARY OF THE INVENTION

Accordingly, it is an object of this invention to provide an improved tuning system for a television receiver.

It is an additional object of this invention to provide an improved frequency synthesizer tuning system for a television receiver.

It is another object of this invention to provide an improved frequency synthesizer tuning system for a television receiver which includes a provision for adjusting the synthesizer loop for frequency offsets in the received signal with a minimum number of signal detectors.

It is still another object of this invention to provide an improved frequency synthesizer tuning system for a television receiver which operates to adjust the synthesizer loop for frequency offsets in the received signal over a relatively wide pull in range in response to the output of the receiver frequency discriminator by changing the division ratio of a programmable frequency divider in the reference oscillator leg or local oscillator leg of the synthesizer loop at a first relatively high rate from an initial nominal value to a pre-established maximum in one direction, and then resetting the division ratio to a second nominal value once the maximum is reached and continuing to incrementally change the division ratio in the same direction from the second nominal value until a properly tuned condition is indicated by the output of the receiver AFT frequency discriminator, followed by control at a lower rate of operation to maintain tuning during transmitting station drifts.

In accordance with a preferred embodiment of this invention, the frequency synthesizer tuning system for a television receiver includes a stable reference oscillator and a voltage controlled local oscillator in the tuner. A programmable frequency divider is connected between the output of the reference oscillator and one input to a phase comparator, the other input of which is supplied by the output of the local oscillator. The output of the phase comparator then comprises a control signal which is supplied to the local oscillator to control the frequency of its operation.

A counter circuit is connected to the programmable frequency divider for initially setting the divider to a predetermined division ratio upon selection of a desired channel by the viewer. The counter then operates to change the programmable fraction of the division ratio at a first relatively high rate in a direction controlled by the output from the r

eceiver picture carrier discriminator in the absence of a predetermined signal output derived from the discriminator. A control means causes the counter circuit to count in this direction until it is determined that a station is tuned or a predetermined maximum count is attained if no station is correctly tuned, thereupon resetting the counter circuit to a count which is a predetermined amount less than the maximum predetermined count. Counting is continued in the same predetermined direction from the new lesser count to continuously change the programmable fraction of the frequency divider in accordance with the state of operation of the counter. The high rate operation of the counter is terminated by the control means in response to a predetermined signal from the output of the discriminator, indicating that a station is correctly tuned, or after a fixed time-out interval; so that the system automatically adjusts for frequency offsets of the received signal which otherwise would cause the station to be mistuned if a conventional frequency synthesizer tuning system were used. After termination of the high rate operation of the counter, it is switched to a lower rate operation for maintaining tuning during transmitting station drifts.

eceiver picture carrier discriminator in the absence of a predetermined signal output derived from the discriminator. A control means causes the counter circuit to count in this direction until it is determined that a station is tuned or a predetermined maximum count is attained if no station is correctly tuned, thereupon resetting the counter circuit to a count which is a predetermined amount less than the maximum predetermined count. Counting is continued in the same predetermined direction from the new lesser count to continuously change the programmable fraction of the frequency divider in accordance with the state of operation of the counter. The high rate operation of the counter is terminated by the control means in response to a predetermined signal from the output of the discriminator, indicating that a station is correctly tuned, or after a fixed time-out interval; so that the system automatically adjusts for frequency offsets of the received signal which otherwise would cause the station to be mistuned if a conventional frequency synthesizer tuning system were used. After termination of the high rate operation of the counter, it is switched to a lower rate operation for maintaining tuning during transmitting station drifts. BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a block diagram of a television receiver employing a preferred embodiment of the invention;

FIG. 2 is a detailed block diagram of a portion of the circuit of the preferred embodiment shown in FIG. 1;

FIG. 3 is a detailed circuit diagram of a portion of a circuit shown in FIG. 1;

FIG. 4 is a flow chart of the control sequence of operation of the circuit shown in FIG. 1 and 2; and

FIG. 5 shows a waveform and time/frequency chart, respectively, useful in explaining the operation of the circuit shown in FIGS. 1, 2 and 3.

DETAILED DESCRIPTION

Referring now to the drawings, the same reference numbers are used throughout the several figures to designate the same or similar components.

FIG. 1 is a block diagram of a television receiver, which may be a black and white or color television receiver. Mo

st of the circuitry of this receiver is conventional, and for that reason it has not been shown in FIG. 1. Added to the conventional television receiver circuitry of FIG. 1, however, is a frequency synthesizer tuning system, in accordance with a preferred embodiment of the invention, which is capable of automatically changing the reference frequency when a frequency offset exists in the received signal for a particular channel.

st of the circuitry of this receiver is conventional, and for that reason it has not been shown in FIG. 1. Added to the conventional television receiver circuitry of FIG. 1, however, is a frequency synthesizer tuning system, in accordance with a preferred embodiment of the invention, which is capable of automatically changing the reference frequency when a frequency offset exists in the received signal for a particular channel. Transmitted composite television signals, either received over the air or distributed by means of a master antenna TV distribution system, are received by an antenna 10 or on antenna input terminals to the receiver. As is well known, these composite signals include picture and sound carrier components and synchronizing signal components, with the composite signal applied to an RF and tuner stage 11 of the receiver. The stage 11 includes the conventional RF amplifiers and tuner sections of the receiver, including a VHF oscillator section and a UHF oscillator section. Preferably, the UHF and VHF oscillators are voltage controlled oscillators, the freuency of operation of which are varied in response to a tuning voltage applied to them to effect the desired tuning of the receiver.

The output of the RF and tuner stages 11 is applied to the remainder of the television receiver 14, which includes the IF amplifier stages for supplying conventional picture (video) and sound IF signals to the video and sound processing stages of the receiver 14. The circuitry of the receiver 14 may be of any conventional type used to separate, amplify and otherwise process the signals for application to a cathode ray tube 16 and to a loudspeaker 17 which reproduce the picture and sound components, respectively, of the received signal.

The receiver 14 also includes a conventional AFT or automatic fine tuning discriminator circuit and additionally may includ

e a synch separator circuit for producing an output in response to the presence of vertical synchronizatin pulses, a picture carrier detection circuit, and an automatic gain control (AGC) amplifier. Outputs representative of these sensor components are shown as being coupled over a group of lead 20 to sensory circuitry 22, which in turn couples outputs representative of the operation of these various sensor circuits to a microprocessor unit 23 for controlling the operation of the microprocessor unit.

e a synch separator circuit for producing an output in response to the presence of vertical synchronizatin pulses, a picture carrier detection circuit, and an automatic gain control (AGC) amplifier. Outputs representative of these sensor components are shown as being coupled over a group of lead 20 to sensory circuitry 22, which in turn couples outputs representative of the operation of these various sensor circuits to a microprocessor unit 23 for controlling the operation of the microprocessor unit. The microprocessor unit 23 is utilized in the system of FIG. 1 for controlling the operation of a frequency synthesizer tuning system capable of automatic offset correction. When the viewer desires to select a new channel, he enters the desired channel number into a channel selection keyboard 25. There are a number of different keyboards which may be employed to accomplish this function, and the particular design is not important to this invention. The channel selector keyboard 25 also may include switches or keys for initiating a signal seek function in either the "up" or "down" direction.

Information represented by the selection of channel numbers on the keyboard 25 is supplied to the microprocessor unit 23 which provides output signals over a corresponding set of leads 27 to the tuners (local oscillators) 11 to effect the appropriate band switching control for the tuners 11 in accordance with the particular channel which has been selected. In addition, the keyboard 25, operating through the microprocessor unit 23, provides output signals which operate a channel number display 29 to provide an appropriate display of the selected channel number to the viewer.

The microprocessor unit 23 also processes the signals which are used to operate the channel number display 29 through a multiplexing circuit operation to decode the selected channel number into a parallel encoded signal. This signal is applied to corresponding inputs of the count-down counter or programmable frequency divider 31 to cause the division number of the divider 31 to relate to the divided down frequency of the tuner local oscillators connected to the input of the divider 31 through a prescaler divider circuit 32 to the frequency of the reference oscillator 34. Thus, the division number or division ratio of the local oscillator frequency obtained from the output of the programmable divider 31 is appropriately related to the frequency of the reference crystal oscillator 34.

The output of the oscillator 34 also is applied through a countdown circuit or programmable frequency divider 35. Conventional frequency synthesizer techniques are employed; and the microprocessor unit 23 automatically compensates, through appropriate code converter circuitry, for the non-uniform channel spacing of the television signals. It has been found most convenient to cause the programmable frequency divider 31 to divide by numbers corresponding directly to the oscillator frequency of the selected channel, for example, 101, 107, 113 . . . up to 931.

In accordance with the time division multiplex operation of the microprocessor 23, the count of the programmable frequency divider 35 initially is adjusted to a fixed count by the application of appropriate output signals from the microprocessor unit 23 to a point selected to be at or near the mid-point of the operating range of the programmable frequency divider 35. Thus, the output of the divider 35 is a stable reference frequency (because the input is from the reference crystal oscillator 34) which is used to establish initially and to maintain tuning of the receiver to the selected channel.

The output of the programmable divider 35 is applied to one of two inputs of a phase comparator circuit 37. The other input to the phase comparator circuit 37 is supplied from the selected one of the VHF or UHF oscillators in the tuner stages 11 through the programmable frequency divider 31. The phase comparator circuit 37 operates in a conventional manner to supply a DC tuning control signal through a phase locked loop filter circuit 39 and over a lead 40 to the oscillators in the tuner system 11 to change and maintain their operating frequency.

With the exception of the use of the microprocessor unit 23, the operation of the system which has been described thus far is that of a relatively conventional frequency synthesizer system incorporated into a television receiver. This system is similar to the system of the '953 patent. As in the system of that patent, the system shown in FIG. 1, when the transmitted station or station received on a master antenna distribution system provides the station or channel signals at the proper frequency, operates as a relatively conventional frequency synthesizer system. If, however, there is a frequency offset in the received signal to cause the carrier of the received signal to be displaced from the frequency which it should have to some other frequency, it is possible that the system would give the appearance of mistuning to the received station. The microprocessor 23, operating in conjunction with the sensory circuitry 22, is employed in conjunction with the countdown or programmable frequency divider circuit 35 to eliminate this disadvantage and still retain the advantages of frequency synthesizer tuning.

Reference now should be made to FIG. 2 which shows details of t

he interface between the keyboard 25, the microprocessor unit 23, and the circuitry used in the frequency synthesizer portions of the system. A commercially available microprocessor which has been used for the microprocessor 23, and which forms the basis for the diagramatic representation of the microprocessor in FIG. 2, is the Matsushita Electronics Corporation MN1402 four-bit single-chip microcomputer. This microcomputer has two, four-bit parallel input ports labeled "A" and "B". In addition, three output ports, a five-bit output port "C" and two four-bit output ports "D" and "E" are provided. The internal configuration of the microcomputer 23 includes an arithmetic logic unit (ALU), a read only memory (ROM) for storing instructions and constants, and a random access memory (RAM) used for data memory, arranged into four files, each file containing 16 four-bit words. These words are selected by X and Y registers and this memory is used, for example, for timers, counters, etc., and also is used to hold intermediate results. To facilitate an understanding of the operation of the system, a portion of this memory is shown in FIG. 2 as a clock 81 and a reversible counter 82 connected between the "B" input port and the "D" output port. The microcomputer 23 is programmed to permit it to operate in conjunction with the remainder of the circuits shown in FIG. 2. The programming techniques are standard, and the microcomputer 23 itself is a standard commercially available circuit component.

he interface between the keyboard 25, the microprocessor unit 23, and the circuitry used in the frequency synthesizer portions of the system. A commercially available microprocessor which has been used for the microprocessor 23, and which forms the basis for the diagramatic representation of the microprocessor in FIG. 2, is the Matsushita Electronics Corporation MN1402 four-bit single-chip microcomputer. This microcomputer has two, four-bit parallel input ports labeled "A" and "B". In addition, three output ports, a five-bit output port "C" and two four-bit output ports "D" and "E" are provided. The internal configuration of the microcomputer 23 includes an arithmetic logic unit (ALU), a read only memory (ROM) for storing instructions and constants, and a random access memory (RAM) used for data memory, arranged into four files, each file containing 16 four-bit words. These words are selected by X and Y registers and this memory is used, for example, for timers, counters, etc., and also is used to hold intermediate results. To facilitate an understanding of the operation of the system, a portion of this memory is shown in FIG. 2 as a clock 81 and a reversible counter 82 connected between the "B" input port and the "D" output port. The microcomputer 23 is programmed to permit it to operate in conjunction with the remainder of the circuits shown in FIG. 2. The programming techniques are standard, and the microcomputer 23 itself is a standard commercially available circuit component. There are several system parameters that must be selected in the operation of the system shown in FIG. 2. The selection of the nominal frequency of the two signals that feed the phase comparator circuit 37 is an example. Channel selection is provided by changing the frequency division ratio of the selector counter 31 which divides the local oscillator signal after this signal is passed through a prescaler circuit 32 and a divide-by-two divider circuit 41. The nominal frequency from the programmable frequency divider 31 (selector counter) is selected so that the local oscillator (tuner) 11 can be set exactly on frequency for all channels.

Since the frequency divider 31 is able to divide only by integer numbers, one distinct frequency possibility in the range of one KHz is obtained, another in the range of two KHz, etc. A choice must be made as to which of these values is optimum. Each value yields the nominal frequency of all of the 82 channels by simply multiplying by an appropriate integer for each channel. To simplify the phase locked loop filtering problem by the filter 39, it is desirable that the frequencies of the signals supplied to the phase comparator 37 are as high as possible. This permits rapid acquisition of a new channel along with a very clean DC control signal to adjust the local oscillator. A trade-off for this, however, must be made to permit fine tunning adjustment of the local oscillator automatically to correctly tune in stations which are off their assigned frequency, or to manually provide this feature, if desired. The two-speed operation of the system in accordance with the present invention allows a better trade-off to be made by allowing rapid acquisition and then a slower speed for precise tuning.

A compromise solution which is utilized in the circuit of FIG. 2 is to cause the frequency division chain from the local oscillator 11 in the tuner to the phase comparator 37 to be composed of the fixed divide-by-256 prescaler 32, and a fixed divide-by-4 division, which is accomplished by the divider 41 at the input of the counter 31 and a second divider 42 at the output of the counter 31. The variable frequency divider counter 31 then is loaded by means of three latch circuits 44, 45 and 46 at an appropriate time by the time division multiplex operation of the microcomputer 23 and a number that programs the programmable frequency divider counter 31 to divide by the numerical value of the frequency of the local oscillator in MHz for the channel selected. For example, if the receiver is to be tuned to channel 2, which has a nominal local oscillator frequency of 101 MHz, the programmable frequency divider 31 is set to divide by 101. If the receiver is to be tuned to channel 83, which has a nominal local oscillator frequency of 931 MHz, the programmable frequency divider 31 is set to divide by 931. In both cases, the variable divider 31 produces a 1 MHz signal. However, because of the fixed divide-by-256 and the two fixed divide-by-two dividers in series with the programmable divider 31, an output frequency of 976.5625 Hz is supplied from the output of the divider 42 to the upper input of the phase comparator 37.

Although the D output ports of the microcomputer 23 are connected in common to all of these various portions of the circuit, the selection of which of the latches are enabled to respond to the particular output signals appearing on the D output ports at any given time is effected through the C and E output ports of the microcomputer 23 in a time division multiplex fashion. A decoder circuit 52, connected to the lowermost three outputs of the E output port of the microcomputer 23, is used to apply unique decoding signals at different times in the time division multiplex sequence of operation of the microcomputer 23 to the five latch circuits 44, 45, 46, 49 and 50, respectively. At any given time in the sequence, only one of these latch circuits is enabled for operation. A latch load signal is applied from the upper output (EO3) at each cycle of operation of the signals appearing on the E output port to set the latch circuit which is enabled by the output of the decoding circuit 52 with the data appearing on the other inputs to the latch circuit. This data simultaneously appears on the four outputs of the D output port of the microcomputer 23.