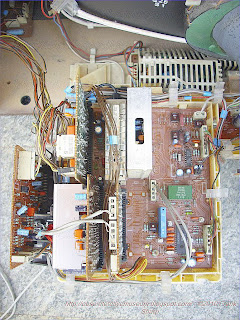

PHILIPS Chassis K40 View and tube view.

Philips in the 70 used two main boards as a chassis design.

With chassis K12 PHILIPS developed a monoprint modular chassis and even K30 and K35 chassis series were made in that way but concepts were different.

With chassis K40 in 1984 they returned to a two board chassis design but in one frame linked and with Units. Technology of these won't share things with the past exept for some little details.

This is even last PHILIPS " K " chassis series !

- Interface Unit (for SCART Socket signal interfacing )

- Sound AMPL. with TDA2040V 8222 280

3580.1

- TRD Unit (Tuning control + drive) with SAB3035 (PHILIPS)

You can see the complexity of the tellye even only from the wiring around it.

- Deflection Board on the right called large signal board. Line deflection output (BU508A) + EHT, E/W

Correction, FRAME Deflection Output with IC TDA3650 (PHILIPS)

- Signal processing board + Tuning control drive TRD (Tuning Remote Digital)

Chrominance + Luminance with TDA3561A, Synchronization With TDA3576B.

CHASSIS K40 Chrominance + Luminance with TDA3561A,

GENERAL DESCRIPTION

The TDA3561A is a decoder for the PAL colour television standard. It combines all functions required for the identification

and demodulation of PAL signals. Furthermore it contains a luminance amplifier, an RGB-matrix and amplifier. These

amplifiers supply output signals up to 5 V peak-to-peak (picture information) enabling direct drive of the discrete output

stages. The circuit also contains separate inputs for data insertion, analogue as well as digital, which can be used for

text display systems (e.g. (Teletext/broadcast antiope), channel number display, etc. Additional to the TDA3560, the

circuit includes the following features:

· The peak white limiter is only active during the time that the 9,3 V level at the output is exceeded. The start of the limiting function is delayed by one line period. This avoids peak white limiting by test patterns which have abrupt

transitions from colour to white signals.

· The brightness control is obtained by inserting a variable pulse in the luminance channel. Therefore the ratio of

brightness variation and signal amplitude at the three outputs will be identical and independent of the difference in gain

of the three channels. Thus discolouring due to adjustment of contrast and brightness is avoided.

· Improved suppression of the internal RGB signals when the device is switched to external signals, and vice versa.

· Non-synchronized external RGB signals do not disturb the black level of the internal signals.

· Improved suppression of the residual 4,4 MHz signal in the RGB output stages.

· Cascoded stages in the demodulators and burst phase detector minimize the radiation of the colour demodulator

inputs.

· High current capability of the RGB outputs and the chrominance output.

The function is described against the corresponding pin

number.

1. + 12 V power supply

The circuit gives good operation in a supply voltage range

between 8 and 13,2 V provided that the supply voltage for

the controls is equal to the supply voltage for the

TDA3561A. All signal and control levels have a linear

dependency on the supply voltage. The current taken by

the device at 12 V is typically 85 mA. It is linearly

dependent on the supply voltage.

2. Control voltage for identification

correct operation. The voltages available under various

signal conditions are given in the specification.

3. Chrominance input

The chroma signal must be a.c.-coupled to the input.

Its amplitude must be between 55 mV and 1100 mV

peak-to-peak (25 mV to 500 mV peak-to-peak burst

signal). All figures for the chroma signals are based on a

colour bar signal with 75% saturation, that is the

burst-to-chroma ratio of the input signal is 1 : 2,25.

4. Reference voltage A.C.C. detector

This pin must be decoupled by a capacitor of about 330

nF. The voltage at this pin is 4,9 V.

5. Control voltage A.C.C.

The A.C.C. is obtained by synchronous detection of the

burst signal followed by a peak detector. A good noise

immunity is obtained in this way and an increase of the

colour for weak input signals is prevented. The

recommended capacitor value at this pin is 2,2 mF.

6. Saturation control

The saturation control range is in excess of 50 dB.

The control voltage range is 2 to 4 V. Saturation control is

a linear function of the control voltage.

When the colour killer is active, the saturation control

voltage is reduced to a low level if the resistance of the

external saturation control network is sufficiently high.

Then the chroma amplifier supplies no signal to the

demodulator. Colour switch-on can be delayed by proper

choice of the time constant for the saturation control

setting circuit.

When the saturation control pin is connected to the power

supply the colour killer circuit is overruled so that the colour

signal is visible on the screen. In this way it is possible to

adjust the oscillator frequency without using a frequency

counter (see also pins 25 and 26).

7. Contrast control

The contrast control range is 20 dB for a control voltage

change from + 2 to + 4 V. Contrast control is a linear

function of the control voltage. The output signal is

suppressed when the control voltage is 1 V or less. If one

or more output signals surpasses the level of 9 V the peak

white limiter circuit becomes active and reduces the output

signals via the contrast control by discharging C2 via an

internal current sink.

8. Sandcastle and field blanking input

The output signals are blanked if the amplitude of the input

pulse is between 2 and 6,5 V. The burst gate and clamping

circuits are activated if the input pulse exceeds a level of

7,5 V.

The higher part of the sandcastle pulse should start just

after the sync pulse to prevent clamping of video signal on

the sync pulse. The width should be about 4 ms for proper

A.C.C. operation.

9. Video-data switching

an input pulse between 1 V and 2 V. In that condition, the

internal RGB signals are switched off and the inserted

signals are supplied to the output amplifiers. If only normal

operation is wanted this pin should be connected to the

negative supply. The switching times are very short

(< 20 ns) to avoid coloured edges of the inserted signals

on the screen.

10. Luminance signal input

The input signal should have a peak-to-peak amplitude of

0,45 V (peak white to sync) to obtain a black-white output

signal to 5 V at nominal contrast. It must be a.c.-coupled to

the input by a capacitor of about 22 nF. The signal is

clamped at the input to an internal reference voltage.

A 1 kW luminance delay line can be applied because the

luminance input impedance is made very high.

Consequently the charging and discharging currents of the

coupling capacitor are very small and do not influence the

signal level at the input noticeably. Additionally the

coupling capacitor value may be small.

11. Brightness control

The black level of the RGB outputs can be set by the

voltage on this pin (see Fig.5). The black level can be set

higher than 4 V however the available output signal

amplitude is reduced (see pin 7). Brightness control also

operates on the black level of the inserted signals.

12, 14, 16. RGB outputs

The output circuits for red, green and blue are identical.

Output signals are 5,25 V (R, G and B) at nominal input

signals and control settings. The black levels of the three

outputs have the same value. The blanking level at the

outputs is 2,1 V. The peak white level is limited to 9,3 V.

When this level exceeded the output signal amplitude is

reduced via the contrast control (see pin 7).

13, 15, 17. Inputs for external RGB signals

The external signals must be a.c.-coupled to the inputs via

a coupling capacitor of about 100 nF. Source impedance

should not exceed 150 W. The input signal required for

a 5 V peak-to-peak output signal is 1 V peak-to-peak.

At the RGB outputs the black level of the inserted signal is

identical to that of normal RGB signals. When these inputs

are not used the coupling capacitors have to be connected

to the negative supply.

18, 19, 20. Black level clamp capacitors

The black level clamp capacitors for the three channels are

connected to these pins. The value of each capacitor

should be about 100 nF.

21, 22. Inputs (B-Y) and (R-Y) demodulators

The input signal is automatically fixed to the required level

by means of the burst phase detector and A.C.C.

generator which are connected to pin 21 and pin 22. As the

burst (applied differentially to those pins) is kept constant

by the A.C.C., the colour difference signals automatically

have the correct value.

23, 24. Burst phase detect

or outputs

At these pins the output of the burst phase detector is

filtered and controls the reference oscillator. An adequate

catching range is obtained with the time constants given in

the application circuit (see Fig.6).

25, 26. Reference oscillator

The frequency of the oscillator is adjusted by the variable

capacitor C1. For frequency adjustment interconnect pin

21 and pin 22. The frequency can be measured by

connecting a suitable frequency counter to pin 25.

28. Output of the chroma amplifier

Both burst and chroma signals are available at the output.

The burst-to-chroma ratio at the output is identical to that

at the input for nominal control settings. The burst signal is

not affected by the controls. The amplitude of the input

signal to the demodulator is kept constant by the A.C.C.

Therefore the output signal at pin 28 will depend on the

signal loss in the delay line.

Synchronization With TDA3576B.12V 70mA sync combination with transmitter identification and vertical 625 divider system

- Power supply on the bottom of the cabinet (SOPS Supply).

PHILIPS TDA3576B SYNC COMBINATION WITH TRANSMITTER IDENTIFICATION

AND VERTICAL 625 DIVIDER SYSTEM.

GENERAL DESCRIPTION

The TDA3576B is a monolithic integrated circuit for use in colour television receivers. The circuit is

optimized for a horizontal and vertical frequency ratio of 625.

Features

• Horizontal sync separator (including noise inverter) with sliding bias such that the sync pulse is

always sliced between top sync level and blanking level

• Phase detector which compares the horizontal sync pulse with the oscillator voltage; this phase

detector is gated

• Phase detector which compares the horizontal flyback pulse with the oscillator voltage

• Horizontal oscillator (31,25 kHz)

• Time constant switching of the first control loop (short time constant during catching and reception

of VCR signals)

• Burst key pulse generator (sandcastle pulse with three levels)

• Very stable automatic vertical synchronization due to the 625 divider system, without delay after

channel change

• Vertical sync pulse separator

• Three voltage level sensor on coincidence detector circuit output

• Video transmitter identification circuit for sound muting and search tuning systems

• Inhibit of vertical sync pulse when no video transmitter is detected.

FUNCTIONAL DESCRIPTION

The video input voltage to drive the sync separator must have negative-going sync, which can be

obtained from synchronous demodulators such as TDA2540 and TDA2541.

The slicing level of the sync separator is determined by the value of the resistor between pins 6 and 7. A

4, 7 kr2 resistor provides a slicing level midway between the top sync level and the blanking level. Thus

the slicing level is independent of the amplitude of the sync pulse input at pin 5.

The nominal top sync level at pin 5 is 3 V, and the amplitude selective noise inverter is activated at

0,7 V.

To

obtain good stability the circuit contains three control loops. In the

first loop the phase of the horizontal sync pulse is compared with a

reference output pulse from the horizontal oscillator. In the second

loop the phase of the flyback pulse is compared with the same reference

output pulse. The first loop is designed for good noise immunity and the

second loop has a fast time constant to compensate quickly for storage

variations of the output stage. The second loop also generates a gating

signal of about 5,5 μs for use in the transmitter identification

circuit. The third control loop generates a second gating signal which

is used in the first phase detector. The pulse width is typically 14 μs.

For a short catching time the output current of the first phase

detector is not gated but is increased by 5 times during catching. This

is caused by the voltage of the coincidence detector at pin 9. For VCR

playback conditions the first control loop must be forced to a fast time

constant, this is achieved by applying an external voltage of~ 2,7 V to

pin 9.

The free running output frequency of the horizontal

oscillator is 31,25 kHz. The vertical frequency output is obtained by

dividing this double horizontal frequency by 625. The double horizontal

fre- quency is fed via a binary divider to provide the normal 15,625 kHz

horizontal output to pin 11. The sandcastle pulse is generated at pin 2

and has three levels. The burst key pulse is of short duration,

typically 4 μs, with an amplitude of 10 Vandis the highest level. The

second level has a pulse duration equal to the horizontal flyback pulse

with an amplitude of 4,5 Vandis used for horizontal blanking. The third

level, amplitude 2,5 V, is used for vertical blanking and has a pulse

duration of 1,34 ms. The last pulse is internal Iv generated by the

divider circuit and is only available when a standard video input signal

is received. An external vertical blanking pulse can be added to this

pin via a suitable series resistor. This pulse will be automatically

clamped to 2,5 V.

The automatic vertical sync block contains the following:

• 625 divider

• In/out-sync detector

• Direct/indirect sync switch

• Identification circuit

It

is fed by a signal obtained by integration of the composite video

signal and an internally generated, clipped video signal. The vertical

sync pulse is sliced out of this integrated signal by an automatically

biased clipper. The video part of the signal helps to build up a

vertical sync when heavy negative-going reflections (mountains) distort

the video signal. The in/out sync-detector considers a signal

out-of-sync when fourteen or more successive incoming vertical sync

pulses are not in phase with a reference signal from the 625 divider.

Therefore a distorted vertical sync signal needs only one

out-of-fourteen pulses to be in phase to keep the system in sync. When

the fifteenth successive out-of-sync pulse is detected, the

direct/indirect sync switch is activated to feed the vertical sync

signal directly out of the block at pin 3 (direct sync vertical output).

At the same time the 625 divider is reset by one of the sync pulses.

After the reset pulse, if the 7th sliced vertical sync pulse coincides

with a 625 divider window, the sync output pulse is presenteu again by

the divider system and switch-over to indirect mode occurs. In the

direct mode, every 7th non-coinciding sliced vertical sync pulse will

reset the counter. A non- standard video signal will result in

continuous reset pulses and the direct/indirect switch will remain in

the direct position.

To avoid delay in vertical synchronization, caused by waiting time of the divider circuit after channel

change or an unsynchronized camera change in the studio, information is fed from the horizontal

coincidence detector to the automatic switch for the vertical sync pulse. The loss of horizontal

synchronization sets the automatic switch to direct vertical sync.

When an external voltage between 2,7 V and 8,2 V is applied via pin 9 to the coincidence detector, the

horizontal phase detector is switched to a short time constant and the automatic switch to direct

vertical sync. A voltage level on pin 9 between 9,2 V and 12 V switches the horizontal phase detector

to a short time constant, without affecting the indirect/direct vertical sync system which remains

operational. Thus when standard signals are received vertical sync pulses are generated by the divider

system.

To avoid disturbance of the horizontal phase detector by the vertical sync pulse the 625 divider system

generates an anti-top-flutter pulse. This pulse is applied to the phase 1 detector when a standard video

signal is received. The anti-top-flutter pulse is also active for standard VCR signal conditions, voltage at

pin 9;;. 9,2 V.

The video transmitter identification circuit detects when a sync pulse occurs during the internal 5,5 μs

gating pulse. This indicates the presence of a video transmitter and results in the capacitor connected

to pin 1 being charged to 8,4 V. When no sync pulse is present the capacitor discharges to< 1 V. The

voltage at pin 1 is compared with an internal d.c. voltage. The identification output at pin 18 is active

when pin 1 is.;; 1,5 V (no video transmitter) and inactive (high impedance) when pin 1 is> 3,5 V,

this information can be used for search tuning.

The vertical sync output pulse at pin 3 is inhibited when no video transmitter is identified, which

prevents interference or noise affecting the frequency of the vertical output stage. This results in a

vertical stable picture, plus vertical stable position information for tuning systems.

RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

Supply voltage (pin 17) Vp = V17-10 max. 13,2 v

Total power dissipation max. 1200 mW

Storage temperature range -55 to + 125 oc

Operating ambient temperature range -25 to +65 oc

THERMAL RESISTANCE From junction to ambient (in free air) Rthj-a 50 K/W

The function is described against the corresponding pin number.

1. Video transmitter identification

A 47 nF capacitor must be connected to this pin. It charges to a level of 8 V when a sync pulse is

detected, and discharges to a level of< 1 V when no sync pulse is detected.

2. Sandcastle output pulse

This output has three levels. The first and highest level (10 V) is the burst key pulse with a typical

duration of 4,0 μs. The second level, for the horizontal blanking, is typically 4,5 V with a pulse duration

equal to the horizontal flyback pulse. For the third level an external vertical flyback pulse must be

applied to this pin. This pulse will be clamped to 2,5 V by an internal clamping circuit. The input

current is typically 2 mA.

3. Vertical output pulse

This pulse is obtained from the 625 divider circuit when standard input signals are received or from the

sync separator when the signals are non-standard. The pulse is inhibited when no video transmitter is

detected. Both pulses have good stability and accuracy and are used to trigger the vertical oscillator.

4. Vertical sync pulse integrator biasing network

The vertical sync pulse is obtained by integrating the composite sync signal in an internal RC-network. An

external capacitor of 10 μF is required for biasing the vertical sync separator, this provides the vertical

sync output pulse with a delay of 37 μs. This value can be changed by an external resistor. A resistor of

470 kn between pin 3 and +12 V gives a delay of 45 μs.

5. Video input

The video input signal must have negative-going sync pulses. The top-sync level can vary between 1 V

and 3,5 V without affecting the sync separator operation. The slicing level is fixed at 50% for the

sync pulse amplitude range 0,1 to 1 V which provides good sync separation down to pulses with an

amplitude of 100 mV peak-to-peak. The slicing level is increased for sync pulses in excess of 1 V

peak-to-peak. The noise gate is activated at an input level< 1 V, thus when noise gating is required the

top sync level should be close to the minimum level of 1 V.

6. Sync separator slicing level output

The sync separator slicing level is determined on this pin. A slicing level of 50% is obtained by

comparing this level with the black level of the video signal, which is detected at pin 7.

7. Black level detector output

The black level of the input signal is detected on this pin. This is required to obtain good sync

separator operation. A 22 μF capacitor in series with a resistor of 82 n must be connected to this pin.

A 4,7 kU resistor connected between pins 6 and 7 results in a slicing level of 50%.

8. Horizontal phase detector output and control oscillator input

The flywheel filter must be connected to this pin. Typical values for the components are a capacitor of

100 nF in parallel with an RC-network of 1 kr2 and 10 μF. Furthermore, a resistor of 270 kH should

be connected between pins 8 and 13 to limit the free running frequency drift.

The output current of the phase detector depends on the condition of the coincidence detector. The

output current is high when the oscillator is out-of-sync. The result is a large catching range, and the

phase detector not gated. The output current is low when the oscillator is synchronized and the phase

detector is gated; this provides good noise immunity.

9. Coincidence detector output

A 1 μF capacitor must be connected to this pin. The output voltage depends on the oscillator condition

(synchronized or not) and on the video input signal. The following output voltages can occur:

• when in-sync

1,3 V

• when out-of-sync

2,7 V

• during noise at the input

2, 1 V

There are two switching levels at pin 9. At the first switching level when the output voltage is< 2, 1 V,

the phase detector output is low and the gating of the phase detector is switched on. When the output

voltage is> 2,7 V, the output current of the phase detector is high and the gating of the phase detector

is switched off. The result is a large catching range and a high dynamic steepness of the PLL. At the

second switching level when the output voltage is> 9,2 V the sync system is switched to a short time

constant while the indirect/direct vertical sync system remains fully operational. This condition is

suitable for VCR application.

10. Negative supply (ground)

11. Horizontal sync pulse output

This is an open collector output. The collector resistor mus be chosen such that sufficient current is

supplied

to the driver stage. The maximum current is 60 mA. The circuit is

designed such that the horizontal output transistor cannot be switched

on during flyback, but is switched on directly after flyback.

12. Control voltage second loop

This voltage controls the output pulse at pin 11 (positive-going edge). The capacitor connected to this

pin must have a minimum value of 6,8 nF. A higher value decreases the dynamic-loop gain in the second

control loop. When a high dynamic-loop gain is not required a capacitor value of 100 nF is recommended.

Horizontal shift is possible by applying an external current to pin 12.

13. Reference voltage control loops

The reference voltage must be decoupled by a capacitor of 10 μF.

14. Decoupling internal power supply

The IC has two power terminals. The main terminal (pin 17) supplies the output stages, the sync

separator and the divider circuit. The specially decoupled terminal (pin 14) supplies the horizontal

oscillator. The decoupling capacitor should be 22 μF.

15. Flyback input pulse

This pulse is required for the second phase control loop and for generating the horizontal blanking

pulse in the sandcastle output. The input current must be at least 0,2 mA and not exceed 3 mA.

16. RC-network horizontal oscillator

Stable components should be chosen for good frequency stability. For adjusting the frequency a part of

the total resistance must be variable. This part must be as small as possible, because of poor stability of

variable carbon resistors. The oscillator can be adjusted when pins 8 and 13 are short circuited (see Fig. 3).

17. Positive supply

The supply voltage may vary between 10,5 and 13,2 V. The current-draw is typ. 70 mA and the range is

50 to 85 mA.

·

18. Video transmitter identification output

This is an emitter-follower output which will be inactive (high-impedance) when the level at pin 1 is

> 4 V (video transmitter detected). The output will be active high when the level at pin 1 is< 1,7 V

(no videotransmitterdetected).This feature can be used for search-tuning and sound-muting.

PHILIPS CHASSIS K40 was using in this chassis the RC-5 infrared remote protocol widely used in after developed products for over 25 Years.

The RC-5 infrared remote protocol was developed by Philips in the late 1980s as a semi-proprietary consumer IR (infrared) remote control communication protocol for consumer electronics. However, it was also adopted by most European manufacturers, as well as many US manufacturers of specialty audio and video equipment.

The RC-5 infrared remote protocol was developed by Philips in the late 1980s as a semi-proprietary consumer IR (infrared) remote control communication protocol for consumer electronics. However, it was also adopted by most European manufacturers, as well as many US manufacturers of specialty audio and video equipment.The advantage of the RC-5 protocol is that (when properly followed) any CD handset (for example) may be used to control any brand of CD player using the RC-5 protocol.

Protocol Details

The basics of the protocol are well known. The handset contains a keypad and a transmitter integrated circuit (IC) driving an IR LED. The command data is a bi-phase encoded bitstream modulating a 36 kHz carrier. (Often the carrier used is 38 kHz or 40 kHz, apparently due to misinformation about the actual protocol.) The IR signal from the transmitter is detected by a specialized IC with an integral photo-diode, and is amplified, filtered, and demodulated so that the receiving device can act upon the received command. RC-5 only provides a one-way link, with information traveling from the handset to the receiving unit.The command comprises 14 bits:

- A start bit, which is always logic 1 and allows the receiving IC to set the proper gain.

- A field bit, which denotes whether the command sent is in the lower field (logic 1 = 0 to 63 decimal) or the upper field (logic 0 = 64 to 127 decimal). The field bit was added later by Philips when it was realized that 64 commands per device were insufficient. Previously, the field bit was combined with the start bit. Many devices still use this original system.

- A control bit, which toggles with each button press. This allows the receiving device to distinguish between two successive button presses (such as "1", "1" for "11") as opposed to the user simply holding down the button and the repeating commands being interrupted by a person walking by, for example.

- A five-bit system address, that selects one of 32 possible systems.

- A six-bit command, that (in conjunction with the field bit) represents one of the 128 possible RC-5 commands.

PHILIPS RC-5 System and Command Codes:

While the protocol is well known and understood, what is not so well documented are the system number allocations and the actual RC-5 commands used for each system. The information provided below is the most complete and accurate information available at this time. It is from a printed document from Philips dated December 1992 that is unfortunately not available in electronic format (e.g., PDF), nor is an updated version available. This information is provided so that companies that wish to use the RC-5 protocol can use it properly, and avoid conflicts with other equipment that may or may not be using the correct system numbers and commands.This code has an instruction set of 2048 different instructions and is divided into 32 address

of each 64 instructions. Every kind of equipment use his own address,

so this makes it possible to change the volume of the TV without change the volume of the hifi.

The transmitted code is a dataword wich consists of 14 bits and is defined as:

2 startbits for the automatic gain control in the infrared receiver.

1 toggle bit (change everytime when a new button is pressed on the ir transmitter)

5 address bits for the systemaddress

6 instructionbits for the pressed key.

The Philips RC5 IR transmission protocol uses Manchester encoding of the message bits. Each pulse burst (mark – RC transmitter ON) is 889us in length, at a carrier frequency of 36kHz (27.7us). Logical bits are transmitted as follows:

- Logical '0' – an 889us pulse burst followed by an 889us space, with a total transmit time of 1.778ms

- Logical '1' – an 889us space followed by an 889us pulse burst, with a total transmit time of 1.778ms

When a key is pressed on the remote controller, the message frame transmitted consists of the following 14 bits, in order:

- two Start bits (S1 and S2), both logical '1'.

- a Toggle bit (T). This bit is inverted each time a key is released and pressed again.

- the 5-bit address for the receiving device

- the 6-bit command.

The address and command bits are each sent most significant bit first. Figure 1 illustrates the format of a Philips RC5 IR transmission frame, for an address of 05h (00101b) and a command of 35h (110101b).

The address and command bits are each sent most significant bit first. Figure 1 illustrates the format of a Philips RC5 IR transmission frame, for an address of 05h (00101b) and a command of 35h (110101b).Figure 1. Example message frame using the Philips RC5 IR transmission protocol.

From Figure 1 we can see that it takes:

- 5.334ms to transmit the Start and Toggle bits (S1, S2 and T). Notice that, as the first half-bit of S1 is a space, the receiver will only notice the real start of the message frame after 889us.

- 8.89ms to transmit the 5 bits for the address

- 10.668ms to transmit the 6 bits for the command

- 24.892ms to fully transmit the actual message frame.

SAB3035 COMPUTER INTERFACE FOR TUNING AND CONTROL (CITAC)

GENERAL DESCRIPTION

The SAB3035 provi

des closed-loop digital tuning of TV receivers, with or without a.f.c., as required. lt

des closed-loop digital tuning of TV receivers, with or without a.f.c., as required. ltalso controls up to 8 analogue functions, 4 general purpose I/O ports and 4 high-current outputs for

tuner band selection.

The IC is used in conjunction with a microcomputer from the MAB8400 family and is controlled via a two-wire, bidirectional I2 C bus.

Featu res

Combined analogue and digital circuitry minimizes the number of additional interfacing components

required

Frequency measurement with resolution of 50 KHz

Selectable prescaler divisor of 64 or 256

32 V tuning voltage amplifier

4 high-current outputs for direct band selection

8 static digital to analogue converters (DACSI for control of analogue functions

Four general purpose input/output (l/O) ports

Tuning with control of speed and direction

Tuning with or without a.f.c.

Single-pin, 4 MHZ on-chip oscillator

I2 C bus slave transceiver

FUNCTIONAL DESCRIPTION

The SAB3035 is a monolithic computer interface which provides tuning and control functions and

operates in conjunction with a microcomputer via an I2 C bus.

Tuning

This is performed using frequency-locked loop digital control. Data corresponding to the required tuner

frequency is stored in a 15-bit frequency buffer. The actual tuner frequency, divided by a factor of 256

(or by 64) by a prescaler, is applied via a gate to a 15-bit frequency counter. This input (FDIV) is

measured over a period controlled by a time reference counter and is compared with the contents of the frequency buffer. The result of the comparison is used to control the tuning voltage so that the tuner frequency equals the contents of the frequency buffer multiplied by 50 kHz within a programmable tuning window (TUW).

The system cycles over a period of 6,4 ms (or 2,56 ms), controlled by the time reference counter which is clocked by an on-chip 4 lVlHz reference oscillator. Regulation of the tuning voltage is performed by a charge pump frequency-locked loop system. The charge IT flowing into the tuning voltage amplifier is controlled by the tuning counter, 3-bit DAC and the charge pump circuit. The charge IT is linear with the frequency deviation Af in steps of 50 .

TDA2541 IF AMPLIFIER WITH DEMODULATOR AND AFC

DESCRIPTION

The TDA2540 and 2541 are IF amplifier and A.M.

demodulator circuits for colour and black and white

television receivers using PNP or NPN tuners. They

are intended for reception of negative or positive

modulation CCIR standard.

They incorporate the following functions : .Gain controlled amplifier .Synchronous demodulator .White spot inverter .Video preamplifier with noise protection .Switchable AFC .AGC with noise gating .Tuner AGC output (NPN tuner for 2540)-(PNP

tuner for 2541) .VCR switch for video output inhibition (VCR

play back).

PHILIPS 26CS5280 /01Z TXT VERONESE CHASSIS K40 Television receiver including a teletext Videotext decoder circuit :

In a teletext decoder circuit the character generator supplies picture elements at a rate of nominally approximately 6 MHz under the control of display pulses occurring at the same rate. These display pulses are derived from reference clock pulses which occur at a rate which is not a rational multiple of 6 MHz. The character generator comprises a generator circuit which receives the reference clock pulses and selects, from each series of N reference clock pulses, as many pulses as correspond to the number of horizontal picture elements constituting a character, while the time interval of N reference clock pulses corresponds to the desired width of the characters to be displayed. The character generator supplies picture elements of distinct length, while the length of a picture element is dependent on the ordinal number of this picture element in the character.

1. A receiver for television signal s including a teletext decoder circuit for decoding teletext signals constituted by character codes which are transmitted in the television signal, and comprising:

a video input circuit receiving the television signal and converting it into a serial data flow;

an acquisition circuit for receiving the serial data flow supplied by the video input circuit and selecting that part therefrom which corresponds to the teletext page described by the viewer;

a character generator comprising:

a memory medium addressed by the character codes which together represent the teletext page desired by the user and which in response to each character code successively supply m2 series of m1 simultaneously occurring character picture element codes each indicating wether a corresponding picture element of the character must be displayed in the foreground colour or in the background colour;

a generator circuit receiving a series of reference clock pulses and deriving display clock pulses therefrom;

a converter circuit receiving each series of m1 simultaneously occurring character picture element codes as well as the display clock pulses for supplying the m1 character picture element codes of a series one after the other and at the display clock pulse rate;

a display control circuit receiving the serial character picture element codes and converting each into an R, a G and a B signal for the relevant picture element of the character to be displayed;

characterized in that

the generator circuit is adapted to partition the series of reference clock pulses applied thereto into groups of N reference clock pulses each, in which N reference clock pulse periods correspond to the desired width of a character to be displayed, and to select from each such group m1 clock pulse to function as display clock pulses;

the converter circuit is adapted to supply each character picture element code during a period which is dependent on the ordinal number of the character picture element code in the series of m1 character picture element codes.

2. A character generator for use in a receiver teletext claim 1, comprising:

a memory medium which is addressable by character codes and successively applies m2 series of m1 simultaneously occurring character picture element codes in response to a character code applied as an address thereto, each character picture element code indicating whether a corresponding picture element of the character must be displayed in the foreground colour or in the background colour;

a generator circuit receiving a series of reference clock pulses and deriving display clock pulses therefrom;

a display control circuit receiving the serial character picture element codes and converting each into an R, a G and a B signal for the relevant picture element of the character to be displayed; characterized in that

the generator circuit is adapted to partition the series of reference clock pulses applied thereto into groups of N reference clock pulses each, in which N reference clock pulse periods correspond to the desired width of a character to be displayed, and to select from each such group m1 clock pulses to function as display clock pulses;

the converter circuit is adapted to supply each character picture element code during a period which is dependent on the ordinal number of the character picture element code in the series of m1 character picture element codes.

BACKGROUND OF THE INVENTION

BACKGROUND OF THE INVENTION 1. Field of the Invention

The invention generally relates to receivers for television signals and more particularly to receivers including teletext decoders for use in a teletext transmission system.

2. Description of the Prior Art

As is generally known, in a teletext transmission system, a number of pages is transmitted from a transmitter to the receiver in a predetermined cyclic sequence. Such a page comprises a plurality of lines and each line comprises a plurality of alphanumerical characters. A character code is assigned to each of these characters and all character codes are transmitted in those (or a number of those) television lines which are not used for the transmission of video signals. These television lines are usually referred to as data lines.

Nowadays the teletext transmission system is based on the standard known as "World System Teletext", abbreviates WST. According to this standard each page has 24 lines and each line comprises 40 characters. Furthermore each data line comprises, inter alia, a line number (in a binary form) and the 40 character codes of the 40 characters of that line.

A receiver which is suitable for use in such a teletext transmission system includes a teletext decoder enabling a user to select a predetermined page for display on a screen. As is indicated in, for example, Reference 1, a teletext decoder comprises, inter alia, a video input circuit (VIP) which receives the received television signal and converts it into a serial data flow. This flow is subsequently applied to an acquisition circuit which selects those data which are required for building up the page desired by the user. The 40 character codes of each teletext line are stored in a page memory which at a given moment thus comprises all character codes of the desired page. These character codes are subsequently applied one after the other and line by line to a character generator which supplies such output signals that the said characters become visible when signals are applied to a display.

The central part of the character generator is constituted by a memory which is sub-divided into a number of submemories, for example, one for each character. Each sub-memory then comprises m 1 ×m 2 memory locations each corresponding to a picture element and the contents of each memory location define whether the relevant picture element must be displayed in the so-called foreground colour or in the so-called background colour. The contents of such a code memory location will be referred to as character picture element code. This memory is each time addressed by a character code and a row code. The character code selects the sub-memory and the row code selects the row of m 1 memory elements whose contents are desired. The memory thus supplies groups of m simultaneously occurring character picture element codes which are applied to a converter circuit. This converter circuit usually includes a buffer circuit for temporarily storing the m 1 substantially presented character picture element codes. It is controlled by display clock pulses occurring at a given rate and being supplied by a generator circuit. It also supplies the m 1 character picture element codes, which are stored in the buffer circuit, one after the other and at a rate of the display clock pulses. The serial character picture element codes thus obtained are applied to a display control circuit converting each character picture element code into an R, a G and a B signal value for the relevant picture element, which signal values are applied to the display device (for example, display tube).

OBJECT AND SUMMARY OF THE INVENTION

A particular object of the invention is to provide a teletext decoder circuit which does not include a separate 6 MHz oscillator but in which for other reasons clock pulses, which are already present in the television receiver, can be used as reference clock pulses, which reference clock pulses generally do not occur at a rate which is a rational multiple of the rate at which the display clock pulses must occur.

According to the invention,

the generator circuit is adapted to partition the series of reference clock pulses applied thereto into groups of N reference clock pulses each, in which N clock pulse periods correspond to the desired width of a character to be displayed, and to select of each such group m 1 clockpulses to function as display clock pulses;

the converter circuit is adapted to supply each character picture element code during a period which is dependent on the ordinal number of the character picture element code in the series of m 1 character picture element codes.

The invention has resulted from research into teletext decoder circuits for use in the field of digital video signal processing in which a 13.5 MHz clock generator is provided for sampling the video signal. The 13.5 MHz clock pulses supplied by this clock generator are now used as reference clock pulses. The generator circuit partitions these reference clock pulses into groups of N clock pulses periods each. The width of such a group is equal to the desired character width. Since a character comprises rows of m 1 picture elements, m 1 reference clock pulses are selected from such a group which clock pulses are distributed over this group as regularly as possible. Since the mutual distance between the display clock pulses thus obtained is not constantly the same, further measures will have to be taken to prevent undesired gaps from occurring between successive picture elements when a character is displayed. Since the length of a picture element is determined by the period during which the converter circuit supplies a given character picture element code, this period has been rendered dependent on the ordinal number of the character picture element code in the series of m 1 character picture element codes.

REFERENCES

1. Computer-controlled teletext, J. R. Kinghorn; Electronic Components and Applications, Vol. 6, No. 1, 1984, pages 15-29.

2. Video and associated systems, Bipolar, MOS; Types MAB 8031 AH to TDA 1521: Philips' Data Handbook, Integrated circuits, Book ICO2a 1986, pages 374,375.

3. Bipolar IC's for video equipment; Philips' Data Handbook, Integrated Circuits Part 2, January 1983.

4. IC' for digital systems in radio, audio and video equipment, Philips' Data Handbook, Integrated Circuits Part 3, September 1982.

BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 shows the general structure of a television receiver including a teletext decoder circuit;

FIG. 2 shows different matrices of picture elements constituting a character;

FIG. 3 shows diagrammatically the general structure of a character generator;

FIG. 4 shows an embodiment of a converter circuit and a generator circuit for use in the character generator shown in FIG. 3, and

FIG. 5 shows some time diagrams to explain its operation;

FIG. 6 shows another embodiment of a converter circuit and a generator circuit for use in the character generator shown in FIG. 3, and

FIG. 7 shows some time diagrams to explain its operation;

FIG. 8 shows a modification of the converter circuit shown in FIG. 6, adapted to round the characters.

EXPLANATION OF THE INVENTION

General structure of a TV receiver

FIG. 1 shows diagra

mmatically the general structure of a colour television receiver. It has an antenna input 1 connected to an antenna 2 receiving a television signal modulated on a high-frequency carrier, which signal is processed in a plurality of processing circuits. More particularly, it is applied to a tuning circuit 23 (tuner or channel selector). This circuit receives a band selection voltage V B in order to enable the receiver to be tuned to a frequency within one of the frequency bands VHF1, VHF2, UHF, etc. The tuning circuit also receives a tuning voltage V T with which the receiver is tuned to the desired frequency within the selected frequency band.

mmatically the general structure of a colour television receiver. It has an antenna input 1 connected to an antenna 2 receiving a television signal modulated on a high-frequency carrier, which signal is processed in a plurality of processing circuits. More particularly, it is applied to a tuning circuit 23 (tuner or channel selector). This circuit receives a band selection voltage V B in order to enable the receiver to be tuned to a frequency within one of the frequency bands VHF1, VHF2, UHF, etc. The tuning circuit also receives a tuning voltage V T with which the receiver is tuned to the desired frequency within the selected frequency band. This tuning circuit 3 supplies an oscillator signal having a frequency of f OSC on the one hand and an intermediate frequency video signal IF on the other hand. The latter signal is applied to an intermediate frequency amplification and demodulation circuit 4 supplying a baseband composite video signal CVBS. The Philips IC TDA 2540 described in Reference 3 can be used for this circuit 4.

The signal CVBS thus obtained is also applied to a colour decoder circuit 5. this circuit supplies the three primary colour signals R', G' and B' which in their turn are applied via an amplifier circuit 6 to a display device 7 in the form of a display tube for the display of broadcasts on a display screen 8. In the colour decoder circuit 5 colour saturation, contrast and brightness are influenced by means of control signals ANL. The circuit also receives an additional set of primary colour signals R, G and B and a switching signal BLK (blanking) with which the primary colour signals R', G' and B' can be replaced by the signals R, G and B of the additional set of primary colour signals. A Philips IC of the TDA 356X family described in Reference 3 can be used for this circuit 5.

The Philips IC SAA 5030 may be used as video input circuits 91, the Philips IC SAA 5040 may be used as teletext acquisition and control circuit, a 1K8 RAM may be used as page memory, a modified version of the Philips IC SAA 5050 may be used as character generator 94 and a modified version of the Philips IC SAA 5020 may be used as control circuit 95, the obvious modification being a result of the fact that this IC is originally intended to receive reference clock pulses at a rate of 6 MHz for which 13.5 MHz has now been taken.

It receives an oscillator signal at the frequency f' OSC which is derived by means of a frequency divider 15, a dividing factor of which is 256, from the oscillator signal at the frequency f OSC which is supplied by the tuning circuit 3. Tuning circuit 3, frequency divider 15 and interface circuit 13 combined constitute a frequency synthesis circuit. The Philips IC SAB 3035 known under the name of CITAC (Computer Interface for Tuning and Analog Control) and described in Reference 4 can be used as interface circuit 13. A specimen from the MAB 84XX family, manufactured by Philips, can be used as a microcomputer.

For operating this television receiver an operating system is provided in the form of a remote control system comprising a hand-held apparatus 16 and a local receiver 17. This receiver 17 has an output which is connected to an input (usually the "interrupt" input) of the microcomputer 12. It may be constituted by the Philips IC TDB 2033 described in Reference 4 and is then intended for receiving infrared signals which are transmitted by the hand-held apparatus 16.

The hand-held apparatus 16 comprises an operating panel 161 with a plurality of figure keys denoted by the FIGS. 0 to 9 inclusive, a colour saturation key SAT, a brightness key BRI, a volume key VOL, and a teletext key TXT. These keys are coupled to a transmitter circuit 162 for which, for example, the Philips IC SAA 3004, which has extensively been described in Reference 4, can be used. When a key is depressed, a code which is specific of that key is generated by the transmitter circuit 162, which code is transferred via an infrared carrier to the local receiver 17, demodulated in this receiver and subsequently presented to the microcomputer 12. This microcomputer thus receiv

es operating instructions and activates, via the bus system 11, one of the circuits connected thereto. It is to be noted that an operating instruction may be a single instruction, that is to say, it is complete after depressing only one key. It may also be multiple, that is to say, it is not complete until two or more keys have been depressed. This situation occurs, for example, when the receiver is operating in the teletext mode. Operation of figure keys then only yields a complete operating instruction when, for example, three figure keys have been depressed. As is known, such a combination results in the page number of the desired teletext page.

es operating instructions and activates, via the bus system 11, one of the circuits connected thereto. It is to be noted that an operating instruction may be a single instruction, that is to say, it is complete after depressing only one key. It may also be multiple, that is to say, it is not complete until two or more keys have been depressed. This situation occurs, for example, when the receiver is operating in the teletext mode. Operation of figure keys then only yields a complete operating instruction when, for example, three figure keys have been depressed. As is known, such a combination results in the page number of the desired teletext page. The character generator

As already stated, a character is a matrix comprising m 2 rows of m 1 picture elements each. Each picture element corresponds to a line section of a predetermined length (measured with respect to time); for example, q/μsec. Such a matrix is indicated at A in FIG. 2 for m 1 =6 and m 2 =10. More particularly this is the matrix of a dummy character. The character for the letter A is indicated at B in the same FIG. 2. It is to be noted that the forty characters constituting a line of teletext page are contiguous to one another without any interspace. The sixth column of the matrix then ensures the required spacing between the successive letters and figures.

FIG. 3 shows diagrammatically the general structure of the character generator described in Reference 2 and adapted to supply a set of R, G and B signals for each picture element of the character. This character generator comprises a buffer 940 which receives the character codes from memory 93 (see FIG. 1). These character codes address a sub-memory in a memory medium 941, which sub-memory consists of m 1 ×m 2 memory elements each comprising a character picture element code. Each m 1 ×m 2 char

acter picture element code corresponds to a picture element of the character and defines, as already stated, whether the relevation picture element must be displayed in the so-called foreground colour or in the so-called background colour. Such a character picture element code has the logic value "0" or "1". A "0" means that the corresponding picture element must be displayed in the background colour (for example, white). The "1" means that the corresponding picture element must be displayed in the foreground colour (for example, black or blue). At C in FIG. 2 there is indicated, the contents of the sub-memory for the character shown at B in FIG. 2.

acter picture element code corresponds to a picture element of the character and defines, as already stated, whether the relevation picture element must be displayed in the so-called foreground colour or in the so-called background colour. Such a character picture element code has the logic value "0" or "1". A "0" means that the corresponding picture element must be displayed in the background colour (for example, white). The "1" means that the corresponding picture element must be displayed in the foreground colour (for example, black or blue). At C in FIG. 2 there is indicated, the contents of the sub-memory for the character shown at B in FIG. 2. The addressed sub-memory is read now by row under the control of a character row signal LOSE. More particularly, all first rows are read of the sub-memories of the forty characters of a teletext line, subsequently all second rows are read, then all third rows are read and so forth until finally all tenth rows are read.

The six character element codes of a row will hereinafter be referred to as CH(1), CH(2), . . . CH(6). They are made available in parallel by the memory medium 941 and are applied to a converter circuit 942 operating as a parallel-series converter. In addition to the six character picture element codes it receives display clock pulses DCL and applies these six character picture element codes one by one at the rate of the display clock pulses to a display control circuit 943 which converts each character picture element code into a set of R, G, B signals.

The display clock pulses DCL and the character row signal LOSE are supplied in known manner (see

When the rate of the reference clock pulses increases, the rate of the display clock pulses also increases and the character width decreases. Without changing the character width the above-described character generator can also be used without any essential changes if the rate of the reference clock pulses is an integral multiple of 6 MHz. In that case the desired display clock pulses can e derived from the reference clock pulses by means of a divider circuit with an integral dividing number. However, there is a complication if f 0 is not a rational multiple of 6 MHz, for example, if f 0 =13.5 MHz and each character nevertheless must have a width of substantially 1 μsec. Two generator circuits and a plurality of converter circuits suitable for use in the character generator shown in FIG. 3 and withstanding the above-mentioned complication will be described hereinafter.

FIG. 4 shows an embodiment of the generator circuit 944 and the converter circuit 942. The reference clock pulses TR are assumed to occur at a rate of 13.5 MHz. To derive the desired display clock pulses from these reference clock pulses, the generator circuit 944 comprises a modulo-N-counter circuit 9441 which receives the 13.5 MHz reference clock pulses TR indicated at A in FIG. 5. The quantity N is chosen to be such that N clock pulse periods of the reference clock pulses substantially correspond to the desired character width of, for example, 1 μsec. This is the case for N=14, which yields a character width of 1.04 μsec.

An encoding network 9442 comprising two output lines 9443 and 9444 is connected to this modulo-N-counter circuit 9441. This encoding network 9442 each time supplies a display clock pulse in response to the first, the third, the sixth, the eighth, the eleventh and the thirteenth reference clock pulse in a group of fourteen reference clock pulses. More particularly the display clock pulse, which is obtained each time in response to the first reference clock pulse of a group, is applied to the output line 9443, whilst the other display clock pulses are applied to the output line 9444. Thus, the pulse series shown at B and C in FIG. 5 occur at these output lines 9443 and 9444, respectively.

The converter circuit 942 is constituted by a shift register circuit 9420 comprising six shift register elements each being suitable for storing a character picture element code CH(.) which is supplied by the memory medium 941 (see FIG. 3). This shift register circuit 9420 has a load pulse input 9421 and a shift pulse input 9422. The load pulse input 9421 is connected to the output line 9443 of the encoding network 9442 and thus receives the display clock pulses indicated at B in FIG. 5. The shift pulse input 9422 is connected to the output line 9444 of the encoding network 9442 and thus receives the display clock pulses indicated at C in FIG. 5.

This converter circuit operates as follows. Whenever a display clock pulse occurs at the load pulse input 9421, the six character picture element codes CH(.) are loaded into the shift register circuit 9420. The first character picture element code CH(1) thereby becomes immediately available at the output. The contents of the shift register el

ements are shifted one position in the direction of the output by each display clock pulse at the shift pulse input 9422.

ements are shifted one position in the direction of the output by each display clock pulse at the shift pulse input 9422. Since the display clock pulses occur at mutually unequal distances, the time interval during which a character picture element code is available at the output of the shift register circuit is longer for the one character picture element code than for the other. This is shown in the time diagrams D of FIG. 5. More particularly the diagrams show for each character picture element code CH(.) during which reference clock pulse periods the code is available at the output of the shift register circuit. The result is that the picture elements from which the character is built up upon display also have unequal lengths as is indicated at D and E in FIG. 2.

The same character display is obtained by implementing the converter circuit 942 and the generator circuit 944 in the way shown in FIG. 6. The generator circuit 944 again comprises the modulo-N-counter circuit 9441 with N=14 which receives the 13.5 MHz reference clock pulses TR shown at A in FIG. 7. An encoding network 9445 is also connected to this counter circuit, which network now comprises six output lines 9446(.). This encoding network 9445 again supplies a display clock pulse in response to the first, the third, the sixth, the eighth, the eleventh and the thirteenth reference clock pulse of a group of fourteen reference clock pulses, which display clock pulses are applied to the respective output lines 9446(1), . . . , 9446(6). Thus, the pulse series indicated at B, C, D, E, F and G in FIG. 7 occur at these outputs.

The converter circuit 942 has six latches 9423(.) each adapted to store a character picture element code CH(.). The outputs of these latches are connected to inputs of respective AND gate circuits 9424(.). Their outputs are connected to inputs of an OR gate circuit 9425. The AND gate circuit is 9424(.) are controlled by the control signals S(1) to S(6), respectively, which are derived by means of a pulse widening circuit 9426 from the display clock pulses occurring at the output lines 9446(.) of the encoding network 9445 and which are also shown in FIG. 7. Such a control signal S(i) determines how long the character picture element code CH(i) is presented to the output of the OR gate circuit 9425 and hence determines the length of the different picture elements of the character on the display screen.

In the above-described embodiments of the converter circuit 942 and the generator circuit 944 the character generator supplies exactly contiguous picture elements on the display screen. This means that the one picture elements begins immediately after the previous picture element has ended. The result is that round and diagonal shapes become vague. It is therefore common practice to realize a rounding for such shapes. This rounding can be realized with the converter circuit shown in FIGS. 4 and 6

by ensuring that two consecutive picture elements partly overlap each other. This is realized in the converter circuit shown in FIG. 4 by means of a rounding circuit 9427 which receives the character picture element codes occurring at the output of the shift register circuit 9420. This rounding circuit 9427 comprises an OR gate 9427(1) and a D flip-flop 9427(2). The T input of this flip-flop receives the clock pulses shown at E in FIG. 5, which pulses are derived from the reference clock pulses TR by means of a delay circuit 9427(3). This circuit has a delay time t 0 for which a value in the time diagram indicated at E in FIG. 5 is chosen which corresponds to half a clock pulse period of the reference cock pulses. The character picture element codes supplied by the shift register circuit 9420 are now applied directly and via the D flip-flop 9427(2) to the OR gate which thereby supplies the six character picture element codes CH(.) in the time intervals as indicated at F in FIG. 5. The result of this measure for the display of the character with the letter A is shown at F in FIG. 2.

by ensuring that two consecutive picture elements partly overlap each other. This is realized in the converter circuit shown in FIG. 4 by means of a rounding circuit 9427 which receives the character picture element codes occurring at the output of the shift register circuit 9420. This rounding circuit 9427 comprises an OR gate 9427(1) and a D flip-flop 9427(2). The T input of this flip-flop receives the clock pulses shown at E in FIG. 5, which pulses are derived from the reference clock pulses TR by means of a delay circuit 9427(3). This circuit has a delay time t 0 for which a value in the time diagram indicated at E in FIG. 5 is chosen which corresponds to half a clock pulse period of the reference cock pulses. The character picture element codes supplied by the shift register circuit 9420 are now applied directly and via the D flip-flop 9427(2) to the OR gate which thereby supplies the six character picture element codes CH(.) in the time intervals as indicated at F in FIG. 5. The result of this measure for the display of the character with the letter A is shown at F in FIG. 2. The same rounding effect can be realized by means of the converter circuit shown in FIG. 6, namely by providin

g it with a rounding circuit as well. This is shown in FIG. 8. In this FIG. 8 the elements corresponding to those in FIG. 6 h

g it with a rounding circuit as well. This is shown in FIG. 8. In this FIG. 8 the elements corresponding to those in FIG. 6 h ave the same reference numerals. The converter circuit 942 shown in FIG. 8 differs from the circuit shown in FIG. 6 in that the said rounding circuit denoted by the reference numeral 9428 is incorporated between the pulse widening circuit 9426 and the AND gate circuits 9424(.). More particularly this rounding circuit is a pluriform version of the rounding circuit 9427 shown in FIG. 4 and is constituted by six D flip-flops 9428(.) and six OR gates 9429(.). These OR gates receive the respective control signals S(1) to S(6) directly and via the D flip-flops. The T inputs of these D flip-flops again receive the version of the reference clock pulses delayed over half a reference clock pulse period by means of the delay circuit 94210. This rounding circuit thus supplies the control signals S'(.) shown in FIG. 7.

ave the same reference numerals. The converter circuit 942 shown in FIG. 8 differs from the circuit shown in FIG. 6 in that the said rounding circuit denoted by the reference numeral 9428 is incorporated between the pulse widening circuit 9426 and the AND gate circuits 9424(.). More particularly this rounding circuit is a pluriform version of the rounding circuit 9427 shown in FIG. 4 and is constituted by six D flip-flops 9428(.) and six OR gates 9429(.). These OR gates receive the respective control signals S(1) to S(6) directly and via the D flip-flops. The T inputs of these D flip-flops again receive the version of the reference clock pulses delayed over half a reference clock pulse period by means of the delay circuit 94210. This rounding circuit thus supplies the control signals S'(.) shown in FIG. 7. Philips Data Handbook, Electronic Components and Materials "Integrated Circuits: Part 3, Sep. 1982: ICs for Digital Systems in Radio, Audio, and Video Equipment: SAA5020 Series", pp. 1-10.

Philips Data Handbook, Electronic Components and Materials "Integrated Circuits: Book IC02a, 1986: Video and Associated Systems: Bipolar, MOS: Types MAB8031AH to TDA1521", pp. 374-375.

F. J. R. Kinghorn, "Computer Controlled Teletext"; Electronic Components and Applications; vol. 6, No. 1, 1984, pp. 15-29.

"World System Teletext Technical Specification", Revised Mar. 1985, pp. 1-10 and 38-41.

Philips Data Handbook, Electronic Components and Materials; "Integrated Circuits, Part 2: Jan. 1983: Bipolar ICs for Video Equipment: TDA2540, TDA2540Q"; pp. 1-8.

Philips Data Handbook, Electronic Components and Materials; "Integrated Circuits: Part 2: Jan. 1983: Bipolar ICs for Video Equipment: TDA 3562A"; pp. 1-16.

Philips Data Handbook, Electronic Components and Materials "Integrated Circuits: Part 3, Sep. 1982: IC's for Digital Systems in Radio, Audio, and Video Equipment: SAA3004"; pp. 1-10.

Philips Data Handbook, Electronic Components and Materials, "Integrated Circuits: Part 3, Sep. 1982: Ics for Digital Systems in Radio, Audio, and Video Equipment: SAB3035", pp. 1-4.

Philips Data Handbook, Electronic Components and Materials "Integrated Circuits: Part 3, Sep. 1982: ICs for Digital Systems in Radio, Audio and Video Equipment: TDB2033", pp. 1-9.

PHILIPS 26CS5280 /01Z TXT VERONESE CHASSIS K40 Teletext / Videotext Error correction circuit using character probability :

An error correction circuit in a television receiver for receiving, for example, Teletext information, Viewdata information or information of comparable systems. The codes representing symbol information received by the receiver are classified into one out of two or more classes in dependence on the frequency of their occurrence, this classification being an indication of the extent to which it is probable that a received code is correctly received.

In FIG. 1, a picture text television receiver has a receiving section, audio and video amplifiers 4 and 9 and a picture tube 10, 11. A text decoder 21 receives symbol information which is stored in a store 25 for display. An error detector circuit 40 including a comparison circuit 43 and two parity circuits 41 and 42, and checks for parity between newly received and already stored symbol information. A reliability circuit 60 is also included.

In FIG. 1, a picture text television receiver has a receiving section, audio and video amplifiers 4 and 9 and a picture tube 10, 11. A text decoder 21 receives symbol information which is stored in a store 25 for display. An error detector circuit 40 including a comparison circuit 43 and two parity circuits 41 and 42, and checks for parity between newly received and already stored symbol information. A reliability circuit 60 is also included.1. An error correction circuit for a receiving device for receiving digitally transmitted symbol information, the transmission of this information being repeated one or more times, the receiving device having a decoding circuit for decoding the received information, an information store coupled to said decoding circuit for storing the information, a circuit for generating synchronizing signals and a video converter circuit coupled to said information store and said generating circuit for converting information and synchronizing signals into a composite video signal for application to a standard television receiver, a symbol address in the information store corresponding with a symbol location on a television picture screen, a symbol location being a portion of a text line which is displayed with a number of video lines greater than one, the error correction circuit being coupled to said decoding circuit and said information store and including means coupled between said decoding circuit and said information store for checking newly received symbol information against symbol information stored in the information store for the corresponding symbol location, a write-switch having one input coupled to said decoding circuit and an output coupled to said information store, and a write-setting circuit, coupled to another input of said write-switch, which determines whether the newly received information is written or not written into the information store, said write-setting circit having an input coupled to said checking means whereby the results of said checking are a factor in the setting of said write-switch by said write-setting circuit, characterized in that the error correction circuit further comprises a classification circuit coupled to the output of said decoding circuit for classifying a newly received and decoded symbol in one of at least two classes on the basis of the probability of occurrence of the newly received symbol, the input of the classification circuit being coupled to another input of the write-setting circuit. 2. An error correction circuit for a receiving device as claimed in claim 1, characterized in that the write-setting circuit includes a reliability circuit and the information store comprises an additional storage element for each symbol address in the information store for storing a reliability bit associated with that symbol address, inputs of the reliability circuit being coupled to the classification circuit and to the information store for accessing the additional storage elements, for determining, from the additional storage element corresponding with the symbol address position of newly received symbol information, a new reliability bit, an output of the reliability circuit being coupled back to the information store for writing this new reliability bit into the corresponding additional storage element when the reliability bit for this symbol address changes its value. 3. An error correction circuit for a receiving device as claimed in claim 2, characterized in that the checking means comprises a comparison circuit for bit-wise comparing a newly received and decoded symbol with a symbol read from an address of the information store, this address corresponding with the symbol location, a comparison output of the comparison circuit being coupled to a further input of the reliability circuit. 4. An error correction circuit for a receiving device as claimed in any one of the preceding claims, characterized in that the classification circuit comprises a parity circuit for classifying newly received symbols for respective particular symbol locations into one of two classes which correspond to an even and an odd parity respectively, of the newly received information, and for classifying symbol information already stored in the corresponding symbol addresses in the information store. 5. An error correction circuit for a receiving device as claimed in claim 2, characterized in that the reliability circuit comprises a reliability flipflop and a reliability read circuit for this flipflop, an output of which also constitutes the output of the reliability circuit. 6. An error correction circuit for a receiving device as claimed in claim 1, characterized in that the error correction circuit comprises a second classification circuit, coupled between said other classification circuit and said write-setting circuit and having inputs coupled to said information store, for classifying a symbol read from the information store. 7. An error correction circuit for a receiving device as claimed in claim 1 characterized in that the information store comprises, for each symbol address in the information store, at least one further storage element for storing the classification associated with the symbol for that symbol address.

Error correction circuits of the above type are used in auxiliary apparatus for the reception of Teletext transmissions or comparable transmissions, these auxiliary apparatus being connected to a standard television receiver either by applying video signals to a so-called video input, or by applying these video signals, modulated on a carrier, to an aerial input of the television set. There are already television receivers with a built-in Teletext receiver already including an error correction circuit of the above-mentioned type.

The present Teletext system as it is already used rather widely in the UK, is based on an 8-bit symbol teletext code having 7 information bits and 1 parity bit; this parity bit is chosen so that each 8-bit symbol in the code has a so-called "odd" parity, that is to say there is an odd number of ones in a symbol, and, consequently, also an odd number of zeros. A display on the television picture screen comprises a "page" consisting of a number of rows (e.g. 24) of symbols.

Only symbols with the "odd" parity are stored in the information store. Each symbol represents either an alpha-numeric or a graphics character for display on the picture screen, or a control symbol.

If, in a subsequent transmission cycle for the same symbol location of the same page, a faulty symbol is detected, then, assuming that only a single error occurs within a symbol, this faulty symbol will have an even parity, that is to say a "one" changed into a "zero", or vice versa, as the result of the error. In this case the information store is not written into and the old information is retained in the relevant symbol address.

For a poor transmission condition an error probability of 0.01 is assumed, that is to say one symbol out of a hundred symbols is received incorrectly. In a complete page having 960 Teletext symbol locations, (i.e. up to 24 rows of up to 40 symbols per row) the displayed page then shows, after the first cycle, 9 to 10 erroneous spaces on average. In the present system substantially all these erroneous spaces are likely to have been corrected in the second cycle.

When the receiving conditions are better, this situation is already correspondingly more favourable in the first cycle. Even in the poorest receiving conditions, it appears that the number of double errors is so small that they may be neglected. Double errors therefore are hardly ever taken into consideration hereafter. It will be apparent that in this system each symbol has a certain degree of redundancy in the form of the parity bit, but this is off-set by the drawback that the 8-bit code, which has 256 (=2 8 ) combinations, is utilized for only 50% of this capacity, i.e. only for the 128 symbols having "odd" parity.

Although, for the U.K. itself, such a code has a sufficient capacity to contain all desired symbols for control, graphics elements, letters, figures, punctuation marks, etc. as required for Teletext and also, for example, for Viewdata, it is not possible to allot a specific symbol to all of the special characters occurring in various other languages.

Several European languages, in so far they are written in latin characters, have all sorts of "extra" characters, for example Umlaut letters, accent letters, etc. When all these extra characters are totalled, including Icelandic, Maltese and Turkish, then it appears that a total of approximately 220 symbols is required, namely the 128 known symbols plus further symbols for these "extra" characters.

Several solutions have been proposed to solve this, but so far none of these have been satisfactory as they are either very cumbersome or allow only one language within one page, so that it is impossible or very difficult e.g. to quote foreign names in a page of text.

Alternatively it has been proposed--and this is of course very obvious--to use the entire 8-bit code for symbols. As the redundancy in the code has now been reduced to zero, no correction can be effected in the second cycle. If two codes for one symbol location differ from one another in different transmission cycles, it is theoretically impossible to decide with certainty which one of the two codes is correct. An additional information store is required to enable a comparison between a newly received symbol in the third cycle and a symbol from the second and the first cycles, and to take the frequently used majority decision thereafter. This is possible, but three reading cycles are necessary before the number of errors is reduced to an acceptable level. As each transmission cycle of a completely full magazine (i.e. a plurality of pages) takes approximately 25 seconds, the correct text is not known until after approximately 75 seconds.