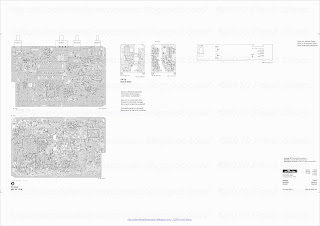

The METZ 70TH73 NORDKAP-70S CHASSIS 600G-1099 is particularly complex and sophisiticated.

It's clearly representing the METZ style of hilghly elaborate product combined with high quality and features.

The VIDEO digital architecture is based around ITT / MICRONAS PRIMUS Powerful Scan Rate Converter including Multistandard Color Decoder, and ITT/ MICRONAS SDA6000 Teletext Decoder with Embedded 16-bit Controller M2 HIGHGRAPHICS.

INFINEON TDA16846,

Controller for Switch Mode Power

Supplies Supporting Low Power

Standby and Power Factor.

The TDA 16846-2 (this name is used in the description for all types) is optimized to

The TDA 16846-2 (this name is used in the description for all types) is optimized tocontrol free running or fixed frequency flyback converters with or without Power Factor

Correction (Current Pump). To provide low power consumption at light loads, this device

reduces the switching frequency in small steps with load, towards an adjustable

minimum (e. g. 20 kHz in standby mode). Additionally, the startup current is very low. To

avoid switching stress on the power devices, the power transistor is always switched on

at minimum voltage. A special circuit is implemented to avoid jitter. The device has several protection functions: VCC over- and undervoltage, mains undervoltage, current

limiting and 2 free usable fault comparators. Regulation can be done by using the

internal error amplifier or an opto coupler feedback (additional input). The output driver

is ideally suited for driving a power MOSFET. Fixed frequency and synchronized

operation are also possible.

The TDA 16846-2 is suited for TV-, VCR- sets, SAT receivers and other sets for

consumer electronics. It also can be used in PC monitors.

The TDA 16847-2 is identical with TDA 16846-2 but has an additional power

measurement output (pin 8) which can be used as a Temporary High Power Circuit.

Features

• Line Current Consumption with PFC

• Low Power Consumption

• Stable and Adjustable Standby Frequency

• Very Low Start-up Current

• Soft-Start for Quiet Start-up

• Free usable Fault Comparators

• Synchronization and Fixed Frequency Circuits

• Over- and Undervoltage Lockout

• Switch Off at Mains Undervoltage

• Temporary High Power Circuit (only TDA 16847-2)

• Mains Voltage Dependent Fold Back Point Correction

• Continuous Frequency Reduction with Decreasing Load

• Adjustable and Voltage Dependent Ringing Suppression Time.

Functional Description

Functional DescriptionStart Up Behaviour (Pin 14)

When power is applied to the chip and the voltage V14 at Pin 14 (VCC) is less than the

upper threshold (VON) of the Supply Voltage Comparator (SVC), then the input current

I14 will be less than 100 µA. The chip is not active (off state) and driver output (Pin 13)

and control output (Pin 4) will be actively held low. When V14 exceeds the upper SVC

threshold (VON) the chip starts working and I14 increases. When V14 falls below the lower

SVC threshold (VOFF) the chip starts again from its initial condition. Figure 4 shows the

start-up circuit and Figure 5 shows the voltage V14 during start up. Charging of C14 is

done by resistor R2 of the “Primary Current Simulation” (see later) and the internal diode

D1, so no additional start up resistor is needed. The capacitor C14 delivers the supply

current until the auxiliary winding of the transformer supplies the chip with current

through the external diode D14.

It is recommended to apply a small RF snubber capacitor of e.g. 100 nF parallel to the

electrolytic capacitor at pin 14 as shown in the application circuits in Figures 15, 16 , and

17.

To avoid multiple pulses during start up in fixed frequency mode (danger of transformer

saturation), the IC works in freerunning mode until the pulses at pin 3 (RZI) exceed the

2.5 V threshold (only TDA 16846-2, TDA 16847-2).

Over- and Undervoltage Lockout OV/SVC (Pin 14)

When V14 at Pin 14 exceeds 16.5 V, e. g. due to a fault in the regulation circuit, the Error

Flip Flop ERR is set and the output driver is shut-down. When V14 goes below the lower

SVC threshold, ERR is reset a

nd the driver output (Pin 13) and the soft-start (Pin 4) are

nd the driver output (Pin 13) and the soft-start (Pin 4) areshut down and actively held low.

Primary Voltage Check PVC (Pin 11)

When the voltage V11 at Pin 11 goes below 1 V the Error Flip Flop (ERR) is set. E.g. a

voltage divider from the rectified mains at Pin 11 prevents high input currents at a too low

input voltage.

Free Usable Fault Comparator FC1 (Pin 10)

When the voltage at Pin 10 exceeds 1 V, the Error Flip Flop (ERR) is set. This can be

used e. g. for mains overvoltage shutdown.

Free Usable Fault Comparator FC2 (Pin 6)

When the voltage at Pin 6 exceeds 1.2 V, the Error Flip Flop (ERR) is set. A resistor

between Pin 9 (REF) and ground is necessary to enable this fault comparator.

Voltage dependent Ringing Suppression Time

During start-up and short-circuit operation, the output voltage of the converter is low and

parasitic zero crossings are applied for a longer time at Pin 3. Therefore the Ringing

Suppression Time TC1 (see “Off-Time Circuit OTC (Pin 1)”) is extended with a factor of

2.2 at a low output voltage. The voltage at pin 1 must not fall below the limit V1L.

THOMSON TDA8172 TV VERTICAL DEFLECTION OUTPUT CIRCUIT,

DESCRIPTION

DESCRIPTIONThe TDA8172 is a monolithic integrated circuit in

HEPTAWATTTMpackage. It is a high efficiency

power boosterfordirectdriving of verticalwindings

of TV yokes. It is intendedfor use in Color andB &

W television as well as in monitorsand displays.

MOUNTING INSTRUCTIONS

The power dissipated in the circuit must be re-

moved by adding an externalheatsink.

Thanks to the HEPTAWATTTMpackage attaching

the heatsinkis very simple, a screw or a compres-

sion spring (clip) being sufficient.

Between the heatsink and the package it is better

to insert a layer of silicon grease, to optimize the

thermal contact ; no electrical isolation is needed

between the two surfaces, since the tab is con-

nected to Pin 4 which is ground.

THOMSON TDA7265 25 +25W STEREO AMPLIFIER WITH MUTE & ST-BY.

DESCRIPTION

The TDA7265 is class AB dual Audio power am-

plifier assembled in the Multiwatt package, spe-

cially designed for high quality sound application

as Hi-Fi music centers andstereo TV sets.

WIDE SUPPLY VOLTAGE RANGE (UP TO

±25V ABS MAX.)

SPLIT SUPPLY

HIGH OUTPUT POWER

25 + 25W @ THD=10%, RL = 8Ω, VS = +20V

NO POPAT TURN-ON/OFF

MUTE(POP FREE)

STAND-BY FEATURE (LOWIq)

SHORT CIRCUIT PROTECTION.

THERMAL OVERLOAD PROTECTION

BRIDGE APPLICATION

Another application suggestion concerns the

BRIDGE configuration, where the two power am-

plifiers are connected as shown by the schematic

diagram of figure.17.

This application shows, however, some operative

limits due to dissipation and current capability of

the output stage. For this reason, we reccomend

to use the TDA7265 in bridge with the supply volt-

age equal/lower than ±16V when the load is 8Ω;

with higher loads (i.e.16Ω), the amplifier can work

correctlyin the whole supplyvoltage range.

The detected characteristics of T.H.D. vs Pout

and FrequencyResponse are shown in fig.18 and

fig.19.

With R1=8Ω, Vs=+/-16V the maximum output

power obtainableis 50Wat T.D.H.=10%.

The quiescent current remains unchanged with

respect to the stereo configuration (~80mA as

typical at Vs=+/-16V).

The last point to take into consideration concerns

the short-circuit protection.As for the stereo appli-

cation, the TDA7265 is fully protected against any

kind of short-circuit ( between Out/Gnd, Out/+Vs

and Out/-Vs).

TDA9817; Single/multistandard VIF/SIF-PLL and FM-PLL/AM demodulators.

GENERAL DESCRIPTION

GENERAL DESCRIPTIONThe TDA9817 is an integrated circuit for single standard

vision IF signal processing and FM demodulation.

The TDA9818 is an integrated circuit for multistandard

vision IF signal processing, sound AM and FM

demodulation.

FEATURES

FEATURES• 5 V supply voltage

• Applicable for Intermediate Frequencies (IFs) of

38.9, 45.75 and 58.75 MHz

• Gain controlled wide band Video IF (VIF) amplifier

(AC-coupled)

• True synchronous demodulation with active carrier

regeneration (very linear demodulation, good

intermodulation figures, reduced harmonics and

excellent pulse response)

• Robustness for over-modulation better than 105% due

to gated phase detector at L/L accent standard and

PLL-bandwidth control at negative modulated standards

• Voltage Controlled Oscillator (VCO) frequency

switchablebetweenL and L accent(alignmentexternal)

picture carrier frequency

• VIF Automatic Gain Control (AGC) detector for gain

control, operating as peak sync detector for B/G, peak

white detector for L; signal controlled reaction time for L

• Tuner AGC with adjustable TakeOver Point (TOP)

• Automatic Frequency Control (AFC) detector without

extra reference circuit

• AC-coupled limiter amplifier for sound intercarrier signal

• Alignment-free FM Phase-Locked Loop (PLL)

demodulator with high linearity

• Sound IF (SIF) input for single reference Quasi Split

Sound (QSS) mode (PLL controlled); SIF AGC detector

for gain controlled SIF amplifier; single reference QSS

mixer able to operate in high performance single

reference QSS mode and in intercarrier mode

• AM demodulator without extra reference circuit

• Stabilizer circuit for ripple rejection and to achieve

constant output signals

• ElectroStatic Discharge (ESD) protection for all pins.

FUNCTIONAL DESCRIPTION

The integrated circuit comprises the functional blocks as

shown in Fig.1:

• Vision IF amplifier and VIF AGC detector

• Tuner AGC

• Frequency Phase Locked Loop detector (FPLL)

• VCO, Travelling Wave Divider (TWD) and AFC

• Video demodulator and amplifier

• Sound IF amplifier and SIF AGC

• Single reference QSS mixer

• AM demodulator

• FM-PLL demodulator

• Audio Frequency (AF) signal processing

• Internal voltage stabilizer.

Vision IF amplifier and VIF AGC detector

The vision IF amplifier consists of three AC-coupled

differential amplifier stages. Each differential stage

comprises a feedback network controlled by emitter

degeneration.

The AGC detector generates the required VIF gain control

voltage for constant video output by charging/discharging

the AGC capacitor. Therefore for negative video

modulation the sync level and for positive video

modulation the peak white level of the video signal is

detected. In order to reduce the reaction time for positive

modulation, where a very large time constant is needed,

an additional level detector increases the discharging

current of the AGC capacitor (fast mode) in the event of a

decreasing VIF amplitude step. The additional level

information is given by the black-level detector voltage.

Tuner AGC

The AGC capacitor voltage is converted to an internal

IF control signal, and is fed to the tuner AGC to generate

the tuner AGC output current at pin TAGC (open-collector

output). The tuner AGC takeover point can be adjusted at

pin TADJ. This allows to match the tuner to the SAW filter

in order to achieve the optimum IF input level.

Frequency Phase Locked Loop detector (FPLL)

The VIF-amplifier output signal is fed into a frequency

detector and into a phase detector via a limiting amplifier.

During acquisition the frequency detector produces a

DC current proportional to the frequency difference

between the input and th

e VCO signal. After frequency

e VCO signal. After frequencylock-in the phase detector produces a DC current

proportional to the phase difference between the VCO and

the input signal. The DC current of either frequency

detector or phase detector is converted into a DC voltage

via the loop filter, which controls the VCO frequency. In the

event of positive modulated signals the phase detector is

gated by composite sync in order to avoid signal distortion

for overmodulated VIF signals.

VCO, Travelling Wave Divider (TWD) and AFC

The VCO operates with a resonance circuit (with L and C

in parallel) at double the picture carrier frequency. The

VCO is controlled by two integrated variable capacitors.

The control voltage required to tune the VCO from its

free-running frequency to actually double the picture

carrier frequency is generated by the frequency-phase

detector (FPLL) and fed via the loop filter to the first

variable capacitor. This control voltage is amplified and

additionally converted into a current which represents the

AFC output signal. At centre frequency the AFC output

current is equal to zero.

For TDA9818: the VCO

centre frequency can be

centre frequency can bedecreased (required for L accent standard) by activating

an additional internal capacitor. This is achieved by using

the L accent switch. In this event the second variable

capacitor can be controlled by a variable resistor at the

L accentswitchforsettingtheVCOcentrefrequencytothe

required L accent value.

The oscillator signal is divided by 2 with a TWD which

generates two differential output signals with a 90 degree

phase difference independent of the frequency.

Video demodulator and amplifier

The video demodulator is realized by a multiplier which is

designed for low distortion and large bandwidth. The

vision IF input signal is multiplied with the ‘in phase’ signal

of the travelling wave divider output. In the demodulator

stage the video signal polarity can be switched in

accordance with the TV standard.

The demodulator output signal is fed via an integrated

low-pass filter for attenuation of the carrier harmonics to

the video amplifier. The video amplifier is realized by an

operational amplifier with internal feedback and high

bandwidth. A low-pass filter is integrated to achieve an

attenuation of the carrier harmonics for B/G and

L standard. The standard dependent level shift in this

stage delivers the same sync level for positive and

negative modulation. The video output signal at pin CVBS

is 1.1 V (p-p) for nominal vision IF modulation, in order to

achieve 1 V (p-p) at sound trap output.

Sound IF amplifier and SIF AGC

The sound IF amplifier consists of two AC-coupled

differential amplifier stages. Each differential stage

comprises a controlled feedback network provided by

emitter degeneration.

The SIF AGC detector is related to the SIF input signal

(average level of AM or FM carrier) and controls the SIF

amplifier to provide a constant SIF signal to the

AM demodulator and single re

ference QSS mixer. At

ference QSS mixer. AtL standard (AM sound) the SIF AGC reaction time is set to

‘slow’ for nominal video conditions. But with a decreasing

VIF amplitude step the SIF AGC is set to ‘fast’ mode

controlled by the VIF AGC detector. In FM mode this

reaction time is always ‘fast’.

Single reference QSS mixer

The single reference QSS mixer is realized by a multiplier.

The SIF amplifier output signal is fed to the single

reference QSS mixer and converted to intercarrier

frequency by the regenerated picture carrier (VCO). The

mixer output signal is fed via a high-pass for attenuation of

the video signal components to the output pin QSS. With

this system a high performance hi-fi stereo sound

processing can be achieved.

For a simplified application without a sound IF SAW filter

the single reference QSS mixer can be switched to the

intercarrier mode by connecting pin SIF2 to ground. In this

mode the sound IF passes the vision IF SAW filter and the

composite IF signal is fed to the single reference QSS

mixer. This IF signal is multiplied with the 90 degree TWD

output signal for converting the sound IF to intercarrier

frequency. This composite intercarrier signal is fed to the

output pin QSS, too. By using this quadrature detection,

the low frequency video signals are removed.

AM demodulator

The AM demodulator is re

alized by a multiplier. The

alized by a multiplier. Themodulated SIF amplifier output signal is multiplied in

phase with the limited (AM is removed) SIF amplifier

output signal. The demodulator output signal is fed via an

integrated low-pass filter for attenuation of the carrier

harmonics to the AF amplifier.

FM-PLL demodulator

The FM-PLL demodulator consists of a limiter and an

FM-PLL. The limiter provides the amplification and

limitation of the FM sound intercarrier signal. The result is

high sensitivity and AM suppression. The amplifier

consists of 7 stages which are internally AC-coupled in

order to minimize the DC offset.

Furthermore the AF output signal can be muted by

connecting a resistor between the limiter input pin FMin

and ground.

The FM-PLL consists of an integrated relaxation oscillator,

an integrated loop filter and a phase detector. The

oscillator is locked to the FM intercarrier signal, output

from the limiter. As a result of locking, the oscillator

frequency tracks with the modulation of the input signal

and the oscillator control voltage is superimposed by the

AF voltage. The FM-PLL operates as an FM demodulator.

Audio Frequency signal processing

The AF amplifier consists of two parts:

1.

The AF pre-amplifier for FM sound is an operational

amplifier with internal feedback, high gain and high

common mode rejection. The AF voltage from the

PLL demodulator, by principle a small output signal, is

amplified by approximately 33 dB. The low-pass

characteristicoftheamplifierreducestheharmonicsof

the intercarrier signal at the sound output terminal

pin Vde-em at which the de-emphasis network for FM

sound is applied. An additional DC control circuit is

implemented to keep the DC level constant,

independent of process spread.

2.

The AF output amplifier (1

0 dB) provides the required

0 dB) provides the requiredoutput level by a rail-to-rail output stage. This amplifier

makes use of an input selector for switching to AM,

FM de-emphasis or mute state, controlled by the

standard switching voltage and the mute switching

voltage.

Internal voltage stabilizer

The bandgap circuit internally generates a voltage of

approximately 1.25 V, independent of supply voltage and

temperature. A voltage regulator circuit, connected to this

voltage, produces a constant voltage of 3.6 V which is

used as an internal reference voltage.

SDA9402(S) PRIMUS Powerful Scan Rate Converter including Multistandard Color Decoder,

General Description

The SDA 9402

(PRIMUS) is a new component of the

(PRIMUS) is a new component of theMicronas MEGAVISION® IC set in a copper CMOS

embedded DRAM technology. The SDA 9402

comprises all main functions of a digital featurebox in

one monolithic IC. The amount of features is limited in

favour of a low-cost solution. But no trade-off has been

made concerning picture quality. It is ideally suited to

work in conjunction with the ’enhanced digital

deflection processor’ SDA 9380. The package is pin-

upward compatible to other medium-range and high-

end devices of the SDA940X family. A 50/60Hz

derivative is also available (SDA9402S).

The device comprises a digital multistandard color

decoder, a RGB interface with fast-blank capability

(SCART), digital ITU656 input, scaling units including

panorama, embedded DRAM for upconversion, picture

improvements, temporal noise reduction as well as A/

D and D/A converter.

Features

Features• Integrated Video Matrix switch

– Up to seven CVBS inputs, up to two Y/C inputs,

– Up to three CVBS outputs (even when Y/C input)

– 9 bit amplitude resolution for CVBS, Y/C A/D converter

– AGC (Automatic Gain Control)

• Multi-standard color decoder

– PAL/NTSC/SECAM including all substandards

– Automatic recognition of chroma standard

– Only one crystal necessary for all standards

• RGB-FBL or YUV-H-V input

– 8 bit amplitude resolution for RGB or YUV

– 8 bit amplitude resolution for FBL or H

• ITU656 support

– ITU656 input (9402)

– ITU656 input or output (9402S, pin sharing)

• Noise reduction

– Motion adaptive temporal noise reduction

– Field-based temporal noise reduction for luminance and chrominance

– Different motion detectors for luminance and chrominance or identical

– Flexible programming of the temporal noise reduction parameters

– Automatic measurement of the noise level

• Horizontal scaling of the 1fH signal

– Split-screen possible with additional PiP or Text processor

• Flexible digital horizontal scaling of the 2fH signal

– Scaling factors: 3, ... [2 pixel resolution], ..., 0.75 including 16:9 compatibility

– 5 zone panorama generator

• Embedded memory

– On-chip memory controller

– Embedded DRAM core for field memory

– SRAM for PAL/SECAM delay line

• Data format 4:2:2

• Flexible clock and synchronization concept

– Horizontal line-locked or free-running mode

– Vertical locked or free-running mode

• Scan-rate-conversion

– Simple interlaced modes (100/120 Hz): AABB, AAAA, BBBB (9402 only)

– No scan-rate-conversion modes (50/60 Hz): AB, AA, BB (9402S only)

• Flexible output sync controller

– Flexible positioning of the output signal

– Flexible programming of the output sync raster

– ’Blank signal’ generation

Signal manipulations

– Still field

– Insertion of colored background

– Windowing

– Vertical chrominance shift for improved VCR picture quality

• Sharpness improvement

– Digital color transition improvement (DCTI)

– Peaking (luminance)

• Three D/A converters

– 9 bit amplitude resolution for Y, -(R-Y), -(B-Y) output

– 72 MHz clock frequency

– Two-fold oversampling for Anti-imaging

– Simplification of external analog postfiltering

• 1920 active pixel/per line in default configuration

• I²C-bus control (400 kHz)

– selectable I²C address

• 1.8V± 5% and 3.3V ± 5% supply voltages

• P-MQFP-80 package.

CVBS Frontend

The CVBS frontend consists of the color-decoding circuit itself, a sync processing circuit

for generation of H/V signals out of the CVBS signal, and the luminance processing. The

main task of the luminance processing is to remove the color carrier by means of a notch

filter. For PAL and SECAM operation a baseband delay line is used for U and V signals.

This can be used as comb filter in NTSC operation (only for chrominance). The RGB

input can either be used as an overlay for the CVBS channel (RGB+FBL) or as a full

master channel (RGB+H/V). The overlay is done by means of a soft-mix and can be used

e.g. for ’SCART’ connector. This block incorporates a matrix (for RGB signals) which is

switched off for YUV (e.g. YPbPr) input signals. A CBS (contrast, brightness, saturation)

control makes the input signal adjustable.

5.1.1

Source select

Figure 5-1 shows the analog frontend. The analog CVBS signal can be fed to the inputs

CVBS1...7 of SDA 9402 (amplitude 0.5...1.5Vpp). One signal is selected via CVBSEL1

and fed to first ADC. A second signal is selected via CVBSEL2 and fed to the other ADC.

CVBS4&5 or CVBS6&7 are intended to use as separate Y/C inputs (YCSEL). After

clamping to the back porch (switchable to sync-tip clamping by CLPSTGY) both signals

are AD-converted with an amplitude resolution of 9 bit. The conversion is done using a

20.25 MHz free-running stable crystal clock. Before this the signals are lowpassed by

antialias filter. Three inputs can be looped back to output CVBSO1-3 (CVBOSEL1,

CVBOSEL2, CVBSELO3). A signal addition is performed to output a CVBS signal even

when separate Y/C signals are used at input. Inputs that are not used are roughly

clamped to fit in the allowed voltage region. For stand-by operation (power-down mode),

A/D and D/A converter are switched off by STANDBY keeping the source-selector

operational.

Clamping

The clamp timing for the analog inputs is generated from its corresponding CVBS signal.

The clamping algorithm works with a split measurement pulse and a clamping pulse. The

measurement pulse is used to detect the clamping error. The clamping pulse is used to

enable current sources for reducing the detected clamping errors. The start and length

of the measurement signal is adjustable independently for both channels (CLMPST1,

CLMPD1, CLMPST2, CLMPD2). The start and length of the clamping signal is

adjustable for both channels independently (CLMPST1S, CLMPD1S, CLMPST2S,

CLMPD2S). Clamping signals for RGB-channel are not split. Clamping for these ADC

are controlled by CLMPST2 and CLMPD2 only. Clamping can be suppressed for some

lines by CLMPLOW and CLMPHIGH to ignore copyprotection information. No external

sync signals are required.

Synchronization

After elimination of the high frequency components of the CVBS signal by a low pass

filter, horizontal a

nd vertical sync pulses are separated. Horizontal sync pulses are

nd vertical sync pulses are separated. Horizontal sync pulses aregenerated by a digital phase locked loop. The time constant can be adjusted between

fast and slow behavior in four steps (PLLTC) to accommodate different input sources

(e.g. VCR). The time-constant can be changed during normal operation without visible

picture degradation.

Additionally weak input signals from a satellite dish (’fish’) become more stable when

SATNR is enabled. Vertical sync pulses are separated by integration of equalizing

pulses. A vertical flywheel mode improves vertical sync separation for weak signals

(VFLYWHL, VFLYWHLMD). Additionally, v-syncs may be gated by VTHRL and VTHRH

to reject invalid v-syncs. When no input signal is connected the device switches to a free-

running mode. The device can be configured to switch-on background color when no or

only a weak signal is applied (NOSIGB). 50 Hz or 60 Hz operation for sync separation

may be forced separately or selected to work automatically (FLNSTRD)

The digital multistandard chroma decoder is able to decode NTSC and PAL signals with

a subcarrier frequency of 3.58MHz and 4.43MHz (PAL B1)/M/N/602), NTSC M/4.4) as

well as SECAM signals with automatic standard detection. Alternatively a standard can

be forced. The demodulation is done with a regenerated color-carrier. For use of non-

standard crystals or factory adjustment, the frequency of the free-running regenerated

subcarrier can be adjusted between +/-270 ppm via SCADJ. For this purpose the crystal

deviation (SCDEV) ca

n be read out via I²C after chroma PLL locking (indicated by

n be read out via I²C after chroma PLL locking (indicated bySCOUTEN) and can be stored in ?C ROM for SCADJ. For test purposes, CPLLOF

allows a loop opening of the chroma PLL

For adjustment to the specific operational area an automatic norm detection is

selectable. Available 50 Hz color standards are PAL B, PAL N and SECAM. Available

60 Hz color standards are NTSC M, PAL M, PAL60 and NTSC44. For each line standard,

one or more color standards can be chosen for automatic standard detection. In addition,

a standard can be forced as well. Within each line standard, the standard is detected by

consequently switching from one to another. This standard detection process can be set

to slow or fast behavior (LOCKSP). In slow behavior, 25 fields are used to detect the

standard, whereas 15 fields are used in fast behavior. If unsuccessful within this time

period the system tries to detect another standard. For SECAM detection, a choice

between different recognition levels is possible (SCMIDL, SCMREL) and the evaluated

burst position is shiftable (BGPOS).

Color standard (STDET), line standard (LNSTDRD) and color killer status (CKSTAT)

can be read out.

Chroma filter characteristics

An Automatic Chroma Control (ACC) produces a stable output for input chroma

variations from (approximately) -30 dB to +6 dB compared to nominal burst value. The ACC reference value is programmable for NTSC and PAL independently (NTSCREF,

PALREF) to ensure correct color saturation. With ACCFIX, the ACC is disabled and a

constant value (dependent on NTSCREF and PALREF) is used instead. ACCFRZ holds

the current ACC value. The maximum amplification of the ACC can be limited by

ACCLIM. This results a smooth attenuation of color intensity for weak color carrier. If the

chrominance signal is below an adjustable threshold (CKILL (PAL; NTSC) or CKILLS

(SECAM)) the color is switched off. To prevent on / off switching, a hysteresis is given

by CON or CONS which is the value of switching on the color.

COLON switches on the color under any circumstance. The output of the colordecoder

can be set to UV or CrCb data by CRCB. For NTSC only, the color impression (tint) can

be adjusted by the Hue Control between -88 and 90 in steps of 0.7° (HUE). Low

chrominance values (+/- 1...3 LSB) may be deleted by UV-coring (UVCOR). The Chroma

bandwidth can be adjusted by CHRF. The value of CHRF has no linear dependency on

effective bandwidth. The proper constellations are shown in Figure 5-7. A filter with

asymmetrical characteristic around the color carrier is available (IFCOMP) .

IF prefilter

For SECAM mode, the de-emphasis filter can be adjusted by DEEMPFIR and

DEEMPIIR. The bell filter can be adjusted by BELLFIR and BELLIIR.

Bell filter (baseband): standard (black) and implementation (red)

The delay between Y and C is well aligned and can also be adjusted in steps of 50ns

(YCDEL). No picture shifting occurs when switching between different color standards

(e.g. SECAM -> PAL). A delay-line is implemented for PAL and SECAM signals. It acts

as a simple chrominance comb-filter for NTSC and can be disabled by COMB. This

improves the vertical chroma resolution, but cross-color remains.

Luminance Processing

A luminance notch filter is implemented to reject the chroma information from luminance.

Depending on the color standard, one of three different notch characteristics is chosen

(’PAL’, ’NTSC’, ’SECAM’). For PAL and SECAM standards, five different characteristics

are available. For NTSC standard, four different characteristics are available. They can

be selected by NTCHSEL. Alternatively, no notch should be used for Y/C input

(NOTCHOFF). The filter characteristics can be found in Figure 5-11...Figure 5-14. In

SECAM operation, the notch filter can be fixed to one frequency or toggle between 4.4

and 4.25 MHz depending on the transmitted color (Dr, Db) (SECNTCH). A simple

lowpass-filter can be enabled by LPPOST to further reduce high-frequency noise

component from the CVBS signal.

Filter characteristics for Y/C mode

For applications for which a black offset is not desired, controlling may be done using

LMOFST. The positive or negative offset is added to the Y signal before scaling.

RGB-Frontend

An analog RGB input port for an external RGB or YUV source is available. The incoming

signal is clamped to the back porch by a clamping pulse. As the memory is only able to

store a 4:2:2 picture, the YUV input signal is downconverted to 4:2:2. There are two operation modes available. The first one uses this input as an overlay input (soft mix).

The RGB or YUV signal must then be synchronized to the main CVBS signal. The so

called independent mode uses RGB / YUV including sync or H/V signals. This can be

used, for example, for a DVD player or set-top-box. When using H sync from a non CVBS

input (e.g. separate H-sync) this must be indicated by HINP. The usage of separate V

sync must be set by VINP.

Possible input signals for RGB Frontend

The delay of luminance and fast-blank can be adjusted by YFDEL, and chrominance can

be delay adjusted by UVDEL. If necessary, fast-blank can be adjusted fine by FBLDEL.

Digital Prefiltering

A digital prefiltering can be enabled. This reduces the bandwidth of very steep input

signals, such as a display of characters. A band limitation is required, because the

succeeding deskewing filter performs best below 14 MHz. The filtering is performed in

all four channels and can be disabled by AABYP. For signal conversion to 4:2:2, an

additional chrominance lowpass can be enabled by CHRSF. The deskewing filter can be

disabled by SKEWSEL. This is necessary when using the HOUT50-pin in connection

with a Micronas picture-in-picture

device (e.g. SDA938x, SDA948x, SDA958x).

device (e.g. SDA938x, SDA948x, SDA958x).In this application, the RGB input (in1, in2, in3) of the PiP can not be used for other RGB

signals (e.g. ’SCART’ is not possible).

RGB->YUV Matrix

RGB or YUV signals are selected by YUVSEL. The matrix coefficients are set according

to ITU recommendations.

Contrast, Brightness and Saturation Control of Input signal

The YUV signal can be manipulated in order to fit to the main channel. The contrast can

be adjusted between 0 and 1.97 in 64 steps (CONADJ). The brightness is adjustable in

255 steps (BRTADJ). Due to the independent chroma adjustment of U and V (64 steps

each, USAT, VSAT), UV as well as CrCb input signals can both be displayed correctly.

Soft Mix

The soft-mixing is done by means of alpha-mixing. Alpha is derived from the fast blank

input (FBL), which indicates a signal insertion. The value of ? is between ’0’ and ’128’.

’0’ means that only the main signal is fed through to the output. ’128’ means that only the

inserted signal becomes visible.

FBL activity and overflow detection

It is important to know whether the FBL input is used or not. Therefore a detection circuit

gives information via the I2C bus to the microcontroller. The circuit uses the FBL value

as input. If it is greater than a threshold for one or five clock cycles (FBLCONF), the I²C

register FBLACTIVE is set. This register is reset when it is read by the microcontroller.

PFBL, PG, PR, PB indicate an overflow of the corresponding ADC (upper limit:

ADC=255) exceeding 5 clock cycles duration. These signals are also set by overflow and

reset by I²C reading only.

Horizontal Prescaler (sample-rate-converter)

The main application is the conversion of the data coming from the 40.5/20.25MHz pixel

clock domain down to the number of pixels stored in the memory (factor 2/3). Generally

the number of incoming pixels can be decimated by a factor between 1 and 64 in a

granularity of 2 output pixels. The horizontal scaler reduces the number of incoming

pixels by subsampling. To prevent the introduction of alias distortion low pass filters are

used for luminance and chrominance processing (Figure 5-23). In case of ITU656 input,

the lowpass filter must be disabled by HAAPRESC.

The horizontal prescaler consists of two main subsampling stages. The first stage is a

scaler for rational decimation factors in a range of 1 to 2, controlled by HSCPRESC. The

second stage is a MTA (moving target average) filter for integer decimation factors

(1,2,3,4...32), controlled by HDCPRESC. Due to its architecture the MTA filter

automatically adapts its low pass filter characteristic to the used subsampling factor.

Noise Reduction

The Figure 5-24 shows a block diagram of the motion adaptive temporal noise reduction

(first order IIR filter). The structure of the temporal motion adaptive noise reduction is the

same for luminance as for chrominance signal. Noise reduction is enabled by NRON.

Temporal noise reduction

The equation below describes the behavior of the temporal adaptive noise reduction

filter. The same equation is valid for the chrominance signal. Depending on the motion

in the input signal, the K-factor Ky (Kuv) is adjustable between 0 (no motion) and 15

(motion) by the motion detector. The K-factor for the chrominance filter can be either Ky

(output of the luminance motion detector, TNRSEL=0) or Kuv (output of the chrominance

motion detector, TNRSEL=1). The delay of the feedback path is a field delay.

The output of the motion detector is weighted TNRCLC and TNRCLY. The output is

mapped to the values Ky and Kc by look-up-tables (LUT Y and LUT C). The input value

range is separated into 8 segments, where segment 0 covers the range 0...3, segment

1 covers the range 4...7 etc. and segment 7 covers the range 48...63 of motion value.

Noise Measurement

The noise measurem

ent algorithm can be used to change the parameters of the

ent algorithm can be used to change the parameters of thetemporal noise reduction processing depending on the actual noise level of the input

signal. This is done by the TV- microcontroller which reads the noise level (NOISEME),

and sends different parameter sets to the temporal noise reduction registers of the SDA

9402 depending on this value (0=no noise, 30=strong noise). Value 31 indicates an

overflow status which means that the measurement failed. The line taken for noise

measurement is selected by NMLINE. When NOISEME contains updated data which

was not read so far, NMSTATUS is set. NMSTATUS is reset when read.

Horizontal Postscaler

After field memory, the display processing is performed using a different clock. In this

way a decoupling of input and output clocks is achieved.

The conversion to the display clock is done by an interpolation filter. This can be used

for horizontal expansion in the range of 1...4 in steps of 2 pixels (HSCPOSC). Due to

increased clock frequency in the backend part (36 MHz instead of 27MHz), the horizontal

expansion factors result as 0.75 ... 3. This ensures that the factor 0.75 gives no loss of

resolution. This is used to show a 4:3 picture on a 16:9 tube.

Because of the nonlinear characteristic and integer number of pixel, sometimes different

HSCPOSC values result in the same decimation factors.

Panorama Mode

The picture can be geometrically di

storted in horizontal direction for an improved

storted in horizontal direction for an improvedimpression in the case of expansions of 4:3 pictures to a 16:9 ratio tube. It is enabled by

HPANON. The idea behind this panorama mode is to keep the middle part of the picture

in a 4:3 ratio and to stretch the left and the right to fill the entire width of the 16:9 screen.

For the adjustment of the expansion process, the picture is divided into 5 segments. For

each of these segments the increment value for the expansion factor can be defined

separately.

Visualization of panorama segments

Each end of a segment can be defined individually in a granularity of two output pixels.

For every segment an increment value can be defined (HINC0...HINC4) which indicates

the amount of decimation/expansion. One LSB is equivalent to an offset of 0.125 to

HSCPRESC per double pixel. This means that with HINC, HSCPRESC is altered in the

range from -32...31.875 per double pixel.

Display processing

The display processing part contains an integrated triple 9-bit DAC and performs digital

enhancements and manipulations of the digital video component signal. The Figure 5-

32 shows the block diagram of the display processing part.

Peaking

The luminance peaking filter improves the overall frequency response of the luminance

channel. It consists of two filters working in parallel. They have high pass (HP) and band

pass (BP) characteristics. Their gain factors are programmable separately (BCOF,

HCOF). Values greater than 4 peak the signal, whereas values less than 4 attenuate the

signal. The high pass and the band pass filters are equipped with a common coring

algorithm. It is optimized to achieve a smooth display of grey scales, not to improve the

signal-to-noise ratio. Therefore no artifacts are produced. Coring can be switched off

(YCOR). The Figure 5-33 shows the block diagram of the peaking block

Peaking filter: Bandpass and Highpass filter

The peaking filter clock frequency is CLKB36 (36 MHz). The maximum signal frequency

of the picture stored in the memory is 6.75 MHz. Due to a peaking after postscaler, the

frequency range of the peaking filter varies with the expansion factor of the postscaler.

Digital color transition improvement (DCTI)

A new digital algorithm is implemented to improve horizontal transitions of the

chrominance signals resulting in a better picture sharpness. A correction signal

proportional to the slope of the detected horizontal transition of the input signal is added

to the original input signal. Different correction signals are selected according to the

bandwidth of the input signal. The amplitude of the correction signal is adjustable by the

I²C bus parameter ASCENTCTI.

The exact position of a color transition is calculated by detecting the corresponding zero

transition of the second derivative of both chrominance signals. Low pass filtering is

performed to avoid noise sensitivity. The I²C bus parameter THRESHC modifies the

sensitivity of the DCTI circuit. High values of THRESHC result in an improvement only

of significant color transitions. Small color variations remain unchanged.

To eliminate “wrong color” transitions, which are caused by over- and undershoots at the

chroma transition, the sharpened chroma signals are automatically limited to a proper

value.

Coarse and fine delay

Before digital-to-analog conversion an adjustment of the phase of the luminance is

performed. A coarse delay from -8 to +7 in steps of 1 pixel CLKB36 (~28 ns) are possible

(COARSEDEL). FINEDEL shifts the luminance one CLKB72 (~14 ns) pixel. This can be

used to compensate delays, when Y and UV are externally processed differently (e.g.

lowpass filtered).

Oversampling and DAC

After conversion into 8:8:8 format (CLKB72=72MHz), three 9-bit digital-to-analog

converters are used for analog YUV output. This twofold-oversampling generates 1920

active pixels per line (when using recommended settings) and simplifies the external

postfiltering. Output voltage is determined by PKLY, PKLU and PKLV in a range of 0.4

...1.9 V (fullscale).

DAC output signals

8 bits of the luminance D/A converter are used for the entire signal. The 9th bit is used

for over- and undershoots caused by the peaking to prevent or reduce clipping artifacts.

As the CTI block seldomly produces such overshoots, a full-scale operation can be

activated by CHROMAMP.

Output-Sync Controller

The output sync controller generates horizontal and vertical synchronization signals for

the scanrate-converted output signal.

HOUT Generator

The HOUT generator has two operation modes, which can be selected by the parameter

HOUTFR. The HOUT signal is active high for 64 clock cycles (CLKB36). In the

freerunning-mode the HOUT signal is generated depending on the PPLOP parameter.

In the locked-mode the HOUT signal is locked on the incoming H-Sync signal derived

from CVBS. The polarity of the HOUT signal is programmable by the parameter

HOUTPOL.

VOUT Generator

The VOUT generator has two operation modes, which can be selected by the parameter

VOUTFR. In the freerunning-mode (VOUTFR=1) the VOUT signal is generated

depending on the LPFOP parameter.

In the locked-mode the VOUT signal is synchronized by the incoming V-Sync signal

derived from CVBS, delayed by some lines (OPDEL). During one incoming V-Sync

signal, two VOUT pulses have to be generated. The polarity of the VOUT signal is

programmable by the parameter VOUTPOL. The VOUT signal is active high for two

output lines.

Background Generator

This generator is able to realize an automatic closing and opening of the displayed

picture. This means that with every picture the displayed colored background, defined by

UBORDER, VBORDER and YBORDER will get bigger or smaller. The original picture

data will be replaced by the background values and vice versa. There is also the

possibility to realize a fixed border via the I²C bus (BORDPOSH and BORDPOSV). 4096

different colors are available.

BORDPOSH and BORDPOSV also influence the window generation. This means the

automatic opening and closing of the picture will start or end at the position which is

defined with these values. The border is calculated with the following formula: The

horizontal border o

n the left side of the TV screen is 2*BORDPOSH and 2*BORDPOSH

n the left side of the TV screen is 2*BORDPOSH and 2*BORDPOSHon the right side of the TV screen. This means, that 4*BORDPOSH pixels are overwritten

with border values. The same applies to the vertical direction. 4*BORDPOSV lines in

total are overwritten with background values. BORDERV decides whether upper or

lower or both borders are displayed. BORDERH decides whether left or right or both

borders are displayed.

Digital 656 input

The IC decodes a digital 8bit@27MHz data stream according to ITU.BT656 standard.

The input is selected by EN656.

Clock Concept

A single 20.25 MHz crystal at fundamental mode is used as clock reference. All other

clocks are derived from this source. The CVBS frontend works with 20.25 MHz, the RGB

frontend works with 40.5 MHz, the oversampling DACs use 72.0 MHz and the memory

and all parts behind the memory are clocked with 36 MHz.

Three different clock concepts are supported. The difference is the behavior in clocking

the memory output. The frontend part of the SDA 9402 uses a free-running but crystal-

stable clock (CLKF). After deskewing, an orthogonal picture is written into the memory.

The read out is done using the (CLKB) clock.

The horizontal sync-signal output (HOUT) is derived from a counter running with CLKB.

The VOUT is directly derived from the input vertical signal, which is generated by the

sync-separation block. This ’H-freerunning-V-locked mode’ is only possible together with

a DC coupled deflection controller.

In ’H-and-V-locked mode’ CLKB is line-locked to the incoming signal. The freerunning

YUV picture data and the internal H signal are converted to the line-locked domain. Now

HOUT and the sync signal in the 1fH domain are directly coupled.

In case of ’H-and-V-freerunning mode’ the HOUT and VOUT signals are derived from

counters running with CLKB. There is no connection to the incoming signal. This mode

can be used for stable pictures when no signal is applied (e.g. channel search with OSD

insertion).

Clock system

A clock output of 27MHz (50 Hz version:13.5 MHz) is possible (pin 27:clkout). This clock

is 3/4 of CLKB36. HOUT and VOUT are in line with this sampling clock. The clock output

can be disabled by CLKOUTON. Additionally a 20.25 MHz clock can be output to pin 74

(656hin/clkf20) to supply other ICs (e.g. PiP) with the same clock (CLKF2PAD). When

enabled, 656-input with separate H/V-sync is not possible. For 656-output operation,

CLKB36 is given to pin 9 (656clk).

Linelocked clock generation

Linelocked horizontal sync pulses are generated by a digital phase locked loop. The time

constant can be adjusted between fast and s

low behavior in eight steps (TICO) to

low behavior in eight steps (TICO) toaccommodate different input sources (e.g. VCR). Noisy input signals become more

stable when a noise-reduction is enabled (HSWIN). The PLL control can be frozen up to

15 lines before v-sync (FION) for a duration up to 15 lines (FILE). This may be used to

reduce disturbances by h-phase errors which are produced by VCR’s. Because of the

delay between read and write pointer of field memory (Figure 5-31), the incoming 50Hz

v-sync lies in the active picture area.

The output frequency for the 100/120 Hz version dependent on IICINCR is

The value is internally divided by two for the 50/60 Hz version.

I²C bus clock domains

The registers themselves are grouped in an I²C bus interface block, one in each domain.

The transmitted data is received by the I²C bus kernel. The I²C bus kernel itself is located

in the CP domain. This means that the working frequency is 20.25 MHz. The data is

transmitted to the I²C bus interface blocks via an internal serial bus.

For the write process, the I²C bus master has to write a ’don’t care’ byte to the

subaddress FFh (store command) to make the register values available to the four I²C

bus interface blocks (except for the not-take-over registers).

In order to have a defined time step for the several blocks in the different domains, where the data will be available from the I²C bus interface blocks, the data are made valid with internal V-sync related

signals (rising

edge), depending on the different clock domains. The subaddresses,

edge), depending on the different clock domains. The subaddresses,where the data are made valid with the V-sync signal of the 20.25 MHz domain are

indicated in the overview of the subaddresses with „V20“, the others are called “V40”,

“V36F” and “V36B”, respectively. The I²C parameter V20STAT, V40STAT and

V36BSTAT reflect the state of the register values. If these bits are read as ’1’, then the

store command was sent, but the data is not made available yet. If these bits are ’0’ then

the data was made valid and a new write or read cycle can start. The bits V20STAT,

V40STAT and V36BSTAT may be checked before writing or reading new data,

otherwise data can be lost by overwriting. No V36FSTAT register exist. To make the

register values available to the four I²C bus interface immediately after sending, the I²C

bus master has to write a ’don’t care’ byte to the subaddress FEh (store command).

I²C bus clock domains

For the read process, the I²C bus master must not send a store command. In order to

have a defined time step for the I²C bus interface blocks in the different domains, where

the data will be available from the different blocks, the data is made valid with the same

V-Sync related signals mentioned above for the write process. The SDA 9402

distinguishes between two different types of read-registers. The behavior of the “normal”

read registers does not differ from the behavior of the write registers.Only the direction

of the data flow is opposite. The “rs typ” read registers behave differently. They can be

only set (means value 1) by the internal blocks using the rising edge of a corresponding

signal. After reading by the I²C bus master, the registers will be automatically reset

(means value 0) by the I²C bus kernel/interface.

For example the register NMSTATUSbelongs to the “rs typ” read registers. NMSTATUS signalizes a new value for NOISEME. So if NMSTATUS is read as ’0’ the current noise measurement has not been updated.

If the NMSTATUS is read as ’1’ a new noise measurement value can be read. All other

“rs typ” read registers work in the same way. The “rs typ” read registers will be marked

in the overview with the short cut “rstyp” or will have the additional hint “Note: reset

automatically when read/write” in the detailed I²C bus command description.

By default all registers are made valid by the internal V-Sync related signals and, in

addition, a store command has to be sent for write registers. The registers, which should

also be made available immediately as for writing and reading, are marked with the short

cut NTO (No take over mechanism).

Registers which need a hand-shake mechanism between the I²C bus interface and the

different blocks are marked with the shortcut HS (Hand shake mechanism). This means

that all bits of the registers are used when the last register is written. After PPLIP9-2 is

written, PPLIP1-0 must be written to allow these bits to have effect.

The registers for the write parameter STOPMODE are directly connected to the read

registers of the parameter SMMIRROR. So it is possible to check the I²C bus protocol by

writing and reading to the register STOPMODE and SMMIRROR, respectively.

The transmitted data is internally stored in registers. Writing to or reading from a non -

existant register is permitted and does n

ot generate a fault by the IC.

ot generate a fault by the IC.After switching on the IC, all bits of the SDA 9402 are set to defined states, (refer to

Table 6- 2). POR is set after reset to pin 24. It stays ’1’, until it is cancled via software

PORCNCL. This can be used to decide during TV operation, whether to program all

registers (e.g. after power failure reset) or only altered ones (normal TV operation).

SDA 9380 EDDC Enhanced Deflection Controller and RGB Processor,

General description

The SDA 9380

is a highly integrated deflection controller and RGB video processor for CTV receiv-

is a highly integrated deflection controller and RGB video processor for CTV receiv-ers with 15 to 19kHz or 31 to 38kHz line frequencies. The deflection component controls among oth-

ers an horizontal driver circuit for a flyback line output stage, a DC coupled vertical saw-tooth output

stage and an East-West raster correction circuit. All adjustable output parameters are I²C-Bus con-

trolled. Inputs are HSYNC and VSYNC. The HSYNC signal is the reference for the internal clock

system which includes the=χΝ=and χΟ=control loops.

The RGB processor has two YUV/RGB inputs and one RGB input. One YUV/RGB input and the

RGB input are for SVGA and text/OSD with fast blanking. The RGB output stage has two control

loops for cut off and white level with halt capability in vertical shrink modes. An overall Y output and

an adjustable delay of the RGB outputs related to this signal are suitable for a scan velocity modula-

tion circuit.

The supply voltages of the IC are 3.3V and 8V. It is mounted in a P-MQFP package with 64 pins.

Features

Deflection

=No external clock needed

=χΝ=PLL and=χΟ=PLL on chip

= =Standard line frequencies for NTSC and PAL

= =18.75kHz line frequency for 625 lines/60 Hz

= =Doubled line frequencies for NTSC and PAL, MUSE standard, DTV standard

Also suitable for VGA, Macintosh (35kHz) and SVGA standard (38kHz, 800*600*60Hz)

=Automatic switching between 31, 35 and 38kHz in Monitor mode with 2 digital outputs for

controlling B+ and 1 analog input to keep watch on it

=I²C-Bus alignment of all deflection parameters

=All EW-, V- and H- functions

=Picture width and picture height EHT compensation

=Dynamic PH EHT compensation (white bar)

=Compensation of H-phase deviation (e.g. caused by white bar)

=Upper/lower EW-corner correction separately adjustable

=Extreme EW-corner correction (coefficient of sixth order) for super flat tubes

=V-angle and V-bow correction

=Two special control items for vertical zoom/shrink and scroll function with absolutely

correct tracking of the E/W and HD-output signals

=No re-adjustment of E/W after changing vertical S-correction and linearity needed

=H-frequent PWM output signal for generating an adjustable vertical frequent parabola or

a constant pulse width, selectable by I²C

=H- and V-blanking time adjustable

=Partial overscan adjustable to hide the cut off control measuring lines in the reduced

scan modes

=Self adaptation of V-frequency / number of lines per field between 192 and 680 for

each possible line frequency

=Selectable Black Switch-Off behaviour via I²C-Bus.

Protection against EHT run away (X-rays protection)

• =Protection against missing V-deflection (CRT-protection)

• =D/A ouput with 8 bit resolution for general purpose

• =Digital output for general purpose, controlled by I2C-Bus

• =Selectable softstart of the H-output stage

RGB Video

• Two universal YUV/RGB inputs and one RGB input, one YUV/RGB and RGB input with

fast blanking capability

• One fast blank input with contrast reduction capability

• Switchable color difference matrix for PAL/SECAM, NTSC(U.S.), NTSC(Japan) and

HDTV

• Common saturation, brightness and contrast control for all three input channels possible

• Cut off and white level control loop

• Halt command for white level control loop to switch off the white level reference lines in

vertical shrink mode

• Black stretching of non-standard input signals

• Selectable blue stretch circuit shifting white towards light blue

• Peak drive limiter with soft clipping, adjustable per I²C

• Average beam current limiter, adjustable per I²C

• Luminance output signal SVM for scan velocity modulation; adjustable delay from SVM to

the RGB outputs.

System description

5.1

Functional description

5.1.1 Deflection controller

The main input signals are H

SYNC with a frequency range of about 31 to 38kHz and VSYNC with

SYNC with a frequency range of about 31 to 38kHz and VSYNC withvertical frequencies of 50 to 120 Hz. When connecting pin FH1_2 with Low level a line frequency of

15 to 19kHz is suitable.

For displaying computer signals horizontal frequencies up to 38 kHz can be processed.

In the selectable Monitor mode the adaptation to the input frequency in the range of 31.25 to 38kHz

is done automatically. Two output pins (H35K and H38K) for controlling e.g. the supply voltage of the

line output stage indicate the frequency of HSYNC. When the H-frequency is increasing, these out-

puts are stable until the frequency of HSYNC appears on the output HD (see 11.1). In case of

decreasing H-frequency they are changed immediately to flag the new detected frequency but

change of the PLL frequency will be not allowed until the supply voltage of the H-output stage (B+)

is decreased. Pin HSAFE is used to watch B+.

The output signals control the horizontal as well as the vertical deflection stages and the East-West

raster correction circuit.

The H-output signal HD (open drain output) compensates the delays of the line output stage and its

phase can be modulated vertical frequent to remove horizontal distortions of vertical raster lines (V-

Bow, V-Angle). Time reference is the middle of the front and back edge of the line flyback pulse. A

positive HD pulse switches off the line output transistor. Maximal H-shift is about 2.25 µsec for

fH=31kHz.

Picture tubes with 4:3 or 16:9 aspect ratio can be used by adapting the raster to the aspect ratio of

the source signal.

The V-output saw-tooth signals VD- and VD+ controls a DC coupled output stage and can be dis-

abled. Suitable blanking signals are delivered by the IC.

The East-West output signal E/W is a vertical frequent parabola of 6th order, enabling an extreme

corner correction for super flat tubes. T

he common corner correction realised with coefficients of

he common corner correction realised with coefficients offourth order, is separately adjustable for the upper and lower part of the screen.

The pulse width modulated horizontal frequent output signal PWM has two options. A vertical fre-

quent parabolic function or a constant pulse width in each line, selectable by I²C, is available. After

external integration the parabola may be used for vertical dynamic focusing rsp. the DC voltage for

adjustment of H-offset or rotation.

The output D/A delivers a variable DC signal and an I2C Bus controlled digital output is available for

general purpose.

The picture width and picture height compensation (PW/PH Comp) processes the beam current

dependent input signal IBEAM with effect to the outputs E/W and VD to keep width and height con-

stant and independent of brightness.

The alignment parameter AFC EHT Compensation enables to adjust the influence of the input sig-

nal IBEAM on the horizontal phase.

The selectable start up circuit controls the energy supply of the H-output stage during the receiver's

run up time by smooth decreasing the line output transistors switching frequency down to the nor-

mal operating value (softstart). HD starts with about 1.7 times the line frequency and converges within 85ms to its final value. The high time is kept constant. The normal operating pulse ratio H/L is

either 45/55 or 40/60 (selectable by I²C). A watch dog function limits an increasing of the HD period

to max. +10%.

The implemented Black Switch-Off behaviour is defined by two I2C bits (BSO1, BSO0). When

enabled the signal at BSOIN (e.g. the supply voltage of the line output stage) is watched. If its level

does not come up to a defined threshold Black Swich-Off is started (see 11.2). At first the RGB out-

puts are switched to continuous blanking immediately and the vertical output signals are changed to

about 115..120% overs

can. After a delay of 42 lines the picture tube capacitance is discharged with

can. After a delay of 42 lines the picture tube capacitance is discharged witha current of some mA. From now the vertical overscan rate is calculated depending on the actual

voltage at BSOIN to get the desired deflection angle. Three relations are selectable by I2C. After the

voltage at BSOIN is dropped down to about 20% of its initial value the output HD and the overscan

calculation may stop.

The protection circuit watches an EHT reference and the saw-tooth of the vertical output stage. If

the EHT succeeds a defined threshold or if the V-deflection fails (refer to 11.5) the related bit is set in

the status byte and the output PROTON goes High. The output HD is deactivated (H-level) immedi-

ately independent of the selected Black Switch-Off function.

HPROT:

input

Vi < V2

continuous blanking

Vi > V1

HD disabled

V2 ≤=Vi < V1

operating range

VPROT:

vertical saw-tooth voltage

Vi < V1 in first half of V-period

or Vi > V2 in second half : HD disabled

The pin SCP delivers the composite blanking signal SCP. It contains burst (Vb), H-blanking HBL

(VHBL) and selectable V-blanking (control bit SSC). The phase and width of the H-blanking period

can be varied by I2C-Bus. For the timing following settings are possible :

BD = 1

: TBL = 0

BD = 0, BSE = 0 (default value)

: THBL = tf (H-flyback time)

BD = 0, BSE = 1(alignment range)

: THBL = (4 * H_blanking-time + 1) / CLL

: TDBL = (H_shift + 4 * H_blanking_phase

- 2*H_blanking_time + 45) / CLL

SSC = 0

: TBL = TVBL during V-blanking period

SSC = 1

: TBL is always THBL

RGB processing

To provide an accurate biasing of the picture tube the offsets and gains of the RGB output stages

are continuously adjusted by a cut off and white level control loop. Leakage, cut off and white current

are measured each frame during vertical flyback at the DCI input. The position of the measurement

lines is adjustable by IIC bus (see page 31). The reference currents for the cut off and white levels

are adjusted by IIC bus with a 6 bit parameter for each output and a common 3 bit gain parameter.

Because the video amplifiers are part of the control loops, the overall gain and offset is no more

adjustable in this stage. For proper dimensioning of the video amplifiers there is an IIC status bit

(CLOW), which is 0 when all offset and gain actuators of the RGB outputs are within 50% of its full

range. The control loops can be switched to halt mode to switch off the measurement lines in verti-

cal shrink mode. When the TV screen is switched on brightness and contrast ramp up in a soft start

mode as soon as the cut off control loop is locked.

There are three circuits implemented for beam current limiting:

-First there is a circuit for accurate average beam current limiting. The beam current is measured at

the Ibeam input and limited by reducing first contrast and, after half contrast is reached, brightness

too. All parameters (limit value,

gain, up time constant and down time constant) are adjustable by IIC

gain, up time constant and down time constant) are adjustable by IICbus.

-Second a peak drive limiter circuit is implemented for the higher frequency content of the video sig-

nal. It reduces contrast when a limit value is exceeded by the R, G or B video signals. Also all

parameters (limit value, up time constant and down time constant) are adjustable by IIC bus.

-Third there is a soft clipper for the very high frequency content of the video signal. It limits the R, G

or B video signals according to the diagram at 11.7. Limit value and slope are adjustable by IIC bus.

The TV screen can be switched to blue by IIC bus when no video signal is available.

When the blue stretch function is activated by IIC bus, the gain of the red and green output is

reduced by 17% for amplitudes more than 80% of the nominal amplitude. This shifts white towards

light blue.

A black stretch function (switchable by IIC bus) stretches video signals with a black level which is

higher than the clamping level towards black. Therefore the peak dark value of the video signal is

stored. The height of the peak dark value determines the amount of stretch (diagram at 11.6). The

screen area in which the peak dark detector is enabled is programmable by IIC bus. So it is possible

to screen black borders of the picture (e.g. letter box format) which otherwise prevent the desired

function of black stretch.

An overall luminance output is provided for supplying a circuit for scan velocity modulation. The

delay of the RGB outputs to the luminance output is adjustable by IIC bus. So a proper alignment of

the video signals and the current in the SVM coil is possible.

Circuit description

The HSYNC is reference for a numeric PLL. This PLL generates a clock which is phase locked to

the incoming horizontal sync pulse and exactly 864 times faster than the horizontal frequency. The

polarity of the external horizontal sync pulses may be positive (see figure below) or negative. In

case of negative polarity the incoming HSYNC signal is automatically inverted for an easier applica-

tion in VGA or SVGA mode.

Incoming signal HSYNC (internal clock)

Pulse width tw for I2C-bus Bit ’HSWMI’=0:

1.5 µs ... 4.5µs (High or Low level)

FH1_2 = High

3.0 µs ... 9.0µs (High or Low level)

FH1_2 = Low

Pulse width tw for I2C-bus Bit ’HSWMI’=1:

0.8 µs ... 4.5µs (High or Low level)

FH1_2 = High

1.7 µs ... 9.0µs (High or Low level)

FH1_2 = Low

(The specified pulse width depends on the I²C-bus bits INCR4...INCR0 rsp. PLL clock frequency.

The above values are valid for INCR = 6. For higher INCR values the allowed pulse width is

decreasing proportional to the increasing PLL clock frequency.)

The described input signal is first applied to an A/D converter. Conversion takes place with 7 bits

and a nominal frequency of 27 MHz. The digital PLL uses a low pass filter to obtaine defined slopes

for further measurements (PAL/NTSC applications). In addition the actual high and low level of the

signal as well as a threshold value is evaluated and used to calculate the phase error between inter-

nal clock and external horizontal sync pulse. By means of digital PI filtering an increment is gained

from this. The PI filter can be set by the I2C-bus VCR bit so that the lock-in behaviour of the PLL is

optimal in relation to either the TV or VCR mode. Moreover it is possible to adapt the nominal fre-

quency by means of 5 I2C-bus bits (INCR4..INCR0) to different horizontal frequencies. An additional

bus bit GENMOD offers the possibility to use the PLL as a frequency generator which frequency is

controlled by the INCR bits.

Once an increment has been obtained, either from the PI-filter or the I2C-bus, it can be used to

operate the Digital Timing Oscillator. The DTO generates a saw-tooth with a frequency that is pro-

portional to the increment. The saw-tooth is converted into a sinusoidal clock signal by means of sin

ROM’s and D/A converters and applied to an analog PLL which multiplies the frequency by 4 (for

detailed explanation see pinning and I2C-bus description) and minimizes residual jitter. In this man-

ner the required line locked clock is provided to operate the other functional parts of the circuit. If no

HSYNC is applied to pin 18 the system holds its momentary frequency for 2040 lines and following

resets the PLL to its nominal frequency. The status bit CON indicates the lock state of the PLL.

The system also provides a stable HS-pulse for internal use. The phase between this internal pulse

and the external HSYNC is adjustable via I2C bus bits HPHASE. It can be shifted over the range of

one TV line.

An external clock (CLKI) can be provided by pin selection (CLEXT = H) or I²C control (SCLIIC = H,

CLEXTIIC = H). This is recommended when using the SDA 9380 with a scan rate conversion sys-

tem. The clock frequency has to be 864 · fHSYNC. The external clock mode can not be used with

18.75, 33.75kHz, 35kHz and 38kHz line frequency. Therefore switching to external clock mode is

only possible when INCR = 6, but always allowed during operating without any danger for the H-out-

put stage.

The input signal at VSYNC is the vertical time reference. It has to pass a window avoiding too short

or long V-periods in the case of distorted or missing VSYNC pulses. The window allows a VSYNC

pulse only after a minimum number of lines from its predecessor and sets an artificial one after a

maximum number of lines. The window size is programmable by I2C-bus.

Values which influence shape and amplitude of the output signals are transmitted as reduced binary

values to the SDA 9380 via I²C bus. A CPU which is designed for speed reasons in a pipe line struc-

ture calculates in consideration of feedback signals (e.g. IBEAM) values which exactly represent the

output signals. These values control after D/A conversion the external deflection and raster correc-

tion circuits.

The CPU firmware is stored in an internal ROM.

Explanation of some control items

Explanation of some control itemsVertical aspect,

Two special control items are implemented for the user to adjust the

Vertical scroll:

vertical height (control item: Vertical aspect) and the vertical position

(Vertical scroll). These items may be stored for every display mode to

get an individual height and position if desired. Changing these para-

meters automatically influences the outputs VD+, VD-, E/W, HD in such

a way that absolutely no raster distortion happens. There is no need

for the user to re-adjust any geometry parameter.

The difference of the function of Vertical size and Vertical aspect is

the following: Varying Vertical size causes a linear stretching of the

saw-tooth to eliminate the tolerance of linear components (e.g. feed-

back resistor). But adjusting Vertical aspect takes into consideration

that more or less picture height needs very more or less S-correction

(no linear relation). Therefore Vertical aspect should be used for chang-

ing the aspect ratio (e.g. 16:9 source on 4:3 CRT) or if an individual

picture height is desired for the various PC graphic standards. Vertical

aspect = -128(minimum value) results in a vertical reduction to 37.5%.

Vertical size,

The purpose of these control parameters is the alignment in the factory

Vertical shift:

and service to adapt the output signals VD+, VD- to the picture tube and

to eliminate tolerances of the hardware and deflection yoke. Only one

set of these parameters is required for all display modes.

Vertical linearity,

Changing the vertical linearity and S-correction has no influence on the

Vertical S-correction: E/W-geometry. That means, straight vertical lines remain straight. The

output signals E/W and HD are automatically changed so no re-adjust-

ment of the related control items is needed. This feature saves time for

adjustment of the so called ’smart’ mode (4:3 source on 16:9 CRT)

Guard band:

This control item is useful for optimizing self adaptation. Video signals

with different number

of lines in consecutive fields (e.g. VCR search

of lines in consecutive fields (e.g. VCR searchmode) must not start the procedure of self adaptation. But switching

between different TV standards has to change the slope of the vertical

saw-tooth getting always the same amplitude (self adaptation). To avoid

problems with flicker free TV systems which have alternating number of

lines per field an average value of four consecutive fields is calculated. If

the deviation of these average values (e.g. PAL : 312.5 lines or 625 half

lines) is less or equals Guard band, no adaptation takes place. When it

exceeds Guard band, the vertical slope will be changed.

Vertical EHT comp.:

This item controls the influence of the beam current dependent input

signal IBEAM on the outputs VD+ and VD-

SDA 6000 Teletext Decoder with Embedded 16-bit Controller M2 HIGHGRAPHICS.

M2 is a 16-bit controller based on Infineon’s C16x core with embedded teletext and

graphic controller functions. M2 can be used for a wide range of TV and OSD

applications.

Overview

M2 is designed to provide absolute top performance for a wide spectrum of teletext and

graphic applications in standard and high end TV-sets and VCRs. M2 contains a data

caption unit, a display unit and a high performance Infineon C16x based microcontroller

(so that M2 becomes a one chip TV-controller) an up to level 3.5 teletext decoder and

display processor with enhanced graphic accelerator capabilities. It is not only optimized

for teletext usage but also, due to its extremely efficient architecture, can be used as a

universal graphic engine.

M2 is able to support a wide range of standards like PAL, NTSC or applications like

Teletext, VPS, WSS, Chinatext, Closed Caption and EPG (Electronic Program Guide).

With the support of a huge number of variable character sets and graphic capabilities a

wide range of OSD applications are also open for M2.

A new flexible data caption system enables M2 to slice most data, making the IC an

universal data decoder. The digital slicer concept contains measurement circuitries that

help identify bad signal conditions and therefore support the automatic compensation of

the most common signal disturbances. M2’s enhanced data caption control logic allows

individual programming, which means that every line can carry an individual service to

be sliced and stored in the memory.

The display generation of M2 is based on frame buffer technology. A frame buffer

concept displays information which is individually stored for each pixel, allowing greater

flexibility with screen menus. Proportional fonts, asian characters and even HTML

browsers are just some examples of applications that can now be supported.

Thus, with the M2, the process of generation and display of on-screen graphics is split

up into two independent tasks. The generation of the image in the frame buffer is

supported by a hardware graphics accelerator which frees the CPU from power intensive

address calculations. The graphics accelerator ‘prints’ the characters, at the desired