The CHASSIS 618 A-2 PIP (ICC5341) is the most advanced version of the Thomson CHASSIS ICC5.

It 's coded ICC5341 and was introducing the IMC (Interactive menu control) feature on the chassis base.

It's full multistandard even in the PIP Unit.

It's complex and sophisticated all way.

As any ICC5 it have had a high rate of failure due to dry joints all around the chassis.

When they're fully reworked they give almost never a problem after.

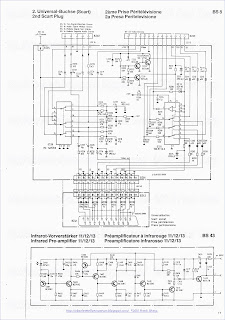

TELEFUNKEN PALCOLOR HIFI 292 PIP "MILLENNIUM" CHASSIS 618 A-2 PIP (ICC5341) CIRCUIT DESCRIPTIONS:

TELEFUNKEN PALCOLOR HIFI 292 PIP "MILLENNIUM" CHASSIS 618 A-2 PIP (ICC5341)COLOR TV SCANNING AND POWER SUPPLY PROCESSOR TEA2029C

DESCRIPTION

The TEA2029C is a complete (horizontal and vertical)

deflection process

or with secondary to primary

or with secondary to primarySMPS control for color TV sets.

DEFLECTION .CERAMIC 500kHz RESONATOR FREQUENCY

REFERENCE .NO LINE AND FRAME OSCILLATOR ADJUSTMENT

.DUAL PLL FOR LINE DEFLECTION .HIGH PERFORMANCE SYNCHRONIZATION .SUPER SANDCASTLE OUTPUT .VIDEO IDENTIFICATION CIRCUIT .AUTOMATIC 50/60Hz STANDARD IDENTIFICATION

.EXCELLENT INTERLACING CONTROL .SPECIALPATENTED FRAME SYNCHRO DEVICE

FOR VCR OPERATION .FRAME SAW-TOOTH GENERATOR .FRAME PHASE MODULATOR FOR THYRISTOR

SMPS CONTROL .ERROR AMPLIFIER AND PHASE MODULATOR

.SYNCHRONIZATION WITH HORIZONTAL

DEFLECTION .SECURITY CIRCUIT AND START UP PROCESSOR.

GENERAL DESCRIPTION

This integrated circuit uses I2L bipolar technology

and combines analog signal processing with digital

processing.

Timing signals are obtainedfrom a voltage-controlled

oscillator (VCO) operatingat 500KHzby means

of a cheap ceramic resonator. This avoids the

frequency adjustment normally required with line

and frame oscillators.

A chain of dividers and appropriate logic circuitry

produce very accurately defined sampling pulses

and the necessary timing signals.

The principal functions implemented are :

- Horizontal scanning processor.

- Frame scanning processor. Two applications are

possible :

- D Class : Power stage using an external

thyristor.

- B Class : Powerstageusing an externalpower

amplifier with fly-back generator

such as the TDA8170.

- Secondary switch mode power regulation.

The SMPS output synchronize a primary I.C.

(TEA2260/61)at the mains part.

This concept allows ACTIVE STANDBY facilities.

- Dual phase-locked loop horizontal scanning.

- High performance frameand line synchronization

with interlacing control.

- Video identification circuit.

- Super sandcastle.

- AGC key pulse output.

- Automatic 50-60Hz standard identification.

- VCR input for PLL time constant and frame synchro

switching.

- Frame saw-tooth generator and phase modulator.

- Switchingmode regulated power supplycomprising

error amplifier and phase modulator.

- Security circuit and start-up processor.

- 500kHzVCO

The circuit is supplied in a 28 pin DIP case.

VCC = 12V.

Synchronization Separator

Line synchronization separator is clamped to

Line synchronization separator is clamped toblack level of input video signal with synchronization

pulse bottom level measurement.

The synchronization pulses are divided centrally

between the black level and the synchronization

pulse bottom level, to improve performance on

video signals in noise conditions.

Frame Synchronization

Frame synchronization is fully integrated (no external

capacitor required).

The frame timing identification logic permits automatic

adaptation to 50 - 60Hz standards or non-interlaced

video.

An automatic synchronization window width system

provides :

- fast frame capture (6.7ms wide window),

- good noise immunity (0.4ms narrow window).

The internal generator starts the discharge of the

saw-tooth generator capacitor so that it is not disturbed

by line fly back effects.

Thanks to the logic control, the beginning of the

charge phase does not depend on any disturbing

effect of the line fly-back.

A 32ms timing is automatically applied on standardized

transmissions, for perfect interlacing.

In VCR mode, the discharge time is controlled by

an internal monostable independent of the line

frequency and gives a direct frame synchronization.

Horizontal Scanning

The horizontalscanningfrequencyis obtainedfrom

the 500kHz VCO.

The circuit uses two phase-locked loops (PLL) :

the first one controls the frequency, the second one

controls the relative phase of the synchronization

and line fly-back signals.

The frequency PLL has two switched time constants

to provide :

- capture with a short time constant,

- good noise immunity after capture with a long

time constant.

The output pulse has a constant duration of 26ms,

indepe

ndent of VCC and any delay in switching off

ndent of VCC and any delay in switching offthe scanning transistor.

Video Identification

The horizontal synchronization signal is sampled

by a 2ms pulse within the synchronization pulse.

The signal is integrated by an external capacitor.

The identification function provides three different

levels :

- 0V : no video identification

- 6V : 60Hz video identification

- 12V : 50Hz video identification

This information may be used for timing research

in the case of frequency or voltage synthetizer type

receivers, and for audio muting.

Super Sandcastle with 3 levels : burst, line flyback,

frame blanking

In the event of vertical scanning failure, the frame

blanking level goes high to protect the tube.

Frame blanking time (start with reset of Frame

divider) is 24 lines.

VCR Input

This provides for continuous use of the short time

constant of the first phase-locked loop (frequency).

In VCR mode, the frame synchronization window widens out to a search window and there is no

delay of frame fly-back (direct synchronization).

Frame Scanning

FRAME SAW-TOOTH GENERATOR. The current

to charge the capacitoris automatically switched to

60Hz operation to maintain constant amplitude.

FRAME PHASE MODULATOR (WITH TWO DIFFERENTIAL

INPUTS). The output signal is a pulse

at the line frequency, pulse width modulatedby the

voltage at the differential pre-amplifier input.

This signal is used to control a thyristor which

provides the scanning current to the yoke. The

saw-tooth output is a low impedance,however, and

can therefore be used in class B operation with a

power amplifier circuit.

Switch Mode Power Supply (SMPS) Secondary

to Primary Regulation

This power supply uses a differential error amplifier

with an internal reference voltage of 1.26V and a

phase modulator operating at the line frequency.

The powertransistor is turnedoff bythe falling edge

of the horizontal saw-tooth.

The ”soft start” device imposes a very small conduction

angle on starting up, this angle progressively

increases to its nominal regulation value.

The maximum conductionangle may be monitored

by forcing a voltage on pin 15. This pin may also

be used for current limitation.

The outputpulse is sent to the primaryS.M.P.S. I.C.

(TEA2261) via a low cost synchro transformer.

Security Circuit and Start Up Processor

When the security input (pin 28) is at a voltage

exceeding 1.26V the three outputs are simultaneously

cut off until this voltagedrops below the 1.26V

threshold again. In this case the switch mode

power supply is restarted by the ”soft start” system.

If this cycle is repeated three times, the three

outputs are cut off definitively. To reset the safety

logic circuits, VCC must be zero volt.

This circuit eliminates the risk to switch off the TV

receiver in the event of a flash affecting the tube.

On starting up, the horizontal and vertical scanning

functions come into operation at VCC = 6V. The

power supply then comes into operation progressively.

On shutting down, the three functions are interrupted

simultaneously after the first line fly-back.

APPLICATION INFORMATION ON FRAME

SCANNING IN SWITCHED MODE:

Fundamentals (see Figure 80)

The secondary winding of EHT transformer provides

the energy required by frame yoke.

The frame current modulation is achieved by

modulating the horizontal saw-tooth current and

subsequent integration by a ”L.C” network to reject

the horizontal frequency component.

General Description

The basic circuit is the phase comparator ”C1”

which compares the horizontal saw-tooth and the

output voltage of Error Amplifier ”A”.

The comparator output will go ”high” when the

horizontal saw-tooth voltage is higher than the ”A”

output voltage. Thus, the Pin 4 output signal is

switched in synchronization with the horizontal frequency

and the duty cycle is modulated at frame

frequency.

A driver stage delivers the current required by the

external power switch.

The external thyristor provides for energy transfer

between transformer and frame yoke.

The thyristor will conduct during the last portion of

horizontal trace phase and for half of the horizontal

retrace.

The inverse parallel-connected diode ”D” conducts

during the second portion of horizontal retrace and

at the beginning of horizontal trace phase.

Main advantages of this system are :

- Power th

yristor soft ”turn-on”

yristor soft ”turn-on”Once the thyristor has been triggered, the current

gradually rises from 0 to IP, where IP will reach

the maximumvalue at the end of horizontal trace.

The slope current is determined by, the current

available through the secondary winding, the

yoke impedance and the ”L.C.” filter characteristics.

- Power thyristor soft ”turn-off”

The secondary output current begins decreasing

and falls to 0 at the middle of retrace. The thyristor

is thus automatically ”turned-off”.

- Excellent efficiency of power stage dueto very

low ”turn-on” and ”turn-off” switching losses.

Frame Flyback

During flyback, due to the loop time constant, the

frame yoke current cannot be locked onto the

reference saw-tooth. Thus the output of amplifier

”A” will remain high and the thyristor is blocked.

The scanning current will begin flowing through

diode ”D”. As a consequence, the capacitor ”C”

starts charging upto the flyback voltage.The thyristor

is triggeredas soon as the yoke current reaches

the maximum positive value.

TDA4443 MULTISTANDARD VIDEO IF AMPLIFIERDESCRIPTION

The TDA4443 is a Video IF amplifier with standard

switch for multistandard colour or monochromeTV

sets, and VTR’s.

SWITCHING OFF THE IF AMPLIFIER WHEN

OPERATING IN VTR MODE .DEMODULATION OF NEGATIVE OR POSITIVE

IF SIGNALS. THE OUTPUT REMAINS

ON THE SAME POLARITY IN EVERY CASE .IF AGC AUTOMATICALLY ADJUSTED TO

THE ACTUALSTANDARD .TWO AGC POSSIBILITIES FOR B/G MODE :

1. GATED AGC

2. UNGATED AGC ON SYNC. LEVEL AND

CONTROLLED DISCHARGE DEPENDENT

ON THE AVERAGE SIGNAL LEVEL FOR VTR

AND PERI TV APPLICATIONS

FOR STANDARD L : FAST AGC ON PEAK

WHITE BY CONTROLLED DISCHARGE .POSITIVE OR NEGATIVE GATING PULSE .EXTREMELY HIGH INPUT SENSITIVITY .LOW DIFFERENTIAL DISTORTION .CONSTANT INPUT IMPEDANCE .VERY HIGH SUPPLY VOLTAGE REJECTION .FEW EXTERNAL COMPONENTS .LOW IMPEDANCE VIDEO OUTPUT .SMALL TOLERANCES OF THE FIXED VIDEO

SIGNALAMPLITUDE .ADJUSTABLE, DELAYED AGC FOR PNP

TUNERS.

GENERAL DESCRIPTION

This video IF processing circuit integrates the following

functional blocks : .Three symmetrical, very stable, gain controlled

wideband amplifier stages - without feedback

by a quasi-galvanic coupling. .Demodulator controlled by the picture carrier .Video output amplifier with high supply voltage

rejection .Polarity switch for the video output signal .AGC on peak white level .GatedAGC .Discharge control .Delayed tuner AGC .At VTR Reading mode the video output signal

is at ultra white level.

TDA4445A SOUND IF AMPLIFIER

.QUADRATURE INTERCARRIER DEMODULATOR

.VERY HIGH INPUT SENSITIVITY .GOODSIGNALTO NOISE RATIO .FAST AVERAGINGAGC .IF AMPLIFIER CAN BE SWITCHED OFF FOR

VTR MODE .GOODAM SUPPRESSION .OUTPUT SIGNAL STABILIZED AGAINST

SUPPLY VOLTAGE VARIATIONS .VERY FEW EXTERNAL COMPONENTS

DESCRIPTION

TDA4445A:

Sound IF amplifier, with FM processing for quasi

parallel sound system.

TDA4445B:

Sound IF amplifier, with FM processing and AM

demodulator, for multi-standard sound TV appliances.

TDA4445Badditionnal :

Bistandard applications (B/G and L)

No adjustment of the AM demodulator

Low AMdistortion.

GENERAL DESCRIPTION

This circuit includes the following functions : .Three symmetrical and gain controlled wide

band amplifier stages, which are extremely stable

by quasiDC coupling without feedback. .Averaging AGC with discharge control circuit .AGC voltage generator

Quasi parallel sound operation : .High phase accuracy of the carrier signal processing,

independentfrom AM .Linear quadrature demodulator .Sound-IF-amplifier stage with impedance converter

AM-Demodulation (only TDA4445B) : .Carrier controlled demodulator .Audio frequency stage with impedance converter

.Averaging low passAGC.

TELEFUNKEN PALCOLOR HIFI 292 PIP "MILLENNIUM" CHASSIS 618 A-2 PIP (ICC5341) CHASSIS ICC5 Switched mode power supply transformer

A switched mode power supply transformer, particularly for a television receiver, including a primary winding and a secondary winding with the primary winding and the secondary winding each being subdivided into a plurality of respective partial windings. The partial windings of the primary lie in a first group of chambers and the partial windings of the secondary lie in a second group of chambers of a chamber coil body, and the chambers of both groups are nested or interleaved with one another.

1. A switched mode power supply transformer, particularly for a television receiver, comprising in combination:

a primary winding and a secondary winding, with said primary winding being subdivided into three partial windings and said secondary winding being subdivided into two partial windings;

a chamber coil body having a plurality of chambers;

said partial windings of said primary winding being disposed only in a first group of said chambers, and said partial windings of said secondary winding being disposed only in a second group of said chambers, with each of said partial windings being disposed in a respective one of said chambers;

said chambers of said first group being interleaved with said chambers of said second group such th

at they alternate in sequence with said primary partial windings and said secondary partial windings being alternatingly disposed in five successive said chambers, so as to generate the major operating voltage at said secondary winding;

at they alternate in sequence with said primary partial windings and said secondary partial windings being alternatingly disposed in five successive said chambers, so as to generate the major operating voltage at said secondary winding; an additional secondary winding for generating a further operating voltage, said additional secondary winding likewise being subdivided into a plurality of partial windings; and,

said partial windings of said additional secondary winding are disposed only in respective said chambers of said second group below any of said partial windings of said secondary winding.

2. A transformer as defined in claim 1 wherein the total number of said chambers is six.

3. A transformer as defined in claim 1 wherein the width of the narrowest of said chambers is approximately 1 mm.

4. A transformer as defined in claim 1 or 2 wherein the widths of said chambers are different.

5. A transformer as defined in claim 1 or 2 wherein the total width of all of said chambers is only approximately 20 mm, whereby a flat and optimally coupled transformer is realized.

6. A transformer as defined in claim 1 wherein said additional secondary winding provides an operating voltage for a load which has a fluctuating current input.

7. A transformer as defined in claim 1 wherein said partial windings of said additional secondary winding are connected in parallel.

8. A transformer as defined in claim 1 wherein said partial windings of said primary winding are connected in series.

9. A transformer as defined in claim 1 or 8 wherein said partial windings of said secondary winding are connected in series.

10. A transformer as defined

in claim 1 further comprising a plurality of auxiliary primary windings disposed in one chamber of said first group which is disposed in approximately the center of said first group and above the said partial winding of said primary winding disposed in said one chamber of said first group.

in claim 1 further comprising a plurality of auxiliary primary windings disposed in one chamber of said first group which is disposed in approximately the center of said first group and above the said partial winding of said primary winding disposed in said one chamber of said first group. 11. A transformer as defined in claim 1 wherein all of said partial winding disposed in said chambers of both said groups are wound with wire having the same diameter.

12. A switched mode power supply transformer as defined in claim 1 or 10 wherein: said coil body has six of of said chambers; said additional secondary winding is subdivided into three said partial windings; and two of said partial windings of said additional secondary winding are disposed below respective ones of said partial windings of said secondary winding and the third said partial winding of said additional secondary winding is disposed in the sixth said chamber.

13. A switched mode power supply transformer as defined in claim 10 further comprising at least one further secondary winding disposed in one of said chambers of said second group above any partial secondary winding present in said one of said chambers.

14. A switched mode power supply transformer, particularly for a television receiver, comprising in combination:

a primary winding and a secondary winding, with said primary winding and said secondary winding each being subdivided into a plurality of partial windings;

a chamber coil body having a plurality of chambers;

said partial windings of said primary winding being disposed only in a first group of said chambers, and said partial windings of said secondary winding being disposed only in a second group of said chambers with each of said partial windings being disposed in a respective one of said chambers;

said chambers of said first group being interleaved with said chambers of said second group such that said primary partial windings and said secondary partial windings are alternatingly disposed in successive said chambers, so as to generate the major operating voltage at said secondary winding;

an additional secondary winding for generating a further operating voltage, said additional secondary winding likewise being subdivided into a plurality of partial windings, and said partial windings of said additional secondary winding are disposed only in respective said chambers of said second group below any of said partial windings of said secondary winding.

15. A switched mode powe

r supply transformer as defined in claim 1 or 14 wherein each of said partial windings of said primary winding contains the same number of turns and each of said partial windings of said secondary winding contains the same number of turns.

r supply transformer as defined in claim 1 or 14 wherein each of said partial windings of said primary winding contains the same number of turns and each of said partial windings of said secondary winding contains the same number of turns. The present invention relates to a switched mode power supply transformer, particularly for a television receiver.

In communications transmissions devices, particularly in television receivers, it is known to effect the desired dc decoupling from the mains by means of so-called switched mode power supply transformers. Such switched mode power supply transformers are substantially smaller and lighter in weight than a mains transformer for the same power operating at 50 Hz, because they operate at a significantly higher frequency of about 20-30 kHz. Such a switched mode power supply transformer (hereinafter calle

d SMPS transformer) generally includes a primary side with a primary winding serving as the operating winding for the switch and further additional auxiliary windings, as well as a secondary side with a secondary winding for generating the essential operating voltage and possibly further additional windings for generating further operating voltages of different magnitude and polarity. The secondary and primary are insulated from one another as prescribed by VDE and have the necessary dielectric strength so that there is no danger of contact between voltage carrying parts on the secondary. A switched mode power supply (SMPS) circuit for a tv-receiver is described in U.S. Pat. No. 3,967,182, issued June 29, 1976.

d SMPS transformer) generally includes a primary side with a primary winding serving as the operating winding for the switch and further additional auxiliary windings, as well as a secondary side with a secondary winding for generating the essential operating voltage and possibly further additional windings for generating further operating voltages of different magnitude and polarity. The secondary and primary are insulated from one another as prescribed by VDE and have the necessary dielectric strength so that there is no danger of contact between voltage carrying parts on the secondary. A switched mode power supply (SMPS) circuit for a tv-receiver is described in U.S. Pat. No. 3,967,182, issued June 29, 1976. A further requirement placed on such an SMPS transformer is that the stray inductance at least of the primary winding and of the secondary winding should be as small as possible. With too high a stray inductance, a transient behavior may develop during the switching operation which would not assure optimum switch operation of the switching transistor connected to the primary winding and would endanger this transistor by taking on too much power. Moreover, an increased stray inductance undesirably increases the internal resistance of the voltage sources for the individual operating voltages.

It is known to design the windings for such transformers as layered windings. Such layered windings, however, contain feathered intermediate foil layers and, after manufacture, generally require that the coil or the complete transformer be encased in order to insure VDE safety. Use as a chamber winding in television receivers presently does not take place because of the problems to be discussed below. A chamber winding would have the particular advantage that it could be wound more easily and economically by automatic machines. when using a chamber winding for a switched mode power supply, the detailed insulation between the primary and the secondary would be realized initially by two chambers with one of these chambers being filled only with the windings of the primary and the other of these chambers being filled only with the windings of the secondary. However, with such an arrangement there would exist only slight coupling between the primary and the secondary and thus an undesirably high stray inductance. If, on the other hand, the number of chambers were selected to be substantially larger,

the transformer becomes more expensive and unnecessarily large. Moreover, a larger core would be required. Consequently, in the past, no television receiver has been introduced that included an SMPS transformer.

the transformer becomes more expensive and unnecessarily large. Moreover, a larger core would be required. Consequently, in the past, no television receiver has been introduced that included an SMPS transformer. SUMMARY OF THE INVENTION

It is the object of the present invention to provide an SMPS transformer designed in the chamber wound technique which permits economical automatic winding, i.e. can be wound with but a single type of wire, has a structure which is spatially narrow and as flat as possible, provides the required insulation between the primary and secondary windings, and has a low stray inductance. The transformer should not be encased or saturated and nevertheless should produce no interfering noise during operation. The transformer should be able to be held in a circuit board without mechanical aids merely by its connecting terminals which are soldered to the circuit board.

The above object is basically achieved according to the present invention in that the transformer for a switched mode power supply, particularly for a television receiver, comprises: a primary winding and a secondary winding with the primary and secondary windings each being subdivided into a plurality of partial windings; and a chamber coil body with a plurality of chambers; and wherein the partial windings of the primary winding are disposed in a first group of chambers of the coil body, the partial windings of the secondary winding are disposed in a second group of chambers of the coil body, and the chambers of the first and second groups are interleaved.

Due to the fact that the individual windings or partial windings of the primary are disposed only in chambers of the first group and the windings or partial windings of the secondary are disposed only in chambers of the second group, i.e. primary and secondary are distributed to separate chambers, the necessary dielectric strength between primary and secondary is assured. By dividing each of the primary and secondary windings to a respective plurality or group of chambers and, due to the interleaved or nested arrangement of the chambers of the primary and the secondary, the desired fixed coupling between primary and secondary, and thus the desired low stray inductance at the primary and secondary, are realized. It has been found that a total number of chambers in the order of magnitude of six constitutes an economically favorable solution. With a smaller number of chambers, the coupling between primary and secondary is reduced. With a larger number of chambers, however, either the individual chambers become too small or the entire transformer, and particularly the core, become too large.

BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a circuit diagram for a preferred embodiment of a switched mode power supply transformer according to the invention.

FIG. 2 is a schematic partial sectional view showing the distribution of the individual windings of FIG. 1 to different chambers according to the invention.

DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

FIG. 1 shows a transformer intended for a switched mode power supply for a television receiver with a power output between 40 and 150 watts. The transformer includes a primary side P and a secondary side S which, while maintaining the required dielectric strength of, for example, 10,00

0 V, are galvanically decoupled or separated from one another. The primary side P includes a primary winding 1 which, as the operating winding, will lie in the collector circuit of a switching transistor switched at about 20-30 kHz. The primary winding 1 is divided into three partial windings 1a, 1b and 1c which are connected in series. When utilized in a television receiver, the beginning of partial winding 1a and the end of partial winding 1c are connected into the collector circuit of the switching transistor, while the taps between the partial windings 1a-1b and 1b-1c are not utilized, but rather form supporting points for the connection of the terminals of the partial windings. The primary side P also includes an additional winding 3 which feeds the feedback path with which the primary winding 1a-1c is designed as a self-resonant circuit. Moreover, the primary side P includes an additional winding 4 for regulating the moment of current flow in the switching transistor in the sense of stabilizing the amplitude of the output voltages on the secondary side S.

0 V, are galvanically decoupled or separated from one another. The primary side P includes a primary winding 1 which, as the operating winding, will lie in the collector circuit of a switching transistor switched at about 20-30 kHz. The primary winding 1 is divided into three partial windings 1a, 1b and 1c which are connected in series. When utilized in a television receiver, the beginning of partial winding 1a and the end of partial winding 1c are connected into the collector circuit of the switching transistor, while the taps between the partial windings 1a-1b and 1b-1c are not utilized, but rather form supporting points for the connection of the terminals of the partial windings. The primary side P also includes an additional winding 3 which feeds the feedback path with which the primary winding 1a-1c is designed as a self-resonant circuit. Moreover, the primary side P includes an additional winding 4 for regulating the moment of current flow in the switching transistor in the sense of stabilizing the amplitude of the output voltages on the secondary side S. The secondary side S initially includes the secondary winding 2 from which is obtained, via a rectifier circuit (not shown), the main operating voltage U1. The secondary winding 2 is divided into two series connected partial windings 2a and 2b. Additionally, the secondary winding S includes a winding 5 for generating an operating voltage for the video amplifier and a further winding 6 for generating the operating voltage for the vertical deflection stage of a television receiver. Moreover, an additional secondary winding 7 is provided from which, after rectification, the operating voltage or the audio output stage of the receiver is obtained. Winding 7 comprises three partial windings 7a, 7b, 7c which are connected in parallel. The audio output stage of a television receiver has a greatly fluctuating current input between 50 mA and 1000 mA so that the load of the secondary side S varies considerably. This variation in load may effect an undesirable change in the operating voltage U1 which also influences the horizontal deflection amplitude. This undesirable dependency can be reduced in that the coupling between winding 7 and winding 4 is dimensioned greater, for regulating purposes, than the coupling between winding 2 and winding 4. This solution is described in greater detail in Federal Republic of Germany Offenlegungsschrift (laid open application) DE-OS No. 2,749,847 of May 10, 1979. This increased coupling between windings 7 and 4 is realized in the present case by the three parallel connected windings 7a, 7b, 7c. Finally, the secondary S includes a further winding 8 which serves to generate, after rectification, a negative operating voltage of -30 V.

FIG. 2 show

s one half of the chamber coil body 9 for the individual windings of FIG. 1, with the body 9 including a total of six chambers 10. The size and particularly the widths of the individual chambers 10 can vary with respect to one another and the widths may all be different. Preferably, the width of the narrowest chamber 10 is about 1 mm and the total width of all six chambers is only approximately 20 mm so as to realize a flat and optimally coupled transformer.

s one half of the chamber coil body 9 for the individual windings of FIG. 1, with the body 9 including a total of six chambers 10. The size and particularly the widths of the individual chambers 10 can vary with respect to one another and the widths may all be different. Preferably, the width of the narrowest chamber 10 is about 1 mm and the total width of all six chambers is only approximately 20 mm so as to realize a flat and optimally coupled transformer. As shown, one third of the primary winding 1, in the form of respective partial windings 1a, 1b and 1c, is distributed to each of the first, third and fifth chambers 10 of the coil body 9. The additional primary windings 3 and 4 are disposed in the third chamber 10 above the partial winding 1b. One half of the secondary winding 2, in the form of respective partial windings 2a, 2b, is dis

tributed to each of the second and fourth chambers 10 of the coil body 9. The three partial windings 7a, 7b and 7c of the additional secondary winding 7 for the audio output stage are distributed to the second, fourth and sixth chambers 10, respectively, with the partial windings 7a-7c being disposed closest to the longitudinal axis of the coil body 9 and thus below any partial secondary winding 2a, 2b or other secondary winding which may be located in the same chamber. That is, the partial windings 7a and 7b are disposed below the partial windings 2a and 2b, respectively, in the respective second and fourth chambers 10, and below the additional secondary windings 5 and 8 in the sixth chamber 10. Further winding 6 is disposed above partial secondary winding 2b.

tributed to each of the second and fourth chambers 10 of the coil body 9. The three partial windings 7a, 7b and 7c of the additional secondary winding 7 for the audio output stage are distributed to the second, fourth and sixth chambers 10, respectively, with the partial windings 7a-7c being disposed closest to the longitudinal axis of the coil body 9 and thus below any partial secondary winding 2a, 2b or other secondary winding which may be located in the same chamber. That is, the partial windings 7a and 7b are disposed below the partial windings 2a and 2b, respectively, in the respective second and fourth chambers 10, and below the additional secondary windings 5 and 8 in the sixth chamber 10. Further winding 6 is disposed above partial secondary winding 2b. As can be seen in FIG. 2, the chambers 10 contain alternatingly only windings or partial windings of the primary side P or of the secondary side S. The illustrated nesting or interleaving of the windings, i.e. the alternating arrangement of windings of the primary side P and of the secondary side S in successive chambers 10, assures the desired close coupling between the primary side P and the secondary side S. The arrangement of the windings 3, 4 in approximately the center of the coil body 9 above partial winding 1b assures the desired close coupling between the windings 3, 4 with the other windings.

In an embodiment of the transformer shown in FIGS. 1 and 2 which was successfully tested in practice, the individual windings were all wound with the same diameter wire and contained the following numbers of turns:

| ______________________________________ |

| Winding No. Number of Turns |

| ______________________________________ |

1a 22 1b 22 1c 22 2a 30 2b 30 3 3 4 10 5 25 6 1 7a 11 7b 11 7c 11 8 16 |

| ______________________________________ |

It will be understood that the above description of the present invention is susceptible to various modifications, changes and adaptations, and the same are intended to be comprehended within the meaning and range of equivalents of the appended claims.

TELEFUNKEN PALCOLOR HIFI 292 PIP "MILLENNIUM" CHASSIS 618 A-2 PIP (ICC5341) NS5000 Raster distortion correction circuitry Unit for a video display apparatus that includes a square-planar picture tube

1. Video display apparatus with correction of raster distortion, comprising:

a picture tube having a phosphor screen located on a faceplate having an aspherically curved surface contour, with at least one of a minor and major axis exhibiting a curvature that changes from an edge of the faceplate to the center;

deflection means including horizontal and vertical deflection windings for generating respectively therein horizontal and vertical deflection currents to enable an electron beam of said picture tube to scan a raster on said phosphor screen;

a parabola generator coupled to said deflection means for generating a generally parabolically shaped signal that produces a parabolic modulation of the scanning of said electron beam to generally provide correction of a first raster distortion while leaving uncorrected a residual raster distortion due to the change in curvature of said faceplate from said edge to the center; and

means for nonlinearly modifying said (parabolic modulation) parabolically shaped signal as a function of said change in curvature of said faceplate to provide additional modulation of the scanning of said electron beam for correcting said residual raster distortion.

2. Apparatus according to claim 1 wherein said first raster distortion results in side pincushion raster distortion and wherein said faceplate has an aspherically curved geometry that results in areas of said faceplate near the top and bottom being of increased curvature relative to the curvature in areas near the center. 3. Apparatus according to claim 2 wherein said residual raster distortion comprises a barrel-like distortion of a raster display of a vertical line pattern in said areas near the top and bottom of said faceplate. 4. Apparatus according to claim 2 wherein said nonlinearly modifying means comprises a current source coupled to said parabola generator and a switched current divider that switches from a first conductive state to a second conductive state during that portion of a vertical trace interval when a raster is being scanned on said faceplate in said areas of increased curvature. 5. Apparatus according to claim 4 wherein said parabolically shaped signal is a generally parabolically shaped input voltage repeating at a vertical deflection rate and having both a DC component voltage and an AC parabolic component voltage and wherein said switched current divider comprises an impedance receiving a constant current from said current source for establishing a bias voltage level and switching means responsive to said bias voltage level and direct current coupled to said parabola generator for shunting a portion of said constant current when said input voltage goes beyond a threshold voltage level established in accordance with said bias voltage level to modify the waveshape of said input voltage in a manner that corrects said residual raster distortion. 6. A circuit for correcting a given error of electron beam positioning in a video display apparatus, comprising:

a deflection winding;

an output stage for generating current in said deflection winding to control said electron beam positioning;

a parabolic voltage generator for developing a generally parabolically shaped input voltage repeating at a deflection rate and having both a DC component voltage and an AC parabolic component voltage;

an amplifier for driving said output stage in accordance with said parabolically shaped input voltage to generally correct said given error while retaining a residual error of said electron beam positioning;

a current source;

an impedance receiving current from said current source for establishing a bias voltage level; and

switching means responsive to said bias voltage level and direct current coupled to said parabolically shaped input voltage for shunting a portion of the current from said current source when said input voltage goes beyond a threshold voltage level established in accordance with said bias voltage level to modify the waveshape of said input voltage in a manner that corrects said residual error.

7. A circuit according to claim 6 wherein said switching means is direct current coupled to an output terminal of said parabolic voltage generator, at which terminal said input voltage is developed, and which is direct current coupled to a terminal of said impedance, at which impedance terminal said bias voltage level is developed. 8. A circuit according to claim 7 wherein said switching means comprises a diode in which there flows the shunted portion of current from said current source. 9. A circuit according to claim 7 wherein the shunted portion of current from said current source establishes a modified parabola voltage at an output terminal of said switching means that is direct current coupled to the output terminal of said parabolic voltage generator, said modified parabola voltage having a waveform that generally follows the waveform of said input voltage when said switching means is in one conductive state and having a waveform of waveshape that is substantially different than that of said input voltage when said switching means is in another conductive state. 10. A circuit according to claim 9 including means for AC coupling said modified parabola voltage to said amplifier. 11. A circuit according to claim 10 including means for adjusting said bias voltage level to adjust the switching instants of said switching means and wherein a peak amplitude of said modified parabola voltage remains substantially unchanged for different adjustments of said bias voltage level. 12. A circuit according to claim 11 including an adjustable voltage divider coupled to said AC coupling means and direct current coupled to said amplifier for adjusting the amplitude of the AC coupled modified parabola voltage, and wherein the peak amplitude of the modified parabola voltage that is established at the output terminal of said switching means remains substantially unchanged for different adjustments of said voltage divider. 13. A circuit according to claim 9 wherein said input voltage includes an AC sawtooth component voltage repeating at said deflection rate and further including means for applying said sawtooth component voltage to said impedance to provide common-mode rejection of said sawtooth component voltage with respect to the shunted portion of current from said current source. 14. A circuit according to claim 9 wherein said switching means applies an additional voltage to said terminal of said impedance that is representative of the difference between said bias voltage level and said input voltage to control the amplitude of the shunted portion of current in accordance with said additional voltage. 15. A circuit according to claim 9 wherein said current source comprises a source of DC voltage coupled to a second impedance, and wherein said switching means applies an additional voltage to said terminal of the first mentioned impedance that is representative of a difference between said bias voltage level and said input voltage. 16. A circuit according to claim 15 wherein said DC voltage of said DC voltage source is substantially greater in magnitude than that of said additional voltage to prevent significant changes from occurring in the magnitude of said current source when said switching means changes conductive states. 17. A circuit according to claim 6 wherein said video display apparatus includes a picture tube having a phosphor screen located on a faceplate having an aspherically curved geometry that produces a relatively flat surface contour and wherein said residual error of electron beam positioning is produced in accordance with said aspherically curved geometry. 18. A circuit according to claim 17 wherein said given error is produced by side pincushion distortion and wherein said residual error produces a barrel-like distortion of a raster display of a vertical line pattern in regions near the top and bottom of said faceplate where the curvature of said faceplate is increased relative to the curvature in the center region. 19. Apparatus according to claim 1 wherein said nonlinearly modifying means produces a parabolic modulation when scanning raster lines near top and bottom of said raster that is different than when scanning raster lines near raster center for correcting said residual raster distortion due to the aspherically curved geometry of said faceplate.

New, flatter faceplate picture tubes, such as the RCA Corporation square-planar picture tubes, have aspherically curved faceplate contours. A tube of this type, having a complex curvature faceplate, is described in the following U.S. patent applications, herein incorporated by reference.

1. U.S. patent application Ser. No. 469,772, filed Feb. 25, 1983, by F. R. Ragland, Jr. entitled CATHODE-RAY TUBE HAVING AN IMPROVED SHADOW MASK CONTOUR.

2. U.S. patent application Ser. No. 469,774, filed Feb. 25, 1983 by F. R. Ragland, Jr. entitled CATHODE-RAY TUBE HAVING A FACEPLATE PANEL WITH A SUBSTANTIALLY PLANAR PERIPHARY.

3. U.S. patent application Ser. No. 469,775, filed Feb. 25, 1983, by R. J. D'Amato et al., entitled CATHODE-RAY TUBE HAVING DIFFERENT CURVATURE ALONG MAJOR AND MINOR AXES.

4. U.S. patent application Ser. No. 529,644, filed Sept. 6, 1983, by R. J. D'Amato et al., entitled CATHODE-RAY TUBE HAVING A FACEPLATE PANEL WITH AN ESSENTIALLY PLANAR SCREEN PERIPHERY.

In one form of flatter faceplate picture tube, as typified by the RCA 110° COTY-SP, square-planar, 27 V, color television picture tube, A68ACC10X, the formula for the tube faceplate sagittal height, z, in millimeters, with reference to the center of the faceplate is given by: Z=A 1 X 2 +A 2 X 4 +A 3 Y 2 +A 4 X 2 Y 2 +A 5 X 4 Y 2 +A 6 Y 4 +A 7 X 2 Y 4 +A 8 X 4 Y 4 ,

where X and Y are the distance coordinates, in millimeters, from the faceplate center along the major and minor axes, respectively, and where: A 1 =-0.236424229×10 -4 A 2 =-0.363538575×10 -8 A 3 =-0.422441063×10 -3 A 4 =-0.213537355×10 -8 A 5 =+0.883912220×10 -13 A 6 =-0.100020398×10 -9 A 7 =+0.117915353×10 -14 A 8 =+0.527722295×10 -21

The picture tube faceplate defined by this formula has a relatively shallow curvature near the center of the faceplate, which increases near the edg

es along paths parallel to both the major and minor axes of the tube. The overall result is a faceplate of relatively flat appearance and with planar edges, namely, with points along the top, bottom, right and left edges located substantially in a common plane.

es along paths parallel to both the major and minor axes of the tube. The overall result is a faceplate of relatively flat appearance and with planar edges, namely, with points along the top, bottom, right and left edges located substantially in a common plane. In general, the raster scanned on the phosphor screen of a picture tube may exhibit an east-west or side pincushion raster distortion. This distortion may be substantially corrected by a side pincushion correction circuit that produces a parabolic amplitude modulation of the horizontal deflection current. The required vertical rate parabola voltage may be obtained from the vertical deflection circuit by integration of the vertical sawtooth current.

When using such a conventional circuit for raster correction in a picture tube, such as a square-planar picture tube that has an aspherically curved faceplate, a small but often objectionable raster distortion may remain at the top and bottom of the display, as illustrated by the solid vertical lines of a raster R display R in FIG. 1. Due to the aspherically curved geometry of the faceplate, the vertical line bend away from the vertical direction near the top and bottom of the raster display, where the curvature of the faceplate increases. The overall appearance of the vertical lines in FIG. 1 is slightly barrel-shaped.

In accordance with an aspect of the invention, a video display apparatus includes a picture tube having a phos

phor screen located on a faceplate having an aspherically curved geometry. Correction circuitry is provided that compensates for raster distortion or electron beam positioning errors, such as pincushion or convergence distortions. The correction circuitry includes a parabola generator coupled to deflection circuitry for producing a parabolic modulation of the scanning of the electron beam. The modulation generally provides correction of the raster distortion or electron beam positioning error, while retaining a residual error due to the aspherically curved geometry of the faceplate. The modulation is nonlinearly modified in accordance with the aspherically curved geometry to provide additional modulation of the scanning of the electron beam for correcting the residual error.

phor screen located on a faceplate having an aspherically curved geometry. Correction circuitry is provided that compensates for raster distortion or electron beam positioning errors, such as pincushion or convergence distortions. The correction circuitry includes a parabola generator coupled to deflection circuitry for producing a parabolic modulation of the scanning of the electron beam. The modulation generally provides correction of the raster distortion or electron beam positioning error, while retaining a residual error due to the aspherically curved geometry of the faceplate. The modulation is nonlinearly modified in accordance with the aspherically curved geometry to provide additional modulation of the scanning of the electron beam for correcting the residual error. In accordance with another aspect of the invention, a particularly advantageous arrangement of correction circuitry smoothly straightens the bent vertical lines near the top and bottom of the raster display illustrated in FIG. 1.

The parabola generator of the correction circuit arrangement produces a generally parabolically shaped input voltage repeating at a deflection rate. An amplifier drives an output stage that generates current in a deflection winding to control the electron beam landing position. The amplifier is responsive to the output of the parabola generator for driving the output stage in accordance with the parabolically shaped input voltage to generally correct electron beam landing error, while retaining a residual error. A current source with a switched current dividing network is responsive to a threshold level of the parabolically shaped input voltage for supplying to the amplifier a portion of the current from the current source when the input voltage exceeds the threshold level to correct the residual error.

FIG. 1 illustrates vertical lines of a raster display scanned on the screen of a square-planar picture tube;

FIG. 2 illustrates in block diagram form raster scanning circuitry used in conjunction with raster scanning on the aspherically curved faceplate of a square-planar picture tube, shown schematically in FIG. 2 from a side elevation view, in partial breakaway;

FIG. 3 illustrates detailed embodiments of the horizontal and vertical deflection circuits of FIG. 2, including circuitry embodying the invention that corrects for the residual side pincushion distortion illustrated in FIG. 1;

FIG. 4 illustrates a detailed embodiment of a portion of the circuit of FIG. 3; and

FIG. 5 illustrates waveforms useful in explaining operation of the circuits of FIGS. 3 and 4.

In FIG. 1, there is illustrated vertical lines of a raster display R that is generated on the phosphor screen of a faceplate 30 of a

square-planar picture tube SP of FIG. 2. Horizontal and vertical deflection circuits 20 and 40 of FIG. 2 generate horizontal and vertical deflection currents in horizontal and vertical deflection windings L H and L V , respectively. The horizontal and vertical deflection currents deflect electron beams 18 in square-planar picture tube SP to produce raster display R on faceplate 30.

square-planar picture tube SP of FIG. 2. Horizontal and vertical deflection circuits 20 and 40 of FIG. 2 generate horizontal and vertical deflection currents in horizontal and vertical deflection windings L H and L V , respectively. The horizontal and vertical deflection currents deflect electron beams 18 in square-planar picture tube SP to produce raster display R on faceplate 30. Square-planar picture tube SP incorporates a glass envelope 11 comprising a generally rectangular faceplate panel 19 and a tubular neck 14 connected by a funnel 16. Panel 19 comprises viewing faceplate 30 and a peripheral flange or side wall 12, which is sealed to funnel 16 by a glass frit 17. A generally rectangular 3-color cathodoluminescent phosphor screen 15 is carried by the inner surface of faceplate 30. The screen may be a line screen, with the phosphor lines extending substantially parallel to the minor or vertical axis Y--Y of the tube. Alternatively, the screen may be a dot screen. A multi-aperture color selection electrode or shadow mask 13 is removably mounted within panel 19 in predetermined spaced relation to screen 15. An electron gun 10, shown schematically by dashed lines in FIG. 2, is centrally mounted within neck 14 to generate and accelerate the three electron beams 18 along convergent paths through mask 13 to screen 15.

The line and field deflection currents in line and field deflection windings L H and L V , respectively, subject the three electron beams 18 to vertical and horizontal magnetic flux that scans the beams horizontally in the direction of the major or horizontal axis X--X and vertically in the direction of the minor axis Y--Y, in a rectangular raster pattern over screen 15. The longitudinal axis of picture tube SP is labeled Z--Z in FIG. 2.

Faceplate 30 of square-planar color picture tube SP is relatively flat. The curvature of the faceplate is complex and may be approximated in accordance with the polynominal expression given above. In the field scanning direction, or as the electron beams are scanned from top edge to bottom edge, vertically, the curvature of the faceplate decreases from top edge to center and then increases again to the bottom edge. A similar situation holds in the line scanning direction.

Assume that horizontal and vertical deflection circuits 20 and 40 of FIG. 2 correct for distortions such as S-distortion, north-south and gullwing distortion. Furthermore, assume that horizontal deflection circuit 20 generally corrects for side pincushion distortion by parabolically modulating the amplitude of the horizontal deflection current. The display of a vertical line pattern on faceplate 30 by means of raster line scanning produces a raster display such as illustrated in solid-line in FIG. 1. The generally vertical lines exhibit a residual distortion at the top and bottom of the raster which, due to the aspherically curved geometry of faceplate 30, causes the vertical raster lines to be bent inward toward the center in a barrel-like manner.

In accordance with a feature of the invention, horizontal deflection circuit 20 nonlinearly modifies the parabolic modulation of the horizontal deflection current to straighten the vertical lines at the top and bottom of the raster, as illustrated by the dashed-line, straight line segments of FIG. 1.

FIG. 3 illustrates

detailed embodiments of vertical deflection circuit 40 and horizontal deflection circuit 20 of FIG. 2 that include nonlinear waveshaping circuitry in accordance with an aspect of the invention. In horizontal deflection circuit 20 of FIG. 3, a B+ voltage is applied to the primary winding W p of a flyback transformer T1 via a small valued resistor 21. A capacitor 22 provides filtering. Primary winding W p is coupled to a horizontal output stage 70 of horizontal deflection circuit 20. Horizontal output stage 70 includes a horizontal oscillator and driver 25, a horizontal output transistor Q1, a first retrace capacitor C R1 coupled across transistor Q1, a damper diode D2, a second retrace capacitor C R2 coupled across diode D2 and the series arrangement of a linearity inductor 26, and S-shaping capacitor C s , deflection winding L H of FIG. 2, and a resonant circuit 27, comprising a capacitor C1 in parallel with the inductance of a tapped winding W1 of a transformer T2. Deflection winding L H is coupled to the tap terminal of winding W1.

detailed embodiments of vertical deflection circuit 40 and horizontal deflection circuit 20 of FIG. 2 that include nonlinear waveshaping circuitry in accordance with an aspect of the invention. In horizontal deflection circuit 20 of FIG. 3, a B+ voltage is applied to the primary winding W p of a flyback transformer T1 via a small valued resistor 21. A capacitor 22 provides filtering. Primary winding W p is coupled to a horizontal output stage 70 of horizontal deflection circuit 20. Horizontal output stage 70 includes a horizontal oscillator and driver 25, a horizontal output transistor Q1, a first retrace capacitor C R1 coupled across transistor Q1, a damper diode D2, a second retrace capacitor C R2 coupled across diode D2 and the series arrangement of a linearity inductor 26, and S-shaping capacitor C s , deflection winding L H of FIG. 2, and a resonant circuit 27, comprising a capacitor C1 in parallel with the inductance of a tapped winding W1 of a transformer T2. Deflection winding L H is coupled to the tap terminal of winding W1. Resonant circuit 27 is tuned to produce approximately two cycles of oscillation during the horizontal trace interval for introducing an oscillatory current component into horizontal deflection current i H that provides dynamic S-correction of the raster scanned on faceplate 30 of square-planar picture tube SP of FIG. 1. The function of dynamic S-correction, resonant circuit 27 is more fully described in U.S. Pat. No. 4,563,618, by P. E. Haferl, issued Jan. 7, 1986, entitled S-CORRECTED DEFLECTION CIRCUIT.

To provide side pincushion correction, the amplitude of horizontal deflection current i H is modulated at a vertical rate by a side pincushion correction modulator circuit 30 that drives horizontal output circuit 70. Side pincushion correction circuit 30 includes a damper diode D3 with a grounded anode and a cathode coupled to the anode of damper diode D2, a retrace capacitor C R3 coupled across diode D3, a modulator choke inductor L m coupled to the junction of retrace capacitors C R2 and C R3 , and a modulator control circuit 60 coupled to choke L m .

Modulator control circuit 60 modulates at a vertical rate the modulator current i m in choke L m , to concurrently modulate the retrace pulse voltage V Rm developed across modulator retrace capacitor C R3 . The modulation of retrace pulse voltage V Rm produces a concurrent but opposite sense modulation of deflection retrace pulse voltage V Rd across deflection retrace capacitor C R2 . The vertical rate modulation of deflection retrace pulse voltage V Rd produces the required vertical rate modulation of horizontal deflection current i H that provides side pincushion correction.

The opposing sense modulation of retrace pulse voltages V Rd and V Rm produces an unmodulated retrace pulse voltage V R at the collector of horizontal output transistor Q1. Retrace pulse voltage V R is applied to the primary winding W p of flyback transformer T1 for generating an unmodulated retrace pulse voltage V RH at a terminal A of a secondary winding W s . An unmodulated retrace pulse voltage is also generated in a high voltage winding W HV for developing an ultor accelerating potential at a terminal U of a high voltage generating circuit 23.

FIG. 3 also illustrates a detailed embodiment of vertical deflection circuit 40 of FIG. 2. Vertical deflection circuit 40 includes a vertical deflection amplifier U1 coupled to vertical deflection winding L V of FIG. 2 for generating a vertical deflection current i V that deflects the electron beams in picture tube SP of FIG. 2 in the vertical direction. Vertical deflection winding L V is coupled to a north-south and gullwing distortion correction circuit 34 for modulating vertical deflection current i V in a manner that corrects both north-south pincushion distortion and gullwing distortion of the raster when scanning raster lines on square-planar picture tube SP of FIG. 2. A description of the operation of north-south pincushion and gullwing correction circuit 34 may be found in U.S. patent application Ser. No. 719,227, filed Apr. 2, 1985, by P. E. Haferl entitled NORTH-SOUTH PINCUSHION CORRECTED DEFLECTION CIRCUIT, now U.S. Pat. No. 4,668,897 and in U.S. patent application Ser. No. 733,661, filed May 10, 1985, by P. E. Haferl et al, entitled GULLWING DISTORTION CORRECTED DEFLECTION CIRCUITRY FOR A SQUARE-PLANAR PICTURE TUBE, both herein incorporated by reference.

Vertical deflection current i V , after passing through correction circuit 34, flows through a coupling or vertical S-shaping capacitor C V and a current sampling resi

stor R s . Coupling capacitor C V intergrates vertical deflection current i V to develop across the capacitor between terminals 35 and 36 an AC parabola voltage, of almost ideal waveshape, that repeats at the vertical deflection rate. The voltage across capacitor C V comprises the AC parabola voltage superimposed upon a DC level established by vertical deflection amplifier U1. The voltage V sV developed across current sampling resistor R s is illustrated in FIG. 5a and comprises an AC, S-shaped, sawtooth voltage repeating at the vertical deflection rate. The voltage V1 developed at terminal 35 is illustrated in FIG. 5b and equals the sum of the voltages developed across capacitor C V and resistor R s . Thus, the AC component of voltage V1 during the vertical trace interval t 3 -t 7 of FIG. 5b is a generally parabolically shaped voltage that is skewed downward by the relatively small sawtooth voltage component derived from sampling resistor R s .

stor R s . Coupling capacitor C V intergrates vertical deflection current i V to develop across the capacitor between terminals 35 and 36 an AC parabola voltage, of almost ideal waveshape, that repeats at the vertical deflection rate. The voltage across capacitor C V comprises the AC parabola voltage superimposed upon a DC level established by vertical deflection amplifier U1. The voltage V sV developed across current sampling resistor R s is illustrated in FIG. 5a and comprises an AC, S-shaped, sawtooth voltage repeating at the vertical deflection rate. The voltage V1 developed at terminal 35 is illustrated in FIG. 5b and equals the sum of the voltages developed across capacitor C V and resistor R s . Thus, the AC component of voltage V1 during the vertical trace interval t 3 -t 7 of FIG. 5b is a generally parabolically shaped voltage that is skewed downward by the relatively small sawtooth voltage component derived from sampling resistor R s . The voltages at terminals 35 and 36 are applied to vertical deflection amplifier U1 to provide DC and AC feeback, respectively, to the amplifier. The vertical rate voltages V1 and V sV , the horizontal rate retrace pulse voltage V RH and a voltage V ds developed across winding W2 of transformer T2 are coupled to correction circuit 34 to provide deflection synchronization information and to provide waveform information that produces the required waveshaping and modulation of vertical deflection current i v , as described in the aforementioned U.S. patent applications.

Vertical deflection circuit 40 may be considered as a low impedance voltage source 48 that generates parabola voltage V1 at output terminal 35 of the source.

Vertical parabola voltage V1 is nonlinearly waveshaped by a nonlinear network 50 and is then applied via a DC blocking capacitor C2 and a parabola amplitude adjusting potentiometer R a to the noninverting input terminal of an amplifier U2 of side pincushion control circuit 60. Vertical sawtooth voltage V sV is applied to the inverting input terminal of amplifier U2 via the wiper arm of a trapeze adjusting potentiometer R t and a resistor 31. The DC level at the inverting input terminal is controlled by a width adjus

ting potentiometer 33 that couples a +25 V source to the inverting input terminal via a resistor 32 and the wiper arm of potentiometer 33. The output of amplifier U2 is coupled to an inverting driver stage U3 that applies a modulation voltage V m to modulator choke inductor L m .

ting potentiometer 33 that couples a +25 V source to the inverting input terminal via a resistor 32 and the wiper arm of potentiometer 33. The output of amplifier U2 is coupled to an inverting driver stage U3 that applies a modulation voltage V m to modulator choke inductor L m . Side pincushion control circuit 60 is operated in the switched mode at the horizontal rate. A horizontal sawtooth voltage generator 29, synchronized by horizontal retrace pulse voltage V RH , applies a horizontal rate sawtooth voltage V sH to the noninverting input terminal of amplifier U2 via a resistor R g . Resistor R g represents the effective source impedance of sawtooth voltage generator 29. The output of amplifier U2 is a pulse width modulated, horizontal rate voltage having a duty cycle that varies at a vertical rate. Modulation voltage V m therefore is also a pulse width modulated, horizontal rate voltage having a duty cycle that varies at a vertical rate. This enables the drive provided by side pincushion modulator circuit 30 to be varied in a manner that corrects side pincushion distortion.

Side pincushion modulator circuit 30 operates in a manner similar to that described in U.S. patent application Ser. No. 651,301, filed Sept. 17, 1984, now U.S. Pat. No. 4,634,937 by P. E. Haferl, entitled EAST-WEST CORRECTION CIRCUIT. Other side pincushion correction circuits, such as switched mode diodc modulator circuits, may be used to drive horizontal output stage 70.

In accordance with an aspect of the invention, nonlinear waveshaping network 50 is interposed between terminal 35 and the noninverting input terminal of amplifier U2 of side pincushion control circuit 60. Nonlinear network 50 modifies the waveshape of parabola voltage V1 at terminal 35 to generate a modified parabola voltage V2 at a terminal 37, as illustrated by the solid-line waveform of voltage V2 in FIG. 5f. Shaped parabola voltage V2 is then applied to the noninverting input terminal of amplifier U2 via AC coupling capacitor C2 and potentiometer R a . The additional waveshaping provided by nonlinear network 50 corrects the residual side pincushion error that would otherwise exist when scanning a raster on the phosphor screen of a square-planar picture tube.

Nonlinear waveshaping network 50 comprises a constant current source CS in series with a potentiometer R2 that is coupled to the wiper arm of trapeze adjusting potentiometer R t . A diode D1, functioning as a unidirectional switch, is coupled between the wiper arm of potentiometer R2 and terminal 37, with the cathode of diode D1 being coupled to terminal 37.

In operation, constant current source CS generates an almost ideal constant current i 0 , illustrated in FIG. 5d, that does not significantly change in value throughout the entire vertical deflection interval t 3 -t 8 . Diode D1 is reverse biased by voltage V2 during the interval t b of FIG. 5. During this interval, all of current i 0 that flows into end terminal 38 of potentiometer R2 flows out of the other end terminal 39, as illustrated in FIG. 5c by the current i 3 during the interval t b . Current i 3 flows in that portion R2b of potentiometer R2 between intermediate wiper arm terminal 41 and end terminal 39 coupled to the wiper arm of potentiometer R t . The solid-line waveform of FIG. 5c also illustrates the voltage V3 developed by current i 3 in resistance R2b.

When diode D1 is nonconductive, during the interval t b of FIG. 5, constant current source CS advantageously establishes an adjustable DC bias voltage level V b at intermediate wiper arm terminal 41, as illustrated by the dotted-line waveform of FIG. 5c. Voltage V b equals the constant voltage level V 0 that is established for voltage V3

by constant current source CS, summed with the vertical sawtooth voltage developed at the wiper arm of trapeze adjusting potentiometer R t . Illustratively, voltage level V 0 is shown in FIG. 5c at a level established by the wiper arm of potentiometer R2 when the wiper arm is in a centered position.

by constant current source CS, summed with the vertical sawtooth voltage developed at the wiper arm of trapeze adjusting potentiometer R t . Illustratively, voltage level V 0 is shown in FIG. 5c at a level established by the wiper arm of potentiometer R2 when the wiper arm is in a centered position. When diode D1 is nonconductive, voltage V1 is divided by a voltage divider (R1, R a , R b , R g ) coupled between terminal 35 and the noninverting input terminal of amplifier U2 for developing voltage V2 at terminal 37, which terminal is an intermediate point of the voltage divider. As illustrated in FIGS. 5b and 5f, voltages V1 and V2 exhibit substantially the same waveshape during the interval t b .

During the second half of vertical trace, after the center of trace instant t 5 , voltages V1 and V2 decrease in amplitude. Near time t 6 , voltage V1 has decreased to a threshold voltage level V' al and voltage V2 has decreased to a threshold voltage level V a1 . The decreased voltage V2 at terminal 37 near time t 6 or time t 1 , enables diode D1 of nonlinear waveshaping circuit 50 to begin conducting, thereby coupling together terminals 37 and 41.

Diode D1 continues to conduct throughout the interval t a of FIG. 5. During this interval, voltages V1 and V2 are below the threshold levels V' a2 and V a2 , respectively. At the end of the interval t a , near time t 9 or time t 4 , voltages V1 and V2 have increased sufficiently to reestablish at terminal 41 the bias voltage level V b of FIG. 5c that forces diode D1 to become nonconductive.

During the interval t a , when diode D1 is conductive, a portion of constant current i O of FIG. 5d, that flows in the upper resistance portion R2a of potentiometer R2, is shunted away from resistance R2b via the wiper arm of potentiometer R2 and diode D1. The shunt current i c in diode D1 is illustrated in FIG. 5e during the interval t 1 -t 4 or t 6 -t 9 . Current i c substracts from constant current i 0 when diode D1 is conductive to reduce the amplitude of current i 3 in resistance R2b by the amount of current shunted. As illustrated in FIG. 5c, current i 3 , during the interval t a , has the same waveshape as current i c of FIG. 5e, but inverted in phase.

The waveshape of current i c is determined in accordance with the waveshape of the parabolic component of voltage V1 that is applied to the voltage divider (R1, R2b) formed whendiode D1 is conductive. The amplitude of current i c is related to the difference in value between the bias voltage level V b and the parabolic voltage V1.

Cor

rection current i c , flowing into terminal 37, modifies the waveshape of voltage V2 during the interval t a to correct the residual side pincushion error that would otherwise exist in raster display R of FIG. 1. Correction current i c flows mainly in resistor R1 to provide an additional voltage drop between terminals 37 and 35 that produces a flatter slope to the sides of parabola voltage V2 during the conduction interval t a of diode D1.

rection current i c , flowing into terminal 37, modifies the waveshape of voltage V2 during the interval t a to correct the residual side pincushion error that would otherwise exist in raster display R of FIG. 1. Correction current i c flows mainly in resistor R1 to provide an additional voltage drop between terminals 37 and 35 that produces a flatter slope to the sides of parabola voltage V2 during the conduction interval t a of diode D1. The solid-line waveform of FIG. 5f during the interval t a illustrates voltage V2 with diode D1 conducting. The dashed-line waveform illustrates the waveshape that voltage V2 would have assumed had diode D1 remained nonconductive during the interval t a . Comparing the solid-line waveform with the dashed-line waveform in FIG. 5f, one notes that the presence of nonlinear network 50 waveshapes parabola voltage V2 during the intervals t 3 -t 4 and t 6 -t 7 , when the top and bottom of the raster are being scanned.

The flattening of parabola voltage V2 occurs when the raster lines between lines L3 and L4 and between lines L6 and L7 of FIG. 1 are being scanned. This flattening produces less modulation of the amplitude of deflection current i H when scanning the top and bottom raster lines. The result of the nonlinear waveshaping is the straightening of the bent vertical line segments of raster display R of FIG. 1 to correct the residual side pincushion error caused by the increased curvature of the faceplate of a square-planar picture tube in the top and bottom regions of the faceplate.

FIG. 4 illustrates a more de

tailed embodiment of a portion of the circuitry of FIG. 3 that includes nonlinear network 50. Items in FIGS. 3 and 4 similarly identified perform similar functions or represent similar quantities.

tailed embodiment of a portion of the circuitry of FIG. 3 that includes nonlinear network 50. Items in FIGS. 3 and 4 similarly identified perform similar functions or represent similar quantities. Inverting driver stage U3 comprises a switching transistor Q2 driven at its base by amplifier U2 and having its collector coupled to choke inductor L m and its emitter coupled to ground. During those intervals within each horizontal deflection cycle that transistor Q2 is cutoff, modulator current i m flows to the B+ supply via a flywheel diode D4. DC biasing for transistor Q2 is established by voltage dividing resistors 42 and 43. To provide stabilized operation of driver transistor Q2, negative feedback from the collector of the transistor to the noninverting input terminal of amplifier U2 is provided via a resistor 44.

Horizontal sawtooth generator 29 comprises an RC network including a resistor 45 coupled to flyback transformer terminal A and a capacitor 46 coupled to the noninverting input terminal of amplifier U2. DC biasing of the noninverting input terminal is provided by resistor R b . Horizontal retrace pulse voltage V RH is integrated by the RC network to develop the horizontal sawtooth voltage V sH that produces the horizontal rate switching of transistor Q2. The duty cycle of the horizontal rate switching is modulated by means of the vertical rate modulation of the AC-zero level of voltage V sH .

In FIG. 4, constant current source CS comprises a DC voltage source of relatively large magnitude, such as the 140 volt, B+ voltage source, coupled to a resistor R3 of relatively large value, such as 180 kilohm. The amplitude of constant current i 0 is mainly determined by the value of the B+ voltage divided by the sum of the values of resistors R3 and R2. Current i 0 establishes an adjustable bias voltage level V b at the wiper arm of potentiometer R2 that maintains diode D1 nonconductive during the interval t b of FIG. 5 when parabola voltage V1 is sufficiently large in amplitude to keep the diode reverse biased. During the remaining interval t a , parabola voltage V1 is sufficiently small in amplitude to enable diode D1 to shunt some of current i 0 away from resistance portion R2b of potentiometer R2 to provide the correction current i c that waveshapes parabola voltage V2.

Advantageously, diode D1 is DC coupled to parabola voltage source 48 via resistor R1, with the cathode of diode D1 being coupled on the DC side (with respect to parabola voltage V1) of coupling capacitor C2. By means of the DC connection of diode D1 to parabola voltage source 48, the diode switching instants t 4 and T 6 may be adjusted by potentiometer R2 independently of the adjustment of east-west parabola amplitude potentiometer R a . When potentiometer R a is adjusted for the desired parabola amplitude, the AC-zero level of the parabola voltage applied to the noninverting input terminal of amplifier U2 also varies. This variation of the AC-zero level has little or no effect on the switching of diode D1.

For example, assume amplitude potentiometer R a is adjusted to provide the proper amount of side pincushion correction when the central raster lines are being scanned between raster line L4 and raster line L6 of FIG. 1 during the interval t 4 -t 6 of FIG. 5. Potentiometer R2 may then be adjusted to establish a bias voltage level V b that enables diode D1 to switch conductive states near times t 4 and t 6 . The switching of diode D1 near times t 4 and t 6 provides the required additional waveshaping of voltage V2 that corrects the residual side pincushion error in the top and bottom regions of raster display R.

The instants when diode D1 switches conductive states are controlled by the DC bias level V b established by potentiometer R2 rather than by amplitude potentiometer R a . The adjustment of potentiometer R2 has no significant effect on the previous amplitude adjustment provided by potentiometer R a .

When the wiper arm of potentiometer R2 is moved towards end terminal 39, the conduction interval t a of diode D1 decreases and the cutof interval t b increases. The location of raster lines L4 and L6 where nonlinear waveshaping begins moves away from center raster line L5 towards top and bottom raster lines L3 and L7, respectively. The peak downward excursion of voltage V2, that occurs near the beginning of retrace near times t 2 and t 7 , also moves downward toward the dashed-line level that represents the peak downward excursion when diode D1 is cutoff for the entire vertical deflection interval t 2 -t 7 .

The amount of nonlinear waveshaping of parabola voltage V2 may be defined as the voltage difference between the dashed and solid-line waveforms V2 of FIG. 5f at times t 3 and t 7 , the start and end of vertical trace, respectively. This voltage difference relative to the dashed-line waveform V2 represents the amount of correction resulting on the raster display of FIG. 1.

When the wiper arm of potentiometer R2 is moved toward end terminal 38, the amount of nonlinear waveshaping increases until the conduction interval t a of diode D1 equals the nonconduction interval t b . As the wiper arm of potentiometer R2 is moved further toward end terminal 38, the amount of waveshaping begins to decrease and reaches zero when bias voltage level V b is set at a sufficiently high level to enable diode D1 to conduct for the entire vertical deflection interval.

The