INDESIT TC26SIL CHASSIS VV025C 30AX THYRISTORS LINE DEFLECTION CIRCUIT CASE STUDY (Thyristor Horizontal Output Circuits)

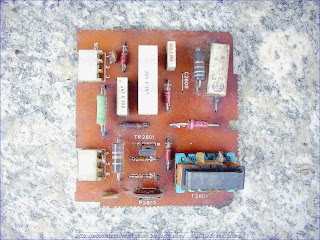

INDESIT TC26SIL CHASSIS C1 30AX VV025C Deflection Supply circuit:

A D.C. supply circuit for a television receiver which has a load circuit including at least one controllable semiconductor switch, the supply circuit comprising means for rectifying an alternating mains supply, a smoothing circuit connected between the rectifying means and load circuit and delay means for delaying the application of the full rectified and smoothed voltage to the load circuit when the receiver is initially turned on, wherein the delay means include means for inhibiting a certain number of cycles of the rectified A.C. voltage from being applied to the said smoothing means, so as to provide a D.C. voltage in which the number of cycles inhibited from reaching the smoothing means determines the delay with which the said D.C. voltage reaches the full value at the load circuit.

1.

A D.C. supply circuit for a television receiver which has a load

circuit, the supply circuit comprising rectifying means for rectifying

an alternating mains supply, a smoothing circuit connected between the

rectifying means and the load circuit of the television receiver, and

delay means for delaying the application of the maximum voltage from the

supply circuit to the load circuit when the receiver is initially

turned on even if the receiver has just previously been turned on and

then off, and said delay means comprising inhibiting means for

inhibiting at least a portion of a certain number of cycles of the

voltage from the supply circuit from being applied to said smoothing

circuit so as to provide a D.C. voltage in which the number of cycles

having portions inhibited from reaching the smoothing circuit determines

the length of delay period provided before the said D.C. voltage

reaches its maximum value at the load circuit.

1.

A D.C. supply circuit for a television receiver which has a load

circuit, the supply circuit comprising rectifying means for rectifying

an alternating mains supply, a smoothing circuit connected between the

rectifying means and the load circuit of the television receiver, and

delay means for delaying the application of the maximum voltage from the

supply circuit to the load circuit when the receiver is initially

turned on even if the receiver has just previously been turned on and

then off, and said delay means comprising inhibiting means for

inhibiting at least a portion of a certain number of cycles of the

voltage from the supply circuit from being applied to said smoothing

circuit so as to provide a D.C. voltage in which the number of cycles

having portions inhibited from reaching the smoothing circuit determines

the length of delay period provided before the said D.C. voltage

reaches its maximum value at the load circuit.2. A supply circuit as claimed in claim 1, in which said inhibiting means operates in a periodic fashion during a time interval corresponding to the required delay, said inhibiting means comprising a network of circuits with a preset time constant for determining said time interval.

3. A supply circuit as claimed in claim 2, in which the means for inhibiting includes a semiconductor device.

4. A supply circuit as claimed in claim 3, in which said semiconductor device is an electronic switch.

5. A supply circuit as claimed in claim 4, in which said electronic switch has a control terminal.

6. A supply circuit as claimed in claim 5, in which said electronic switch comprises a thyristor.

7. A supply circuit as claimed in claim 6, in which said thyristor is connected between the output of said rectifying means and the input of the load circuit.

8. A supply circuit as claimed in claim 7, in which clamping means are provided between the output of said rectifying means and the control terminal of the thyristor.

9. A supply circuit as claimed in claim 8, in which the control terminal of the thyristor receives a signal depending on the voltage at the terminals of said clamping means and the value of the D.C. voltage supplied to the load circuit.

10. A supply circuit as claimed in claim 8, in which said clamping means include a diode and capacitor.

11. A supply circuit as claimed in claim 8, in which said clamping means has no effect on circuit operation once the required delay has been achieved.

12. A supply circuit as claimed in claim 1, in which a circuit is provided for overload protection, which circuit cuts off current to the load circuit whenever the current supplied exceeds a preset threshold.

13. A D.C. supply circuit as claimed in claim 1, wherein said inhibiting means comprises a capacitor.

14. A D.C. supply circuit as claimed in claim 13, wherein said inhibiting means further comprises discharge means for quickly discharging said capacitor after the receiver has been turned off.

15. A D.C. supply circuit as claimed in claim 14, wherein said discharge means comprises a resistor coupled to said capacitor and adapted to be coupled to the load.

16. A supply circuit for supplying voltage to a load from A.C. power mains, said circuit comprising a controlled switch adapted to be coupled between the A.C. power mains and the load, and delay means for delaying the application of the maximum voltage to the load even if the supply circuit has just previously been turned on and then off, and said delay means comprising inhibiting means for controlling said controlled switch to inhibit at least a portion of a certain number of cycles of the A.C. power mains voltage from providing voltage to the load, said inhibited portions becoming successively shorter in time after said supply circuit is turned on, said certain number of cycles determining the delay until the load voltage reaches its maximum value.

Description:

The present invention relates to

a

D.C. supply circuit for a television receiver which has a load circuit

including at least one controllable semiconductor switch, such as a

thyristor, the supply circuit comprising means for rectifying an

alternating mains supply, a smoothing circuit connected between the

rectifying means and the load circuit and delay means for delaying the

application of the full rectified and smoothed voltage to the load

circuit when the receiver is initially turned on.

a

D.C. supply circuit for a television receiver which has a load circuit

including at least one controllable semiconductor switch, such as a

thyristor, the supply circuit comprising means for rectifying an

alternating mains supply, a smoothing circuit connected between the

rectifying means and the load circuit and delay means for delaying the

application of the full rectified and smoothed voltage to the load

circuit when the receiver is initially turned on.In circuits of this type, this delay is required to prevent the D.C. supply and pilot voltages from being applied simultaneously to the output and thyristor control terminals respectively when the television receiver is turned on. Without this delay, parasitic oscillations would be produced which, in the case of a circuit forming part of a television horizontal deflection circuit containing a large number of resonant circuits, would be serious enough to produce overvoltages capable of causing break-down the semiconductor.

One known way of providing this delay is to include in the circuit components whose characteristics vary according to temperature and, consequently, the current flowing through them. These components, whether PTC (positive temperature coefficient) or NTC (negative temperature coefficient), are connected so that, initially, they absorb most of the voltage directed to the thyristor output terminal, after which, the current flowing through them causes them to heat up and be cut out of the circuit.

One drawback of this type of circuit, however, is that it takes a long time for the initial operating condition to be restored (receiver off). This means that if the operator turns the receiver off and on in the space of a few minutes, there is a risk of damaging the thyristor in that the delay circuit has not yet returned to its initial condition. In fact, as long as the PTC or NTC is warm, the delay circuit does not work.

BRIEF DESCRIPTION OF THE INVENTION

With a view to mitigating the disadvantages encountered with the known circuits, the present invention p

rovides

a D.C. supply circuit for a television receiver which has a load

circuit including at least one controllable semiconductor switch, the

supply circuit comprising means for rectifying an alternating mains

supply, a smoothing circuit connected between the rectifying means and

load circuit and delay means for delaying the application of the full

rectified and smoothed voltage to the load circuit when the receiver is

initially turned on, wherein the delay means include means for

inhibiting a certain number of cycles of the rectified A.C. voltage from

being applied to the said smoothing means, so as to provide a D.C.

voltage in which the number of cycles prevented from reaching the

smoothing means determines the delay with which the said D.C. voltage

reaches the full value at the load circuit.

rovides

a D.C. supply circuit for a television receiver which has a load

circuit including at least one controllable semiconductor switch, the

supply circuit comprising means for rectifying an alternating mains

supply, a smoothing circuit connected between the rectifying means and

load circuit and delay means for delaying the application of the full

rectified and smoothed voltage to the load circuit when the receiver is

initially turned on, wherein the delay means include means for

inhibiting a certain number of cycles of the rectified A.C. voltage from

being applied to the said smoothing means, so as to provide a D.C.

voltage in which the number of cycles prevented from reaching the

smoothing means determines the delay with which the said D.C. voltage

reaches the full value at the load circuit.BRIEF DESCRIPTION OF THE FIGURES

The invention will now be described, by way of a non-limiting example, with reference to the attached drawings, in which:

FIG. 1 shows one possible application of the supply circuit embodying the principles of the present invention;

FIG. 2 shows the voltage curves, not to scale, at main points on the FIG. 1 circuit.

DETAILED DESCRIPTION OF THE INVENTION

Numerals 1 and 2 in FIG. 1 are used t

o

designate two input terminals of the supply circuit which are intended

for connection to the mains supply. Numeral 3 represents a

current-limiting resistor connected between terminal 1 and one input of a

full wave diode bridge rectifier formed of diodes 4, 5, 6 and 7. A

filter capacitor 8, is connected between one D.C. output terminal of the

diode bridge and the resistor 3 and a second capacitor 9 sharing the

same function, is connected between the D.C. output of the bridge and

input terminal 2. The output of the diode bridge is connected to the

anode of thyristor 10 which has its cathode connected to ground by way

of a smoothing capacitor 11 and its gate connected to the emitter of PNP

transistor 12 which acts as protection. The collector of transistor 12

is connected to the cathode of thyristor 10. A diode 13 is also

connected between the emitter and collector of transistor 12. The

cathode of thyristor 10 is further connected, through a resistor 14, to a

group of horizontal or line deflection circuits indicated schematically

in the Figure by block 15, to the input of which a filter capacitor 16

is also connected.

o

designate two input terminals of the supply circuit which are intended

for connection to the mains supply. Numeral 3 represents a

current-limiting resistor connected between terminal 1 and one input of a

full wave diode bridge rectifier formed of diodes 4, 5, 6 and 7. A

filter capacitor 8, is connected between one D.C. output terminal of the

diode bridge and the resistor 3 and a second capacitor 9 sharing the

same function, is connected between the D.C. output of the bridge and

input terminal 2. The output of the diode bridge is connected to the

anode of thyristor 10 which has its cathode connected to ground by way

of a smoothing capacitor 11 and its gate connected to the emitter of PNP

transistor 12 which acts as protection. The collector of transistor 12

is connected to the cathode of thyristor 10. A diode 13 is also

connected between the emitter and collector of transistor 12. The

cathode of thyristor 10 is further connected, through a resistor 14, to a

group of horizontal or line deflection circuits indicated schematically

in the Figure by block 15, to the input of which a filter capacitor 16

is also connected.To understand the description given below of how the circuit works, block 15 may be considered as providing a load equivalent to a 500 Ohm resistor.

The output of the diode bridge is also connected to the input of block 15 by way of a capacitor 17, resistor 18, a capacitor 19, a resistor 20 and a Zener diode 21, connected in series with one another.

A diode 22 and resistor 23 are also connected between the junction of capacitor 17 and resistor 18 and the input of block 15.

A capacitor 24 is connected between the cathode of diode 22 and ground.

A biasing resistor 25 is connected between the base of transistor 12 and the junction of capacitor 19 and resistor 20. A resistor 26 is connected in parallel with the capacitor 19.

Operation of the circuit will now be described with reference to the waveforms shown in FIG. 2 in which VC24 indicates the voltage curve at the terminals of condenser 24 and VC16 the voltage curve at the terminals of condenser C16 at corresponding times.

Under normal running conditions, the supply voltage from the mains supply is full wave rectified by diodes 4, 5, 6 and 7, and passes via the thyristor 10 be be smoothed by capacitors 11 and 16 and resistor 14, then applied to block 15. The thyristor 10 regulates the current supplied to block 15 and receives gating pulses via capacitor 17 and resistor 18, which introduce a suitable phase shift, and conducts in time with the conduction period of the bridge diodes 4 through 7.

The following are typical values of the components in the circuit of FIG. 1, given only by way of non-limiting example:

RATING TABLE

______________________________________

3 resistor 5.1 16 condenser 300 μF 4 diode 1N4007 17 condenser 470 nF 5 diode 1N4007 18 resistor 1.8

K

6 diode 1N4007 19 condenser 220 μF 7 diode 1N4007 20 resistor 8.2 K 8

condenser 1.5 nF 21 zener diode ZPY10 9 condenser 1.5 nF 22 diode 1N4007

10 thyristor F301 23 resistor 50 K 11 condenser 100 μF 24 condenser 8

μF 12 transistor BC307B 25 resistor 1K 13 diode BAV20 26 resistor 1.5 K

14 resistor 20

K

6 diode 1N4007 19 condenser 220 μF 7 diode 1N4007 20 resistor 8.2 K 8

condenser 1.5 nF 21 zener diode ZPY10 9 condenser 1.5 nF 22 diode 1N4007

10 thyristor F301 23 resistor 50 K 11 condenser 100 μF 24 condenser 8

μF 12 transistor BC307B 25 resistor 1K 13 diode BAV20 26 resistor 1.5 K

14 resistor 20______________________________________

If the current delivered to the load 15 is too high, the voltage across the Zener diode 21 exceeds the threshold voltage and transistor 12 switches from the disabled to the saturated state. In this situation, thyristor 10 no longer receives the gating pulses and remains disabled as long as the overload condition persists. The function of diode 13 is to fix the voltage value at the terminals of transistor 12, during the period in which the thyristor is non-conductive, regardless of the parameters of thyristor 10.

Let is now consider how the circuit works when the receiver is first turned on. As capacitor 24 is discharged, the pulse current applied to resistor 18 and normally taken to trigger the thyristor 10 is instead used to charge the said capacitor 24. Consequently, the thyristor 10 only conducts when capacitor 24 is charged.

When this occurs, during the first rectified A.C. voltage cycle, the effect of the 2-3 μsec time constant created by capacitor 3, 8, 17 and 24 and resistor 3, connected in series, is that the voltage across the terminals of resistor 18 is sufficient to make thyristor 10 conduct. However, the moment thyristor 10 starts conducting, it charges capacitors 11 and 16 with a much higher voltage than that across the terminals of capacitor 24. The reason for this is that capacitor 24 was charged at only 1/16 of the peak value available at the terminals of capacitors 17 and 24, connected in series.

As the discharge time constant of capacitor 24 is approximately 1 second, the voltage at its terminals effectively remains fixed at the present value with the result that thyristor 10 is extinguished after the first half wave and is not fired again in that, in the mean

time,

the gate-cathode voltage has been inverted. The thyristor 10 remains

disabled until its gate terminal once more receives a positive voltage,

with respect to the cathode, sufficient to fire it. During the period in

which the thyristor is disabled, capacitors 11 and 16 discharge partly

through the load (block 15, roughly 500 Ohm equivalent resistance) and

partly, through diodes 13 and 22 and resistor 18, to thereby charge

capacitor 24 which rises to a new voltage value.

time,

the gate-cathode voltage has been inverted. The thyristor 10 remains

disabled until its gate terminal once more receives a positive voltage,

with respect to the cathode, sufficient to fire it. During the period in

which the thyristor is disabled, capacitors 11 and 16 discharge partly

through the load (block 15, roughly 500 Ohm equivalent resistance) and

partly, through diodes 13 and 22 and resistor 18, to thereby charge

capacitor 24 which rises to a new voltage value.When the voltage across the terminals of capacitor 11 falls below the value that the capacitor 24 has been brought up to, thyristor 10 is fired once more to repeat the cycle. This time capacitors 11 and 16 are charged to a higher voltage than before since they were not fully discharged. As the voltage of capacitor 24 is higher than that set previously, in that during the period in which thyristor 10 is non-conductive, capacitor 24 is recharged through diodes 13 and 22 and resistor 18, the threshold at which thyristor 10 is restarted is also higher. This is repeated for a number of cycles. Each time, thyristor 10 is disabled for a shorter length of time as the voltage at the terminals of capacitor 24 gets closer to the nominal voltage capacitor 11 should have. When capacitor 24 reaches its own nominal voltage, which is higher than that of capacitor 11, thyristor 10 is no longer disabled and the circuit can be said to have reached its steady state operating condition. Capacitor 24 remains charged until the receiver is turned off. When this happens, the capacitor 24 discharges through resistor 23 and the load consisting of block 15. By means of careful selection of the rating of resistor

23, it is possible to regulate the time taken for the circuit to return

to initial operating conditions after the receiver is turned off, so as

to overcome the drawbacks mentioned previously in connection with the

prior art circuit using temperature dependent components. In the circuit

described, this time is roughly 400 ms.

23, it is possible to regulate the time taken for the circuit to return

to initial operating conditions after the receiver is turned off, so as

to overcome the drawbacks mentioned previously in connection with the

prior art circuit using temperature dependent components. In the circuit

described, this time is roughly 400 ms.FIG. 2 shows clearly the voltage curves at the terminals of capacitors 16 and 24. t1, t2, t3, t4 and t5 indicate the cycles, performed at various instants, by the circuit operating periodically.

The first cycle ranges from 0 to t1 and shows the above voltage curve during the first conduction-disabling cycle of thyristor 10. From t1 to t2 thyristor 10 performs another conduction-disabling cycle while the voltage across the terminals of capacitor 24 rises. This is repeated for a number of cycles until normal running (i.e. steady state condition) is reached. Each of these cycles is the same, the only difference being that the length of time thyristor 10 is disabled gets shorter as the voltage of capacitor 24 increases.

MOTOROLA TV ICs DEMODULATION:........is one operation in a TV receiver that is particularly suited to integration. We saw in other posts the basic differential amplifier circuit-widely used in i.c.s-operating as an f.m. detector in an intercarrier sound i.c.: the circuit functioned as a quadrature detector for the f.m. input signal. The same basic circuit can however be used in other ways to provide demodulation, depending on the inputs applied to it. This post is going to take a look at two Motorola detector i.c.s, the MC1330P + TBA396 + TDA3950 which acts as a synchronous detector for the vision and sound signals and the MC1327P which acts as a chroma signal demodulator, RGB matrix and PAL switch. In both these i.c.s differential amplifier circuits are used as double balanced demodulators.

Video Synchronous Demodulator:

The Motorola MC1330P low-level video detector is used in

the INDESIT TC26SIL CHASSIS C1 30AX VV025C .. single -standard colour chassis. Fig. 1 shows the i.c. in block diagram form together with the external circuitry as used in the INDESIT TC26SIL CHASSIS C1 30AX VV025C . The input from the final i.f. stage is fed to an integrated emitter follower at pin 7. This emitter follower provides two drives, one to a limiter amplifier section and the other to the synchronous detector section. As is by now well known a synchronous detector requires two inputs, the signal to be demodulated and a reference signal to provide the switching action. In this case the 39.5MHz i.f. carrier is used as the reference signal. The limiter section removes the modulation and feeds the carrier to the external tuned circuit L108 /C126. The 39.5MHz sinewave is then clipped and applied to the syn- chronous detector section. The detected output is fed to a video preamplifier section which provides across its external load resistors R126 and R232 the 6MHz intercarrier sound feed at pin 5 and the video signal at pin 4. L109 /C129 remove the 6MHz signal from the feed to the luminance and chrominance sections of the receiver.

the INDESIT TC26SIL CHASSIS C1 30AX VV025C .. single -standard colour chassis. Fig. 1 shows the i.c. in block diagram form together with the external circuitry as used in the INDESIT TC26SIL CHASSIS C1 30AX VV025C . The input from the final i.f. stage is fed to an integrated emitter follower at pin 7. This emitter follower provides two drives, one to a limiter amplifier section and the other to the synchronous detector section. As is by now well known a synchronous detector requires two inputs, the signal to be demodulated and a reference signal to provide the switching action. In this case the 39.5MHz i.f. carrier is used as the reference signal. The limiter section removes the modulation and feeds the carrier to the external tuned circuit L108 /C126. The 39.5MHz sinewave is then clipped and applied to the syn- chronous detector section. The detected output is fed to a video preamplifier section which provides across its external load resistors R126 and R232 the 6MHz intercarrier sound feed at pin 5 and the video signal at pin 4. L109 /C129 remove the 6MHz signal from the feed to the luminance and chrominance sections of the receiver.The use of this i.c. makes possible a number of basic changes in TV receiver design in the 70's and used about 1982. First, detection is carried out at a much lower level (about 50mV) than is possible using a single diode detector. In addition to providing more linear detection this means that less i.f. gain is required-making up the gain at v.f. is a simple matter. The advantages of this include less need for sound trapping, less critical tuning and more stable i.f. performance.

AFC Output:

The i.c. also provides an output (a 350mV clipped carrier) across the external load resistor R250 to drive an a.f.c. circuit. In the INDESIT TC26SIL CHASSIS C1 30AX VV025C. the a.f.c. circuit consists of a limiter/amplifier stage, discriminator and d.c. amplifier.

Internal Circuit:

The internal circuit of the MC1330P is shown in Fig. 2. The input emitter -follower is Q4. This drives the differential amplifier pair Q5/Q13 which forms part of the synchronous detector circuit and Q16 which with Q17 forms part of the limiter/amplifier section. The external 39.5MHz tuned circuit is con- nected between

the collectors of Q16 and Q17 between which the clipper diodes D1 and D2 are also connected. As a result anti -phase squarewaves appear at the bases of Q8 and Q9 which act as emitter -followers driving Q7 and Q11, and Q10 and Q6, respectively. The double balanced synchronous detector consists of Q6, Q7 and Q5 on one side and Q10, Q11 and Q13 on the other side. The output is developed across the base emitter junction of Q20 which is connected in the collector circuit of Q7 and acts as an emitter -follower to drive the video amplifier section Q23, Q24 and Q25. As we have seen external loads are connected to Q25 at its emitter and collector-providing the main output at pin 4 and an auxiliary output if required at pin 5. The carrier signal for the a.f.c. system is taken from the collector load of Q17 and passed via tabout 20V stabilised is fed in at pin 6 while pin 8

the collectors of Q16 and Q17 between which the clipper diodes D1 and D2 are also connected. As a result anti -phase squarewaves appear at the bases of Q8 and Q9 which act as emitter -followers driving Q7 and Q11, and Q10 and Q6, respectively. The double balanced synchronous detector consists of Q6, Q7 and Q5 on one side and Q10, Q11 and Q13 on the other side. The output is developed across the base emitter junction of Q20 which is connected in the collector circuit of Q7 and acts as an emitter -follower to drive the video amplifier section Q23, Q24 and Q25. As we have seen external loads are connected to Q25 at its emitter and collector-providing the main output at pin 4 and an auxiliary output if required at pin 5. The carrier signal for the a.f.c. system is taken from the collector load of Q17 and passed via tabout 20V stabilised is fed in at pin 6 while pin 8provides the common earthing point.

Chrominance Demodulator:

For chrominance signal demodulation, RGB matrixing and PAL V switching a Mot

orola type MC1327P i.c. is used in the INDESIT TC26SIL CHASSIS C1 30AX VV025C colour chassis. Fig. 3 shows a block diagram of the i.c. and the surrounding circuitry. The V and U signals, separated in the PAL matrix circuit part of which is shown, are fed in at pins 9 and 8 respectively to separate double balanced chroma synchronous detector circuits which are of the same basic pattern as used in the MC1330P. The U and V reference carriers are fed in at pins 13 and 12 respectively, C178 and R191 giving a 90° shift to the U reference carrier to obtain the correct quadrature conditions. The PAL V switch is built in and is driven by a waveform derived from the ident signal. This is fed in at pin 11. The luminance signal is fed in at pin 3 and line and field blanking pulses at pin 6: blanked RGB outputs are then obtained from emitter followers behind pins 2, 1 and 4 respectively. A 5V peak -to -peak output signal is obtained with an input of 0.3V p -p and the i.c. incorporates a regulated power supply.

orola type MC1327P i.c. is used in the INDESIT TC26SIL CHASSIS C1 30AX VV025C colour chassis. Fig. 3 shows a block diagram of the i.c. and the surrounding circuitry. The V and U signals, separated in the PAL matrix circuit part of which is shown, are fed in at pins 9 and 8 respectively to separate double balanced chroma synchronous detector circuits which are of the same basic pattern as used in the MC1330P. The U and V reference carriers are fed in at pins 13 and 12 respectively, C178 and R191 giving a 90° shift to the U reference carrier to obtain the correct quadrature conditions. The PAL V switch is built in and is driven by a waveform derived from the ident signal. This is fed in at pin 11. The luminance signal is fed in at pin 3 and line and field blanking pulses at pin 6: blanked RGB outputs are then obtained from emitter followers behind pins 2, 1 and 4 respectively. A 5V peak -to -peak output signal is obtained with an input of 0.3V p -p and the i.c. incorporates a regulated power supply.MOTOROLA TV ICs DEMODULATION:TBA396

INDESIT TC26SIL CHASSIS VV025C 30AX RGB Amplifying circuit /indesit patent:

amplifier circuit suitable for use as a video amplifier in a color

television circuit for driving the variable impedance load provided by a

color television picture tube, in which the load impedance of the

amplifier element of the circuit is also made variable. This is

achieved, in one embodiment by using as the output stage of the

amplifier two transistors with a complementary symmetrical configuration

so that one is always substantially cut-off while the other conducts.

In another embodiment a transistor in common collector configuration

acts as the amplifier element and its emitter from which the output of

the amplifier is taken is connected by a diode to the collector of a

transistor which feeds the base of the common collector transistor.

amplifier circuit suitable for use as a video amplifier in a color

television circuit for driving the variable impedance load provided by a

color television picture tube, in which the load impedance of the

amplifier element of the circuit is also made variable. This is

achieved, in one embodiment by using as the output stage of the

amplifier two transistors with a complementary symmetrical configuration

so that one is always substantially cut-off while the other conducts.

In another embodiment a transistor in common collector configuration

acts as the amplifier element and its emitter from which the output of

the amplifier is taken is connected by a diode to the collector of a

transistor which feeds the base of the common collector transistor.a first amplifier element (61) such as a transistor, having input and output terminals, and having an output impedance which is substantially lower than the minimum value of said load impedance within the frequency range of the signals fed to said amplifier circuit;

means for connecting said first amplifier output to said user load impedance;

a second amplifier element (85) such as a transistor, having input and output terminals;

means for connecting said second amplifier output terminal to said first amplifier input terminal;

a commutation element connected between the output terminal of said first amplifier element and the output element of said second amplifier element; and

a diode (59) connected to the input of said first amplifier and to the output element of said second amplifier for compensation of said first amplifier for temperature variations.

2. The electrical amplifier circuit of claim 1, further comprising: a negative feedback which is obtained by connecting the emitter of said first transistor to the base of said second transistor; and

a biasing circuit for the emitter of said second

transistor including

at least one transistor of opposite conductivity type with respect to

said second transistor, said at least one transistor being connected in a

circuit similar to the circuit of said second transistor so as to

obtain compensation for the variation in the voltage due to the thermal

drift effect, wherein said biasing circuit comprises a third transistor

connected in common collector configuration and a fourth transistor

connected in a circuit corresponding to that of said second transistor,

and is fed from the same voltage source which is used for biasing the

base of the second transistor.

transistor including

at least one transistor of opposite conductivity type with respect to

said second transistor, said at least one transistor being connected in a

circuit similar to the circuit of said second transistor so as to

obtain compensation for the variation in the voltage due to the thermal

drift effect, wherein said biasing circuit comprises a third transistor

connected in common collector configuration and a fourth transistor

connected in a circuit corresponding to that of said second transistor,

and is fed from the same voltage source which is used for biasing the

base of the second transistor.3. The amplifier circuit of claim 1, wherein the said first amplifier element having a low output impedance is a first transistor connected in common collector configuration and said commutation element is a semiconductor diode; said second amplifier element is a second transistor and said commutator element is connected between the emitter of said first transistor and the collector output electrode of said second transistor; and there is provided a negative feedback circuit obtained connecting the emitter of said first transistor to the base of said second transistor.

There are various known circuits capable of operating as video amplifiers, but all include transistors which operate under class A conditions and which dissipate a considerable amount of power. This is due to the fact that in order to obtain the required band width it is necessary to use only moderate load impedances. Thus, since for example the control voltage of a colour picture tube is of the order of 100-200 V the currents in the transistor at the impedance values normally used are in the region of tens of milliamps, and therefore the dissipated power is of the order of a few watts. It is therefore necessary to use power transistors which require a heat dissipator, and likewise the load resistors must be capable of dissipating several watts. All this means that rather costly components are required.

Furthermore, because all video amplifiers require a stabilised supply voltage in order to ensure correct operation and in particular in order to prevent any variation in contrast as the main supply voltage varies, it is usually necessary to provide stabilising circuits which further complicate the amplifier circuits. It is not possible to draw the required supply voltage directly from the stabilised horizontal deflection circuits because of the considerable power consumed by the amplifiers.

The present invention seeks therefore to provide a video amplifying circuit, for a television receiver, in which the disadvantages mentioned above are overcome, or at least reduced in effect.

According to the present invention, there is provided an electrical amplifier circuit having at least one amplifier element, for providing high voltages for driving a user device whose impedance varies with frequency, characterised by the fact that the load impedance of the said amplifier element is variable.

Various embodiments of the invention will now be described, by way of example, with reference to the accompanying drawings, in which:

FIG. 1 is an electrical diagram of a video amplifier constructed as a first embodiment of the invention;

FIG. 2 is an electrical diagram of a video amplifier formed as a second embodiment of the invention;

FIG. 3 is an electrical diagram of a power supply circuit for the amplifier of FIG. 2; and

FIG. 4 is a block diagram of a part of a colour television receiver, comprising three amplifiers constructed as in FIG. 2 and a power supply circuit constructed as in FIG. 3.

Referring now to the drawings, in the amplifier circuit of FIG. 1, the input signal is fed to a terminal 1 and is fed through two series connected

resistors 2 and 3

to be applied to the base of an NPN transistor 4 which is connected in a

common collector configuration.

resistors 2 and 3

to be applied to the base of an NPN transistor 4 which is connected in a

common collector configuration. The collector of the transistor 4 is connected to a first supply voltage source +V1, whilst the emitter is earthed via a resistor 5. The junction between the two input resistors 2 and 3 is earthed via a resistor 6 and a Zener diode 7, in series and the junction between the resistor 6 and the diode 7 is connected to the voltage source +V1 through a resistor 8 and to earth through a capacitor 9. The network formed by the resistors 3, 6, 8 and by the Zener diode 7 is a biasing network for the transistor 4; it also serves as a limiter circuit to limit the maximum amplitude of the video signal, in particular, the amplitude of the synchronisation pulses, for the purpose of making the clamping operations, effected downstream, independent of any amplitude differences in the signal which is supplied to the video amplifier by the circuits upstream of it. The video signal output of the transistor 4, taken from the emitter, is fed through a resistor 10 to the emitter of a PNP transistor 11 connected in cascade with the transistor 4. The collector of the transistor 11 is connected to earth through an inductor 12 and a resistor 13 in series, and the base of the transistor 11 is connected to earth through a resistor 14 and a capacitor 15 in series. The LC and RC networks constituted by the resistors 13 and 14, the inductor 12 and capacitor 15 act as phase shifting networks to compensate for phase displacements introduced by the parasitic elements present in the circuit.

The base of the transistor 11 is also connected to the first terminal of a resistor 16, whose other terminal is connected to earth through a resistor 17 and a capacitor 18 in parallel and also to the collector of a PNP transistor 19 through a resistor 20 and a diode 21 in series. To the junction of the cathode of the diode 21 with the resistor 20 there is connected a resistor 23 and a capacitor 24 in series. The resistor 23 has a terminal 22 to which is fed the line return pulse. The emitter of the transistor 19 is connected to a supply voltage source +V2 through a resistor 25.

The base of the transistor 19 is earthed through a resistor 26 and a variable resistor 27 in series, and is also connected to a supply voltage source +V3 through two resistors 28 and 29 in series. Across the resistor 29 is connected a protection diode 49.

The junction between the resistors 28 and 29 is connected to the emitter of a transistor 11 through a resistor 30, a variable resistor 31, and a capacitor 32 in series. The transistor 19 with the associated components serves to control the bias of the final stage of the video amplifier, which latter is constituted by two transistors 33 and 34 respectively PNP and NPN, mounted in a complementary symmetrical configuration.

The emitter of the transistor 33 is connected to the voltage supply source +V3 through a resistor 35, the colector is connected to a resistor 36 which is connected in series with another resistor 37 which is connected to the collector of the tran

sistor 34, the emitter of which is connected to

earth through a resistor 38. The bases of the two transistors 33 and 34

are connected together through a capacitor 39, and the base of the

transistor 34 is earthed through a resistor 42. The output from the

circuit is taken from the junction between the two resistors 36 and 37.

sistor 34, the emitter of which is connected to

earth through a resistor 38. The bases of the two transistors 33 and 34

are connected together through a capacitor 39, and the base of the

transistor 34 is earthed through a resistor 42. The output from the

circuit is taken from the junction between the two resistors 36 and 37. The base of the transistor 34 is fed with the video signal from the collector of the transistor 11 via an RC circuit comprising a resistor 40 and a capacitor 41 in parallel, which acts to compensate for phase displacements present in the circuit.

The base of the transistor 33 is connected to the voltage supply +V3 via a resistor 43 having a diode 45 in parallel with it and a resistor 44 having a diode 47 and a capacitor 46 in parallel with it. The diode 47 serves to supply a bias voltage equal to the voltage between the base and the emitter of the transistor 33 so as to keep the transistor 33 ready to conduct when it has to change from a non-conducting to a conducting state. The junction between the resistors 43 and 44 is earthed via a resistor 48.

The diode 45, like the diode 49 in parallel with the resistor 29, is a protection diode. The base of the transistor 33 is connected to earth through a resistor 50.

The operation of the amplifier circuit described with reference to FIG. 1 is as follows:

The circuit of the transistors 4 and 11 is a control circuit which controls the final stage comprising the circuit of the transistors 33 and 34 which are connected in a complementary symmetrical configuration, such that the transistor 34 conducts during the positive half-wave of the signal whilst the transistor 33 conducts during the negative half-wave. In order to avoid crossover distortion the two transistors are not completely cut off during the periods of non-conduction, but are kept in a slightly conductive condition, so that when the polarity of the wave form innerts and the conducting transistor becomes cut-off, there is no delay in the start of conduction of the previously nonconducting conducting transistor. The pass-band is obtained in this case by the negative feed-back of the amplifier provided by the RC network composed of the resistors 30 and 31 and the capacitor 32. The negative feed-back is taken from the output of the final stage to the input of the transistor 11, which controls the final stage.

The power supply to the final stage is provided by the voltage source +V3 which does not require much stabilisation because of the stabilisation control of the transistor 19. In fact, the voltage at the output of the amplifier, which is taken from the terminal 79 is also fed to a voltage divider formed by the resistors 29, 28, 26 and 27 and thus controls the base of the transistor 19, which generates from it and the stabilised voltage +V2 a bias control voltage. The comparison of the stabilised voltage +V2 with the output on the terminal 79 of the amplifier circuit only occurs during the line returns so as not to be tied to the type of picture transmitted, and for this reason the line return pulses drawn, in a known manner, from the horizontal deflection circuits are taken to the collector of the transistor 19, so that the transistor conducts only during the line return period.

In dependence on the degree of conduction of the transistor, and therefore on the voltage at its base, there appears across the filter network comprising the resistors 20, 17 and the capacitor 18 a voltage which is representative of the voltage present at the output of the first stage of the amplifier. This voltage, amplified by the transis

tor 11, is taken to the base of the transistor

34 for the purpose of controlling its bias. In this manner, optimum

stabilisation of the final stage is obtained without requiring complex

stabilisation circuits in the power supply circuits of the television

receiver.

tor 11, is taken to the base of the transistor

34 for the purpose of controlling its bias. In this manner, optimum

stabilisation of the final stage is obtained without requiring complex

stabilisation circuits in the power supply circuits of the television

receiver. From the above description, the advantages obtained over the prior art will be apparent to those skilled in the art particularly the avoidance of components which dissipate considerable power. This is possible because of the fact that the load impedance is greater than in known circuits and consequently the current in the stage is less. In the circuit shown in FIG. 1 the collector current is 8mA, whereas in previously known video amplifier circuits of this type the current is of the order of 30 mA: the improvement obtained can readily be appreciated. It is thus possible to use transistors of 1 W power dissipation instead of transistors of 5 W. Furthermore, because the power consumption of this stage is constant and sufficiently low, it is possible to draw the supply voltage from the horizontal deflection circuits, thus making use of a supply voltage which is already stabilised against the variations in consumption of the television receiver caused by the variations in the picture content and the control of contrast and brightness.

With respect to known circuits there is a further ecomony of components due to the fact that it is not necessary with this circuit, to provide compensation coils for the other frequencies at the output of the amplifier.

Wit

h regard to the

load impedance, this is greater than in previous circuits because of the

fact that the load resistance is provided largely by the resistance

presented by the transistor which is not conducting at any one line, and

the reactance is also greater because the parasitic capacities are

less.

h regard to the

load impedance, this is greater than in previous circuits because of the

fact that the load resistance is provided largely by the resistance

presented by the transistor which is not conducting at any one line, and

the reactance is also greater because the parasitic capacities are

less. The following table indicates the values of the circuit elements of the circuit of FIG. 1, this being an embodiment of the invention which has been tested and proven in practice to operate successfully.

| ______________________________________ |

| TABLE OF VALUES. RESISTORS CAPACITORS |

| ______________________________________ |

2 47 Ohm 9 10μF 3 10 Ohm 15 56 pF 5 1 K ohm 18 22 μF 6 2.7 K ohm 24 0.1 μF 8 1 K ohm 32 10 μF 10 220 Ohm 39 4.7 μF 13 680 Ohm 41 330 pF 14 100 Ohm 46 0.1 μF 16 6.8 K ohm INDUCTORS 17 33 K ohm 12 0.2 nH 20 10 K ohm TRANSISTORS 23 100 Ohm 4 BC 148 B 25 180 Ohm 11 BC 158 B 26 3.3 K ohm 19 BC 158 B 27 2.2 K ohm 33 MPS A92 28 47 K ohm 34 MPS A42 29 56 K ohm SUPPLIES 30 6.8 K ohm +V1 = 26 V 31 4.7 K ohm +V2 = 11 V 35 180 Ohm +V3 = 200 V 36 1 Ohm 37 1 K ohm 38 180 Ohm 40 2.7 K ohm 42 2.7 K ohm 43 2.2 M ohm 44 2.2 M ohm 48 56 K ohm 50 4.7 M ohm |

| ______________________________________ |

The embodiment illustrated in FIG. 2 has the advantages of the embodiment of FIG. 1, but achieves them in a simpler manner.

Referring

now to FIG. 2 there is shown an amplifier circuit having an input

terminal 51 which is connected by an input circuit comprising two

capacitors 52 and 53 in series with one another and two resistors 54 and

55 in series with one another and in parallel with the capacitors 52

and 53 to the base of an NPN transistor 85 connected in common emitter

configuration.

Referring

now to FIG. 2 there is shown an amplifier circuit having an input

terminal 51 which is connected by an input circuit comprising two

capacitors 52 and 53 in series with one another and two resistors 54 and

55 in series with one another and in parallel with the capacitors 52

and 53 to the base of an NPN transistor 85 connected in common emitter

configuration. The emitter of the transistor 85 is in effect connected to a source of biasing voltage (terminal 56) through a resistor 57 of low value. The collector of the transistor 85 is connected to the junction point of the cathodes of two diodes 58 and 59; the anode of the diode 59 is connected to one terminal of a resistor 60 the other terminal of which is connected to a supply potential +V3 and to the base of a second NPN transistor 61. The collector of the transistor 61 is connected via a resistor 62, to the supply potential +V3. The emitter of transistor 61 is connected to the anode of the diode 58, to one terminal of a resistor 63 and to an output terminal 64. The other terminal of the resistor 63 is connected to the base of the transistor 85 and, through a resistor 65, to earth.

In the circuit of FIG. 3 a positive supply potential +V1 feeds the electrodes of the emitter and the base of a PNP transistor 66 through, respectively, a resistor 67 and two resistors 68 and 69, in series the former of which is a variable resistor.

The collector of the transistor 66 is connected to the anode of a diode 70, whose cathode is connected to the base of a second PNP transistor 71 and to one terminal of a resistor 72 the other terminal of which is connected to earth. The collector of the transistor 71 is also connected to earth through a resistor 73. The emitter of the transistor 71 is connected to an output terminal 56, to the emitter of the transistor 66 through a resistor 74 and to the base of the transistor 66 through a resistor 75.

Between the emitter of the transistor 66 and earth are connected in series a Zener diode 76 and two normal diodes 77 and 78.

The following table shows, by way of example, the values of the circuit elements in one embodiment each of the circuits of FIG. 2 and FIG. 3 which have proven in practice to be operative.

| TABLE |

| ______________________________________ |

| RESISTORS CAPACITORS |

| ______________________________________ |

54 2.2 KΩ 52 18 pF 55 1.5 KΩ 53 18 pF 57 6.8 Ω 60 47 KΩ 62 1 KΩ DIODES. 63 47 KΩ 58 1N 4148 65 3.3 KΩ 59 1N 4148 67 1.5 KΩ 70 1N 4148 68 10 KΩ 76 ZV 12 69 10 KΩ 77 1N 4148 72 4.7 KΩ 78 1N 4148 73 560 Ω 74 2.2 KΩ TRANSISTORS 75 4.7 KΩ 85 MPSA 42 SUPPLY 61 MPSA 42 VOLTAGES 66 BC 308 +V1 26 V 71 BC 308 +V3 220 V |

| ______________________________________ |

The operation of the circuit of FIG. 2 is as follows:

The operation of the circuit of FIG. 2 is as follows: The video signal to be amplified is fed to the terminal 51 and reaches the base of the transistor 85 through the compensating network constituted by the elements 52, 53, 54 and 55. The controllable element 54 can be used for adjusting the gain of the amplifier to the required value.

The signal appears amplified on the collector of the transistor 85 and, neglecting for the moment the two diodes 58 and 59, it is fed to the base of the transistor 61 and appears, amplified, at the emitter, and therefore at the output terminal 64.

The load resistor 63 of the transistor 61 provides a strong negative feed-back which serves to stabilise the gain of the amplifier and increase its band-width; with the values indicated the voltage gain is of the order of 26 and the band-width greater than 4 MHz.

The effect of the input capacitance of the picture tube which is fed from the terminal 64, is largely neutralised by the low output impedance of the transistor 61 and also by the strong negative feed-back.

The capacitance in parallel with the resistor 60 proves to be less than that present at the terminal 64. In consequence it is possible to select for the resistor 60 a relatively high value (for example 50 KΩ), thus reducing the current consumed by the transistor 85, and therefore the colour dissipation effect of this transistor and the resistor 60.

Likewise the resistor 63 can be of 50 KΩ and therefore the current and the power dissipation of the transistor 61 are comparable to those in the circuit of the transistor 85. Furthermore, when the maximum current passes through the transistor 85, the minimum current passes through the transistor 61 and vice versa, so that the total current absorbed is relatively constant.

The circuit of FIG. 2 as described so far would function very well in the transients when the current in the transistor 85 drops suddenly; in the transients of opposite sign (when the current in the transistor 85 increases suddenly) the transistor 61 becomes slower in cutting off and the operation is less satisfactory; it is during these transients that the diode 58 comes into action and, by becoming conductive, allows the terminal 64 to follow directly the voltage at the collector of the transistor 85 as it falls, short circuiting for a time the transistor 61.

The diode 59 serves to compensate for the variation of the Vbe of the transistor 61 with temperature variations, and the resistor 62 serves to protect the transistor 61 from sudden overvoltages at the point +V3, due to picture tube discharges.

The terminal 56 could be simply conn

ected to a source of reference potential

(for example a Zener), which has a suitable value in relation to the

biasing voltage which is fed to the terminal 51 as well as the input

signal mentioned above. The circuit of FIG. 3 is a possible power supply

circuit for supplying an appropriate potential to the terminal 56 and,

at the same time, for compensating for variations in the characteristics

of the transistor 85 in dependence on the temperature.

ected to a source of reference potential

(for example a Zener), which has a suitable value in relation to the

biasing voltage which is fed to the terminal 51 as well as the input

signal mentioned above. The circuit of FIG. 3 is a possible power supply

circuit for supplying an appropriate potential to the terminal 56 and,

at the same time, for compensating for variations in the characteristics

of the transistor 85 in dependence on the temperature. The circuit of FIG. 3 is similar to that of the amplifier of FIG. 2, except that it uses PNP transistors and the emitter of the first transistor (transistor 66) is connected to a stabilised source represented by the three diodes 76, 77, 78; as known, by connecting in series a Zener (diode 76) and two or more normal silicon diodes (diodes 77, 78) a reference voltage can be obtained which varies little with the temperature.

The input voltage +V1 is the same as that which biases the input terminal 51 supplied with the video signal.

The voltage drift at the point 64 of the circuit of FIG. 2 is, for a temperature variation of + 15° to 50° C, of the order of 5 Volts if the point 56 of FIG. 2 is connected to a fixed voltage; and is of the order of about 1 Volt if the point 56 of FIG. 2 is connected to the point 56 of FIG. 3.

FIG. 4 is a block diagram of a part of a colour television receiver circuit using the circuits of FIG. 2 and FIG. 3. In FIG. 4 there are shown three amplifiers A1, A2, A3 identical to those of FIG. 2 for supplying the three colour picture tube with three primary signals R, G, B. The three amplifiers receive from a preamplifier-mixer P the three signals to be amplified. Thes

e

also receive from a biassing source S, identical to that of FIG. 3, a

stabilised and compensated bias voltage. The source S and the

preamplifier P are fed by the voltage +V1 ; the preamplifier P also receives the luminance signals Y and the chrominance signals C. The three amplifiers A1, A2, A3, are also fed by the non-stabilised voltage source +V3.

e

also receive from a biassing source S, identical to that of FIG. 3, a

stabilised and compensated bias voltage. The source S and the

preamplifier P are fed by the voltage +V1 ; the preamplifier P also receives the luminance signals Y and the chrominance signals C. The three amplifiers A1, A2, A3, are also fed by the non-stabilised voltage source +V3. The arrangement of FIG. 4, with the values indicated in the table, has a total consumption from the source +V3 of about 15 mA. Such a circuit arrangement lends itself easily to production by thick film techniques; it is possible to produce separately three identical modules A1, A2 and A3, and the module S, or they can all be produced as parts of a single circuit.

It

is also possible to produce on a single small silicone chip the same

four circuits in the form of a monolithic integrated circuit, in view of

the low overall dissipation; only the resistors 60 and 63 would need to

be left as separate circuit elements.

It

is also possible to produce on a single small silicone chip the same

four circuits in the form of a monolithic integrated circuit, in view of

the low overall dissipation; only the resistors 60 and 63 would need to

be left as separate circuit elements. The arrangement also lends itself to use with television picture tubes of the P.I.L. (Precision In Line) type, in which it is necessary to vary the bias of the cathodes; for this purpose it is sufficient to make the resistor 65 controllable.

The module P may be provided by one of the integrated circuits available on the market, for example, the type MOTOROLA MC1327.

The embodiments illustrated and described relate to video amplifier circuits for colour television receivers; it is however clear that circuits for other purposes (for example video amplifiers for black and white television receivers) can be made in accordance with the principles of the present invention without departing from the scope of the present invention as defined in the following claims.

INDESIT TC26SIL CHASSIS VV025C 30AX INTEGRAL THYRISTOR-RECTIFIER DEVICE

A semiconductor switching device comprising a silicon controlled rectifier (SCR) and a diode rectifier integrally connected in parallel with the SCR in a single semiconductor body. The device is of the NPNP or PNPN type, having gate, cathode, and anode electrodes. A portion of each intermediate N and P region makes ohmic contact to the respective anode or cathode electrode of the SCR. In addition, each intermediate region includes a highly conductive edge portion. These portions are spaced from the adjacent external regions by relatively low conductive portions, and limit the conduction of the diode rectifier to the periphery of the device. A profile of gold recombination centers further electrically isolates the central SCR portion from the peripheral diode portion.

That class of thyristors known as controlled rectifiers are semiconductor switches having four semiconducting regions of alternate conductivity and which employ anode, cathode, and gate electrodes. These devices are usually fabricated from silicon. In its normal state, the silicon controlled rectifier (SCR) is non-conductive until an appropriate voltage or current pulse is applied to the gate electrode, at which point current flows from the anode to the cathode and delivers power to a load circuit. If the SCR is reverse biased, it is non-conductive, and cannot be turned on by a gating signal. Once conduction starts, the gate loses control and current flows from the anode to the cathode until it drops below a certain value (called the holding current), at which point the SCR turns off and the gate electrode regains control. The SCR is thus a solid state device capable of performing the circuit function of a thyratron tube in many electronic applications. In some of these applications, such as in automobile ignition systems and horizontal deflection circuits in television receivers, it is necessary to connect a separate rectifier diode in parallel with the SCR. See, for example, W. Dietz, U. S. Pat. Nos. 3,452,244 and 3,449,623. In these applications, the anode of the rectifier diode is connected to the cathode of the SCR, and the cathode of the rectifier is connected to the SCR anode. Thus, the rectifier diode will be forward biased and current will flow through it when the SCR is reverse biased; i.e., when the SCR cathode is positive with respect to its anode. For reasons of economy and ease of handling, it would be preferable if the circuit function of the SCR and the associated diode rectifier could be combined in a single device, so that instead of requiring two devices and five electrical connections, one device and three electrical connections are all that would be necessary. In fact, because of the semiconductor profile employed, many SCR's of the shorted emitter variety inherently function as a diode rectifier when reverse biased. However, the diode rectifier function of such devices is not isolated from the controlled rectifier portion, thus preventing a rapid transition from one function to the other. Therefore, it would be desirable to physically and electrically isolate the diode rectifier portion from that portion of the device which functions as an SCR.

That class of thyristors known as controlled rectifiers are semiconductor switches having four semiconducting regions of alternate conductivity and which employ anode, cathode, and gate electrodes. These devices are usually fabricated from silicon. In its normal state, the silicon controlled rectifier (SCR) is non-conductive until an appropriate voltage or current pulse is applied to the gate electrode, at which point current flows from the anode to the cathode and delivers power to a load circuit. If the SCR is reverse biased, it is non-conductive, and cannot be turned on by a gating signal. Once conduction starts, the gate loses control and current flows from the anode to the cathode until it drops below a certain value (called the holding current), at which point the SCR turns off and the gate electrode regains control. The SCR is thus a solid state device capable of performing the circuit function of a thyratron tube in many electronic applications. In some of these applications, such as in automobile ignition systems and horizontal deflection circuits in television receivers, it is necessary to connect a separate rectifier diode in parallel with the SCR. See, for example, W. Dietz, U. S. Pat. Nos. 3,452,244 and 3,449,623. In these applications, the anode of the rectifier diode is connected to the cathode of the SCR, and the cathode of the rectifier is connected to the SCR anode. Thus, the rectifier diode will be forward biased and current will flow through it when the SCR is reverse biased; i.e., when the SCR cathode is positive with respect to its anode. For reasons of economy and ease of handling, it would be preferable if the circuit function of the SCR and the associated diode rectifier could be combined in a single device, so that instead of requiring two devices and five electrical connections, one device and three electrical connections are all that would be necessary. In fact, because of the semiconductor profile employed, many SCR's of the shorted emitter variety inherently function as a diode rectifier when reverse biased. However, the diode rectifier function of such devices is not isolated from the controlled rectifier portion, thus preventing a rapid transition from one function to the other. Therefore, it would be desirable to physically and electrically isolate the diode rectifier portion from that portion of the device which functions as an SCR.INDESIT TC26SIL CHASSIS VV025C 30AX LINE DEFLECTION WITH THYRISTOR SWITCH TECHNOLOGY OVERVIEW.

(Thyristor Horizontalsteuerung UND ABLENKUNG)

Description:

1. A horizontal deflection circuit for generating the deflection current in the deflection coil of a television picture tube wher

German Aus

legeschrift (DT-AS) No. 1,537,308 discloses a horizontal deflection circuit in which, for generating a periodic sawtooth current within the respective deflection coil of the picture tube, in a first branch circuit, the deflection coil is connected to a sufficiently large capacitor serving as a current source via a first controlled, bilaterally conductive switch which is formed by a controlled rectifier and a diode connected in inverse parallel. The control electrode of the rectifier is connected to a drive pulse source which renders the switch conductive during part of the sawtooth trace period. In that arrangement, the sawtooth retrace, i.e. the current reversal, also referred to as "commutation", is initiated by a second controlled switch.

As can be seen, such a circuit needs two different, separate inductive elements, it being known that inductive elements are expensive to manufacture and always have a certain volume determined by the electrical properties required.

The object of the invention is to reduce the amount of inductive elements required.

The invention is characterized in that the input inductor and the commutating inductor are combined in a unit designed as a transformer which is proportioned so that the open-circuit inductance of the transformer is essentially equal to the value of the input inductor, while the short-circuit inductance of the transformer is essentially equal to the value of the commutating inductor, and that the second switch is connected in series with the dc voltage source and a first winding of the transformer.

This solution has an added advantage in that, in mass production, both the open-circuit and the short-circuit inductance are reproducible with reliability.

According to another feature of the invention, the electrical isolation between the windings of the transformer is such that the transformer operates as an isolation transformer between the supply and the subcircuits connected to a second winding or to additional windings of the transformer. In this manner, the transformer additionally provides reliable mains isolation.

According to a further feature of the invention, the second switch is connected between ground and that terminal of the first winding of the transformer not connected to the supply potential. This simplifies the control of the switch.

According to a further feature of the invention, to regulate the energy supply, the second winding of the transf

The advantage gained by this measure lies in the fact that the control takes place on the side separated from the mains, so no separate isolation device is required for the gating of the third switch. Further details and advantages will be apparent from the following description of the accompanying drawings and from the claims. In the drawings,

FIG. 1 is a basic circuit diagram of the arrangement disclosed in German Auslegeschrift (DT-AS) No. 1,537,308;

FIG. 2 shows a first embodiment of the horizontal deflection circuit according to the invention, and

FIG. 3 shows a development of the horizontal deflection circuit according to the invention.

FIG. 1 shows the essential circuit elements of the horizontal deflection circuit known from the German Auslegeschrift (DT-AS) No. 1,537,308 referred to by way of introduction.

Connected in series with a dc voltage source UB is an input inductor Le and a bipolar, controlled switch S2. In the following, this switch will be referred to as the "second switch"; it is usually called the "commutating switch" to indicate its function.

In known circuits, the second switch S2 consists of a controlled rectifier and a diode connected in inverse parallel.

The second switch S

FIGS. 2 and 3 show the horizontal deflection circuit modified in accordance with the present invention. Like circuit elements are designated by the same reference characters as in FIG. 1.

FIG. 2 shows the basic principle of the invention. The two inductors Le and Lk of FIG. 1 have been replaced by a transformer U. To be able to serve as a substitute for the two inductors Le and Lk, the transformer must be proportioned in a special manner. Regardless of the turns ratio, the open-circuit inductance of the transformer is chosen to be essentially equal to the value of the input inductor Le, and the short-circuit inductance of the transformer is essentially equal to the value of the commutating inductor Lk.

To permit the second switch S2 to be utilized for the connection of the dc voltage source UB, it is included in the circuit of that winding U1 of the transformer connected to the dc voltage UB.

In principle, it is of no consequence for the operation of the switch S2 whether it is inserted on

In compliance with pertinent safety regulations, the transformer U may be designed as an isolation transformer and can thus provide mains separation, which is necessary for various reasons. It is known from German Offenlegungschrift (DT-OS) No. 2,233,249 to provide dc isolation by designing the commutating inductor as a transformer, but this measure is not suited to attaining the object of the present invention.

If the energy to be taken from the dc voltage source is to be controlled as a function of the energy needed in the horizontal deflection circuit and in following subcircuits, the embodiment of the horizontal deflection circuit of FIG. 3 may be used.

The circuit including the winding U2 of the transformer U contains a third controlled switch S3, which, too, is inserted on the grounded side of the winding U2 for the reasons mentioned above. This third switch S3, just as the second switch S2, is operated at the frequency of a horizontal oscillator HO, but a control circuit RS whose input l is fed with a controlled variable is inserted between the oscillator and the switch S3. Depending on this controlled variable, the controlled rectifier of the third switch S3 can be caused to turn on earlier. A suitable controlled variable containing information on the energy consumption is, for example, the flyback pulse capable of being taken from the high voltage generating circuit (not shown). Details of the operation of this kind of energy control are described in applicant's German Offenlegungsschrift (DT-OS) No. b 2,253,386 and do not form part of the present invention.

With mains isolation, the additional, third switch S3 shown here has the advantage of being on the side isolated from the mains and eliminates the need for an isolation device in the control lead of the controlled rectifier.

As an isolation transformer, the transformer U may also carry additional windings U3 and U4 if power is to be supplied to the audio output stage, for example; in addition, the first switch S1 may be gated via such an additional winding.

The points marked at the windings U1 and U2 indicate the phase relationship between the respective voltages. Connected in parallel with the winding U1 and the second switch S2 is a capacitor CE which completes the circuit for the horizontal-frequency alternating current; this serves in particular to bypass the dc voltage source or the electrolytic capacitors contained therein.

INDESIT TC26SIL CHASSIS VV025C 30AX Electron beam deflection circuit including thyristors Further Discussion and deepening of knowledge, Thyristor horizontal output circuits:

1. An electron beam deflection circuit for a cathode ray tube with electromagnetic deflection by means of a sawtooth current waveform having a trace portion and a retrace portion, said circuit comprising: a deflection winding; a first source of electrical energy formed by a first capacitor;

2. A deflection circuit as claimed in claim 1, wherein said amount of additional current is greater than or equal to 5 per cent of the peak-to-peak value of the current flowing through the deflection winding.

3. A deflection circuit as claimed in claim 1, wherein said means for drawing a substantial amount of additional current through said first switching means comprises a resistor connected in parallel to said first capacitor.

4. A deflection circuit as claimed in claim 1, wherein said means for drawing an additional current is formed by connecting said first and second energy sources in series so that the current charging said reactive circuit means forms the said additional current.

The present invention relates to electron beam deflection circuits including thyristors, such as silicon controlled rectifiers and relates, in particular, to horizontal deflection circuits for television receivers.

The present invention relates to electron beam deflection circuits including thyristors, such as silicon controlled rectifiers and relates, in particular, to horizontal deflection circuits for television receivers. The present invention constitutes an improvement in the circuit described in U.S. Pat. No. 3,449,623 filed on Sept. 6, 1966, this circuit being described in greater detail below with reference to FIGS. 1 and 2 of the accompanying drawings. A deflection circuit of this type comprises a first thyristor switch which allows the conenction of the horizontal deflection winding to a constant voltage source during the time interval used for the transmisstion of the picture signal and for applying this signal to the grid of the cathode ray tube (this interval will be termed the "trace portion" of the scan), and a second thyristor switch which provides the forced commutation of the first one by applying to it a reverse current of equal amplitude to that which passes through it from the said voltage source and thus to initiate the retrace during the horizontal blanking interval.

The present invention constitutes an improvement in the circuit described in U.S. Pat. No. 3,449,623 filed on Sept. 6, 1966, this circuit being described in greater detail below with reference to FIGS. 1 and 2 of the accompanying drawings. A deflection circuit of this type comprises a first thyristor switch which allows the conenction of the horizontal deflection winding to a constant voltage source during the time interval used for the transmisstion of the picture signal and for applying this signal to the grid of the cathode ray tube (this interval will be termed the "trace portion" of the scan), and a second thyristor switch which provides the forced commutation of the first one by applying to it a reverse current of equal amplitude to that which passes through it from the said voltage source and thus to initiate the retrace during the horizontal blanking interval. A undirectional reverse blocking triode type thyristor or silicon controlled rectifier (SCR), such as that used in the aformentioned circuit, requires a certain turn-off time between the instant at which the anode current ceases and the instant at which a positive bias may be applied to it without turning it on, due to the fact that there is still a high concentration of free carriers in the vicinity of the middle junction, this concentration being reduced by a process of recombination independently from the reverse polarity applied to the thyristor. This turn-off time of the thyristor is a function of a number of parameters such as the junction temperature, the DC current level, the decay time of the direct current, the peak level of the reverse current applied, the amplitude of the reverse anode to cathode voltage, the external impedance of the gate electrode, and so on, certain of these varying considerably from one thyristor to another.

A undirectional reverse blocking triode type thyristor or silicon controlled rectifier (SCR), such as that used in the aformentioned circuit, requires a certain turn-off time between the instant at which the anode current ceases and the instant at which a positive bias may be applied to it without turning it on, due to the fact that there is still a high concentration of free carriers in the vicinity of the middle junction, this concentration being reduced by a process of recombination independently from the reverse polarity applied to the thyristor. This turn-off time of the thyristor is a function of a number of parameters such as the junction temperature, the DC current level, the decay time of the direct current, the peak level of the reverse current applied, the amplitude of the reverse anode to cathode voltage, the external impedance of the gate electrode, and so on, certain of these varying considerably from one thyristor to another.In horizontal deflection circuits for television receivers, the flyback or retrace time is limited to approximately 20 percent of the horizontal scan period, the retrace time being in the case of the CCIR standard of 625 lines, approximately 12 microseconds and, in the case of the French standard of 819 lines, approximately 9 microseconds. During this relatively short interval, the thyristor has to be rendered non-conducting and the electron beam has to be returned to the origin of the scan. The first thyristor is blocked by means of a series resonant LC circuit which is subject to a certain number of restrictions (limitations as to the component values employed) due to the fact that, inter alia, it simultaneously determines the turn-off time of the circuit which blocks the thyristor and it forms part of the series resonant circuit which is to carry out the retrace. To obtain proper operation of the deflection circuit of the aforementioned Patent, especially when used for the French standard of 819 lines per image, the values of the components used have to subject to very close tolerances (approximately 2%), which results in high costs.

The improved deflection circuit, object o