WAS capable of driving CRT TUBES with 110° degree from 22 to 27 (fsq) Inches btw CRT of 30ax system to 45ax system and 17 to 21 inches format with 90° degree CRT TUBES, with few variants on the chassis and a Main +B Supply voltage fixed for all types to +140volt.

(Was a little surprise to see a color TV set fitted with an ancient PHILIPS 30AX Crt in an almost empty cabinet with this chassis bottom placed...........in an era of time where I have seen almost all "K" series chassis types filling up tv cabinets in the right way..........)

When I've seen for first time this chassis I had a laugh as like seeing a tv set with missing parts. The reality was indeed true no missing parts the chassis is the forerunner of the minimisation of tv chassis technology.

- POWER SUPPLY OPERATION In Brief :

The chopper circuit relies on feedback from the transformer to sustain oscillation. As with any chopper circuit, regulation is achieved by controlling the on/off timing of the chopper transistor. For control purposes the base of Tr7717 monitors the 140V h.t. supply. Its emitter is provided with a stable 6.2V reference voltage by zener diode D6715. The error voltage produced at the collector of Tr7717 drives Tr7719 which controls the current through the LED in the CNX62 optocoupler Tr7668. This device is used to provide mains isolation in the feedback path. The light-sensitive section of the optocoupler sets the d.c. voltage at the base of transistor Tr7685. At switch on the base of the chopper transistor Tr7687 is forward biased via R3686. It switches on and a sawtooth current flows through the primary winding 5-7 of the chopper transformer T5663. Tr7687 and T5663 form a blocking -oscillator circuit. Positive feedback via winding 1-9 on the transformer and D6672 drives Tr7687. When the transformer satu- rates, the drive is removed and Tr7687 switches off. The resonant circuit formed by C2664 with the primary winding of T5663 then oscillates, producing an overswing that switches Tr7687 on again. In normal operation Tr7687's switch -off timing is controlled by the pulse -width modulator consisting of transistor Tr7685 and its associated components. As mentioned above, the d.c. conditions at the base of Tr7685 are set by the conduction of the optocou- pler. The base of Tr7685 is also fed with a sawtooth L waveform that's developed across C2675, which with R3678/9 integrates the feedback from winding 1-11 on the transformer via D6667. In addition a negative reference voltage is established across C2690 by the action of D6689 and D6672 while Tr7687 is conductive. When the sawtooth waveform at the base of Tr7685 has risen to a sufficiently posi- tive value Tr7685 and Tr7686 switch on, removing the drive from Tr7687 which switches off very rapidly. The nominal operating frequency of the chopper circuit is 40kHz - it can vary between 20-60kHz. Over -voltage protection is provided by thyristor Ty6698 whose gate voltage is obtained from one of the rectifiers connected to the line output transformer. If the voltages in the line output stage are excessive Ty6698 conducts, placing a short-circuit across the 140V line. In this state the chopper circuit operates at a very low frequency of approximately 1.3kHz, with low voltage/current conditions. Current via D6696 holds Ty6698 on - switching the set off removes this short- circuit condition. In the unloaded state the circuit operating frequency is approximately 100Hz. In the standby mode thyristor Ty6727 is switched on to maintain the 5V supply to the control section without the need for a separate power supply. In this mode the control circuit provides drive to the anode of the optocoupler LED and the voltages delivered to rest of the set are far below the normal levels.

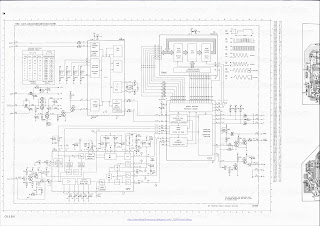

Fig. 1 shows the circuit. The most common problem is failure of the BUT11 chopper transistor Tr7687. In this event the mains fuse F1651 will usually be blackened or even shattered, with possible failure of one or more of the bridge rectifier diodes D6654-7. The surge limiter resistor R3654 will sometimes have failed as well. Remove the faulty BUT11 transistor and check D6663, D6664 and C2664. This capacitor can split: use a good quality 1.5kV capacitor in this position. In later sets the snubber network D6663/R3663/C2663 may be omitted, in which case the chopper transistor is type BUT11A. It's important that the correct type of transistor is used in this position. A BUT11 fitted in a set without the snubber network will fail again, but it's perfectly in order to fit a BUT11A in all sets. Transistors Tr7685 and Tr7686 should also be checked and, we've learnt from experience, it's best to replace the CNX62 optocoupler Tr7668 in the error signal feedback circuit Once replacement components have been fitted as neces- sary there's an official modification that should be carried out on earlier sets to reduce the likelihood of chopper tran- sistor failure. It consists of fitting a BYD33D diode with its anode to the collector of transistor Tr7686 and its cathode to the base of the chopper transistor Tr7687, and reconnecting R3687 so that one end remains connected to the base of Tr7686 while the other end is moved to connect with the base of Tr7687.

Fig. 1 shows the circuit. The most common problem is failure of the BUT11 chopper transistor Tr7687. In this event the mains fuse F1651 will usually be blackened or even shattered, with possible failure of one or more of the bridge rectifier diodes D6654-7. The surge limiter resistor R3654 will sometimes have failed as well. Remove the faulty BUT11 transistor and check D6663, D6664 and C2664. This capacitor can split: use a good quality 1.5kV capacitor in this position. In later sets the snubber network D6663/R3663/C2663 may be omitted, in which case the chopper transistor is type BUT11A. It's important that the correct type of transistor is used in this position. A BUT11 fitted in a set without the snubber network will fail again, but it's perfectly in order to fit a BUT11A in all sets. Transistors Tr7685 and Tr7686 should also be checked and, we've learnt from experience, it's best to replace the CNX62 optocoupler Tr7668 in the error signal feedback circuit Once replacement components have been fitted as neces- sary there's an official modification that should be carried out on earlier sets to reduce the likelihood of chopper tran- sistor failure. It consists of fitting a BYD33D diode with its anode to the collector of transistor Tr7686 and its cathode to the base of the chopper transistor Tr7687, and reconnecting R3687 so that one end remains connected to the base of Tr7686 while the other end is moved to connect with the base of Tr7687.

Before you switch on it's best to carry out a visual examination for dry -joints, particularly around the chopper trans- former T5663 and the mains input circuit, including the degaussing thermistor R3653. Dry -joints in these areas could have been the' cause of the original failure of the chopper transistor. I suggest that you then disconnect the supply to the line output stage by unplugging connector M17 and provide a dummy load in the form of a 60W lamp - connect it across the 140V h.t. supply's 47µF reservoir capacitor C2697. A meter set to read the h.t. voltage should also be connected here. Next connect the set to the mains supply via a variac which should be set to OV output. Switch on and slowly advance the output from the variac to about 90V. If all is well the lamp should by now be glowing and the meter should read about 140V. If the reading is low, at about 40V, the set may be in the standby condition (this applies to remote control sets). Try pressing the programme up or down button at the front of the set: this should bring it out of standby. If the supply now reads 140V, advance the setting of the variac SLOWLY, checking that the 140V supply remains 19V to audio Lc 220 220 12V 1k6 Tr7707 BC548 160 109621 constant. Should the h.t. voltage rise with the increased supply from the variac, switch off and check the circuit around the optocoupler. One possible cause of no regulation is broken print between R3659 and R3660.

Before you switch on it's best to carry out a visual examination for dry -joints, particularly around the chopper trans- former T5663 and the mains input circuit, including the degaussing thermistor R3653. Dry -joints in these areas could have been the' cause of the original failure of the chopper transistor. I suggest that you then disconnect the supply to the line output stage by unplugging connector M17 and provide a dummy load in the form of a 60W lamp - connect it across the 140V h.t. supply's 47µF reservoir capacitor C2697. A meter set to read the h.t. voltage should also be connected here. Next connect the set to the mains supply via a variac which should be set to OV output. Switch on and slowly advance the output from the variac to about 90V. If all is well the lamp should by now be glowing and the meter should read about 140V. If the reading is low, at about 40V, the set may be in the standby condition (this applies to remote control sets). Try pressing the programme up or down button at the front of the set: this should bring it out of standby. If the supply now reads 140V, advance the setting of the variac SLOWLY, checking that the 140V supply remains 19V to audio Lc 220 220 12V 1k6 Tr7707 BC548 160 109621 constant. Should the h.t. voltage rise with the increased supply from the variac, switch off and check the circuit around the optocoupler. One possible cause of no regulation is broken print between R3659 and R3660.If the h.t. supply remains low or doesn't come up at all, switch off and check the mains input circuitry and the 680kS2 start-up resistor R3686. One cause a failure to start is a defective degaussing thermistor (R3653) - it has two sections, one of which may provide surge limiting.

The correct replacement must be used - there are different types for 110° and 90° sets.

Engineers are often caught out by this, fitting the wrong type then spending hours trying to find out why the power supply won't work on load. Once the 140V supply has been established and is stable the variac can be brought up to provide the full mains supply. It should then be possible to switch off the set, disconnect the lamp and meter, reconnect socket M17 and check the set out. I've found this power supply repair procedure to be the safest way of ensuring that the minimum number of BUT11A transistors end up in the bin!

A faulty chopper transformer can cause repeated failure of the BUT11A transistor, but in my experience this is uncommon.

CHASSIS 2A The Line Output Stage:

Not many faults occur in the line output stage, which uses conventional circuitry. One point to note is that the line output transistor is type BU508V. A BU508A is not suitable and will fail within a very short time. Another common problem is failure of C2618. Its value depends on the screen size: the rating is 2kV. C2609, whose value is also dependent on screen size (voltage rating 2kV), can also be a problem. One case of line cramp at the right-hand side of the screen was caused by a defective line driver transformer. So far I've had to change the line output transformer in this chassis, but it does seem to suffer from dry -joints. These should be attended to as a matter of course. If, when the brightness setting is advanced, you have a blank raster with flyback lines check C2496 (22nF). When this capacitor goes open -circuit the luminance amplifier in the colour decoder chip is biased off. It's part of the beam limiting circuit. Timebase Generators The sync circuitry and timebase generators are contained within the well-known TDA2579 chip IC7535, which also provides sandcastle pulse and transmission identification outputs. No line drive with the h.t. supply present should lead to a check at pin 16 of this chip. This pin receives a start-up supply from the chopper circuit via R3556 (2700) and 83555 (5600) - during normal operation the chip is operated from a line output stage derived 11V line (+13a). The voltage is stabilised at 9V within the chip. If the voltage at pin 16 is low, check whether the external zener diode D6555 (BZX79/C12) is leaky or short-circuit. The chip itself could be faulty. If

removing the solder from pin 16 makes the 9V supply come up, replace the chip. Field Output The field output stage consists of a TDA3653 chip in 20 and 21in. models or a TDA3654 in larger -screen sets. The most common fault is for the chip to have failed. Whenever

removing the solder from pin 16 makes the 9V supply come up, replace the chip. Field Output The field output stage consists of a TDA3653 chip in 20 and 21in. models or a TDA3654 in larger -screen sets. The most common fault is for the chip to have failed. Wheneveryou have to fit a replacement, C2571 (100µF) and C2565 (390pF) must also be changed. Failure of these two capaci- tors can result in failure of the chip. C2565 is a small, plate - ceramic capacitor that's mounted on the print side of the board, between pins 1 and 5 of the i.c. If it's left out, a herringbone -type pattern may be seen on the screen followed by the rapid demise of the chip.

CHASSIS 2A Audio Stages:

The audio output chip is a TDA1013A. No problems here apart from occasional failure of the chip itself. Another possible cause of no sound is the headphone socket. The well-known TBA120S intercarrier sound chip is used (IC7111), with the interstation mute voltage being applied to pin 4. Between these two chips there's an HEF4053BP i.c. (IC7122) for switching between internal or external audio, the latter being fed via the scart socket. This chip has been known to fail, giving the no sound symptom: as a quick check pins 13 and 15 can be shorted together so. that the off -air sound is fed directly to the audio chip.

CHASSIS 2A Video Section:

A TDA3561A colour decoder chip is used. No colour or no luminance can be caused by the chip itself. With no luminance however first check the voltage at the contrast control pin 7. If the voltage here is nbgative or very low and not controllable, you might fmd that the trouble is caused by the previously mentioned capacitor C2496 in the line output stage. Failure of the 8.867MHz crystal X1269 is an occa- sional cause of no colour.

The only problems I've had with the c.r.t. base panel mounted RGB output stages have been dryjoints, giving intermittent colours.

CHASSIS 2A Tuner and IF Circuits; The tuner is normally a U343C or U344C depending on whether the set has remote control. It's understood that these have been superseded by later versions and that no modifications are required when fitting one of these as a replacement. The i.f. module U1040 is not considered to be a repairable unit. If the can is opened however you find that there's a standard TDA2541 chip and a SAW filter. I.F. problems are usually caused by the chip itself, which can be replaced.

There's a single transistor in the can, Tr7065 (BC548). It's the video emitter -follower.

The video signal leaves the i.f. can at pin 15, passing to the TDA5850 chip IC7526 which switches between internal and external video. This chip can fail, the result being loss of video signal. Make sure that the set hasn't been switched to external video via the remote control unit however!

CHASSIS 2A Teletext: A strange "net -curtain" effect can sometimes be seen on the screen with teletext models. It takes the form of fairly close, evenly -spaced faint bars that run from the top to the bottom of the screen.

The cause is the SAA5241 chip IC7770 on the teletext panel going high -resistance in its socket. To cure the trouble remove the chip and its holder then solder the chip into the board directly. Apart from this the teletext panel is very reliable. Odd dropouts can some- times be cured by careful adjustment of the 6MHz oscillator (trim C2802).

CHASSIS 2A Control Section: Few

faults occur in the control section. I've had stuck buttons on the control panel (Telefunken strip PCB), giving continuous programme changing etc.

faults occur in the control section. I've had stuck buttons on the control panel (Telefunken strip PCB), giving continuous programme changing etc. The most common problem is loss of memory due to failure of the nicad backup battery. When this has to be replaced the set must be retuned and the personal prefer- ence levels reset. Another occasional problem is failure to come out of the standby mode. If it's not due to the nicad battery, check that the BZX79/C4V7 zener diode D6734 isn't leaky. Conclusion It's hoped that these notes will be of help to engineers who are not too familiar with the 2A chassis. Notes on some later Philips chassis will follow in subsequent posts. Since the SOPS power supply circuit was used in several chassis (Born on K40) the notes on this in the present article also apply to the other related chassis.

1. A degaussing circuit for demagnetizing ferromagnetic components in a colour television receiver, said circuit comprising a rectifier circuit, the series arrangement of a degaussing coil and a first thermistor with a positive temperature coefficient, said series arrangement is connectable to at least one terminal of an alternating current voltage source, and furthermore comprising a resistance element means for contributing to heating of the first thermistor and for protecting said rectifier circuit comprising a second thermistor with a negative temperature coefficient which is connectable to a terminal of the alternating current voltage source and which is thermally coupled to the first thermistor with a positive temperature coefficient, the second thermistor being connected to said rectifier circuit in the receiver.

2. A circuit as claimed in claim 1, wherein said rectifier circuit comprises a rectifier having a current which also flows through the second thermistor, and the temperature of the second thermistor in the final operating state exceeds the temperature of the first thermistor.

3. A circuit as claimed in claim 2, wherein the second thermistor is connected in series with the rectifier circuit, the series arrangement thus formed being connected in parallel with the series arrangement of the degaussing coil and the first thermistor, and both series arrangements being connectable to the terminals of the alternating current voltage source.

4. A circuit as claimed in claim 2, wherein the series arrangement of the degaussing coil and the first thermistor is connected in parallel with the rectifier circuit, thereby forming two juctions, one of the junctions being connectable to a first terminal of the alternating current voltage source, the other juction being connected to the second thermistor, said second thermistor being connectable to the second terminal of the alternating current voltage source.

5. A circuit as claimed in claim 4, wherein the rectifier circuit comprises the Graetz type and a supply capacitor, and the product of the total ohmic resistance value of said parallel circuit in the cold state by the capacitance of said supply capacitor amounts to approximately 50% of the duration of the cycle of the voltage supplied by the alternating current voltage source.

6. A circuit as claimed in claim 2, wherein the second thermistor is connected in parallel with the series arrangement of the degaussing coil and the third thermistor, thereby forming a parallel circuit included in a supply lead of the rectifier, said rectifier comprising a full-wave rectifier of the type that substantially no direct current component can flow through said supply lead.

7. A circuit as claimed in claim 6, wherein the resistance value of the first thermistor in the cold state is more than 20 times lower than the ohmic resistance value of the degaussing coil.

8. A circuit as claimed in claim 6, characterized in that the rectifier circuit is of the Graetz-type and in that the product of the total ohmic resistance value of the said parallel circuit in the cold state by the capacitance of a supply capacitor being part of the rectifier circuit amounts to approximately 50% of the duration of the cycle of the voltage supplied by the a.c. voltage source.

9. A circuit as claimed in claim 6 wherein the rectifier circuit comprises the Graetz type.

Description:

The invention relates to a degaussing circuit for demagnetizing ferromagnetic components in a colour television receiver, comprising the series arrangement of a degaussing coil and a thermistor with a positive temperature coefficient, which series arrangement is connectable to at least one terminal of an a.c. voltage source and furthermore comprising a resistance element for contributing to heating of the thermistor.

Such a circuit is known from German Patent Specification No. 1,282,679. In order to reduce the current which flows through the degaussing coil at the end of the process, which current might produce an unwanted magnetic residual field in the ferromagnetic components to be demagnetized the thermistor is raised by means of a resistance element already present in the receiver to a higher temperature than the temperature which would be produced by the final current alone. For this results in a further increase in the resistance value of the thermistor.

In practice, in the known circuit a wire-wound resistor with a high permissible power can be used as resistance element, which wire-wound resistor is arranged in the immediate vicinity of the thermistor. However, the drawback of this measure is that the temperature of the wire-wound resistor cannot be controlled so very well so that the difference between the maximum permissible temperature of the thermistor and the ambient temperature cannot be checked with certainty. Consequently, the risk of overheating, which may be destructive to the thermistor, is not excluded. For this reason the circuit is no longer used.

It is an object of the invention to avoid said drawback of the known circuit whilst also the costs can be reduced and to that end the circuit according to the invention is characterized in that the resistance element is a (second) thermistor with a negative temperature coefficient which is connectable to a terminal of the a.c. voltage source and which is thermally coupled to the (first) thermistor with a positive temperature coefficient, the second thermistor being at the same time a protection resistance for a rectifier circuit in the receiver.

By means of heat transfer from the second to the first thermistor the latter attains, as wanted, a higher temperature. As the current through the second thermistor soon assumes a value which substantially does not depend on the degaussing circuit and which cannot exceed a given maximum, an equilibrium condition is obtained whereafter the temperature cannot increase to an appreciable extent so that the circuit according to the invention is safe. It will be noted that degaussing circuits having two thermally intercoupled thermistors having temperature coefficients of the opposite sign are known per se. U.S. Pat. No. 3,495,136 discloses a circuit which includes such a combination. The publication "IEEE Transactions on Broadcast and Television Receivers" Vol. BTR 1972, No. 1, pages 7 to 9 inclusive describes degaussing circuits in which a thermistor having a negative temperature coefficient is included in series with a supply voltage circuit. However, this thermistor is not thermally coupled to a thermistor having a positive temperature coefficient.

The invention will be further explained by way of non-limitative example with reference to the accompanying figures wherein

FIG. 1 shows a first construction of the circuit according to the invention,

FIG. 2 is a characteristic curve for explaining the invention,

FIG. 3 shows a second construction of the circuit according to the invention,

FIG. 4 shows a third construction of the circuit according to the invention,

FIGS. 5a and 5b are waveforms occurring therein and

FIG. 6 shows a fourth construction of the circuit according to the invention.

In FIG. 1 a degaussing coil 1 of a partly shown colour television receiver having a display tube of the shadow mask type is in series with a thermistor 2. The series arrangement of a second thermistor 7 and a rectifier circuit 8 is in parallel with the series arrangement of coil 1 and thermistor 2. Thermistor 7 has a negative temperature coefficient, whilst thermistor 2 has a positive temperature coefficient. The thermistors are thermally coupled because they have been brought into intimate contact with one another which is indicated in FIG. 1 by means of a double arrow. The parallel circuit constituted by components 1, 2, 7 and 8 can be connected through a switch 6 to the terminals 3 and 4 of an A.C. voltage source 5, for example the electric power supply mains.

Rectifier circuit 8 is diagrammatically shown in FIG. 1 as the series arrangement of a rectifier 9 and the parallel arrangements of a supply capacitor 10 of a high capacitance and a load 11. In operation the rectifier 9, which may consist in known manner of one or more diodes, rectifies the mains voltage of source 5 so that a D.C. voltage is available across capacitor 10 for feeding further parts of the receiver. A direct current flows through these parts. So load 11 represents a resistance whose value is equal to the ratio of said d.c. voltage to this direct current. Of course the receiver may comprise further supply circuits, not shown, for example for generating D.C. voltages of different values as well as one or more mains transformers.

In the cold condition thermistor 2 has a comparatively low resistance value (of approximately 25 Ohm), whilst thermistor 7 has a comparatively high value (of approximately 70 Ohm). Immediately after switch-on of mains switch 6 a large current flows through the thermistor 2 and coil 1 of approximately 5 A (peak value) or more. Because the series arrangement of the thermistor 7 and rectifier circuit 8 is in parallel with the source 5 the current therethrough is at the start independent of the degaussing current which flows through the branch 1, 2. The currents through both thermistors are able to heat them in a rather short time (approximately 10 seconds).

FIG. 2 shows on a logarithmic scale the resistance value R of thermistor 2 plotted as a function of the temperature T. Above the so-called Curie-temperature To (approximately 75° C.) the specific resistance of the material from which the thermistor 2 consists and consequently also its resistance value increases very steeply. In the absence of thermistor 7 thermistor 2 would attain, owing to self-heating, a temperature T1 (approximately 130° C.) with a corresponding resistance value R1 of approximately 20 kOhm, the amplitude of the degaussing current would then be brought to a value of approximately 20 mA.

When the temperature increases the resistance value of thermistor 7 decreases. The current through this thermistor is mainly determined by the values of the voltage across and of the current through load 11, which values, in the warm condition, are substantially independent of the temperature of thermistors 2 and 7 and of the degaussing circuit. For, they only depend on the operating conditions of the various parts of the receiver which are provided with supply voltage by circuit 8. Said current cannot, for example owing to the action of a safety circuit, exceed a given maximum.

The final value of thermistor 7 is low, for example, approximately 1 Ohm and a current of 1.5 A (r.m.s. value) and a temperature of 175° C. Thermistor 7 is chosen such that even for the smallest possible current through it, depending on load 11, it attains a final temperature which is higher than T1. Consequently, thermistor 7 delivers heat to thermistor 2. As a portion of the heat radiated by the thermistor 7 yet goes to the environment the final temperature of thermistor 2 will be lower than that of thermistor 7. Owing to the heat transfer thermistor 7 attains a final temperature T2 which is approximately 20° to 30° C. higher than T1. An equilibrium condition occurs wherein the final temperature of thermistor 7 is lower than the final temparature without thermal coupling to thermistor 2 and wherein both thermistors are approximately kept at said final temperatures by the final currents. This situation is stable and, consequently, safe: for an increase in temperature T1 causes a decrease in the current through thermistor 2 which opposes the increase in the temperature. It also prevents the temperature from rising too high which might cause the resistance value R to decrease. The final value R2 of thermistor 2 is higher than R1, namely approximately 60 kOhm and the final amplitude of the current through coil 1 is reduced to the desired value, i.e. less than 5 mA.

In the preceding the dissipation in coil 1 in the final condition is assumed to be negligibly small with respect to that in thermistor 2. This is justified by the fact that the ohmic resistance value (approximately 20 Ohm) of coil 1 is much lower than value R2 so that the output voltage drop across coil 1 is negligibly small.

Thermistor 7 is a safety resistor for rectifier circuit 8. Because prior to switch-on of mains switch 6 capacitor 10 is still uncharged a very large current would flow through rectifier 9 and capacitor 10 after switch-on if thermistor 7 would be absent. This might cause damage to these components and also to switch 6. It would also be possible that a fuse 12 which in FIG. 1 is included between switch 6 and the junction point of thermistors 2 and 7 would melt. The starting current is limited by thermistor 7 whilst the thermistor substantially produces no voltage drop in the hot condition.

Compared with the case wherein thermistor 7 is replaced by a linear resistor the circuit according to the invention means a considerable saving in energy. For, the final value of thermistor 7 is lower than the value of the linear resistance i.e. the above-mentioned starting value (approximately 70 Ohm) of thermistor 7 whereas the value of the rectified voltage across capacitor 10 is only decreased during the warming up time of thermistor 7.

There is an additional advantage, namely the fact that after switch-on of mains switch 6 the current derived by circuit 8 from source 5 grows gradually and not suddenly which attenuates the jump produced by circuit 1, 2.

FIG. 3 shows a second construction of the circuit according to the invention, with the same reference numerals as in FIG. 1 wherein the rectifier circuit 8 is in parallel with the series arrangement of coil 1 and thermistor 2, whilst thermistor 7 is included between mains switch 6 and the junction of thermistor 2 and circuit 8. In this construction thermistor 7 limits the switch-on value also for the degaussing current so that for both thermistors types must be chosen which each have a lower starting value than in the case of FIG. 1. In the final state there is substantially no difference between the two constructions.

It will be noted that in the two described constructions of the circuit thermistor 7 has a dual function, namely protecting the rectifier circuit 8 and increasing the final value of thermistor 2 and, consequently, reducing the final degaussing current, which means a saving compared with the case where the degaussing circuit is constructed in a known manner, for example with two thermally inter-coupled thermistors with positive temperature-coefficients, whilst thermistor 7 or a linear resistor in the same position is not coupled herewith.

In FIG. 4 thermistor 7 is in parallel with the series arrangement of degaussing coil 1 and thermistor 2. The circuit constituted by components 1, 2 and 7 can be connected through fuse 12 and switch 6 to terminal 3 of a.c. voltage source 5. In this example rectifier 9 is of the Graetz-type: four diodes 9a, 9b, 9c and 9d form a bridge in a diagonal whereof components 10 and 11 are included, whilst a point of the other diagonal is connected to that junction of series arrangement 1, 2 and thermistor 7 which is not connected to mains switch 6. The other point of said diagonal is connectable through switch 6 to the other terminal 4 of source 5.

In FIG. 4 thermistor 7 is in parallel with the series arrangement of degaussing coil 1 and thermistor 2. The circuit constituted by components 1, 2 and 7 can be connected through fuse 12 and switch 6 to terminal 3 of a.c. voltage source 5. In this example rectifier 9 is of the Graetz-type: four diodes 9a, 9b, 9c and 9d form a bridge in a diagonal whereof components 10 and 11 are included, whilst a point of the other diagonal is connected to that junction of series arrangement 1, 2 and thermistor 7 which is not connected to mains switch 6. The other point of said diagonal is connectable through switch 6 to the other terminal 4 of source 5.In the cold state thermistor 2 has a comparatively low resistance value (of approximately 4 Ohm), whereas thermistor 7 has a comparatively high value (of approximately 150 Ohm). Capacitor 10 has as yet no charge. In this circuit coil 1 has an ohmic resistance value of approximately 100 Ohm. Immediately after switch-on of mains switch 6, the voltage of the source 5 is substantially completely across the parallel circuit constituted by components 1, 2, 7. If this voltage has an effective value of 220 V then a current of approximately 3.1 A (peak value) flows through thermistor 2 and coil 1, whilst a current of approximately 2.1 A flows through thermistor 7 which in the beginning is independent of the degaussing current flowing through branch 1, 2.

FIG. 5a represents one cycle of the current which flows through rectifier 9, at the start of the procedure. Herein it is assumed that the frequency of the mains voltage is 50 Hz which corresponds to a cycle of 20 ms. When capacitor 10 is discharged diodes 9a and 9d or 9b and 9c respectively conduct during the entire half cycle, that is to say that opening angle thereof is equal to 10 ms.

After switch-on the degaussing current through coil 1 gradually decreases, on the one hand, because the resistance value of thermistor 2 becomes higher when the thermistor becomes warmer and on the other hand because capacitor 10 is being charged. In addition, when the temperature increases the resistance value of thermistor 7 decreases. The final value thereof is low, for example approximately 2 Ohm. As in FIG. 1 and 3, thermistor 2 attains a final temperature T2 which exceeds the final temperature T1 which would be attained by self-heating in the absence of thermistor 7, which causes the final valve of thermistor 2 to become higher. The final amplitude of the degaussing current is consequently reduced to the desired value. This final state is stable and, consequently, safe.

FIG. 5b represents one cycle of the current flowing through rectifier 9 at the end of the process. The value thereof depends on the value of load 11; in a given receiver a peak value of approximately 4A was measured at an opening angle for the rectifying diodes of approximately 3 ms. It will be noted that the degaussing current through coil 1 is substantially of the same form as the currents in FIG. 5a and 5b as the reactance of the coil at low frequencies may be neglected relative to the ohmic resistance value hereof. FIGS. 5a and 5b show that the shape of the current is substantially symmetrical relative to the zero value. A condition for this is that the decrease in the amplitude of the degaussing current does not take place too rapidly, which decrease is determined by the product of the resistance value of the circuit 1, 2, 7 and the capacitance of capacitor 10. Because the capacitance is determined by the permissible amplitude of the ripple voltage across load 11 said condition implies a minimum value for this resistance and, consequently, of the initial resistance value of thermistor 7 and of the ohmic resistance value of the degaussing coil, whilst maintaining the magnetic properties thereof. In the example of FIG. 4 capacitor 10 has a capacitance of 200 μuF whilst said resistance value is approximately 60 Ohm in the cold state so that said product is approximately equal to 12 ms, that is to say in the order of magnitude of 50 to 60 % of the duration of the cycle.

The reason why the shape of the current must be substantial symmetrical relative to the zero value, the negative and the positive peak values being consequently substantially equal to one another, is that the degaussing current should substantially not contain a direct current component, which component would generate an unwanted magnetic field. When using a Graetz-rectifier as is the case in FIG. 4, the degaussing current reverses its direction at each half cycle as the current alternatingly flows either through diodes 9b and 9c or through diodes 9d and 9a. A single-phase rectifier in which the current does not reverse may not be used for the construction of FIG. 4. FIG. 6 represents a rectifier of the voltage doubler type which may be used. Herein rectifier circuit 8 comprises two diodes 9a and 9b and two capacitors 10a and 10b. It is obvious that the degaussing current which also flows through capacitor 10b comprises no direct current component. It is also obvious that the circuit 1, 2, 7 may be included in the supply lead to terminal 4 which, of course, also applies to the construction in FIG. 4. It can be noted that the single-phase rectifier, shown in FIG. 3, produces a d.c. voltage drop across thermistor 7. Consequently, also in this construction, reference should be given a Graetz rectifier.

In FIGS. 4 and 6 the initial current is limited by components 1, 2 and, especially, 7. It will be noted that thermistor 2 always has a rather low voltage drop across it, both in FIG. 4 and in FIG. 6. For, at the beginning of the process the voltage of source 5 is found substantially fully across coil, 1, which has a much higher ohmic resistance value, whilst the voltage across the series circuit 1, 2 at the end of the process is low, as thermistor 7 which is now low-ohmic substantially short-circuits said series arrangement. The advantage thereof is that thermistor 2 may be much thinner than thermistor 2 in FIGS. 1 and 3, that is to say 0.5 to 0.7 mm instead of approximately 2 mm, which means a considerable saving in material. It is consequently cheaper. In addition, the dissipation is much lower and the loss of heat to the environment much lower. The preceding also applies with respect of thermistors which in known circuits are in series with the degaussing coil and which, at least at the beginning of degaussing must be able to withstand a high voltage.

PHILIPS 26CE2281 RUBENS CHASSIS 2A Composite thermistor component:

A component consisting of two coupled PTC thermistors with the first thermistor having a lower cold resistance than the second thermistor and the first thermistor having a higher resistance at the operating temperature than the second thermistor. According to the invention, the electric connection to the second thermistor is made directly by solely mechanical contacts to the surface of the ceramic thermistor body. This means a considerable simplification during manufacture, as the second thermistor need not be provided with electrode layers.

Inventors:

Belhomme, Charles J. G. (Brussels, BE) U.S. Philips Corporation (New York, NY)

1. A thermistor component comprising

a first positive temperature coefficient of resistance thermistor,

a second positive temperature coefficient of resistance thermistor thermally in contact with said first thermistor, said second thermistor having a resistance substantially higher than the resistance of said first thermistor in the unoperated condition, and said second thermistor having a resistance lower than the resistance of the first thermistor at an operating temperature, wherein said second thermistor contributes to heating of said first thermistor during operation,

electrical connection to said first thermistor applied through metallic contact layers on said first thermistor, and

electrical connection to said second thermistor applied solely by mechanical contacts to a surface of said second thermistor, wherein said first thermistor has contact layers at opposite major faces, and said second thermistor has opposite major faces free of contact layers.

2. A degaussing circuit having a thermistor component as claimed in claim 1, in which said first thermistor is connected in a series arrangement with a degaussing coil and an alternating mains supply, and said second thermistor is connected in parallel with said series arrangement.

3. A thermistor component comprising

a first positive temperature coefficient of resistance thermistor,

a second positive temperature coefficient of resistance thermistor thermally in contact with said first thermistor, said second thermistor having a resistance substantially higher than the resistance of said first thermistor in the unoperated condition, and said second thermistor having a resistance lower than the resistance of the first thermistor at an operating temperature, wherein said second thermistor contributes to heating of said first thermistor during operation,

electrical connection to said first thermistor applied through metallic contact layers on said first thermistor, and

electrical connection to said second thermistor applied solely by mechanical contacts to a surface of said second thermistor, wherein said mechanical contacts include contact springs in direct contact with a major face of said second thermistor, and wherein at least one of said contact springs is in contact with a contact layer on said first thermistor.

4. A thermistor component comprising

a first positive temperature coefficient of resistance thermistor,

a second positive temperature coefficient of resistance thermistor thermally in contact with said first thermistor, said second thermistor having a resistance substantially higher than the resistance of said first thermistor in the unoperated condition, and said second thermistor having a resistance lower than the resistance of the first thermistor at an operating temperature, wherein said second thermistor contributes to heating of said first thermistor during operation,

electrical connection to said first thermistor applied through metallic contact layers on said first thermistor, and

electrical connection to said second thermistor applied solely be mechanical contacts to a surface of said second thermistor, wherein said first and second thermistors each have a major face in contact with a feedthrough plate, wherein said mechanical contacts include contact springs in direct contact with a major face of said second thermistor, and wherein at least one of said contact springs is in contact with a contact layer on said first thermistor.

5. A thermistor component according to claim 1, wherein said first and second thermistors are ceramic.

6. A thermistor component according to claim 1, wherein said first thermistor has a Curie point of 75° C. and said second thermistor has a Curie point of 180° C.

7. A thermistor component comprising

a first positive temperature coefficient of resistance thermistor,

a second positive temperature coefficient of resistance thermistor thermally in contact with said first thermistor, said second thermistor having a resistance substantially higher than the resistance of said first thermistor in the unoperated condition, and said second thermistor having a resistance lower than the resistance of the first thermistor at an operating temperature, wherein said second thermistor contributes to heating of said first thermistor during operation,

electrical connection to said first thermistor applied through metallic contact layers on said first thermistor, and

electrical connection to said second thermistor applied solely by mechanical contacts to a surface of said second thermistor, wherein said first and second thermistors each have a major face in contact with a feedthrough plate, and wherein said first thermistor has contact layers at opposite major faces, and said second thermistor has opposite major faces free of contact layers.

Description:

The invention relates to a composite thermistor component comprising two thermistors having a positive temperature coefficient of the resistance, the thermistors being thermally coupled to one another, to a degaussing circuit in which the component is incorporated and to colour television receiver comprising a shadow-mask picture display tube and a degaussing circuit of this type.

Such a composite thermistor component, which is described in United Kingdom patent specification No. 1,531,277 comprises a first thermistor and a second thermistor which each have a positive temperature coefficient of resistance, the second thermistor having a resistance which is substantially higher than the resistance of the first thermistor when the thermistors are in the unoperated (cold) condition, the two thermistors being thermally coupled such that in operation the second thermistor contributes to the heating of the first thermistor and that the resistance of the second thermistor at the final operating temperature of the component is lower than the resistance of the first thermistor.

It is an object of the invention to considerably simplify the composite thermistor component and according to the invention it is characterized in that the electrical connection to the second thermistor is made directly by solely mechanical contacts to the surface of the ceramic thermistor body.

The present invention will be described without limitation by reference to the drawing figures wherein

FIG. 1 is a schematic representation of a circuit used for degaussing metal parts, and

FIG. 2 is a view of a structure in accordance with the present invention.

The composite thermistor component is inter alia used in a circuit for degaussing metal parts, particularly the inner shield and the shadow mask, of a colour television display tube. A first thermistor 2 is connected in a series arrangement with a degaussing coil 1 to a first (3) and second (4) terminal for an alternating mains supply (5) via a switch (6), the first thermistor having a positive temperature coefficient of resistance, and the second thermistor 7 has a positive temperature coefficient of resistance connected in parallel with the series arrangement of coil 1 and thermistor 2. The two thermistors are thermally coupled because they are in intimate contact with one another.

This is shown in FIG. 1 by means of an arrow.

The description and the drawing of the abovementioned United Kingdom patent specification give the impression that the two thermistors are contacted directly by means of the ceramic surfaces. For a person skilled in the art, the use of ceramic components having metallized areas of contact in an electrical circuit has, however, always been such a matter of course that the presence of such metallized areas of contact had been omitted from the description for the sake of simplicity.

As a matter of fact, contacting by way of the ceramic surface by mechanical contact only can only be effected on the parallel thermistor in the circuit, that is to say the thermistor which, in the unoperated condition, has the higher resistance, contributes to heating the other thermistor during operation and has at the prevailing temperature a resistance which is lower than that of the other thermistor.

The thermistor which is in series with the degaussing coil must be of a low resistance during the unoperated condition and the metallized layer which is in intimate contact therewith must be present on substantially the entire surface area. Contacting of the series thermistor body by solely mechanical contacts only directly to the surface of the thermistor body does not result in a useful component.

Relative to the component which is known from the United Kingdom patent specification No. 1,531,277, in which the second thermistor (7) is provided with a vacuum-deposited nickel-chromium nickel-chromium layer onto which a thin silver layer has been vacuum-deposited, which silver layer is reinforced with a silver paste, the second thermistor must be somewhat changed to obtain a composite component according to the invention having similar operating characteristics. The material must have a Curie point which is approximately 10° C. higher than that of the material used for the second thermistor in the United Kingdom patent specification No. 1,531,277 component in order to achieve this.

In FIG. 2, reference numerals 2 and 7 denote the thermistors which have been given the same reference numerals as in FIG. 1, that is to say 7 is the thermistor having a positive temperature coefficient and a resistance value which is higher than that of thermistor 2 when the thermistors are in the unoperated (cold) condition and a resistance value at the final operating temperature which is lower than the resistance value of thermistor 2.

Thermistor 2 is provided on each major surface by vacuum deposition with a 0.1 μm thick Ni-Cr layer, onto which a 0.3 μm thick silver layer and a 10 μm silver containing layer are deposited, the three superposed layers constituting a contact layer 11. Thermistor 7 is built-in without having been provided with a contact layer on either major surface. In the composite thermistor component, the major surface of the thermistor 7 which is opposed to the thermistor 2 bears directly against a silver-plated stainless steel plate 12, which is provided with a feed-through 9 to the circuit, and the silver-plated stainless plate 12 bears against the contact layer 11 on the opposed major surface of the thermistor 2. On both sides the silver-plated stainless steel contact springs 8 and 10 push against the thermistors, that is to say contact spring 8 is in direct contact with the ceramic surface of thermistor 7 and contact spring 10 is in direct contact with the contact layer 11 on thermistor 2.

In one embodiment thermistor 2 has a composition

Ba0,80 Ca0,10 Sr0,10 TiO3 +0,3 mole % TiO2 +0,4 mole % Sb2 O3 and 0,08 mole % MnO.

This thermistor has a resistance value of approximately 40 Ohm at 25° C., the Curie point being 75° C.

Thermistor 7 has the composition:

B0,70 Ca0,10 Pb0,20 TiO3 +3 mol % TiO2 +0,4 mol % Sb2 O3 +0,08 mol % MnO.

This material has a Curie point of 180° C. The resistance value of the thermistor at 25° C. was not determined without contact layers, which is difficult to achieve, but with vacuum-deposited contact layers, a resistance of 50 to 400 Ohm then been measured.

In the construction of the thermistor as described in United Kingdom patent specification No. 1,531,277, provided with vacuum-deposited NiCr+Ag and a silver-containing layer, material was used having a Curie point of 170° C. and a resistance of the thermistor at 25° C. of 800-4000 Ohm. The relevant composition was:

Ba0,72 Ca0,10 Pb0,18 TiO3 +0,3 mol % TiO2 +0,4 mole % Sb2 O3 +0,08 mole % MnO.

Chrominance + Luminance with TDA3561A,

GENERAL DESCRIPTION

The TDA3561A is a dec

and demodulation of PAL signals. Furthermore it contains a luminance amplifier, an RGB-matrix and amplifier. These

amplifiers supply output signals up to 5 V peak-to-peak (picture information) enabling direct drive of the discrete output

stages. The circuit also contains separate inputs for data insertion, analogue as well as digital, which can be used for

text display systems (e.g. (Teletext/broadcast antiope), channel number display, etc. Additional to the TDA3560, the

circuit includes the following features:

· The peak white limiter is only active during the time that the 9,3 V level at the output is exceeded. The start of the limiting function is delayed by one line period. This avoids peak white limiting by test patterns which have abrupt

transitions from colour to white signals.

· The brightness control is obtained by inserting a variable pulse in the luminance channel. Therefore the ratio of

brightness variation and signal amplitude at the three outputs will be identical and independent of the difference in gain

of the three channels. Thus discolouring due to adjustment of contrast and brightness is avoided.

· Improved suppression of the internal RGB signals when the device is switched to external signals, and vice versa.

· Non-synchronized external RGB signals do not disturb the black level of the internal signals.

· Improved suppression of the residual 4,4 MHz signal in the RGB output stages.

· Cascoded stages in the demodulators and burst phase detector minimize the radiation of the colour demodulator

inputs.

· High current capability of the RGB outputs and the chrominance output.

The function is described against the corresponding pin

number.

1. + 12 V power supply

The circuit gives good operation in a supply voltage range

between 8 and 13,2 V provided that the supply voltage for

the controls is equal to the supply voltage for the

TDA3561A. All signal and control levels have a linear

dependency on the supply voltage. The current taken by

the device at 12 V is typically 85 mA. It is linearly

dependent on the supply voltage.

2. Control voltage for identification

correct operation. The voltages available under various

signal conditions are given in the specification.

3. Chrominance input

The chroma signal must be a.c.-coupled to the input.

Its amplitude must be between 55 mV and 1100 mV

peak-to-peak (25 mV to 500 mV peak-to-peak burst

signal). All figures for the chroma signals are based on a

colour bar signal with 75% saturation, that is the

burst-to-chroma ratio of the input signal is 1 : 2,25.

4. Reference voltage A.C.C. detector

This pin must be decoupled by a capacitor of about 330

nF. The voltage at this pin is 4,9 V.

5. Control voltage A.C.C.

The A.C.C. is obtained by synchronous detection of the

burst signal followed by a peak detector. A good noise

immunity is obtained in this way and an increase of the

colour for weak input signals is prevented. The

recommended capacitor value at this pin is 2,2 mF.

6. Saturation control

The saturation control range is in excess of 50 dB.

The control voltage range is 2 to 4 V. Saturation control is

a linear function of the control voltage.

When the colour killer is active, the saturation control

voltage is reduced to a low level if the resistance of the

external saturation control network is sufficiently high.

Then the chroma amplifier supplies no signal to the

demodulator. Colour switch-on can be delayed by proper

choice of the time constant for the saturation control

setting circuit.

When the saturation control pin is connected to the power

supply the colour killer circuit is overruled so that the colour

signal is visible on the screen. In this way it is possible to

adjust the oscillator frequency without using a frequency

counter (see also pins 25 and 26).

7. Contrast control

The contrast control range is 20 dB for a control voltage

change from + 2 to + 4 V. Contrast control is a linear

function of the control voltage. The output signal is

suppressed when the control voltage is 1 V or less. If one

or more output signals surpasses the level of 9 V the peak

white limiter circuit becomes active and reduces the output

signals via the contrast control by discharging C2 via an

internal current sink.

8. Sandcastle and field blanking input

The output signals are blanked if the amplitude of the input

pulse is between 2 and 6,5 V. The burst gate and clamping

circuits are activated if the input pulse exceeds a level of

7,5 V.

The higher part of the sandcastle pulse should start just

after the sync pulse to prevent clamping of video signal on

the sync pulse. The width should be about 4 ms for proper

A.C.C. operation.

9. Video-data switching

an input pulse between 1 V and 2 V. In that condition, the

internal RGB signals are switched off and the inserted

signals are supplied to the output amplifiers. If only normal

operation is wanted this pin should be connected to the

negative supply. The switching times are very short

(< 20 ns) to avoid coloured edges of the inserted signals

on the screen.

10. Luminance signal input

The input signal should have a peak-to-peak amplitude of

0,45 V (peak white to sync) to obtain a black-white output

signal to 5 V at nominal contrast. It must be a.c.-coupled to

the input by a capacitor of about 22 nF. The signal is

clamped at the input to an internal reference voltage.

A 1 kW luminance delay line can be applied because the

luminance input impedance is made very high.

Consequently the charging and discharging currents of the

coupling capacitor are very small and do not influence the

signal level at the input noticeably. Additionally the

coupling capacitor value may be small.

11. Brightness control

The black level of the RGB outputs can be set by the

voltage on this pin (see Fig.5). The black level can be set

higher than 4 V however the available output signal

amplitude is reduced (see pin 7). Brightness control also

operates on the black level of the inserted signals.

12, 14, 16. RGB outputs

The output circuits for red, green and blue are identical.

Output signals are 5,25 V (R, G and B) at nominal input

signals and control settings. The black levels of the three

outputs have the same value. The blanking level at the

outputs is 2,1 V. The peak white level is limited to 9,3 V.

When this level exceeded the output signal amplitude is

reduced via the contrast control (see pin 7).

13, 15, 17. Inputs for external RGB signals

The external signals must be a.c.-coupled to the inputs via

a coupling capacitor of about 100 nF. Source impedance

should not exceed 150 W. The input signal required for

a 5 V peak-to-peak output signal is 1 V peak-to-peak.

At the RGB outputs the black level of the inserted signal is

identical to that of normal RGB signals. When these inputs

are not used the coupling capacitors have to be connected

to the negative supply.

18, 19, 20. Black level clamp capacitors

The black level clamp capacitors for the three channels are

connected to these pins. The value of each capacitor

should be about 100 nF.

21, 22. Inputs (B-Y) and (R-Y) demodulators

The input signal is automatically fixed to the required level

by means of the burst phase detector and A.C.C.

generator which are connected to pin 21 and pin 22. As the

burst (applied differentially to those pins) is kept constant

by the A.C.C., the colour difference signals automatically

have the correct value.

23, 24. Burst phase detect

or outputs

At these pins the output of the burst phase detector is

filtered and controls the reference oscillator. An adequate

catching range is obtained with the time constants given in

the application circuit (see Fig.6).

25, 26. Reference oscillator

The frequency of the oscillator is adjusted by the variable

capacitor C1. For frequency adjustment interconnect pin

21 and pin 22. The frequency can be measured by

connecting a suitable frequency counter to pin 25.

28. Output of the chroma amplifier

Both burst and chroma signals are available at the output.

The burst-to-chroma ratio at the output is identical to that

at the input for nominal control settings. The burst signal is

not affected by the controls. The amplitude of the input

signal to the demodulator is kept constant by the A.C.C.

Therefore the output signal at pin 28 will depend on the

signal loss in the delay line.

PHILIPS 26CE2281 CHASSIS 2A Switched-mode self oscillating supply voltage circuit:PHILIPS POWER SUPPLY (SOPS - Self Oscillating Power Supply)

A switched-mode self-oscillating supply voltage circuit for converting an input voltage into an output d.c. voltage which is substantially independent of variations of the input voltage and/or a load connected to the output voltage. The circuit comprises a first controllable switch connected in series with a transformer winding and a second controllable switch for turning-off the first switch. The conduction period of the first switch is controlled by means of a control voltage present on a control electrode of the second switch. The circuit can be switched-over to a stand-up state in which the energy supplied to the load is reduced to zero. A starting network is connected between the input voltage and the second switch so that the current therein flows through the second switch during the period of time this switch conducts and does not flow to the control electode of the first switch in the stand-by state.

1. A switched-mode self-oscillating supply voltage circuit for converting an input voltage into an output d.c. voltage which is substantially independent of variations of the input voltage and/or of a load connected to the terminals of the output voltage, comprising a transformer having a primary and a feedback winding, a first controllable switch connected in series with the primary winding, the series arrangement thus formed being coupled between terminals for the input voltage, a second controllable switch coupled via a turn-off capacitor to the control electrode of the first switch to turn it off, means coupling the feedback winding to said control electrode, a transformer winding being coupled via a rectifier to an output capacitor having terminals which supply the output voltage, an output voltage-dependent control voltage being present on a control electrode of the second switch for controlling the conduction period of the first switch, the circuit being switchable between an operating state and a stand-by state in which relative to the operating state the supply energy supplied to the load is considerably reduced, a starting network connected to a terminal for the input voltage, means for adjusting the control voltage in the stand-by state to a value at which the first controllable switch is cut-off, a connection which carries current during the conduction period for the second controllable switch being provided between the starting network and said second switch, and means providing a connection between the starting network and the control electrode of the first switch, which connection does not carry current in the stand-by state.

1. A switched-mode self-oscillating supply voltage circuit for converting an input voltage into an output d.c. voltage which is substantially independent of variations of the input voltage and/or of a load connected to the terminals of the output voltage, comprising a transformer having a primary and a feedback winding, a first controllable switch connected in series with the primary winding, the series arrangement thus formed being coupled between terminals for the input voltage, a second controllable switch coupled via a turn-off capacitor to the control electrode of the first switch to turn it off, means coupling the feedback winding to said control electrode, a transformer winding being coupled via a rectifier to an output capacitor having terminals which supply the output voltage, an output voltage-dependent control voltage being present on a control electrode of the second switch for controlling the conduction period of the first switch, the circuit being switchable between an operating state and a stand-by state in which relative to the operating state the supply energy supplied to the load is considerably reduced, a starting network connected to a terminal for the input voltage, means for adjusting the control voltage in the stand-by state to a value at which the first controllable switch is cut-off, a connection which carries current during the conduction period for the second controllable switch being provided between the starting network and said second switch, and means providing a connection between the starting network and the control electrode of the first switch, which connection does not carry current in the stand-by state.2. A supply voltage circuit as claimed in claim 1, further comprising a resistor included between the connection of the starting network to the second switch and a turn-off capacitor present in the connection to the control electrode of the first switch.

3. A supply voltage circuit as claimed in claim 2, characterized in that the second controllable switch comprises a thyristor having a main current path included in the control electrode connection of the first controllable switch, said thyristor having a first control gate electrode for adjusting the turn-off instant of the first switch and a second control electrode to which the starting network and the resistor are connected.

4. A supply voltage circuit as claimed in claim 1, characterized in that a resistor is included in the connection to the control electrode of the second controllable switch so that a current flows through said resistor in the stand-by state of a value sufficient to cut-off the first controllable switch.

Such a supply voltage circuit is disclosed in German Patent Application No. 2,651,196. With this prior art circuit supply energy can be applied in the operating state to the different portions of a television receiver. In the stand-by state the majority of the output voltages of the circuit are so low that the receiver is substantially in the switched-off condition. In the prior art circuit the starting network is formed by a resistor connected to the unstabilized input voltage and through which on turn-on of the circuit a current flows via the feedback winding to the control electrode of the first controllable switch, which is a switching transistor, and brings it to and maintains it in the conductive state, as a result of which the circuit can start.

In the stand-by state the transistor is non-conducting in a large part of the period of the generated oscillation so that little energy is stored in the transformer. However, the starting resistor is connected via a diode to the second controllable switch, which is a thyristor. As the sum of the voltages across these elements is higher than the base-emitter threshold voltage of the transistor, the diode and the thyristor cannot simultaneously carry current. This implies that current flows through the starting resistor to the base of the transistor via the feedback winding after a capacitor connected to the feedback winding has been charged.

The invention has for its object to provide an improved circuit of the same type in which in the stand-by state the supply energy applied to the load is reduced to zero. The prior art circuit cannot be improved in this respect without the use of mechanical switches, for example relays. According to the invention, the switched-mode self-oscillating supply voltage circuit does not comprise such relays and is characterized in that it further comprises means for adjusting the control voltage in the stand-by state to a value at which the first controllable switch is cut-off. A connection which carries current during the conduction period of the second controllable switch is provided between the starting network and said second switch while a connection present between the starting network and the control electrode of the first switch does not carry current in the stand-by state.

The invention is based on the recognition that the prior art supply voltage circuit cannot oscillate, so that the energy supplied by it is zero, if the control voltage obtains a value as referred to, while the starting network is connected in such a manner that in the stand-by state no current can flow through it to the control electrode of the first controllable switch.

It should be noted that in the said German Patent Application the starting network is in the form of a resistor which is connected to an unstabilized input d.c. voltage. It is, however, known, for example, from German Patent Specification No. 2,417,628 to employ for this purpose a rectifier network connected to an a.c. voltage from which the said input d.c. voltage is derived by rectification.

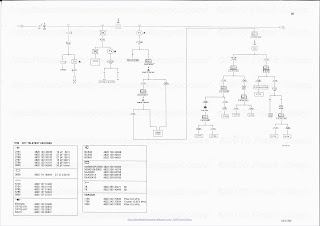

The invention will now be further described by way of example with reference to the accompanying drawing, which shows a basic circuit diagram of a switched-mode self-oscillating supply voltage circuit.

The self-oscillating supply circuit shown in the FIGURE comprises a npn-switching transistor Tr1 having its collector connected to the primary winding L1 of a transformer T, while the emitter is connected to ground via a small resistor R1, for example 1.5 Ohm. Resistor R1 is decoupled for the high frequencies by means of a 150 nF capacitor C1. One end of winding L1 is connected to a conductor which carries an unstabilized input d.c. voltage V B of, for example, 300 V. Voltage V B has a negative rail connected to ground and is derived from the electric power supply by rectification. One end of a feedback winding L2 is connected to the base of transistor Tr1 via the parallel arrangement of a small inductance L3 and a damping resistor R2. A terminal of a 47 μF capacitor C2 is connected to the junction of the elements L2, L3 and R2. The series arrangement of a diode D1 and a 2.2 Ohm-limiting resistor R3 is arranged between the other terminal of capacitor C2 and the other end of winding L2 and the series arrangement of a resistor R4 of 12 Ohm and a diode D2 is arranged between the same end of winding L2 and the emitter of transistor Tr1. A 150 nF capacitor C3 is connected in parallel with diode D2. The anode of diode D1 is connected to that end of winding L2 which is not connected to capacitor C2, while the anode of diode D2 is connected to the emitter of transistor Tr1. In the FIGURE the winding sense of windings L1 and L2 is indicated by means of dots.

The junction of capacitor C2 and resistor R3 is connected to a 100 Ohm resistor R5 and to the emitter of a pnp-transistor Tr2. The base of transistor Tr2 is connected to the other terminal of resistor R5 and to the collector of an npn-transistor Tr3, whose emitter is connected to ground. The base of Tr3 is connected to the collector of transistor Tr2. Transistors Tr2 and Tr3 form an artificial thyristor, i.e. a controllable diode whose anode is the emitter of transistor Tr2 while the cathode is the emitter of transistor Tr3. The base of transistor Tr2 is the anode gate and the base of transistor Tr3 is the cathode gate of the thyristor formed. Between the last-mentioned base and the emitter of transistor Tr1 there is arranged the series network of a 2.2 kOhm resistor R6 with the parallel arrangement of a 2.2 kOhm resistor R7 and a 100 μF capacitor C4. The series arrangement of a diode D11 and a 220 Ohm limiting resistor R19 is arranged between the junction of components R6, R7 and C4 and the junction of components C2, L2, R2 and L3. The cathode of diode D11 is connected to capacitor C2.

Because of the feedback the described circuit oscillates independently as soon as the steady state is achieved. It will be described hereinafter how this state is obtained. During the time transistor Tr1 conducts the current flowing through the resistor R1 increases linearly. The resistor R4 then partly determines the base current of transistor Tr1. Capacitor C4 and resistor R7 form a voltage source the voltage of which is subtracted from the voltage drop across resistor R1. As soon as the voltage on the base of transistor Tr3 is equal to approximately 0.7 V this transistor becomes conductive, as a result of which the thyristor formed by transistors Tr2 and Tr3 becomes rapidly conductive and remains so. Across capacitor C2 there is a negative voltage by means of which transistor Tr1 is turned off. The inverse base current thereof flows through thyristor Tr2, Tr3. This causes charge to be withdrawn from capacitor C2, while the charge carriers stored in transistor Tr1 are removed with the aid of inductance L3. As soon as the collector current of transistor Tr1 has been turned off, the voltage across winding L2 reverses its polarity, which current recharges the capacitor. Now the voltage at the junction of components C2, R3 and R5 is negative, causing thyristor Tr2, Tr3 to extinguish.

Because of the feedback the described circuit oscillates independently as soon as the steady state is achieved. It will be described hereinafter how this state is obtained. During the time transistor Tr1 conducts the current flowing through the resistor R1 increases linearly. The resistor R4 then partly determines the base current of transistor Tr1. Capacitor C4 and resistor R7 form a voltage source the voltage of which is subtracted from the voltage drop across resistor R1. As soon as the voltage on the base of transistor Tr3 is equal to approximately 0.7 V this transistor becomes conductive, as a result of which the thyristor formed by transistors Tr2 and Tr3 becomes rapidly conductive and remains so. Across capacitor C2 there is a negative voltage by means of which transistor Tr1 is turned off. The inverse base current thereof flows through thyristor Tr2, Tr3. This causes charge to be withdrawn from capacitor C2, while the charge carriers stored in transistor Tr1 are removed with the aid of inductance L3. As soon as the collector current of transistor Tr1 has been turned off, the voltage across winding L2 reverses its polarity, which current recharges the capacitor. Now the voltage at the junction of components C2, R3 and R5 is negative, causing thyristor Tr2, Tr3 to extinguish. Secondary windings L4, L5 and L6 are provided on the core of transformer T with the indicated winding senses. When transistor Tr1 is turned off, a current which recharges a smoothing capacitor C5, C6 or C7 via a rectifier D3, D4 or D5 flows through each of these windings. The voltages across these capacitors are the output voltages of the supply circuit for loads connectable thereto. These loads, which are not shown in the FIGURE, are, for example, portions of a television receiver.

Secondary windings L4, L5 and L6 are provided on the core of transformer T with the indicated winding senses. When transistor Tr1 is turned off, a current which recharges a smoothing capacitor C5, C6 or C7 via a rectifier D3, D4 or D5 flows through each of these windings. The voltages across these capacitors are the output voltages of the supply circuit for loads connectable thereto. These loads, which are not shown in the FIGURE, are, for example, portions of a television receiver.In parallel with winding L1 there is the series network of a 2.2 nF tuning capacitor C8 and a 100 Ohm limiting resistor R8. The anode of a diode D6 is connected to the junction of components R8 and C8, while the cathode is connected to the other terminal of resistor R8. Winding L1 and capacitor C8 form a resonant circuit across which an oscillation is produced after windings L4, L5 and L6 have become currentless. At a later instant the current through circuit L1, C8 reverses its direction. As a result thereof a current is generated in winding L2 which flows via diode D2 and resistor R4 to the base of transistor Tr1 and makes this transistor conductive and maintains it in this state. The dissipation in resistor R8 is reduced by means of diode D6. A clamping network formed by the parallel arrangement of a 22 kOhm resistor R9 and a 120 nF capacitor C9 is arranged in series with a diode D7. This whole assembly is in parallel with winding L1 and cuts-off parasitic oscillations which would be produced during the period of time in which transistor Tr1 is non-conductive. The output voltages of the supply circuit are kept substantially constant in spite of variations of voltage V B and/or the loads, thanks to a control of the turning-on instant of thyrisistor Tr2, Tr3. For this purpose the emitter of a light-sensitive transistor Tr4 is connected to the base of transistor

Tr3. The collector of transistor Tr4 is connected via a resistor R10 to the conductor which carries the voltage V B and to a Zener diode Z1 which has a positive voltage of approximately 7.5 V, while the base is unconnected. The other end of diode Z1 is connected to ground. A light-emitting diode D8, whose cathode is connected to the collector of an npn-transistor Tr5, is optically coupled to transistor Tr4. By means of a potentiometer R11 the base of transistor Tr5 can be adjusted to a d.c. voltage which is derived from the voltage V 0 of approximately 130 V across capacitor C6. The anode of diode D8 is connected to a d.c. voltage V 1 of approximately 13 V. A resistor R12 is also connected to voltage V 1 , the other end of the resistor being connected to the emitter of transistor Tr5, to the cathode of a Zener diode Z2 which has a voltage of approximately 7.5 V and to a smoothing capacitor C10. The other ends of diode Z2 and capacitor C10 are connected to ground. Voltage V1 can be generated by means of a transformer connected to the electric AC supply and a rectifier, which are not shown for the sake of simplicity, more specifically for a remote control to which constantly supply energy is always applied, even when the majority of the components of the receiver in what is referred to as the stand-by state are not supplied with supply energy.