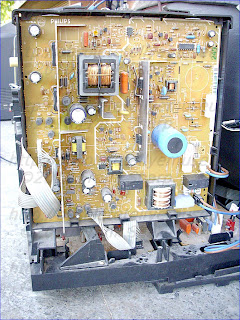

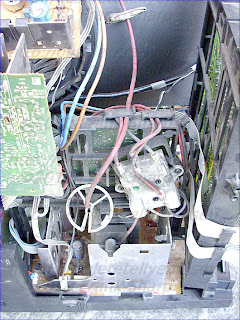

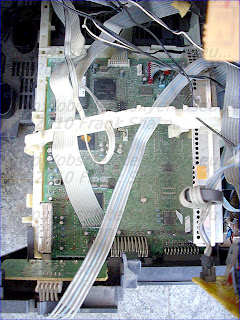

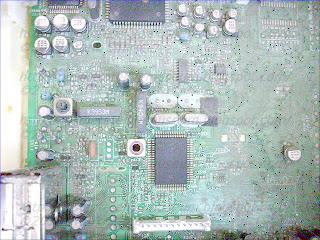

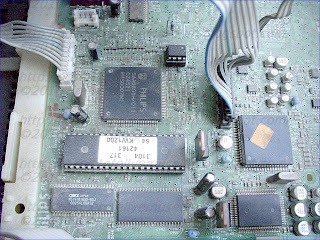

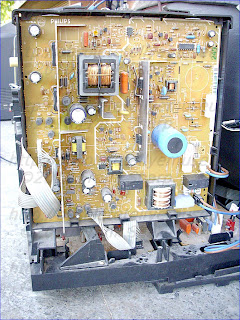

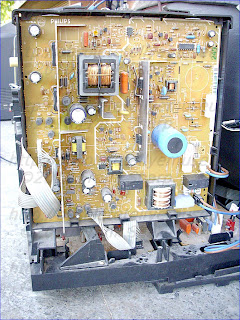

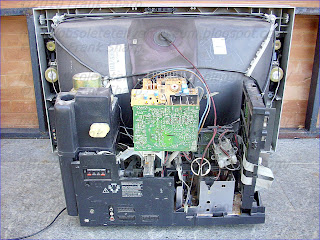

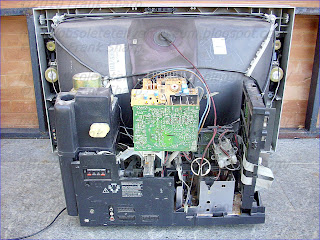

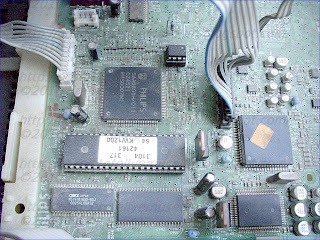

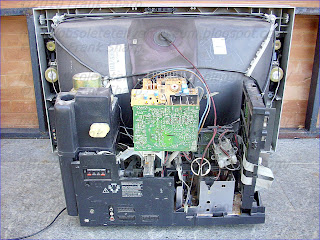

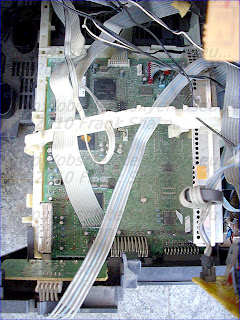

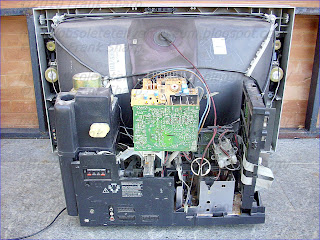

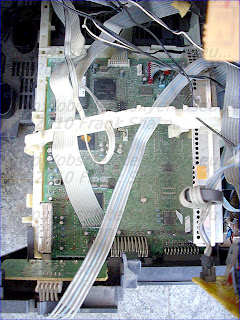

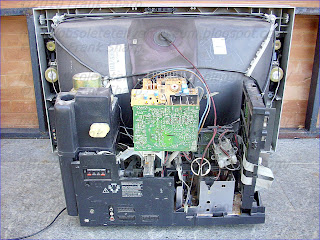

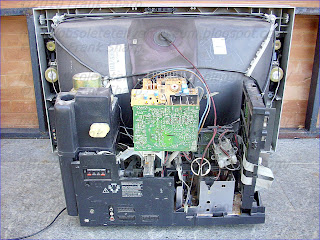

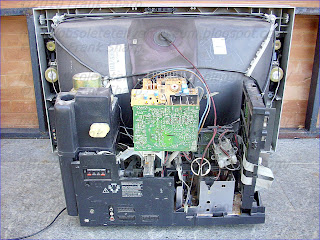

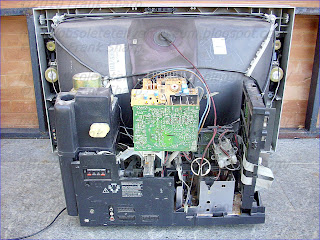

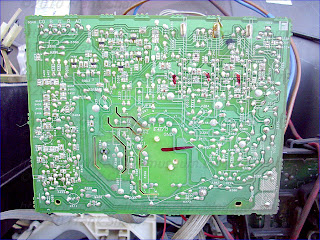

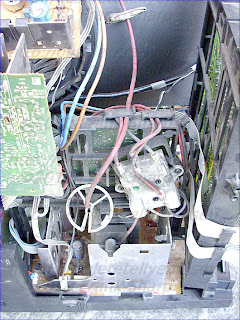

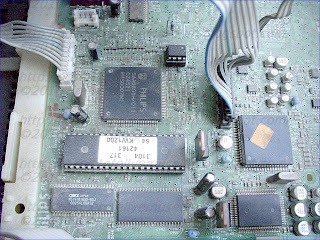

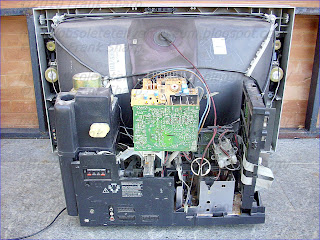

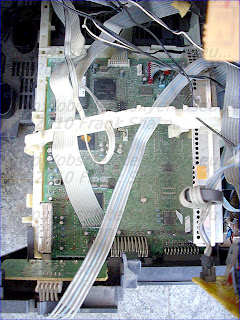

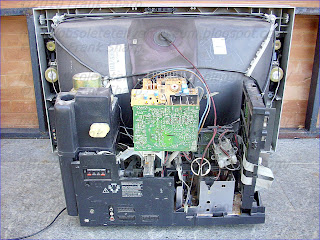

The chassis MG3.1E is particularly complex with various ASIC's interconnected via I2C bus and a sophisticated Microprocessor CCU.

There is even a sub Woofer integrated in the chassis.

It was not easy to service and to understand even because of the complexity toghether with the very high features level.

CIRCUITS DESCRIPTIONS:

TOP SUPPLY:

MOTO

ROLA MC34067 HIGH PERFORMANCE ZERO VOLTAGE SWITCH RESONANT MODE CONTROLLER

ROLA MC34067 HIGH PERFORMANCE ZERO VOLTAGE SWITCH RESONANT MODE CONTROLLERThe MC34067/MC33067 are high performance zero voltage switch

resonant mode controllers designed for off–line and dc–to–dc converter

applications that utilize frequency modulated constant off–time or constant

deadtime control. These integrated circuits feature a variable frequency

oscillator, a precise retriggerable one–shot timer, temperature compensated

reference, high gain wide bandwidth error amplifier, steering flip–flop, and

dual high current totem pole outputs ideally suited for driving power

MOSFETs.

Also included are protective features consisting of a high speed fault

comparator and latch, programmable soft–start circuitry, input undervoltage

lockout with selectable thresholds, and reference undervoltage lockout.

These devices are available in dual–in–line and surface mount packages.

• Zero Voltage Switch Resonant Mode Operation

• Variable Frequency Oscillator with a Control Range Exceeding 1000:1

• Precision One–Shot Timer for Controlled Off–Time

• Internally Trimmed Bandgap Reference

• 4.0 MHz Error Amplifier

• Dual High Current Totem Pole Outputs

• Selectable Undervoltage Lockout Thresholds with Hysteresis

• Enable Input

• Programmable Soft–Start Circuitry

• Low Startup Current for Off–Line Operation

OPERATING DESCRIPTION

Introduction

As power supply designers have strived to increase power

conversion efficiency and reduce passive component size,

high frequency resonant mode power converters have

emerged as attractive alternatives to conventional

pulse–width modulated control. When compared to

pulse–width modulated converters, resonant mode control

offers several benefits including lower switching losses,

higher efficiency, lower EMI emission, and smaller size. A

new integrated circuit has been developed to support this

trend in power supply design. The MC34067 Resonant Mode

Controller is a high performance bipolar IC dedicated to

variable frequency power control at frequencies exceeding

1.0 MHz. This

integrated circuit provides the features and

integrated circuit provides the features andperformance specifically for zero voltage switching resonant

mode power supply applications.

The primary purpose of the control chip is to provide a

fixed off–time to the gates of external power MOSFETs at a

repetition rate regulated by a feedback control loop.

Additional features of the IC ensure that system startup and

fault conditions are administered in a safe, controlled manner.

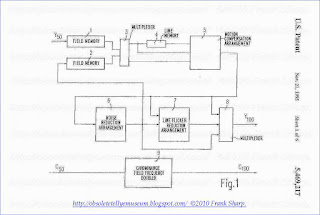

A simplified block diagram of the IC is shown on the front

page, which identifies the main functional blocks and the

block–to–block interconnects. Figure 13 is a detailed

functional diagram which accurately represents the internal

circuitry. The various functions can be divided into two

sections. The first section includes the primary control path

which produces precise output pulses at the desired

frequency. Included in this section are a variable frequency

Oscillator, a One–Shot, a pulse Steering Flip–Flop, a pair of

power MOSFET Drivers, and a wide bandwidth Error

Amplifier. The second section provides several peripheral

support functions including a voltage reference, undervoltage

lockout, Soft–Start circuit, and a fault detector.

Primary Control Path

The output pulse width and repetition rate are regulated

through the interaction of the variable frequency Oscillator,

One–Shot timer and Error Amplifier. The Oscillator triggers

the One–Shot which generates a pulse that is alternately

steered to a pair of totem pole output drivers by a toggle

Flip–Flop. The Error Amplifier monitors the output of the

regulator and modulates the frequency of the Oscillator. High

speed Schottky logic is used throughout the primary

control channel to minimize delays and enhance high

frequency characteristics.

Oscillator

The characteristics of the variable frequency Oscillator are

crucial for precise controller performance at high operating

frequencies. In addition to triggering the One–Shot timer and

initiating the output deadtime, the oscillator also determines

the initial voltage for the one–shot capacitor. The Oscillator is

designed to operate at frequencies exceeding 1.0 MHz. The

Error Amplifier can control the oscillator frequency over a

1000:1 frequency range, and both the minimum and

maximum frequencies are easily and accurately

programmed by the proper selection of external components.

Output Section

The pulse(tOS), generated by the Oscillator and One–Shot

timer is gated to dual totem–pole output drives by the

Steering Flip–Flop shown in Figure 16. Positive transitions of

tOS toggle the Flip–Flop, which causes the pulses to alternate

between Output A and Output B. The flip–flop is reset by the

undervoltage lockout circuit during startup to guarantee that

the first pulse appears at Output A.

The totem–pole output drivers are ideally suited for driving

power MOSFETs and are capable of sourcing and sinking

1.5 A. Rise and fall times are typically 20 ns when driving a

1.0 nF load. High source/sink capability in a totem–pole

driver normally increases the risk of high cross conduction

current during output transitions. The MC34067 utilizes a

unique design that virtually eliminates cross conduction, thus

controlling the chip power dissipation at high frequencies. A

separate power ground pin is provided to isolate the sensitive

analog circuitry from large transient currents.

PERIPHERAL SUPPORT FUNCTIONS

The MC34067 Resonant Controller provides a number of

support and protection functions including a precision voltage

reference, undervoltage lockout comparators, soft–start

circuitry, and a fault detector. These peripheral circuits

ensure that the power supply can be turned on and off in a

controlled manner and that the system will be quickly

disabled when a fault condition occurs.

Undervoltage Lockout and Voltage Reference

Separate undervoltage lockout comparators sense the

input VCC voltage and the regulated reference voltage as

illustrated in Figure 17. When VCC increases to the upper

threshold voltage, the VCC UVLO comparator enables the

Reference Regulator. After the Vref output of the Reference

Regulator rises to 4.2 V, the Vref UVLO comparator switches

the UVLO signal to a logic zero state enabling the primary

control path. Reducing VCC to the lower threshold voltage

causes the VCC UVLO comparator to disable the Reference

Regulator. The Vref UVLO comparator then switches the

UVLO output to a logic one state disabling the controller.

The Enable/UVLO Adjust pin allows the power supply

designer to select the VCC UVLO threshold voltages. When

this pin is open, the comparator switches the controller on at

16 V and off at 9.0 V. If this pin is connected to the VCC

terminal, the upper and lower thresholds are reduced to

9.0 V and 8.6 V, respectively. Forcing the Enable/UVLO

Adjust pin low will pull the VCC UVLO comparator input low

(through an internal diode) turning off the controller.

The Reference Regulator provides a precise 5.1 V

reference to internal circuitry and can deliver up to 10 mA to

external loads. The reference is trimmed to better than 2%

initial accuracy and includes active short circuit protection.

Fault Detector

The high speed Fault Comparator and Latch illustrated in

Figure 18 can protect a power supply from destruction under

fault conditions. The Fault Input pin connects to the input of

the Fault Comparator. If this input exceeds the 1.0 V

threshold of the comparator, the Fault Latch is set and two

logic signals simultaneously disable the primary control path.

The signal labeled “Fault” at the output of the Fault

Comparator is connected directly to the output drivers. This

direct path reduces the propagation delay from the Fault

Input to the A and B outputs to typically 70 ns. The Fault

Latch output is OR’d with the UVLO output from the Vref

UVLO comparator to produce the logic output labeled

“UVLO+Fault”. This signal disables the Oscillator and

One–Shot by forcing bot

h the COSC and CT capacitors to be

h the COSC and CT capacitors to becontinually charged.

The Fault Latch is reset during startup by a logic “1” at the

UVLO output of the Vref UVLO comparator. The latch can

also be reset after startup by pulling the Enable/UVLO Adjust

pin momentarily low to disable the Reference Regulator.

Soft–Start Circuit

The Soft–Start circuit shown in Figure 18 forces the

variable frequency Oscillator to start at the maximum

frequency and ramp downward until regulated by the

feedback control loop. The external capacitor at the

CSoft–Start terminal is initially discharged by the UVLO+Fault

signal. The low voltage on the capacitor passes through the

Soft–Start Buffer to hold the Error Amplifier output low. After

UVLO+Fault switches to a logic zero, the soft–start

capacitor is charged by a 9.0 mA current source. The buffer

allows the Error Amplifier output to follow the soft–start

capacitor until it is regulated by the Error Amplifier inputs. The

soft–start function is generally applicable to controllers

operating below resonance and can be disabled by simply

opening the CSoft–Start terminal.

APPLICATIONS INFORMATION

The MC34067 is specifically designed for zero voltage

switching (ZVS) quasi–resonant converter (QRC)

applications. The IC is optimized for double–ended push–pull

or bridge type converters operating in continuous conduction

mode. Operation of this type of ZVS with resonant properties

is similar to standard push–pull or bridge circuits in that the

energy is transferred during the transistor on–time. The

difference is that a series resonant tank is usually introduced

to shape the voltage across the power transistor prior to

turn–on. The resonant tank in this topology is not used to

deliver energy to the output as is the case with zero current

switch topologies. When the power transistor is enabled the

voltage across it should already be zero, yielding minimal

switching loss. Figure 19 shows a timing diagram for a

half–bridge ZVS QRC. An application circuit is shown in

Figure 20. The circuit built is a dc to dc half–bridge converter

delivering 75 W to the output from a 48 V source.

When building a zero voltage switch (ZVS) circuit, the

objective is to waveshape the power transistor’s voltage

waveform so that the voltage across the transistor is zero

when the device is turned on. The purpose of the control IC is

to allow a resonant tank to waveshape the voltage across the

power transistor while still maintaining regulation. This is

accomplished by maintaining a fixed deadtime and by

varying the frequency; thus the effective duty cycle is

changed.

Primary side resonance can be used with ZVS circuits. In

the application circuit, the elements that make the resonant

tank are the primary leakage inductance of the transformer

(LL) and the average output capacitance (COSS) of a power

MOSFET (CR). The desired resonant frequency for the

application circuit is calculated by Equation 6:

L L 2CR

(6)

1

=

p 2

ƒr

In the application circuit, the operating voltage is low and

the value of COSS versus Drain Voltage is known. Because

the COSS of a MOSFET changes with drain voltage, the value

of the CR is approximated as the average COSS of the

MOSFET. For the application circuit the average COSS can be

calculated by Equation 7:

measured at (7) CR

12

2 * COSS = in V

The MOSFET chosen fixes CR and that LL is adjusted to

achieve the desire

d resonant frequency.

d resonant frequency.However, the desired resonant frequency is less critical

than the leakage inductance. Figure 19 shows the primary

current ramping toward its peak value during the resonant

transition. During this time, there is circulating current

flowing through the secondary inductance, which effectively

makes the primary inductance appear shorted. Therefore,

the current through the primary will ramp to its peak value at

a rate controlled by the leakage inductance and the applied

voltage. Energy is not transferred to the secondary during

this stage, because the primary current has not overcome the

circulating current in the secondary. The larger the leakage

inductance, the longer it takes for the primary current to slew.

The practical effect of this is to lower the duty cycle, thus

reducing the operating range.

The maximum duty cycle is controlled by the leakage

inductance, not by the MC34067. The One–Shot in the

MC34067 only assures that the power switch is turned on

under a zero voltage condition. Adjust the one–shot period so

that the output switch is activated while the primary current is

slewing but before the current changes polarity. The resonant

stage should then be designed to be as long as the time for

the primary current to go to zero amps.

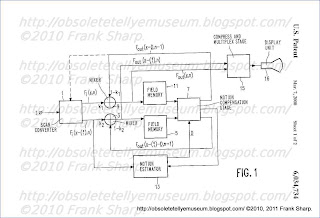

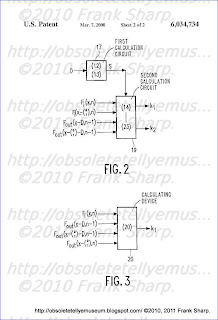

The invention relates to an arrangement for converting an original picture signal representing a sequence of frames, each of which is composed of two interlaced fields, into a converted picture signal which has a double field frequency with respect to the original picture signal.TDA9321H I2C-bus controlled TV input processorGENERAL DESCRIPTION

When converting a picture signal into such a converted picture signal which, with respect to the original picture signal, has a double field frequency, there is the problem that every second field of the converted picture signal must be newly generated, because no corresponding field of the original picture signal is available with respect to time and also with respect to the picture information.

In simple arrangements for doubling the field frequency, every field is doubled. A moving object in the fields of the converted picture signal is imaged twice in the same position before it jumps to the next position in the two subsequent fields. Since the human eye cannot follow these jumps, it is incident on the average speed of motion and observes a moving object from field to field at different positions. This leads to a double structure and motion blurr.

In other arrangements for field doubling of a picture signal a motion compensation is therefore provided by means of which the motion between two fields of the original picture signal is determined so that the motion can be taken into account in fields of the converted picture signal to be generated therebetween as a function of time and a corresponding interpolation can be performed. However, such arrangements have the further problem that possibly present noise is also to be reduced and that the line flicker, which still occurs in spite of the doubling of the field frequency in picture signals generated by way of interlaced scanning, is to be reduced. In the state of the art arrangements are only known in which a motion compensation is combined either with a noise reduction or with a line flicker reduction.

The TDA9321H is an input processor for

‘High-end’ television receivers. It contains the following

functions:

· Multistandard IF amplifier with PLL demodulator

· QSS-IF amplifier and AM sound demodulator

· CVBS and Y/C switch with various inputs and outputs

· Multistandard colour decoder which can also decode the

PALplus helper signal

· Integrated baseband delay line (64 ms)

· Sync processor which generates the horizontal and

vertical drive pulses for the feature box

(100 Hz applications) or display processor

(50 Hz applications).

The supply voltage for the TDA9321H is 8 V.

FEATURES

· Multistandard Vision IF (VIF) circuit with Phase-Locked

Loop (PLL) de

modulator

modulator· Sound IF (SIF) amplifier with separate input for single

reference Quasi Split Sound (QSS) mode and separate

Automatic Gain Control (AGC) circuit

· AM demodulator without extra reference circuit

· Switchable group delay correction circuit which can be

used to compensate the group delay pre-correction of

the B/G TV standard in multistandard TV receivers

· Several (I2C-bus controlled) switch outputs which can

be used to switch external circuits such as sound traps,

etc.

· Flexible source selection circuit with 2 external

CVBS inputs, 2 Luminance (Y) and Chrominance (C)

(or additional CVBS) inputs and 2 independently

switchable outputs

· Comb filter interface with CVBS output and Y/C input

· Integrated chrominance trap circuit

· Integrated luminance delay line with adjustable delay

time

· Integrated chrominance band-pass filter with switchable

centre frequency

· Multistandard colour decoder with 4 separate pins for

crystal connection and automatic search system

· PALplus helper demodulator

· Possible blanking of the helper signals for PALplus and

EDTV-2

· Internal baseband delay line

· Two linear RGB inputs with fast blanking; the

RGB signals are converted to YUV signals before they

are supplied to the outputs; one of the RGB inputs can

also be used as YUV input

· Horizontal synchronization circuit with switchable time

constant for the PLL and Macrovision/subtitle gating

· Horizontal synchronization pulse output or clamping

pulse input/output

· Vertical count-down circuit

· Vertical synchronization pulse output

· Two-level sandcastle pulse output

· I2C-bus control of various functions

· Low dissipation.

FUNCTIONAL DESCRIPTION

Vision IF amplifier

The VIF amplifier contains 3 AC-coupled control stages

with a total gain control range which is higher than 66 dB.

The sensitivity of the circuit is comparable with that of

modern IF-ICs.

The video signal is demodulated by a PLL carrier

regenerator. This circuit contains a frequency detector and

a phase detector. During acquisition the frequency

detector will tune the VCO to the correct frequency.

The initial adjustment of the oscillator is realized via the

I2C-bus. The switching between SECAM L and L’ can also

be realized via the I2C-bus. After lock-in the phase

detector controls the VCO so that a stable phase

relationship between the VCO and the input signal is

achieved. The VCO operates at twice the IF frequency.

The reference signal for the demodulator is obtained by

means of a frequency divider circuit. To get a good

performance for phase modulated carrier signals the

control speed of the PLL can be increased by bit FFI.

The AFC output is obtained by using the VCO control

voltage of the PLL and can be read via the I2C-bus.

For fast search tuning systems the window of the AFC can

be increased with a factor 3. The setting is realized with

bit AFW.

The AGC detector operates on top-sync and

top-white-level. The demodulation polarity is switched via

the I2C-bus. The AGC detector time constant capacitor is

connected externally; this is mainly because of the

flexibility of the application. The time constant of the AGC

system during positive modulation is rather long, this is to

avoid visible variations of the signal amplitude. To improve

the speed of the AGC system a circuit has been included

which detects whether the AGC detector is activated every

frame period. When, during 3 field periods, no action is

detected the speed of the system is increased. For signals

without peak white information the system switches

automatically to a gated black level AGC. Because a black

level clamp pulse is required for this mode of operation the

circuit will only switch to black level AGC in the internal

mode.

The circuits contain a video identification (ident) circuit

which is independent of the synchronization circuit.

Therefore search tuning is possible when the display

section of the receiver is used as a monitor. However, this

ident circuit cannot be made as sensitive as the slower

sync ident circuit (bit SL). It is recommended to use both

ident outputs to obtain a reliable search system. The ident

output is supplied to the tuning system via the I2C-bus.

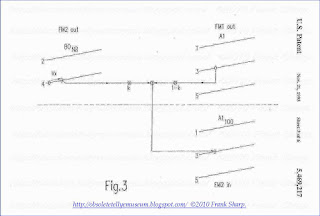

The input of the ident circuit is connected to pin 14

(see Fig.3). This has the advantage that the ident circuit

can also be made operative when a scrambled signal is

received (descrambler connected between pins 10

and 14). A second advantage is that the ident circuit can

be used when the VIF amplifier is not used (e.g. with

built-in satellite tuners). The video ident circuit can also be

used to identify the selected CBVS or Y/C signal.

The switching between the 2 modes can be realized with

bit VIM.

The TDA9321H contains a group delay correction circuit

which can be switched between the BG and a flat group

delay response characteristic. This has the advantage that

in multistandard receivers no compromise has to be made

for the choice of the SAW filter. Both the input and output

of the group delay correction circuit are externally

available so that the sound trap can be connected

between the VIF output and the group delay correction

input. The output signal of the correction circuit can be

supplied to the internal video processing circuit and to the

external SCART plug.

The IC has several (I2C-bus controlled) output ports which

can be used to switch sound traps or other external

components.

When th

e VIF amplifier is not used the complete VIF

e VIF amplifier is not used the complete VIFamplifier can be switched off with bit IFO.

Sound circuit

The SIF amplifier is similar to the VIF amplifier and has a

gain control range of approximately 66 dB. The AGC

circuit is related to the SIF carrier levels (average level of

AM or FM carriers) and ensures a constant signal

amplitude to the AM demodulator and the QSS mixer.

The single reference QSS mixer is realized by a multiplier.

In this multiplier the SIF signal is converted to the

intercarrier frequency by mixing it with the regenerated

picture carrier from the VCO. The mixer output signal is

supplied to the output via a high-pass filter for attenuation

of the residual video signals. With this system a high

performance hi-fi stereo sound processing can be

achieved.

The AM sound demodulator is realized by a multiplier.

The modulated SIF signal is multiplied in phase with the

limited SIF signal. The demodulator output signal is

supplied to the output via a low-pass filter for attenuation

of the carrier harmonics.

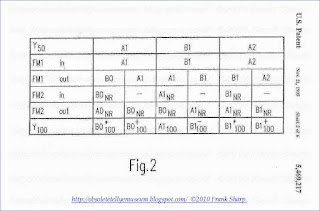

Video switches

The circuit has 3 CVBS inputs (1 internal and 2 externals)

and 2 Y/C inputs. The Y/C inputs can also be used as

additional CVBS inputs. The switch configuration is given

in Fig.3. The various sources can be selected via the

I2C-bus.

The circuit can be set in a mode in which it automatically

detects whether a CVBS or a Y/C signal is supplied to the

Y/C inputs. In this mode the TV-standard identification first

takes place on the added Y/CVBS and the C input signal.

Then both chrominance input signal amplitudes are

checked once and the input signal with the highest burst

signal amplitude is selected. The result of the detection

can be read via the I2C-bus.

The IC has 2 inputs (AV1 and AV2) which can be used to

read the status levels of pin 8 of the SCART plug.

The information is available in the output status byte 02 in

bits D0 to D3.

The 3 outputs of the video switches (CVBSCF, CVBSTXT

and CVBSPIP) can be independently switched to the

various input signals. The names are just arbitrary and it is,

for instance, possible to use the CVBSCF signal to drive

the comb filter and the teletext decoder in parallel and to

supply the CVBSTXT signal to the SCART plug (via an

emitter follower).

For

comb filter interfacing the circuit has the CVBSCF

comb filter interfacing the circuit has the CVBSCFoutput, a 3rd Y/C input, a reference signal output REFO

and 2 control pins (SYS1 and SYS2) which switch the

comb filter to the standard of the incoming signal (as

detected by the ident circuit of the colour decoder). When

a signal is recognized which can be combed and the comb

filter is enabled by bit ECMB the Y/C signals coming from

the comb filter are automatically selected. This is indicated

via bit CMB in output status byte 02 (D5). For signals

which cannot be combed (such as SECAM or

black-to-white signals) the Y/C signals coming from the

comb filter are not selected.

Chrominance and luminance processing

The circuits contain a chrominance band-pass, a SECAM

cloche filter and a chrominance trap circuit. The filters are

realized by means of gyrator circuits and they are

automatically calibrated by comparing the tuning

frequency with the crystal frequency of the decoder.

The luminance delay line is also realized by means of

gyrator circuits. The centre frequency of the chrominance

band-pass filter is switchable via the I2C-bus so that the

performance can be optimized for ‘front-end’ signals and

external CVBS signals.

The luminance output signal which is derived from the

incoming CVBS or Y/C signal can be varied in amplitude

by means of a separate gain setting control via the I2C-bus

control bits GAI1 and GAI0. The gain variation which can

be realized with these bits is -1 to +2 dB.

Colour decoder

The colour decoder can decode PAL, NTSC and SECAM

signals. The PAL/NTSC decoder contains an

alignment-free crystal oscillator with 4 separate pins for

crystal connection, a killer circuit and two colour difference

demodulators. The 90° phase shift for the reference signal

is produced internally.

Because it is possible to connect 4 different crystals to the

colour decoder, all colour standards can be decoded

without external switching circuits. Which crystals are

connected to the decoder must be indicated via the

I2C-bus. The crystal connection pins which are not used

must be left open-circuit.

The horizontal oscillator is calibrated by means of the

crystal frequency of the colour PLL. For a reliable

calibration it is very important that the crystal indication

bits XA to XD are not corrupted. For this reason

bits XA to XD can be read in the output bytes so that the

software can check the I2C-bus transmission.

The IC contains an Automatic Colour Limiting (ACL) circuit

which is switchable via the I2C-bus and prevents

oversaturation occuring when signals with a high

chrominance-to-burst ratio are received. The ACL circuit is

designed such that it only reduces the chrominance signal

and not the burst signal. This has the advantage that the

colour sensitivity is not affected by this function. The ACL

function is mainly intended for NTSC signals but it can also

be used for PAL signals. For SECAM signals the ACL

function should be switched off.

The SECAM decoder contains an auto-calibrating PLL

demodulator which has two references: the 4.43 MHz

subcarrier frequency which is obtained from the crystal

oscillator which is used to tune the PLL to the desired

free-running frequency and the band gap reference to

obtain the correct absolute value of the output signal.

The VCO of the PLL is calibrated during each vertical

blanking period, when the IC is in search or SECAM mode.

The circuit can also decode the PALplus helper signal and

can insert the various reference signals: set-ups and

timing signals which are required for the PALplus decoder

ICs.

The baseband delay line (TDA4665 function) is integrated.

RGB switch and matrix

The IC has 2 RGB inputs with fast switching. The switching

of the various sourcing is controlled via the I2C-bus and the

condition of the switch inputs can be read from the I2C-bus

status bytes. If the RGB signals are not synchronous with

the selected decoder input signal, an external clamp pulse

has to be supplied to the HA/CLP input. The IC must be set

in this mode via the I2C-bus. In that case the vertical pulse

is suppressed by switching the VA output in a

high-impedance off-state.

When an external RGB signal is mixed with the internal

YUV signal it is necessary to switch-off the PALplus

demodulation. To detect the presence of a fast blanking a

circuit is added which forces bits MACP and HD to zero if

a blanking pulse is detected in 2 consecutive lines. This

system is chosen to prevent switching-off at every spike

which is detected on the fast blanking input.

The IC has the possibility to use the RGB1 input as YUV

input. This function can be enabled by means of bit YUV in

subaddress 0A (D3). When switched to the YUV input the

input signals must have the same amplitude and polarity

as the YUV output signals. The Y signal has to be supplied

to the GI1 input, the U signal to the BI1 input and the

V signal to the RI1 input.

Synchronization circuit

The sync separator is preceded by a controlled amplifier

which adjusts the sync pulse amplitude to a fixed level.

These pulses are fed to the slicing stage which operates at

50% of the amplitude. The separated sync pulses are fed

to the phase detector and to the coincidence detector. This

coincidence detector is used to detect whether the line

oscillator is synchronized and can also be used for

transmitter identification. This circuit can be made less

sensitive with bit STM. This mode can be used during

search tuning to avoid the tuning system stopping at very

weak input signals. The PLL has a very high statical

steepness so that the phase of the picture is independent

of the line frequency.

For the horizontal output pulse 2 conditions are possible:

· An HA pulse which has a phase and width which is

identical to the incoming horizontal sync pulse

· A clamp pulse (CLP) which has a phase and width which

is identical to the clamp pulse in the sandcastle pulse.

The HA/CLP signal is generated by means of an oscillator

which is running at a frequency of 440 ´ fhor. Its frequency

is divided by 440 to lock the first loop to the incoming

signal. The time constant of the loop can be forced by the

I2C-bus (fast or slow).

If required the IC can select the time constant depending

on the noise content of the incoming video signal.

The free-running frequency of the oscillator is determined

by a digital control circuit which is locked to the reference

signal of the colour decoder. When the IC is switched on

the HA/CLP is suppressed and the oscillator is calibrated

as soon as all subaddress bytes have been sent. When the

frequency of the oscillator is correct the HA/CLP signal is

switched on again. When the coincidence detector

indicates an out-of-lock situation the calibration procedure

is repeated.

The VA pulse is obtained via a vertical count-down circuit.

The count-down circuit has various windows depending on

the incoming signal (50 or 60 Hz standard or

non-standard). The count-down circuit can be forced in

various modes via the I2C-bus. To obtain short switching

times of the count-down circuit during a channel change

the divider can be forced in the search window by means

of bit NCIN.

SAA4961 Integrated multistandard comb filterGENERAL DESCRIPTION

The

SAA4961 is an adaptive alignment-free one chip

SAA4961 is an adaptive alignment-free one chipcomb filter compatible with both PAL and NTSC systems

and provides high performance in Y/C separation.

FEATURES

· One chip adaptive multistandard comb filter

· Time discrete but continuous amplitude signal

processing with analog interfaces

· Internal delay lines, filters, clock processing and signal

switches

· Alignment-free

· No hanging dots or residual cross colour on vertical

transients

· Few external components.

FUNCTIONAL DESCRIPTION

Functional requirements

The multistandard comb filter processes the video

standards PAL B, G, H, M, N and NTSC M. PAL D and I

signals can also be processed but with the drawback of a

slightly reduced bandwidth.

For SECAM and SVHS signals the input signals can be

bypassed to the output without processing by selecting the

BYPASS-mode.

A sync separation circuit is incorporated to generate

control signals for the internal clock processing. With a

sync compression of up to 12 dB the sync separator works

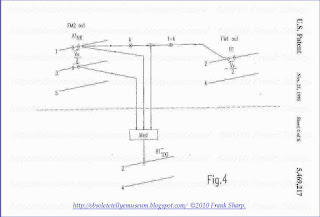

properly (see Fig.4).

The IC is controlled via six pins:

1. BYP forces the IC into the BYPASS-mode (comb filter

function off)

2. SSYN defines whether the COMB-mode is entered

synchronously or not and defines the polarity of the

BYP pin

3. SYS1 selects the video standard

4. SYS2 selects the video standard

5. FSCSW selects the reference frequency fsc or 2 ´ fsc

6. LPFION enables the internal pre-filter.

It is possible to select the following modes of operation:

COMB-mode: luminance and chrominance comb filter

function active if BYPASS-mode not active.

BYPASS-mode: signal processing not active, all clocks

inactive, Cext (pin 10) is bypassed to CO (pin 12) and

Yext/CVBS (pin 17) is bypassed to YO (pin 14) and

CVBSO (pin 15). This mode is forced via BYP (pin 3).

If the stimulus of the mode is changed, the IC is following

the new mode after the stabilization time given in Table 1.

Table 1 Stabilization time after mode change

The mode change from BYPASS to COMB depends on

SSYN (pin 6) and can be asynchronous or synchronous

related to the vertical pulse. The mode change from

COMB to BYPASS is always performed asynchronously.

MODE CHANGE

MAXIMUM

STABILIZATION

TIME

COMB-mode to BYPASS-mode 1 line

BYPASS-mode to COMB-mode 1 field

Pin description

FSC (PIN 1)

Input for the reference frequency fsc (see note 2 of Chapter

“Characteristics”) or 2 ´ fsc. For SECAM standard signals

the best signal performance in BYPASS-mode is achieved

by switching the FSC input signal off externally.

BYP (PIN 3)

Input signal that controls the operation mode. A low-pass

filter is added to the input for suppression of subcarrier

frequencies. Thus applications are supported where the

operation mode (COMB or BYPASS) is controlled by the

DC-level of the FSC input signal at pin 1. For those

applications the BYP input can be externally connected to

FSC (pin 1).

Depending on SSYN (pin 6) the function of BYP can be

adapted to a certain application with respect to the polarity

of the logic level and with respect to the behaviour when

entering the COMB-mode.

Depending on SSYN the BYP input can be either inverted

or non-inverted

The PLL and the clock processing are always stopped if

the selected level for BYPASS is applied to BYP

(independent of the vertical pulse).

REFBP (PIN 5)

Decoupling capacitor for the band-pass filter reference

voltage.

SSYN (PIN 6)

Input signal that controls the function of BYP (pin 3).

VCCA, VCCO, VDDD AND VCCPLL (PINS 7, 8, 22 AND 27)

Supply voltages.

AGND, OGND, DGND AND PLLGND (PINS 9, 11,

21 AND 26)

Ground connection. AGND is used as signal reference for

all analog input and output signals.

Cext (PIN 10)

Input for an external chrominance signal which is

correlated to the external VBS signal.

CO (PIN 12)

Chrominance output signal. This output can be switched

between the comb filtered chrominance from the CVBS

signal and the external chrominance signal from the input

Cext if the IC is forced into BYPASS-mode.

FSCSW (PIN 13)

Input signal to select between fsc or 2 ´ fsc as reference at

the FSC input pin.

YO (PIN 14)

VBS output signal. This output can be switched between

the comb filtered luminance signal (including

synchronization) and the external (C)VBS signal from the

input Yext/CVBS. In COMB-mode the output signal is

delayed by 2 lines (1 line at NTSC) and by an additional

processing delay.

CVBSO (PIN 15)

CVBS output signal directly from the input in

BYPASS-mode or delayed by the signal processing time

of 2 lines (1 line at NTSC) and an additional processing

delay.

Yext/CVBS (PIN 17)

Input for the CVBS signal or for an external VBS signal.

LPFION (PIN 18)

Input signal to disable the internal pre-filter LPFI.

CSY (PIN 19)

Sync top capacitor for the sync separator.

SYS1 AND SYS2 (PINS 20 AND 23)

System switch input signals to adapt the signal processing

to the different CVBS standards.

Internal functional description

SWITCHED CAPACITOR DELAY LINE

Delays the CVBS input signal by 2 lines and 4 lines

(all PAL standards) or by 1 line and 2 lines (NTSC

standard). Input

signals for the delay lines are the CVBS

signals for the delay lines are the CVBSsignal, the clock CL3 (3 ´ fsc), the control signal HSEL and

the standard selection signal SYSPAL.

Output signals are the non-delayed, the 2-line delayed and

the 4-line delayed CVBS signal (PAL) or the 1-line delayed

and the 2-line delayed CVBS signal (NTSC).

SWITCHED CAPACITOR BAND-PASS FILTERS (BPFS)

The comb filter input BPFs attenuate the low frequencies

to guarantee a correct signal processing within the logical

comb filter.

The comb filter output BPF reduces the alias components

that are the result of the non-linear signal processing within

the logical comb filter.

LOGICAL COMB FILTER

Separates the chrominance from the band-pass filtered

CVBS signal.

COMPENSATION DELAY

Compensates the internal processing time of the

band-pass filters and the logical comb filter section.

ADDER

The comb filtered luminance output signal is obtained by

adding the delayed CVBS signal and the inverted comb

filtered chrominance signal.

LOW-PASS FILTER INPUT (LPFI)

Analog input low-pass filter to reduce the outband

frequencies of EMC. The input low-pass filter is included in

the signal path but it can be switched off via the input

signal LPFION.

LOW-PASS FILTER OUTPUTS (LPFO1 AND LPFO2)

Two different types of output low-pass filters (LPFO1 and

LPFO2) are necessary to get equal signal delays within the

luminance path and the chrominance path (important for

good transient behaviour). The low-pass output filter type

LPFO1 is used for the luminance output while LPFO2 is

used for the chrominance output. The filters are analog 3rd

order elliptic low-pass filters that convert the output signals

from the time discrete to the time continuous domain

(reconstruction filter).

LPF CONTROL

Automatic tuning of the low-pass filters is achieved by

adjusting the filter delays. The control information for all

filters (CONT1 and CONT2) is derived from a built-in

reference filter (LPFO1-type) that is part of a control loop.

The control loop tunes the reference filter delay and thus

all other filter delays to a time constant derived from the

system clock CL3.

CONTROL AND CLOCK PROCESSING (CLOCK CONTROL)

The control and clock processing block (see Fig.9)

consists of the sub-blocks PLL, the clock processing and

the mode control. The PLL and the clock processing are

released for operation if the input level at BYP selects the

COMB-mode.

Main tasks of the control and clock processing are:

· Clock generation of system clock CL3

· Delay line start control

· Mode control.

The signal processing is based on a 3 ´ fsc system clock

(CL3), that is generated by the clock processing from the

fsc signal at FSC (pin 1) via a PLL. Because the subcarrier

frequency divided by the line frequency results not in an

integer value a clock phase correction of 180° is necessary

every second line for PAL standards or every line for

NTSC standard. The clock phase correction is controlled

by the input signals horizontal sync. Additionally the delay

line start is synchronized once a field to the input signals

horizontal sync. The 25 Hz PAL offset is corrected in this

way.

The PLL provides a master clock MCK of 6 ´ fsc, which is

locked to the subcarrier frequency at FSC (pin 1).

The system clock CL3 (3 ´ fsc) is obtained from MCK by a

divide-by-two circuit. The 180° phase shift is generated by

stopping the divide-by-two circuit for one MCK clock cycle.

The generated clock is a pseudo-line-locked clock that is

referenced to fsc. The sync separator generates the

necessary signals HDET and VDET indicating the line (H)

and the field (V) sync periods.

The current mode of operation (BYPASS or COMB) is

external readable via COMBENA (pin 25).

The input signals of the control and clock processing

(CLOCK CONTROL) are:

HDET: analog horizontal pulse from sync separator

VDET: analog vertical pulse from sync separator

FSC: subcarrier frequency (fsc or 2 ´ fsc)

FSCSW: reference frequency selection

BYP: BYPASS control signal

SSYN: vertical synchronous mode selection for BYP

and polarity selection of BYP.

The output signals are:

CL3: system clock (3 ´ fsc)

HSEL: line start signals for the delay lines

STOPS: forces the comb filter via the switches S2A,

S2B and S2C into the BYPASS-mode (always

asynchronous) or COMB-mode (synchronous or

asynchronous with VINT; depending on SSYN)

COMBENA: HIGH during COMB-mode; otherwise

LOW.

HORIZONTAL AND VERTICAL SYNC SEPARATOR

A built-in sync separator circuit generates the HDET and

VDET signals from the Yext/CVBS input signal. This circuit

is still operating properly at input signals with a 12 dB

attenuated sync in a normal 700 mV black-to-white video

signal .

CLAMP

The black level clamping of the video input signal is

performed by the sync separator stage. The clamping level

is nearly adequate to the voltage at REFDL (pin 24).

SIGNAL SWITCH S1

The switch is included to bypass the low-pass input filter.

For the CVBS input of the delay line block two signals can

be selected via the slow signal switch S1.

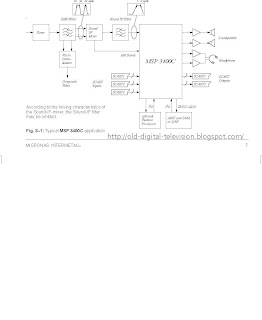

SOUND PROCESSING WITH MSP3400C

Multistandard Sound Processor

Release Notes: The hardware description in this

document is valid for the MSP 3400C – C8 and newer

codes. Revision bars indicate significant changes

to the previous version.

1. Introduction

The MSP 3400C is designed as single-chip Multistandard

Sound Processor for applications in analog and

digital TV sets, satellite receivers and video recorders.

The MSP-family, which is based on the MSP 2400, demonstrates

the progressive development towards highly

integrated multi-functional ICs.

The MSP 3400C, again, improves function integration:

The full TV sound processing, starting with analog

sound IF signal-in, down to processed analog AF-out, is

performed in a single chip. The IC is produced in 0.8 mm

CMOS technology, combined with high performance

digital signal processing.

The MSP 3400C 0.8 m CMOS version is fully pin and

software compatible to the 1.0 m MSP 3400 and MSP

3410. The main difference between the MSP 3400C and

the MSP 3410, consists of the MSP 3410 being able to

decode NICAM signals.

2. Features of the MSP 3400C:

2.1. Features of the Demodulator and Decoder

Sections

The MSP 3400C is designed to perform demodulation

of FM-mono TV sound and two carrier FM systems according

to the German or Korean terrestrial specs. With

certain constraints, it is also possible to do AM-demodulation

according to the SECAM system. Alternatively, the

satellite specs can be processed with the MSP 3400C.

For FM carrier detection in satellite operation, the AMdemodulation

offers a powerful feature to calculate the

carrier field strength, which can be used for automatic

search algorithms. So, the IC facilitates a first step towards

multistandard capability with its very flexible

application and may be used in TV-sets, satellite tuners,

and video recorders.

The MSP 3400C facilitates profitable multistandard capability,

offering the following advantages:

– two selectable analog inputs (TV and SAT-IF sources)

– Automatic Gain Control (AGC) for analog input: input

range: 0.14 – 3 Vpp

– integrated A/D converter for sound-IF inputs

– all demodulation and filtering is performed on chip and

is individually programmable

– no external filter hardware is required

– only one crystal clock (18.432 MHz) is necessary

– FM carrier level calculation for automatic search algorithms

and carrier mute function

– high deviation FM-mono mode (max. deviation:

approx. 360 kHz)

2.2. Features of the DSP-Section

– flexible selection of audio sources to be processed

– digital input and output interfaces via I2S-Bus for external

DSP-processors, surround sound, ADR etc.

– digital interface to proc

ess ADR (Astra Digital Radio)

ess ADR (Astra Digital Radio)together with DRP 3510 A

– performance of all deemphasis systems including

adaptive Wegener Panda 1 without external components

or controlling

– digitally performed FM-identification decoding and dematrixing

– digital baseband processing: volume, bass, treble,

5-band equalizer, loudness, pseudostereo, and basewidth

enlargement

– simple controlling of volume, bass, treble, equalizer

etc.

– increased audio bandwidth for FM-Audio-signals

(20 Hz – 15 kHz, 1 dB)

2.3. Features of the Analog Section

– three selectable analog pairs of audio baseband inputs

(= three SCART inputs)

input level: 32 V RMS,

input impedance: .25 kW

– one selectable analog mono input (i.e. AM sound),

input level: 32 V RMS,

input impedance: .10 kW

– two high quality A/D converters, S/N-Ratio: .85 dB

– 20 Hz to 20 kHz Bandwidth for SCART-to-SCARTCopy

facilities

– MAIN (loudspeaker) and AUX (headphones): two

pairs of 4-fold oversampled D/A-converters

output level per channel: max. 1.4 V RMS

output resistance: max. 5 kW

S/N-Ratio: .85 dB at maximum volume

max. noise voltage in mute mode: 310 mV (BW: 20 Hz

...16 kHz)

– one pair of four-fold oversampled D/A-converters supplying

two selectable pairs of SCART-Outputs. Output

level per channel: max. 2 V RMS, output resistance:

max. 0.5 kW, S/N-Ratio: .85 dB

(20 Hz...16 kHz).

SAA7712H Sound effects DSP

FEATURES

1.1 Hardware features

· Digital Signal Processor (DSP) core:

– 18 bits data width, 12 bits coefficient width

– Separate X, Y and P memories (both 384 bytes word

XRAM and YRAM, 3 kbytes word PROM)

– 1 kbytes delay line memory suited for Dolby Pro

Logic Surround.

· Inputs:

– 2 slave 18-bit digital stereo inputs: I2S-bus and

LSB-justified serial formats

– 2 master 18-bit digital stereo inputs: I2S-bus and

LSB-justified serial formats.

· Outputs:

– 4 DACs with 4-times oversampling and noise

shaping, fed to 4 output pins and configurable from

the DSP program, as left, right, front and surround

channels of a Dolby Pro Logic Surround system

– 2 master 18-bit digital stereo outputs: I2S-bus and

LSB-justified serial formats.

· 4-channel 5-band or 2-channel 10-band

I2C-bus controlled parametric equalizer

· I2C-bus microcontroller interface for:

– Access to full X and Y memory space

– Control of hardware settings: selectors,

programmable clock generations, etc.

· Controllable Phase-Locked Loop (PLL) to generate the

high frequency DSP clock from common fundamental

oscillator crystal

· 3.3 V process with 3.3 or 5 V digital periphery:

– 3.3 or 5 V I2S-bus and I2C-bus microcontroller

interfacing.

· Operating temperature range from 0 to 70 °C.

1.2 Software features

· Dolby Pro Logic Surround/Dolby 3 stereo:

Trademark of Dolby Laboratories Licensing Corporation

· Noise generation: A pink noise generator is included

for installation of the Dolby Pro Logic/Dolby 3 stereo

mode

· Hall/Matrix Surround: When no Dolby Pro Logic

Surround source material is available then this mode

can be used to produce a signal in the surround channel

· Incredible Surround (222-IS): This algorithm expands

the stereo width (stereo expander). This is intended to

be used when the 2 speakers are placed close together

(TV set and Midi set).

· Robust Incredible Surround (222-RIS): Same as

incredible surround only an alternative algorithm

· 3D Surround (422) or Incredible Virtual Surround:

Dolby Pro Logic Surround reproduced by 2 speakers

(L and R)

· IS-3D Surround (422-IS): Same as 3D Surround (422)

only with extra stereo width expander on left and right

· RIS-3D Surround (422-RIS): Same as IS-3D Surround

(422) with alternative algorithm

· 3D Surround (423) or Incredible Virtual Surround:

Dolby Pro Logic Surround reproduced by 3 speakers

(L, C and R)

· IS-3D Surround (423-IS): Same as 3D Surround (423)

only with extra stereo width expander on left and right

· RIS-3D Surround (423-RIS): Same as IS-3D Surround

(423-IS) with alternative algorithm.

· Voice cancelling (karaoke): Rejects voice out of

source material, mainly intended to be used with

karaoke. Several karaoke modes available in stereo

mode and in Dolby Pro Logic mode, such as (auto) voice

cancel, (auto) centre voice cancel, (auto) multi left and

(auto) multi right.

· Microphone mix modes (karaoke): Mono microphone

mixed to left, right and centre channel

· Spectrum analysis: 3-band spectrum analyser is

provided

· Dolby B: Both a Dolby B encoder as well as a Dolby B

decoder is implemented

· 2 Room solution: In all modes not requiring more than

2 output channels (stereo and karaoke incredible

surround) it is also possible to feed the source signal to

the other 2 output channels (with same processed or

not processed signal)

· Dynamic Bass Enhancement (DBE): Dynamic bass

enhancement generates a sub-woofer channel, which is

either a separate output or is added to the front channels

· Volume processing: Independent volume processing

of all 4 output channels

· AC-3/MPEG-2: Inputs available intended to be used

with an AC-3/MPEG-2 co-processor. In this mode the

SAA7712H can be used as post-processor.

· Output redirection: Several output configurations are

possible (normal 4 channel, special 4 + 2 channel,

record 2 + 2 channel, 6 or 6 + 2 channel).

Depending on the sample frequency several combinations

of the above mentioned features are possible.

2 APPLICATIONS

The SAA7712H can be used in TV sets with:

· Dolby Pro Logic Surround, incredible surround,

3D Surround and advanced acoustics processing

· Multi-channel sound decoding (AC-3 and MPEG-2) on a

co-processor. The SAA7712H can be used for

post-processing.

3 GENERAL DESCRIPTION

The SAA7712H provides for digital signal processing

power in TV systems and home theatre systems.

A DSP core is equipped with digital inputs and outputs, a

5-band parametric equalizer accelerator, a digital

co-processor interface and a delay line memory. This

architecture accommodates on-chip standard sound

processing, incredible surround, Dolby Pro Logic Surround

and other surround sound processing algorithms.

The architecture also supports co-processing, e.g. to add

to the processing power of the internal DSP core or for

multi-channel surround decoding.

All settings and parameters are controlled by an I2C-bus

interface. The available interfaces support a high

application flexibility.

The DSP core communicates over 32 dedicated registers.

The selected digital input is master for the data rate of the

DSP core. This input can be selected among 2 slave

I2S-bus inputs. The 4 outputs from the core are passed

through 4 DACs and then routed to 4 output pins.

Two master I2S-bus outputs and two master I2S-bus

inputs can serve as an I2S-bus co-processor interface.

Eight of the remaining registers are used for

communication with the hardware equalizer, and eight for

communication with the delay line memory.

All I2S-bus inputs and outputs support the Philips I2S-bus

format as well as 16, 18 and 20-bit LSB-justified formats.

FUNCTIONAL DESCRIPTION

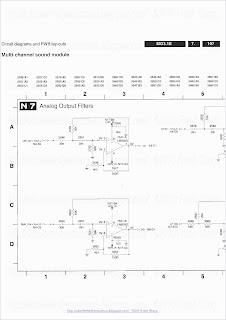

8.1 Analog outputs

8.1.1 ANALOG OUTPUT CIRCUIT

Depending on the configuration of the equalizer sections,

the SAA7712H has 2 or 4 analog outputs which are

supplied by the same power supply. Each of these outputs

has a voltage and a current pin (see Fig.3). The signals are

available on 2 outputs (OUT0 and OUT1), or 4 outputs

(OUT0, OUT1, OUT2 and OUT3).

DAC FREQUENCY

The sample rate (fs) of the selected source is the frame

rate of the DSP. The word clock for the upsample filter and

the clock for the DACs, at 4fs, are derived internally from

the word select of the selected audio source.

DACS

Each of the four low noise high dynamic range DACs

consists of a signed-magnitude DAC with current output,

followed by a buffer operational amplifier.

8.1.4 UPSAMPLE FILTER

To reduce spectral components above the audio band, a

fixed 4 times oversampling and interpolating digital filter is

used. The filters give an out-of-audio-band attenuation of

at least 29 dB. The filter is followed by a first-order noise

shaper to expand the dynamic range to more than 105 dB.

The band around multiples of the sample frequency of the

DAC (4fs) is not affected by the digital filter. A capacitor

must be added in parallel with the DAC output amplifier to

attenuate this out-of-band noise further to an acceptable

level.

In Fig.4 the overall frequency spectrum at the DAC audio

output without external capacitor or low-pass filter for the

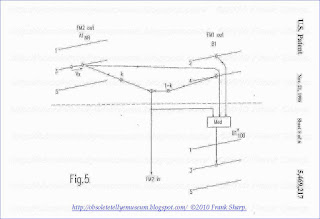

audio sampling frequencies of 38 kHz is shown. In Fig.5

the detailed spectrum around fs is shown for an fs of

38, 44.1 and 48 kHz. The pass band bandwidth (-3 dB) is

1¤2fs.

PERFORMANCE

The signed-magnitude noise-shaped DAC has a dynamic

range in excess of 100 dB. The signal-to-noise ratio of the

audio output at full-scale is determined by the word length

of the converter. The noise at low outputs is fully

determined by the noise performance of the DAC. Since it

is a signed-magnitude type, the noise at digital silence is

also low. As a disadvantage, the total THD is higher than

conventional DACs.

POWER-ON MUTE (POM)

To avoid any uncontrolled noise at the audio outputs after

power-on of the IC, the reference current source of the

DAC is switched off. The capacitor on pin POM

determines the time after which this current has a soft

switch-on. So at power-on the current audio signal outputs

are always muted. The loading of the external capacitor is

done in two stages via two different current sources.

The loading starts at a current level that is 9 times lower

than the current loading after the voltage on pin POM has

passed the 1 V level. This results in an almost dB linear

behaviour.

8.1.7 POWER-OFF PLOP SUPPRESSION

Power should still be provided to the analog part of the

DAC, while the digital part is switching off. As a result, the

output voltage will decrease gradually allowing the power

amplifier some extra time to switch-off without audible

plops. If a 5 V power supply is present, the supply voltage

of the analog part of the DAC can be fed from the 5 V

power supply via a 1.8 V zener diode. A capacitor,

connected to the 3.3 V power supply, provides power to

the analog part when the 5 V power supply is switching off

fast.

8.1.8 PIN VREFDA

With two internal resistors half the supply voltage (VDDA2)

is obtained and c

oupled to an internal buffer. This

oupled to an internal buffer. Thisreference voltage is used as DC voltage for the output

operational amplifiers and as reference for the DAC.

In order to obtain the lowest noise and to have the best

ripple rejection, a filter capacitor has to be added between

this pin and ground.

8.1.9 INTERNAL DAC CURRENT REFERENCE

As a reference for the internal DAC current and for the

DAC current source output, a current is drawn from the

level on pin VREFDA to pin VSSA2 (ground) via an internal

resistor. The absolute value of this resistor also

determines the absolute current of the DAC. This means

that the absolute value of the current is not that fixed due

to the spread of the current reference resistor value. This,

however, does not influence the absolute output voltages

because these voltages are also derived from a

conversion of the DAC current to the actual output voltage

via internal resistors.

8.1.10 SUPPLY OF THE ANALOG OUTPUTS

All the analog circuitry of the DACs and the operational

amplifiers are fed by 2 supply pins, VDDA2 and VSSA2.

Pin VDDA2 must have sufficient decoupling to prevent THD

degradation and to ensure a good power supply rejection

ratio.

The digital part of the DAC is fully supplied from the chip

core supply.

TDA9176 Luminance Transient Improvement (LTI) ICGENERAL DESCRIPTION

The TDA9176 is a Luminance Transient Improvement

(LTI) IC which is suitable for operation in both

50 and 100 Hz environments. The device can be used in

conjunction with both LCD and CRT displays.

The TDA9176 also contains chrominance delay lines to

compensate for the luminance delay. The device can be

used as a low-power, cost effective alternative to (but also

in combination with) Scan Velocity Modulation (SVM).

The device operates at a supply voltage of 8 V. The device

is contained in a 16 pin dual in-line package.

FEATURES

· Luminance transient improvement

· Line width control

· Can be used in 50 and 100 Hz environments

(1FH and 2FH)

· Compensating chrominance delay

· YUV interface

· Black insertion or clamping are selectable

· Amplitude selection for optimum operation with

450 mV (p-p) and 1 Vbl-wh luminance signals.

FUNCTIONAL DESCRIPTION

The TDA9176 is a Luminance Transient Improvement

(LTI) IC which is suitable for operation in both

50 and 100 Hz environments. The IC also contains

chrominance delay lines to compensate for the luminance

delay. A diagram of the LTI processor is illustrated in Fig.3.

The LTI processor contains a delay line which drives a

minimum/maximum (MINMAX) detector and a control

circuit. When the control circuit discovers a transient, the

LTI shaper switches from the minimum to the maximum

signal (or vice-versa, depending on the sign of the

transient). By mixing the original signal with the switched

signal, a variable transient improvement is obtained.

The 50% crossing point of the transient is not affected by

the LTI circuit.

If the rise time improvement is active, the duty cycle of the

output signal can be varied with the line width control input.

This function delays the rising edge and advances the

falling edge (or vice-versa). This can be used for example

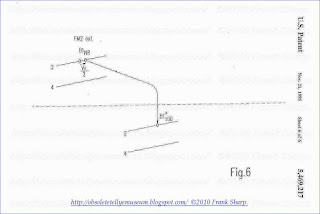

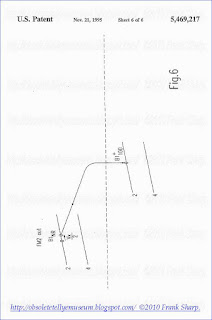

aperture correction. Figures 4 and 5 illustrate some

waveforms of the LTI processor.

For correct operation the LTI circuit requires a number of

fast clamps. To overcome problems where noise is

superimposed on the input signal the device contains an

input clamp that can either clamp to the black level of the

input signal, or, insert a black level. When a black level is

inserted, the internal clamps do not respond to the noise

on the input signal (see Fig.1). When the input signal

already has an inserted black level (e.g. when it is driven

from the TDA9170 picture booster) it is recommended to

set the device to the clamping mode. If no inserted black

level is available on the input signal it is recommended to

select the black insert mode of the input clamp.

The chrominance delay lines compensate for the delay of

the luminance signal in the LTI circuit. This is to safeguard

a correct colour fit.

Two and three level sandcastles can be used as a timing

signal, only the clamp pulse of the sandcastle input is used

in the device.

There are three selection inputs to select the modes of

operation. These selections are as follows:

1. 1FH or 2FH, for the 50 or 100 Hz applications.

2. Amplitude selection, for optimum operation of the

circuit with 450 mV (p-p) or 1 Vbl-wh luminance signals.

3. Black insertion or clamping of the luminance signal.

The selection inputs must be directly connected to either

ground or the supply rail. The modes are selected as

follows:

Frequency selection: GND = 1FH mode,

VCC = 2FH mode

Amplitude selection: GND = 450 mV (p-p),

VCC = 1 Vbl-wh mode

Black insertion/clamp: GND = clamp mode,

VCC = black insert mode.

If the selection pins are left floating, internal 1 MW resistors

connected to the pins set the device to, 1FH mode, black

insert mode and 1 Vbl-wh mode.

TDA933xH series I2C-bus controlled TV display processors:

GENERAL DESCRIPTION

The TDA933xH series are display processors for

‘High-end’ television receivers which contain the following

functions:

· RGB control processor with Y, U and V inputs, a linear

RGB input for SCART or VGA signals with fast blanking,

a linear RGB input for OSD and text signals with a fast

blanking or blending option and an RGB output stage

with black current stabilization, which is realized with the

CCC (2-point black current measurement) system.

· Programm

able deflection processor with internal clock

able deflection processor with internal clockgeneration, which generates the drive signals for the

horizontal, East-West (E-W) and vertical deflection.

The circuit has various features that are attractive for the

application of 16 : 9 picture tubes.

· The circuit can be used in both single scan (50 or 60 Hz)

and double scan (100 or 120 Hz) applications.

In addition to these functions, the TDA9331H and

TDA9332H have a multi-sync function for the horizontal

PLL, with a frequency range from 30 to 50 kHz (2fH mode)

or 15 to 25 kHz (1fH mode), so that the ICs can also be

used to display SVGA signals.

The supply voltage of the ICs is 8 V. They are each

contained in a 44-pin QFP package.

FEATURES

Available in all ICs:

· Can be used in both single scan (50 or 60 Hz) and

double scan (100 or 120 Hz) applications

· YUV input and linear RGB input with fast blanking

· Separate OSD/text input with fast blanking or blending

· Black stretching of non-standard luminance signals

· Switchable matrix for the colour difference signals

· RGB control circuit with Continuous Cathode Calibration

(CCC), plus white point and black level offset

adjustment

· Blue stretch circuit which offsets colours near white

towards blue

· Internal clock generation for the deflection processing,

which is synchronized by a 12 MHz ceramic resonator

oscillator

· Horizontal synchronization with two control loops and

alignment-free horizontal oscillator

· Slow start and slow stop of the horizontal drive pulses

· Low-power start-up option for the horizontal drive circuit

· Vertical count-down circuit

· Vertical driver optimized for DC-coupled vertical output

stages

· Vertical and horizontal geometry processing

· Horizontal and vertical zoom possibility and vertical

scroll function for application with 16 : 9 picture tubes

· Horizontal parallelogram and bow correction

· I2C-bus control of various functions

· Low dissipation.

FUNCTIONAL DESCRIPTION

RGB control circuit

INPUT SIGNALS

The RGB control circuit of the TDA933xH contains three

sets of input signals:

· YUV input signals, which are supplied by the input

processor or the feature box. Bit GAI can be used to

switch the luminance input signal sensitivity between

0.45 V (p-p) and 1.0 V (b-w). The nominal input signals

for U and V are 1.33 V (p-p) and 1.05 V (p-p),

respectively. These input signals are controlled on

contrast, saturation and brightness.

· The first RGB input is intended for external signals

(SCART in 1fH and VGA in 2fH applications), which have

an amplitude of 0.7 V (p-p) typical. This input is also

controlled on contrast, saturation and brightness.

· The second RGB input is intended for OSD and teletext

signals. The required input signals have an amplitude of

0.7 V (p-p). The switching between the internal signal

and the OSD signal can be realized via a blending

function or via fast blanking. This input is only controlled

on brightness.

Switching between the various sources can be realized via

the I2C-bus and by fast insertion switches. The fast

insertion switches can be enabled via the I2C-bus.

The circuit contains switchable matrix circuits for the

colour difference signals so that the colour reproduction

can be adapted for PAL/SECAM and NTSC. For NTSC,

two different matrices can be chosen. In addition, a matrix

for high-definition ATSC signals is available.

OUTPUT AMPLIFIER

The output signal has an amplitude of approximately

2 V (b-w) at nominal input signals and nominal settings of

the controls. The required ‘white point setting’ of the

picture tube can be realized by means of three separate

gain settings for the RGB channels.

To obtain an accurate biasing of the picture tube, a CCC

circuit has been developed. This function is realized by a

2-point black level stabilization circuit.

By inserting two test levels for each gun and comparing the

resulting cathode currents with two different reference

currents, the influence of the picture tube parameters such

as the spread in cut-off voltage can be eliminated.

This 2-point stabilization is based on the principle that the

ratio between the cathode currents is coupled to the ratio

between the drive voltages according to:

The feedback loop makes the ratio between cathode

currents Ik1 and Ik2 equal to the ratio between the

reference currents (which are internally fixed) by changing

the (black) level and the amplitude of the RGB output

signals via two converging loops. The system operates in

such a way that the black level of the drive signal is

controlled to the cut-off point of the gun. In this way, a very

good grey scale tracking is obtained. The accuracy of the

adjustment of the black level is only dependent on the ratio

of internal currents and these can be made very accurately

in integrated circuits. An additional advantage of the

2-point measurement is that the control system makes the

absolute value of Ik1 and Ik2 identical to the internal

reference currents. Because this adjustment is obtained

by adapting the gain of the RGB control stage, this control

stabilizes the gain of the complete channel (RGB output

stage and cathode characteristic). As a result, this 2-point

loop compensates for variations in the gain figures during

life.

An important property of the 2-point stabilization is that the

offset and the gain of the RGB path are adjusted by the

feedback loop. Hence, the maximum drive voltage for the

cathode is fixed by the relationship between the test

pulses, the reference current and the relative gain setting

of the three channels. Consequently, the drive level of the

CRT cannot be adjusted by adapting the

gain of the RGB

gain of the RGBoutput stage. Because different picture tubes may require

different drive levels, the typical ‘cathode drive level’

amplitude can be adjusted by means of an I2C-bus setting.

Depending on the selected cathode drive level, the typical

gain of the RGB output stages can be fixed, taking into

account the drive capability of the RGB outputs

(pins 40 to 42). More details about the design are given in

the application report (see also Chapter “Characteristics”;

note 11).

The measurement of the high and the low currents of the

2-point stabilization circuit is performed in two consecutive

fields. The leakage current is measured in each field. The

maximum allowable leakage current is 100 mA.

For extra flexibility, it also possible to switch the CCC

circuit to 1-point stabilization with the OPC bit. In this

mode, only the black level at the RGB outputs is controlled

by the loop. The cathode drive level setting has no

influence on the gain in this mode. This level should be set

to the nominal value to get the correct amplitude of the

measuring pulses.

Via the I2C-bus, an adjustable offset can be made on the

black level of red and green channels with respect to the

level that is generated by the black current control loop.

These controls can be used to adjust the colour

temperature of the dark part of the picture, independent of

the white point adjustment.

When the TV receiver is switched on, the black current

stabilization circuit is directly activated and the RGB

outputs are blanked. The blanking is switched off as soon

as the loop has stabilized (e.g. the first time that bit BCF

changes from 1 to 0, see also Chapter “Characteristics”;

note 15). This ensures that the switch-on time is reduced

to a minimum and is only dependent on the warm-up time

of the picture tube.

The black current stabilization system checks the output

level of the three channels and indicates whether the black

level of the lowest RGB output of the IC is in a certain

window (WBC bit), below or above this window (HBC bit).

This indication can be read from the I2C-bus and can be

used for automatic adjustment of voltage Vg2 during the

production of the TV receiver.

When a failure occurs in the black current loop (e.g. due to

an open circuit), status bit BCF is set. This information can

be used to blank the picture tube to avoid damage to the

screen.

The control circuit contains an average beam current

limiting circuit and a peak white level (PWL) circuit. The

PWL detects small white areas in the picture that are not

detected by the average beam current limiter. The PWL

can be adjusted via the I2C-bus. A low-pass filter is placed

in front of the peak detector to prevent it from reacting to

short transients in the video signal. The capacitor of the

low-pass filter is connected externally so that the set

maker can adapt the time constant as required. The IC

also contains a soft clipper that limits the amplitude of the

short transients in the RGB output signals. In this way, spot

blooming on, for instance, subtitles is prevented. The

difference between the PWL and the soft clipping level can

be adjusted via the I2C-bus in a few steps.

The vertical blanking is adapted to the vertical frequency

of the incoming signal (50 or 100 Hz or, 60 or 120 Hz).

When the flyback time of the vertical output stage is

greater than the 60 Hz blanking time, the blanking can be

increased to the same value as that of the 50 Hz blanking.

This can be set by means of bit LBM.

When no video is available, it is possible to insert a blue

background. This feature can be activated via bit EBB.

Synchronization and deflection processing

HORIZONTAL SYNCHRONIZATION AND DRIVE CIRCUIT

The horizontal drive signal is obtained from an internal

VCO which runs at a frequency of 440 times (2fH mode) or

880 times (1fH mode) the frequency of the incoming HD

signal. The free-running frequency of this VCO is

calibrated by a crystal oscillator which needs an external

12 MHz crystal or ceramic resonator as a reference. It is

also possible to supply an external reference signal to the

IC (in this case, the external resonator should be

removed).

The VCO is synchronized to the incoming horizontal HD

pulse (applied from the feature box or the input processor)

by a PLL with an internal time constant. The frequency of

the horizontal drive signal (1fH or 2fH) is selected by means

of a switching pin, which must be connected to ground or

left open circuit.

For HDTV applications, it is possible to change the

free-running frequency of the horizontal drive output from

31.2 kHz to 33.7 kHz by means of bit HDTV.

For safety reasons, switching between 1fH and 2fH

modes is only possible when the IC is in the standby

mode.

For the TDA9331H and TDA9332H, it is also possible to

set the horizontal PLL to a ‘multi-sync’ mode by means of

bit VGA. In this mode, the circuit detects the frequency of

the incoming sync pulses and adjusts the centre frequency

of the VCO accordingly by means of an internal

Digital-to-Analog-Converter (DAC). The frequency range

in this mode is 30 to 50 kHz at the output.

The polarities of the incoming HD and VD pulses are

detected internally. The detected polarity can be read out

via status bits HPOL and VPOL.

The horizontal drive signal is generated by a second

control loop which compares the phase of the reference

signal (applied from the internal VCO) with the flyback

pulse. The time constant of this loop is set internally. The

IC has a dynamic horizontal phase correction input, which

can be used to compensate phase shifts that are caused

by beam current variations. Additional settings of the

horizontal deflection (which are realized via the second

loop) are the horizontal shift and horizontal parallelogram

and bow corrections (see Chapter “Characteristics”;

Fig.16). The adjustments are realized via the I2C-bus.

When no horizontal flyback pulse is detected during three

consecutive line periods, status bit NHF is set.

The horizontal drive signal is switched on and off via the

so-called slow-start/slow-stop procedure. This function is

realized by varying the ton of the horizontal drive pulse. For