Various versions of this were made.

This chassis was introducing the isolated mains power supply Thyristor horizontal output operated and the PIL S4 CRT tube from Videocolor (RCA Technology).

First SALORA TV chassis with a VST Tunign search servo assisted with a TMS1100 controller

specially programmed to perform the functions of the TMS3755DNL.

These were fabricated for a brief period of time and replace with the 1g chassis further.

it's divided by functions and inter related in complex way with all units toghether.

NOT EASY.

THE TBA800, TBA810 AUDIO integrated circuits:

AUDIO integrated circuits are being increasingly used in television chassis and certainly represent the simplest approach to improving the audio side of a TV set. A number of such i.c.s have appeared during the 70's.

Here describes the use of two fairly recent ones, the SGS-ATES TBA800 and TBA8I0S. Both devices can provide reasonably high outputs into a suitable loudspeaker-the TBA800 will give up to 5W and the TBA810S up to 7W.

The main difference between them being that the TBA800 is a somewhat higher voltage, lower current device. The TBA800 is used in the current Grundig and ASA 110° colour chassis while the Finlux 110' colour chassis uses a TBA810. In each of these chassis the audio i.c. is driven from a TBA120 intercarrier sound i.c. The TBA800 and TBA810S can also be used as the field output stage in 110' monochrome chassis with c.r.t.s of up to l7in. and as the field driver stage in larger screen monochrome sets.

The

TBA800 is designed to provide up to 5W into a 16 Ohm load when operated

from a 24V supply. It is encapsulated in the type cf quad -in -line

case shown in Fig. I: the tabs at the centre are to assist in cooling

the device and must be earthed. The TBA800 can be operated from power

supply voltages up to the absolute maximum permissible value of 30V. It

is best to regard 24V as being the upper limit however in order to

provide an adequate safety margin and prevent possible damage during

voltage surges. The minimum power supply voltage recommended by the

manufacturers is 5V, but the power output is then less than 0-5W. The

quiescent current taken by the TBA800 is typically 9mA from a 24V

supply-no device of this type should draw more than 20mA. When an input

signal is applied the current increases considerably- up to about 1.5A

at full power. Two circuits for use with the TBA800 are shown in Figs. 2

and 3 and give comparable performance. The circuit shown in Fig. 2 is somewhat simpler but that

The

TBA800 is designed to provide up to 5W into a 16 Ohm load when operated

from a 24V supply. It is encapsulated in the type cf quad -in -line

case shown in Fig. I: the tabs at the centre are to assist in cooling

the device and must be earthed. The TBA800 can be operated from power

supply voltages up to the absolute maximum permissible value of 30V. It

is best to regard 24V as being the upper limit however in order to

provide an adequate safety margin and prevent possible damage during

voltage surges. The minimum power supply voltage recommended by the

manufacturers is 5V, but the power output is then less than 0-5W. The

quiescent current taken by the TBA800 is typically 9mA from a 24V

supply-no device of this type should draw more than 20mA. When an input

signal is applied the current increases considerably- up to about 1.5A

at full power. Two circuits for use with the TBA800 are shown in Figs. 2

and 3 and give comparable performance. The circuit shown in Fig. 2 is somewhat simpler but thatshown in Fig. 3 enables one side of the loudspeaker to be connected to chassis. The input resistance of the TBA800 is quite high (typically 5 MOhm) but a resistor must be connected between the input pin 8 and chassis otherwise the out- put stage will not operate with the correct bias. In the circuits shown the volume control VR1 provides this function: the bias current that flows through it is typically 1 microA (maximum 5 microA). The average voltage at the output pin 12 is half the supply potential. The loudspeaker must be capacitively coupled therefore and the low frequency response will be worse as this capacitor is decreased in value. The output coupling capacitor C4 in Fig. 2 also provides the bootstrap connection to pin 4. In Fig. 3 an additional capacitor (C9) is required for this purpose.

In both circuits the value of R1 controls the amount of feedback and thus the gain. The output signal is fed back to pin 6 via an internal 7 kOhm resistor. If R1 is reduced in value the gain will increase but the frequency response will be affected and the distortion will rise. With the component values shown the voltage gain of both circuits is typically 140 (43dB) which is quite adequate for most audio applications. R3 in Fig. 3 is necessary only if the power supply voltage is fairly low (less than about 14V).

C2 smooths the power supply input and C1 is connected between pin 1 and chassis to provide r.f. decoupling and help prevent instability. If mains hum is present on the supply line with the circuit shown in Fig. 3 capacitor C8 should be included between pin 7 and chassis. The circuits shown have a level frequency response (within ±3dB) between about 40Hz and 20kHz. If you wish to reduce the upper 3dB level to about 8kHz C5 can be increased to about 560pF. The total harmonic distortion provided by these circuits remains fairly constant at about 0.5% until the power output reaches 3W: it then rises rapidly with power level as shown in Fig. 4.

The

TBA800 can be operated from a 13V supply to feed up to 2.5W into an 80

load or from a 17V supply to feed the same power into a 160 load without

an additional heatsink. If more output power is required the cooling

tabs must be connected to a heatsink. Two methods of mounting the TBA800

are shown in Figs. 5 and 6. In Fig. 5 the device is inserted into a

circuit board and a heatsink is soldered to the same points as the tabs:

this has the disadvantage that the heatsink extends above the board

though on the other hand the whole board can be used for the

construction of the circuit. In Fig. 6 the tabs are soldered directly to

a suitable area of copper on the board: this method has the

disadvantage that about two square inches of the board are not available

for component mounting. It is generally best to make soldered

connections to the pins of the device since this ensures good heat

dissipation with minimum unwanted feedback. Observe the usual heat

precautions when soldering. The pins can however be carefully bent so

that they will fit into a 16 -pin dual -in -line socket.

The

TBA800 can be operated from a 13V supply to feed up to 2.5W into an 80

load or from a 17V supply to feed the same power into a 160 load without

an additional heatsink. If more output power is required the cooling

tabs must be connected to a heatsink. Two methods of mounting the TBA800

are shown in Figs. 5 and 6. In Fig. 5 the device is inserted into a

circuit board and a heatsink is soldered to the same points as the tabs:

this has the disadvantage that the heatsink extends above the board

though on the other hand the whole board can be used for the

construction of the circuit. In Fig. 6 the tabs are soldered directly to

a suitable area of copper on the board: this method has the

disadvantage that about two square inches of the board are not available

for component mounting. It is generally best to make soldered

connections to the pins of the device since this ensures good heat

dissipation with minimum unwanted feedback. Observe the usual heat

precautions when soldering. The pins can however be carefully bent so

that they will fit into a 16 -pin dual -in -line socket.The TBA810S has the same type of encapsulation as the TBA800 and the connections are also as shown in Fig. 1 except that there is no internal connection to pin 3. An alternative version, the TBA810AS, has two horizontal tabs with a hole in each (see Fig. 7) so that a heatsink can be bolted on. Some readers may find it easier to bolt a heatsink to a TBA810AS than to solder the TBA810S tabs. TBA810 devices can provide 7W of audio power to a 40 loudspeaker when operated from a I6V supply. Fig. 8 shows the change in maximum output power with different supply voltages. As a 4.5W output can be obtained with a 12V supply the TBA810 is much more suitable than the TBA800 for use with battery operated equipment. The TBA810 can provide output currents up to 2.5A.

Two circuits for use with TBA810 devices are shown in Figs. 9 and 10: they are very similar to the circuits shown in Figs. 2 and 3 though some of the capacitor values are larger because of the lower output impedance. The two circuits have comparable performance but that shown in Fig. 10 gives somewhat better results at low supply voltages (down to 4V). In either circuit R2 may be replaced with a 100k0 volume control. The bias current flowing in the pin 8 circuit is typically

0-4 microA and the input resistance 5M 0 (the value of R2 must be much less however to ensure correct bias.

The gain decreases as the value of R1 is increased for the same reason as with the TBA800. The values of R1, C3 and C7 affect the high -frequency response. With the values shown the response is level within ±3dB from about 40Hz to nearly 20kHz. Fig. 11 shows values of C3 plotted against R1 where the frequency is 3dB down at 10kHz and 20kHz and C7 is five times C3. The output distortion with these circuits is about 0.3% for outputs up to 3W rising to about 1% at 4W, 3% at 5W and 9% at 6W with a 14.4V supply voltage. The voltage gain is typically 70 times (37dB). Although this value is half that obtained with the TBA800 the input voltage required to produce a given output power is about the same for both types. This is because a smaller output voltage is required to drive a 40 load at a certain power level than is required to drive a 160 load.

The TBA810S may be mounted in the same way as the TBA800. One way of mounting the TBA810AS is shown in Fig. 12. It is simpler however to bolt flat heatsinks to the tabs.

Devices of this type will be destroyed within a fraction of a second if the power supply is accidentally con- nected with reversed polarity. When experimenting therefore it is wise to include a diode in the positive power supply line to prevent any appreciable reverse current flowing in the event of incorrect power supply connection. The diode can be removed once the circuit has been finalised. The TBA800 is likely to be destroyed if the output is accidentally shorted to chassis. The TBA810S and TBA810AS however are protected from damage in the event of such a short-circuit even if this remains for a long time (but note that the earlier TBA8I0 and TBA810A versions did not contain internal circuitry to provide this protection). The TBA800 is not protected against overheating but the TBA810S and TBA810AS incorporate a thermal shutdown circuit.

For this reason the heat- sinks used with the TBA810S and TBA810AS can have a smaller safety factor than those used with the TBA800. If the silicon chip in a TBA810S or TBA810AS becomes too hot the output power is temporarily reduced by the internal thermal shutdown circuit. As with all high -gain amplifiers great care should be taken to keep the input and output circuits well separated otherwise oscillation could occur. The de- coupling capacitors should be soldered close to the i.c. -especially the 0 1pF decoupling capacitor in the supply line (this should be close to pin I).

Field Output Circuit:

Fig. 13 shows a suggested field output stage for monochrome receivers with 12-17in. 110° c.r.t.s using the TBA81OS. For safe working up to 50°C ambient temperature each tab of the device must be soldered to a square inch of copper on the board. The peak -to - peak scanning current is 1.5A, the power delivered to the scan coils 0.47W, power disspipation in the TBA810S 1 8W, scan signal amplitude 4.1V, flyback amplitude 5V and the maximum peak -to -peak current available in the coils 1.75A.

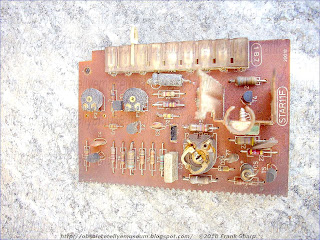

CHASSIS SALORA 1F UNITS VIEW.

- IF UNIT STD014F TB1440 STCC25 SN7666N

- SOUND DISCR UNIT STEJ04A TBA120

- SOUND AMPL OUT STEN02 TBA800

- INPUT SWITCH MODE STPX27

- THYRISTOR SWITCH HORIZONTAL OUT UNIT STP029A

- STAB SUPPLY VCC12V

- FRAME DEFLECTION OUTPUT UNIT STW011

- HORIZONTAL DEFLECTION PROTECTIVE UNIT STPR026B

- HORIZONTAL DEFLECTION STABILIZATION UNIT STL001B

- E/W CORRECTION UNIT STX011A

- RGB AMPL UNIT STY032

- CHROM + LUM UNIT STE011J TBA396 TDA3950A

MOTOROLA TV ICs DEMODULATION:

SALORA 1F6C CHASSIS 1F Supply circuit for a television receiver:

Isolated mains chassis thyristor technology:

A supply circuit for television receivers in which power source isolation is effected via a backward transformer. For the sake of achieving an insusceptibility to interferences, the operating frequency is equal to the line frequency. According to the invention, the supplied energy is controlled by varying the switch-on time during one period of the line frequency, in that the disconnecting time position is changed with the aid of a thyristor switching stage.

A supply circuit for television receivers in which power source isolation is effected via a backward transformer. For the sake of achieving an insusceptibility to interferences, the operating frequency is equal to the line frequency. According to the invention, the supplied energy is controlled by varying the switch-on time during one period of the line frequency, in that the disconnecting time position is changed with the aid of a thyristor switching stage.1. A su

pply circuit for a television receiver having a horizontal output stage including means for controlling line sweep and commutation, the energy required by said horizontal output stage being provided by a power source through a controllable supply circuit that isolates the power source from the horizontal output stage, said controllable supply circuit comprising:

an input transformer having a secondary winding connected to the horizontal output stage for providing the energy required thereby and a primary winding adapted for connection to the power source and being electrically isolated from the secondary winding and the horizontal output stage;

electronic switch means connected in series with the primary winding of the transformer;

first switching control means for switching on the electronic switch means as a function of line frequency; and

second switching control means for switching off the electronic switch means as a function of the energy required by the horizontal output stage, whereby the supply circuit provides the horizontal output stage with the required energy from the power source while also electrically isolating the horizontal output stage from the power source.

2. A supply circuit as described in claim 1, wherein the electronic switch means comprises a thyristor stage.

3. A supply circuit as described in claim 1, wherein the thyristor stage comprises a thyristor and a diode connected in inverse parallel manner, the gate electrode of the thyristor being connected to the first switching control means for turning on the thyristor.

4. A supply circuit as described in claim 3, wherein the first switching control means includes a horizontal deflection oscillator.

5. A supply circuit as described in claim 4, additionally comprising an isolation transformer connected between the thyristor gate and the horizontal deflection oscillator.

6. A supply circuit as described in claim 2, wherein the second switching control means comprises a series resonant circuit having an adjustable resonant frequency, said circuit being connected in parallel with the thyristor stage for causing commutation of the current in the thyristor stage.

7. A supply circuit as described in claim 6, wherein the series resonant circuit includes a transductor having a control winding, and the second switching control means additionally comprises a control circuit adapted to receive a signal from a high voltage transformer of the horizontal output stage and to provide in response thereto an output signal to the control winding of the transductor, said output signal varying in accordance with the signal from the high voltage transformer for varying the inductance of the transductor.

Owing to the various attachments which are capable of being operated in connection with a television receiver, it has increasingly become necessary, for safety reasons, to provide for isolation of the power source the television receiver.

In conventional types of circuits employing backward transformers for effecting the source isolation, it is customary to control the energy supply by way of inserting a transistorized control stage.

The use of transistors in such a circuit part, however, has proved to be problematic owing to the fact that the transistors are sensitive to any case of exceeding the prescribed operational values.

From the German technical journal "Funkschau" 1975, No. 5, page 40 there has already become known a

In order to eliminate as far as possible the danger of noise influences as linked thereto, the actually advantageous thyristor switching stage involves a rather considerable investment.,

It is the object of the invention, therefore, with respect to a circuit of the type mentioned hereinbefore, to avoid the described disadvantages of the conventional arrangments, and to safeguard an operationally reliable control of the supplied energy.

This object is achieved in that the energy as supplied to the horizontal (line) output stage is capable of being controlled by means of a thyristor switching stage arranged in series with the primary winding of the input transformer, with first switching means, in dependence upon the line frequency, switching the thyristor switching stage to the conducting state, and with further switching means serving to block the thyristor switching stage in dependence upon the required energy.

Further details and advantages of the invention may be taken from the patent claims as well as from the following description of the accompanying drawing.

FIG. 1 shows one example of embodiment of the invention.

The horizontal output (final) stage 20 is connected via the input transformer 10 including the primary winding 11 and the secondary winding 12, to the source of supply current B.

The horizontal output (final) stage 20 is connected via the input transformer 10 including the primary winding 11 and the secondary winding 12, to the source of supply current B. As an example relating to the horizontal output (final) stage there is shown in FIG. 1 a thyristor circuit as described in the company publication "Deflection, Power Supply and Correction Circuits for 110° Color Picture Tube A67 - 150x with Toroidal Yoke", No. 59-72-E of Standard Elektrik Lorenz AG, dated Apr. 20, 1972.

By the input transformer 10, the horizontal output stage 20 is galvanically separated from the source of supply current B, i.e. also from the power source. The most important function units of the horizontal output stage will now be mentioned briefly hereinafter.

The reference numeral 21 indicates the schematically shown combined inductive component consisting of deflecting coils and EHT transformer.

The switching stage 22 consisting of a thyristor and of an anti-parallel connected diode, represents the stage controlling the line sweep while the similarly designed switching stage 23 is the so-called commutating switch.

Between these two switching stages there is connected the commutating inductive component 25 and the commutating capacitor consisting of a capacitor combination 26.

The primary circuit of the inductive component 10 designed as an input transformer, is connected to the supply source B, at the "plus" and "minus" terminals of which the rectified power source voltage is available. The input transformer 10 comprises the primary winding 11 and the secondary winding 12. In series with the primary winding 11 there is arranged a thyristor switching stage consisting of a thyristor 13 and of a diode 14, with both the thyristor and the diode being connected antiparallel.

The thyristor 13 is controlled in this case by inserting an isolating transformer 19, by the horizontal oscillator 18, which means to imply that the operating frequency of the supply circuit including the input transformer 10 is identical to that of the horizontal final stage 20.

The switch-on time position, i.e. the one at which the thyristor 13 is switched to the conducting state, is determined by the control pulse from the horizontal oscillator 18.

Disconnection of the thyristor 13 or switching to the non-conducting state, is effected in the usual way by a current reversal during the time interval in which e.g. the commutating switch 23 is blocked. This is effected by the series resonant circuit arranged in parallel with the thyristor switching stage, including the capacitor 16 and the inductive component 15, in cooperation with the diode 14. This disconnecting time position or the time position at which the thyristor 13 is switched to the non-conducting state, is determined by the resonant frequency of the series-resonant circuit. Accordingly, at a constant switch-on time position, it is possible to determine the period of time during which the thyristor 13 is switched to the conducting state, by varying the resonant frequency and, consequently, by shifting the time position at which the thyristor 13 is switched to the non-conducting state. The period of time during which the thyristor 13 is switched to the conducting state, and, consequently, the period of time of the current flow, however, are decisive for the amount of energy capable of being taken off the input transformer 10 or the secondary winding 12 respectively.

Th

e aforementioned variation of the resonant frequency of the series-resonant circuit, may be carried out, on principle, by a capacitance variation of the capacitor 16, as well as by changing the inductance 15, or else by both.

e aforementioned variation of the resonant frequency of the series-resonant circuit, may be carried out, on principle, by a capacitance variation of the capacitor 16, as well as by changing the inductance 15, or else by both. In the shown example of embodiment there has been chosen a variation of the inductance, in which case, as an inductive component, a transductor is inserted in such a way that its operating winding is in series with the capacitor 16. Transductor 15 provides an inductance that varies in accordance with a DC signal applied thereto. If now, in accordance with stipulations, the energy supply is to be controlled in dependence upon the energy requirement, a corresponding control circuit will have to be provided for.

The energy consumed in the horizontal final stage can be measured by the value of the voltage of the kick-back pulse at the EHT transformer. In order to obtain this value, a tap 211 is schematically shown at the inductive component 21 of the horizontal final stage 20. This tap is connected to a control circuit 17.

As already mentioned, a transductor 15 is used as the adjustable inductive component of the series resonant circuit, whose inductance is capable of being varied by varying the current or voltage as applied to the control winding. At the same time, the transductor effects a galvanic separation. The control circuit 17 into the output circuit of which, according to FIG. 1, there is connected the control winding of the transductor 15, thus serves to convert the value of the voltage of the kickback pulse available as the input or control quantity, into a corresponding value for adjusting the inductive component 15.

Control circuits, such as e.g. 17, are on principle generally known to those skilled in the art and, therefore, do not need to be explained in detail herein, especially since the circuit-technical embodiment thereof is not germane to the present invention. An example of a control circuit that may be used for circuit 17 is shown in the publication previously referred to and entitled: "Deflection, Power Supply and Correction Circuits for 110° Color Picture Tube A67 - 150x with Toroidal Yoke".

It should still be mentioned that the input transformer 10 is operated as a backward transformer comprising a correspondingly polarized diode 24 in the secondary circuit, which is of advantage for reasons of dimensioning the input transformer 10.

SALORA 1F6C CHASSIS 1F INTEGRAL THYRISTOR-RECTIFIER DEVICE

A semiconductor switching device comprising a silicon controlled rectifier (SCR) and a diode rectifier integrally connected in parallel with the SCR in a single semiconductor body. The device is of the NPNP or PNPN type, having gate, cathode, and anode electrodes. A portion of each intermediate N and P region makes ohmic contact to the respective anode or cathode electrode of the SCR. In addition, each intermediate region includes a highly conductive edge portion. These portions are spaced from the adjacent external regions by relatively low conductive portions, and limit the conduction of the diode rectifier to the periphery of the device. A profile of gold recombination centers further electrically isolates the central SCR portion from the peripheral diode portion.

That class of thyristors known as controlled rectifiers are semiconductor switches having four semiconducting regions of alternate conductivity and which employ anode, cathode, and gate electrodes. These devices are usually fabricated from silicon. In its normal state, the silicon controlled rectifier (SCR) is non-conductive until an appropriate voltage or current pulse is applied to the gate electrode, at which point current flows from the anode to the cathode and delivers power to a load circuit. If the SCR is reverse biased, it is non-conductive, and cannot be turned on by a gating signal. Once conduction starts, the gate loses control and current flows from the anode to the cathode until it drops below a certain value (called the holding current), at which point the SCR turns off and the gate electrode regains control. The SCR is thus a solid state device capable of performing the circuit function of a thyratron tube in many electronic applications. In some of these applications, such as in automobile ignition systems and horizontal deflection circuits in television receivers, it is necessary to connect a separate rectifier diode in parallel with the SCR. See, for example, W. Dietz, U. S. Pat. Nos. 3,452,244 and 3,449,623. In these applications, the anode of the rectifier diode is connected to the cathode of the SCR, and the cathode of the rectifier is connected to the SCR anode. Thus, the rectifier diode will be forward biased and current will flow through it when the SCR is reverse biased; i.e., when the SCR cathode is positive with respect to its anode. For reasons of economy and ease of handling, it would be preferable if the circuit function of the SCR and the associated diode rectifier could be combined in a single device, so that instead of requiring two devices and five electrical connections, one device and three electrical connections are all that would be necessary. In fact, because of the semiconductor profile employed, many SCR's of the shorted emitter variety inherently function as a diode rectifier when reverse biased. However, the diode rectifier function of such devices is not isolated from the controlled rectifier portion, thus preventing a rapid transition from one function to the other. Therefore, it would be desirable to physically and electrically isolate the diode rectifier portion from that portion of the device which functions as an SCR.

That class of thyristors known as controlled rectifiers are semiconductor switches having four semiconducting regions of alternate conductivity and which employ anode, cathode, and gate electrodes. These devices are usually fabricated from silicon. In its normal state, the silicon controlled rectifier (SCR) is non-conductive until an appropriate voltage or current pulse is applied to the gate electrode, at which point current flows from the anode to the cathode and delivers power to a load circuit. If the SCR is reverse biased, it is non-conductive, and cannot be turned on by a gating signal. Once conduction starts, the gate loses control and current flows from the anode to the cathode until it drops below a certain value (called the holding current), at which point the SCR turns off and the gate electrode regains control. The SCR is thus a solid state device capable of performing the circuit function of a thyratron tube in many electronic applications. In some of these applications, such as in automobile ignition systems and horizontal deflection circuits in television receivers, it is necessary to connect a separate rectifier diode in parallel with the SCR. See, for example, W. Dietz, U. S. Pat. Nos. 3,452,244 and 3,449,623. In these applications, the anode of the rectifier diode is connected to the cathode of the SCR, and the cathode of the rectifier is connected to the SCR anode. Thus, the rectifier diode will be forward biased and current will flow through it when the SCR is reverse biased; i.e., when the SCR cathode is positive with respect to its anode. For reasons of economy and ease of handling, it would be preferable if the circuit function of the SCR and the associated diode rectifier could be combined in a single device, so that instead of requiring two devices and five electrical connections, one device and three electrical connections are all that would be necessary. In fact, because of the semiconductor profile employed, many SCR's of the shorted emitter variety inherently function as a diode rectifier when reverse biased. However, the diode rectifier function of such devices is not isolated from the controlled rectifier portion, thus preventing a rapid transition from one function to the other. Therefore, it would be desirable to physically and electrically isolate the diode rectifier portion from that portion of the device which functions as an SCR.SALORA 1F6C CHASSIS 1F LINE DEFLECTION WITH THYRISTOR SWITCH TECHNOLOGY OVERVIEW.

Horizontal deflection circuit

(Thyristor Horizontalsteuerung)

Description:

1. A horizontal deflection circuit for generating the deflection current in the deflection coil of a television picture tube wher

ein a first switch controls the horizontal sweep, and wherein a second switch in a so-called commutation circuit with a commutating inductor and a commutating capacitor opens the first switch and, in addition, controls the energy transfer from a dc voltage source to an input inductor, characterized in that the input inductor (Le) and the commutating inductor (Lk) are combined in a unit designed as a transformer (U) which is proportioned so that the open-circuit inductance of the transformer is essentially equal to the value of the input inductor (Le), while the short-circuit inductance of the transformer (U) is essentially equal to the value of the commutating inductor (Lk), and that the second switch (S2) is connected in series with the dc voltage source (UB) and a first winding (U1) of the transformer (U). 2. A horizontal deflection circuit according to claim 1, characterized in that the transformer (U) operates as an isolation transformer between the supply (UB) and the subcircuits connected to a second winding. 3. A horizontal deflection circuit according to claim 1, characterized in that the second switch (S2) is connected between ground and that terminal of the first winding (U1) of the transformer (U) not connected to the supply potential (+UB). 4. A horizontal deflection circuit according to claim 1, characterized in that a capacitor (CE) is connected across the series combination of the first winding (U1) of the transformer and the second switch (S2). 5. A horizontal deflection circuit according to claim 1, characterized in that the second winding (U2) of the transformer (U) is connected in series with a first switch (S1), the commutating capacitor (Ck), and a third, bipolar switch (S3) controllable as a function of the value of a controlled variable developed in the deflection circuit. 6. A horizontal deflection circuit according to claim 5, characterized in that the third switch (S3) is connected between ground and the second winding (U2) of the transformer. 7. A horizontal deflection circuit according to claim 2, characterized in that the isolation transformer carries a third winding via which power is supplied to the audio output stage of the television set. 8. A horizontal deflection circuit according to claims 2, characterized in that the voltage serving to control the first switch (S1) is derived from a third winding of the transformer.

German Aus

legeschrift (DT-AS) No. 1,537,308 discloses a horizontal deflection circuit in which, for generating a periodic sawtooth current within the respective deflection coil of the picture tube, in a first branch circuit, the deflection coil is connected to a sufficiently large capacitor serving as a current source via a first controlled, bilaterally conductive switch which is formed by a controlled rectifier and a diode connected in inverse parallel. The control electrode of the rectifier is connected to a drive pulse source which renders the switch conductive during part of the sawtooth trace period. In that arrangement, the sawtooth retrace, i.e. the current reversal, also referred to as "commutation", is initiated by a second controlled switch.

The first controlled switch also forms part of a second branch circuit where it is connected in series with a second current source and a reactance capable of oscillating. When the first switch is closed, the reactance, consisting essentially of a coil and a capacitor, receives energy from the second current source during a fixed time interval. This energy which is taken from the second current source corresponds to the circuit losses caused during the previous deflection cycle.

As can be seen, such a circuit needs two different, separate inductive elements, it being known that inductive elements are expensive to manufacture and always have a certain volume determined by the electrical properties required.

The object of the invention is to reduce the amount of inductive elements required.

The invention is characterized in that the input inductor and the commutating inductor are combined in a unit designed as a transformer which is proportioned so that the open-circuit inductance of the transformer is essentially equal to the value of the input inductor, while the short-circuit inductance of the transformer is essentially equal to the value of the commutating inductor, and that the second switch is connected in series with the dc voltage source and a first winding of the transformer.

This solution has an added advantage in that, in mass production, both the open-circuit and the short-circuit inductance are reproducible with reliability.

According to another feature of the invention, the electrical isolation between the windings of the transformer is such that the transformer operates as an isolation transformer between the supply and the subcircuits connected to a second winding or to additional windings of the transformer. In this manner, the transformer additionally provides reliable mains isolation.

According to a further feature of the invention, the second switch is connected between ground and that terminal of the first winding of the transformer not connected to the supply potential. This simplifies the control of the switch.

According to a further feature of the invention, to regulate the energy supply, the second winding of the transf

ormer is connected in series with the first switch, the commutating capacitor, and a third, bipolar switch controllable as a function of the value of a controlled variable developed in the deflection circuit.

The advantage gained by this measure lies in the fact that the control takes place on the side separated from the mains, so no separate isolation device is required for the gating of the third switch. Further details and advantages will be apparent from the following description of the accompanying drawings and from the claims. In the drawings,

FIG. 1 is a basic circuit diagram of the arrangement disclosed in German Auslegeschrift (DT-AS) No. 1,537,308;

FIG. 2 shows a first embodiment of the horizontal deflection circuit according to the invention, and

FIG. 3 shows a development of the horizontal deflection circuit according to the invention.

FIG. 1 shows the essential circuit elements of the horizontal deflection circuit known from the German Auslegeschrift (DT-AS) No. 1,537,308 referred to by way of introduction.

Connected in series with a dc voltage source UB is an input inductor Le and a bipolar, controlled switch S2. In the following, this switch will be referred to as the "second switch"; it is usually called the "commutating switch" to indicate its function.

In known circuits, the second switch S2 consists of a controlled rectifier and a diode connected in inverse parallel.

The second switch S

2 also forms part of a second circuit which contains, in addition, a commutating inductor Lk, a commutating capacitor Ck, and a first switch S1. The first switch S1, controlling the horizontal sweep, is constructed in the same manner as the above-described second switch S2, consisting of a controlled rectifier and a diode in inverse parallel. Connected in parallel with this first switch is a deflection-coil arrangement AS with a capacitor CA as well as a high voltage generating arrangement (not shown). In FIGS. 1, 2, and 3, this arrangement is only indicated by an arrow and by the reference characters Hsp. The operation of this known horizontal deflection circuit need not be explained here in detail since it is described not only in the German Auslegeschrift referred to by way of introduction, but also in many other publications.

FIGS. 2 and 3 show the horizontal deflection circuit modified in accordance with the present invention. Like circuit elements are designated by the same reference characters as in FIG. 1.

FIG. 2 shows the basic principle of the invention. The two inductors Le and Lk of FIG. 1 have been replaced by a transformer U. To be able to serve as a substitute for the two inductors Le and Lk, the transformer must be proportioned in a special manner. Regardless of the turns ratio, the open-circuit inductance of the transformer is chosen to be essentially equal to the value of the input inductor Le, and the short-circuit inductance of the transformer is essentially equal to the value of the commutating inductor Lk.

To permit the second switch S2 to be utilized for the connection of the dc voltage source UB, it is included in the circuit of that winding U1 of the transformer connected to the dc voltage UB.

In principle, it is of no consequence for the operation of the switch S2 whether it is inserted on

that side of the winding U1 connected to the positive operating potential +UB or on the side connected to ground. In practice, however, the solution shown in FIGS. 2 and 3 will be chosen since the gating of the controlled rectifier is less problematic in this case.

In compliance with pertinent safety regulations, the transformer U may be designed as an isolation transformer and can thus provide mains separation, which is necessary for various reasons. It is known from German Offenlegungschrift (DT-OS) No. 2,233,249 to provide dc isolation by designing the commutating inductor as a transformer, but this measure is not suited to attaining the object of the present invention.

If the energy to be taken from the dc voltage source is to be controlled as a function of the energy needed in the horizontal deflection circuit and in following subcircuits, the embodiment of the horizontal deflection circuit of FIG. 3 may be used.

The circuit including the winding U2 of the transformer U contains a third controlled switch S3, which, too, is inserted on the grounded side of the winding U2 for the reasons mentioned above. This third switch S3, just as the second switch S2, is operated at the frequency of a horizontal oscillator HO, but a control circuit RS whose input l is fed with a controlled variable is inserted between the oscillator and the switch S3. Depending on this controlled variable, the controlled rectifier of the third switch S3 can be caused to turn on earlier. A suitable controlled variable containing information on the energy consumption is, for example, the flyback pulse capable of being taken from the high voltage generating circuit (not shown). Details of the operation of this kind of energy control are described in applicant's German Offenlegungsschrift (DT-OS) No. b 2,253,386 and do not form part of the present invention.

With mains isolation, the additional, third switch S3 shown here has the advantage of being on the side isolated from the mains and eliminates the need for an isolation device in the control lead of the controlled rectifier.

As an isolation transformer, the transformer U may also carry additional windings U3 and U4 if power is to be supplied to the audio output stage, for example; in addition, the first switch S1 may be gated via such an additional winding.

The points marked at the windings U1 and U2 indicate the phase relationship between the respective voltages. Connected in parallel with the winding U1 and the second switch S2 is a capacitor CE which completes the circuit for the horizontal-frequency alternating current; this serves in particular to bypass the dc voltage source or the electrolytic capacitors contained therein.

If required, a well-known tuning coil may be inserted, e.g. in series with the second winding U2, without changing the basic operation of the horizontal deflection circuit according to the invention.

SALORA 1F6C CHASSIS 1F Electron beam deflection circuit including thyristors Further Discussion and deepening of knowledge, Thyristor horizontal output circuits:

1. An electron beam deflection circuit for a cathode ray tube with electromagnetic deflection by means of a sawtooth current waveform having a trace portion and a retrace portion, said circuit comprising: a deflection winding; a first source of electrical energy formed by a first capacitor; first controllable switching means comprising a parallel combination of a first thyristor and a first diode connected together to conduct in opposite directions, for connecting said winding to said first source during said trace portion, while said first switching means is turned on; a second source of electrical energy including a first inductive energy storage means coupled to a voltage supply; reactive circuit means including a combination of inductive and capacitive reactances for storing the energy supplied by said second source; second controllable switching means, substantially similar to said first one, for completing a circuit including said reactive circuit means and said first switching means, when turned on before the end of said trace portion, so as to pass through said first switching means an oscillatory current in opposite direction to that which passes through said first thyristor from said first source and to turn said first thyristor off after these two currents cancel out, the oscillatory current flowing thereafter through said first diode for an interval termed the circuit turn-off time, which has to be greater than the turn-off time of said first thyristor; wherein the improvement comprises: means for drawing, during at least a part of said trace portion, a substantial amount of additional current through said first switching means, in the direction of conduction of said first diode, whereby to perceptibly shift the waveform of the current flowing through said first switching means towards the negative values by an amount equal to that of said substantial additional current and to lengthen, in proportion thereto, said circuit turn-off time, without altering the values of the reactances in the reactive circuit which intervene in the determination of both the circuit turn-off and retrace portion time intervals.

2. A deflection circuit as claimed in claim 1, wherein said amount of additional current is greater than or equal to 5 per cent of the peak-to-peak value of the current flowing through the deflection winding.

3. A deflection circuit as claimed in claim 1, wherein said means for drawing a substantial amount of additional current through said first switching means comprises a resistor connected in parallel to said first capacitor.

4. A deflection circuit as claimed in claim 1, wherein said means for drawing an additional current is formed by connecting said first and second energy sources in series so that the current charging said reactive circuit means forms the said additional current.

5. A deflection circuit as claimed in claim 1, further including a series combination of an autotransformer winding and a second high-value capacitor, said combination being connected in parallel to said first switching means, wherein said autotransformer comprises an intermediate tap located between its terminals respectively connected to said first switching means and to said second capacitor, said tap delivering, during said trace portion, a suitable DC supply voltage lower than the voltage across said second capacitor; and wherein said means for drawing a substantial amount of additional current comprises a load to be fed by said supply voltage and having one terminal connected to ground; and further controllable switching means controlled to conduct during at least part of said trace portion and to remain cut off during said retrace portion, said further switching means being connected between said tap and the other terminal of said load.

The present invention relates to electron beam deflection circuits including thyristors, such as silicon controlled rectifiers and relates, in particular, to horizontal deflection circuits for television receivers.

The present invention relates to electron beam deflection circuits including thyristors, such as silicon controlled rectifiers and relates, in particular, to horizontal deflection circuits for television receivers. The present invention constitutes an improvement in the circuit described in U.S. Pat. No. 3,449,623 filed on Sept. 6, 1966, this circuit being described in greater detail below with reference to FIGS. 1 and 2 of the accompanying drawings. A deflection circuit of this type comprises a first thyristor switch which allows the conenction of the horizontal deflection winding to a constant voltage source during the time interval used for the transmisstion of the picture signal and for applying this signal to the grid of the cathode ray tube (this interval will be termed the "trace portion" of the scan), and a second thyristor switch which provides the forced commutation of the first one by applying to it a reverse current of equal amplitude to that which passes through it from the said voltage source and thus to initiate the retrace during the horizontal blanking interval.

The present invention constitutes an improvement in the circuit described in U.S. Pat. No. 3,449,623 filed on Sept. 6, 1966, this circuit being described in greater detail below with reference to FIGS. 1 and 2 of the accompanying drawings. A deflection circuit of this type comprises a first thyristor switch which allows the conenction of the horizontal deflection winding to a constant voltage source during the time interval used for the transmisstion of the picture signal and for applying this signal to the grid of the cathode ray tube (this interval will be termed the "trace portion" of the scan), and a second thyristor switch which provides the forced commutation of the first one by applying to it a reverse current of equal amplitude to that which passes through it from the said voltage source and thus to initiate the retrace during the horizontal blanking interval.A undirectional reverse blocking triode type thyristor or silicon controlled rectifier (SCR), such as that used in the aformentioned circuit, requires a certain turn-off time between the instant at which the anode current ceases and the instant at which a positive bias may be applied to it without turning it on, due to the fact that there is still a high concentration of free carriers in the vicinity of the middle junction, this concentration being reduced by a process of recombination independently from the reverse polarity applied to the thyristor. This turn-off time of the thyristor is a function of a number of parameters such as the junction temperature, the DC current level, the decay time of the direct current, the peak level of the reverse current applied, the amplitude of the reverse anode to cathode voltage, the external impedance of the gate electrode, and so on, certain of these varying considerably from one thyristor to another.

In horizontal deflection circuits for television receivers, the flyback or retrace time is limited to approximately 20 percent of the horizontal scan period, the retrace time being in the case of the CCIR standard of 625 lines, approximately 12 microseconds and, in the case of the French standard of 819 lines, approximately 9 microseconds. During this relatively short interval, the thyristor has to be rendered non-conducting and the electron beam has to be returned to the origin of the scan. The first thyristor is blocked by means of a series resonant LC circuit which is subject to a certain number of restrictions (limitations as to the component values employed) due to the fact that, inter alia, it simultaneously determines the turn-off time of the circuit which blocks the thyristor and it forms part of the series resonant circuit which is to carry out the retrace. To obtain proper operation of the deflection circuit of the aforementioned Patent, especially when used for the French standard of 819 lines per image, the values of the components used have to subject to very close tolerances (approximately 2%), which results in high costs.

The improved deflection circuit, object o

f the present invention, allows the lengthening of the turn-off time of the circuit for turning the scan thyristor off, without altering the values of the LC circuit, which are determined by other criteria, and without impairing the operation of the circuit.

According to the invention, there is provided an electron beam deflection circuit for a cathode ray tube with electromagentic deflection by means of a sawtooth current waveform having a trace portion and a retrace portion, said circuit comprising: a deflection winding; a first source of electrical energy formed by a first capacitor; first controllable switching means comprising a parallel combination of a first thyristor and a first diode, connected together to conduct in opposite directions, for connecting said winding to said first source during said trace portion when said first switching means is turned on; a second source of electrical energy including a first inductive energy storage means coupled to a voltage supply; reactive circuit means including a combination of inductive and capacitive reactances for storing the energy supplied by the said second source; a second controllable switching means, substantially identical with the first one, for completing a circuit including said reactive circuit means and said first switching means, when turned on, so as to pass through said first thyristor an oscillatory current in the opposite direction to that which passes through it from said first source and to turn it off after these two currents cancel out, the oscillatory current then flowing through said first diode for an interval termed the circuit turn-off time which has to be greater than the turn-off time of said first thyristor; and means for drawing duing at least a part of said trace portion a substantial amount of additional current from said first switching means in the direction of conduction of said first diode, whereby said circuit turn-off time is lengthened in proportion to the amount of said additional current, without altering the values of the reactances in the reactive circuit by shifting the waveform of the current flowing through said first switching means towards the negative by an amount equal to that of said additional current.

A further object of the invention consists in using the supplementary current in the recovery diode of the first switching means to produce a DC voltage which may be used as a power supply for the vertical deflection circuit of the television receiver, for example.

The invention will be better understood and other features and advantages thereof will become apparent from the following description and the accompanying drawings, given by way of example, and in which:

FIG. 1 is a schematic circuit diagram partially in bloc diagram form of a prior art deflection circuit according to the aforementioned Patent;

FIG. 2 shows waveforms of currents and voltages generated at various points in the circuit of FIG. 1;

FIG. 2 shows waveforms of currents and voltages generated at various points in the circuit of FIG. 1;FIG. 3 is a schematic diagram of a deflection circuit according to the invention which allows the principle of the improvement to be explained;

FIG. 4 is a diagram of the waveforms of the current through the first switching means 4, 5 of the circuit of FIG. 3;

FIG. 5 is a circuit diagram of another embodiment of the circuit according to the invention;

FIG. 6 is a schematic representation of the preferred embodiment of the circuit according to the invention; and

FIG. 7 shows voltage waveforms at various points of the high voltage autotransformer 21 of FIG. 6.

In all these Figures the same reference numerals refer to the same components.

FIG. 1 shows the horizontal deflection circuit described and claimed in the U.S. Pat. No. 3,449,623 mentioned above, which comprises a first source of electrical energy in the shape of a first capacitor 2 having a high capacitance C 2 for supplying a substantially constant voltage Uc 2 across its terminals. A first terminal of the first capacitor 2 is connected to ground, whilst its second terminal which supplies a positive voltage is connected to one of the terminals of a horizontal deflection winding shown as a first inductance 1. A first switching means 3, consisting of a first reverse blocking triode thyristor 4 (SCR) and a first recovery diode 5 in parallel, the two being interconnected to conduct current in opposite directions, is connected in parallel with the series combination formed by the deflection winding 1 and the first capacitor 2. The assembly of components 1, 2, 4 and 5 forms the final stage of the horizontal deflection circuit in a television receiver using electromagnetic delfection.

FIG. 1 shows the horizontal deflection circuit described and claimed in the U.S. Pat. No. 3,449,623 mentioned above, which comprises a first source of electrical energy in the shape of a first capacitor 2 having a high capacitance C 2 for supplying a substantially constant voltage Uc 2 across its terminals. A first terminal of the first capacitor 2 is connected to ground, whilst its second terminal which supplies a positive voltage is connected to one of the terminals of a horizontal deflection winding shown as a first inductance 1. A first switching means 3, consisting of a first reverse blocking triode thyristor 4 (SCR) and a first recovery diode 5 in parallel, the two being interconnected to conduct current in opposite directions, is connected in parallel with the series combination formed by the deflection winding 1 and the first capacitor 2. The assembly of components 1, 2, 4 and 5 forms the final stage of the horizontal deflection circuit in a television receiver using electromagnetic delfection.The deflection circuit also includes a drive stage for this final stage which here controls the turning off of the first thyristor 4 to produce the retrace or fly-back portion of the scan during the line-blanking intervals i.e. while the picture signal is not transmitted. This driver stage comprises a second voltage source in the shape of a DC power supply 6 which delivers a constant high voltage E. The negative terminal of the power supply 6 is connected to ground and its positive terminal to one of the terminals of a second inductance 7 of relatively high value, which draws a substantially lineraly varying current from the power supply 6 to avoid its overloading. The other terminal of th

e second inductance 7 is connected, on the one hand, to the junction of the deflection winding 1 and the first switching means 3 by means of a second inductance 8 and a second capacitor 9 in series and, on the other hand, to one of the terminals of a second controllable bi-directionally conducting switching means 10, similar to the first one 3, including a parallel combination of a second thyristor 11 and a second recovery diode 12 also arranged to conduct in opposite directions.

The respective values of the third inductance 8 (L 8 ) and of the second capacitor 9 (C 9 ) are principally selected so that, on the one hand, one half-cycle of oscillation of the first series resonant circuit L 8 - C 9 , (i.e. π √ L 8 . C 9 ) is longer than the turn-off time of the first thyristor 4, but still is as short as possible since this time interval determines the speed of the commutation of the thyristor 4, and, on the other hand, one half-cycle of oscillation of another series resonant circuit formed by L 1 , L 8 and C 9 , i.e. π √ (L 1 + L 8 ) . C 9 , is substantially equal to the required retrace time interval (i.e. shorter than the horizontal blanking interval).

The gate (control electrode) of the second thyristor 11 is coupled to the output of the horizontal oscillator 13 of the television receiver by means of a first pulse transformer 14 and a first pulse shaping circuit 15 so that it is fed short triggering pulses which are to turn it on.

The gate of the first thyristor 4 fed with signals of a substantially rectangular waveform which are negative during the horizontal blanking intervals, is coupled to a winding 16 by means of a second pulse shaping circuit 17, the winding 16 being magnetically coupled to the second inductance 7 to make up the secondary winding of a transformer of which the inductance 7 forms the primary winding. It will be noted here that it is also possible to couple the secondary winding 16 magnetically to a primary winding connected to a suitable output (not shown) of the horizontal oscillator 13.

The operation of a circuit of this type will be explained below with reference to FIG. 2 which shows the waveforms at various points in the circuit of FIG. 1 during approximately one line period.

FIG. 2 is not to scale since one line period (t 7 - t 0 ) is equal to 64 microseconds in the case of 625 lines and 49 microseconds in the case of 819 lines, while the durations of the respective horizontal blanking intervals are approximately 12 and 9.5 microseconds.

FIG. 2 is not to scale since one line period (t 7 - t 0 ) is equal to 64 microseconds in the case of 625 lines and 49 microseconds in the case of 819 lines, while the durations of the respective horizontal blanking intervals are approximately 12 and 9.5 microseconds.Waveform A shows the form of the current i L1 passing through deflection winding 1, this current having a sawtooth waveform substantially linear from t 0 to t 3 and from t 5 to t 7 , and crossing zero at time instants t 0 and t 7 , and reaching values of + I 1m and - I 1m , at time instants t 3 and t 5 respectively, these being its maximum positive and negative amplitudes.

During the second half of the trace portion of the horizontal deflection cycle, that is to say from t 0 to t 3 , the thyristor 4 of the first switching means 3 is conductive and makes the high value capacitor 2 discharge through the deflector winding 1, which has a high inductance, so that current i L1 increases linearly.

A few microseconds (5 to 8 μ s) before the end of the trace portion, i.e. at time instant t 1 , the trigger of the second thyristor 11 receives a short voltage pulse V G11 which causes it to turn on as its anode is at this instant at a positive potential with respect to ground, which is due to the charging of the second capacitor 9 through inductances 7 and 8 by the voltage E from the power supply 6.

When thyristor 11 is made conductive at time t 1 , on the one hand, inductance 7 is connected between ground and the voltage source 6 and a linearly increasing current flows through it and, on the other hand, the reactive circuit 8, 9 forms a loop through the second and first switching means 10 and 3, thus forming a resonant circuit which draws an oscillatory current i 8 ,9 of frequency ##EQU1##

This oscillatory current i 8 ,9 will pass through the first switching means 3, i.e. thyristor 4 and diode 5, in the opposite direction to that of current i L1 . Since the frequency f 1 is high, current i 8 ,9 will increase more rapidly than i L1 and will reach the same level at time t 2 , that is to say i 8 ,9 (t 2 ) = -i L1 (t 2 ) and these currents will cancel out in the thyristor 4 in accordance with the well known principle of forced commutation. After time instant t 2 , current i 8 ,9 continues to increase more rapidly than i L1 , but the difference between them (i 8 ,9 - i L1 ) passes the diode 5 (see wave form B) until it becomes zero at time instant t 3 which is the turn off time instant of the first switching means 3, at which the retrace begins.

The interval between the time instant t 2 and t 3 , i.e. (t 3 -t 2 ), during which diode 5 is conductive and the thyristor is reverse biased will be termed in what follows the circuit turn-off time and it should

be greater than the turn-off time of the thyristor 4 itself since the latter will subsequently become foward biased (i.e. from t 3 to t 5 ) by the retrace or flyback pulse (see waveform E) which should not trigger it.

At time instant t 3 , the switching means 3 is opened (i 4 and i 5 are both zero -- see waveforms B and C) and the reactive circuit 8, 9 forms a loop through capacitor 2 and the deflection coil 1 and thus a series resonant circuit including (L 1 + L 8 ) and C 9 , C 2 being of high value and representing a short circuit for the flyback frequency ##EQU2## thus obtained.

The retrace which stated at time t 3 takes place during one half-cycle of the resonant circuit formed by reactances L 1 , L 8 and C 9 , i.e. during the interval between t 3 and t 5 . In the middle of this interval i.e. at time instant t 4 , both i L1 (waveform A) and i 8 ,9 (waveform D) pass through zero and change their sign, whereas the voltage at the terminals of the first switching means 3 (V 3 , waveform E) passes through a maximum. Thus, from t 4 onwards, thyristor 11 will be reverse biased and diode 12 will conduct the current from the resonant circuit 1, 8 and 9 in order to turn the second thyristor 11 off.

At time instant t 5 , when current i L1 has reached - I 1m and when voltage v 3 falls to zero, diode 5 of the first switching means 3 becomes conductive and the trace portion of scan begins.

Current i 8 ,9 nevertheless continues to flow in the resonant circuit 8, 9 through diodes 5 and 12, which causes a break to appear in waveform D at t 5 , and a negative peak to appear in waveform D and a positive one in waveform B in the interval between t 5 and t 6 , these being principally due to the distributed capacities of coil 1 or to an eventual capacitor (not shown) connected in parallel to the first switching means 3.

At time instant t 6 , diode 12 of the second switching means 10 ceases to conduct after having allowed thyristor 11 time to become turned off completely.

The level of current i 8 ,9 at time instant t 5 (i.e. I c ) as well as the negative peak I D12 in i 8 ,9 and the positive peak I D5 in i 5 depend on the values of L 8 and C 9 in the same way as does the turn-off time of the circuit (t 3 - t 2 ). If, for example, L 8 and C 9 , are increased I D5 increases towards zero and this could cause diode 5 to be cut off in an undesirable fashion. I c also increases towards zero, which is liable to cause diode 12 to be blocked and thyristor 11 to trigger prematurely.

From the foregoing it can be clearly seen that the choice of values for L 8 and C 9 is subject to four limitations which prevent the values from being increased to lengthen the turn-off time of the driver circuit of first switching thyristor 4 so as to forestall its spurious triggering.

Waveform F shows the voltage v G4 obtained at the gate of thyristor 4 from the secondary winding 16 coupled to the inductor 7. This voltage is positive from t 0 to t 1 and from t 6 to t 7 and is negative between t 2 and t 6 i.e. while the second switching means 10 is conducting.

The present invention makes the lengthening of the turn-off time of thyristor 4 possible without altering the parameters of the circuit such as inductance 8 and capacitor 9.

In the circuit shown in FIG. 3, which illustrates the principle of the present invention, means are added to the circuit in FIG. 1 which enable the turn-off time to be lengthened by connecting a load to diode 5 so as to increase the current which flows through it during the time that it is conductive. These means are here formed by a resistor 18 connected in parallel with a capacitor 20 (which replaces capacitor 2) which is of a higher capacitance so that, in practice, it holds its charge during at least one half of the line period. FIG. 4, which shows the waveform of the current in the first switching means 3 for a circuit as shown in FIG. 3, makes it possible to explain how this lenthening of the turn-off time is achieved.

In the circuit shown in FIG. 3, which illustrates the principle of the present invention, means are added to the circuit in FIG. 1 which enable the turn-off time to be lengthened by connecting a load to diode 5 so as to increase the current which flows through it during the time that it is conductive. These means are here formed by a resistor 18 connected in parallel with a capacitor 20 (which replaces capacitor 2) which is of a higher capacitance so that, in practice, it holds its charge during at least one half of the line period. FIG. 4, which shows the waveform of the current in the first switching means 3 for a circuit as shown in FIG. 3, makes it possible to explain how this lenthening of the turn-off time is achieved.In FIG. 4, the broken lines show the waveform of the current in the first switch device 3 in the circuit of FIG. 1, this waveform being produced by adding waveforms B and C of FIG. 2. The current i 4 above the axis flows through thyristor 4 and current i 5 below the axis flows through diode 5. When the capacitance C 20 of the capacitor in series with the deflector coil is increased to some tens of microfarads (C 2 having been of the order of 1 μ F) and when there is connected in parallel with capacitor 20 a resistor 18 the value of which is calculated to draw a strong current I R18 from capacitor 20, that is to say a current at least equal to 0,1 I m (I m being of the order of some tens of amperes), current I R18 is added to that i 5 which flows through diode 5 without in any way altering the linearity of the trace portion nor the oscillatory commutation of thyristor 4 which is brought about by the resonant circuit L 8 , C 9 .

The fact of loading capacitor C 20 by means of a resistor 18 thus has the effect of permanently displacing the waveform of the current in the negative direction by I R18 . Thus, during the trace portion of the scan, the transfer of the current from the diode 5 to the thyristor 4 begins at time t 10 instead of t 0 , that is to say with a delay proportional to I R18 . The effect of the triggering pulse delivered by the horizontal oscillator (13 FIG. 1) to the second thyristor 11 at time instant t 1 , will be to start the commutation process of the first thyristor 4 when the current it draws is less by I R18 than that i 4 (t 1 ) which it would have been drawing had there been no resistor 18. Because of this, the turn-off time of the thyristor 4 proper, which as has been mentioned increases with the maximum current level passing throught it, is slightly reduced. Moreover, because the oscillatory current i 8 ,9 (FIG. 2) from circuit L 8 , C 9 which flows through thyristor 4 in the opposite direction is unchanged, it reaches a value equal to that of the current i L1 (FIG. 1) flowing in the coil 1 in a shorter time, that is to say at time t 12 . Diode 5 will thus take the oscillatory current i 8 ,9 (FIG. 2) over in advance with respect ro time instant t 2 and will conduct it until it reaches zero value at a time instant t 13 later than t 3 , the amounts of advance (t 2 - t 12 ) and delay (t 13 - t 3 ) being practically equal.

It can thus be seen in FIG. 4 that the circuit turn-off time T R of a circuit according to the invention and illustrated by FIG. 3 is distinctly longer than that T r of the circuit in FIG. 1. This increase in the turn-off time (T R - T r ) depends on the current I R18 and increases therewith.

It can thus be seen in FIG. 4 that the circuit turn-off time T R of a circuit according to the invention and illustrated by FIG. 3 is distinctly longer than that T r of the circuit in FIG. 1. This increase in the turn-off time (T R - T r ) depends on the current I R18 and increases therewith.It should be noted at this point that the current I R18 produces a voltage drop at the terminals of the resistor the only effect of which is to heat up the resistor since the level of this voltage (40 to 60 volts) does not necessarily have a suitable value to be used as a voltage supply for other circuits in an existing transistorised television receiver.

In accordance with one embodiment of the invention, illustrated in FIG. 5, an application is proposed for the additional current which is to be drawn through diode 5. In FIG. 5, the positive terminal of capacitor 20 is connected by a conductor 19 to the negative pole of the power supply 6 and the voltage at the terminals of capacitor 20 is thus added to that E from the source 6.

In the preferred embodiment of the present invention, which is shown in FIG. 6, it is possible to cause a supplementary current of a desired value to flow through the first diode 5 while obtaining a voltage which has a suitable value for use in another circuit in the television receiver.

If the voltage at the terminals of capacitor 20 in FIG. 3 is not a usable value, it is possible to connect in parallel with the series circuit comprising the deflector coil 1 and the capacitor 2 in FIG. 1, i.e. in parallel with the terminals of the first switching means 3, a series combination of an autotransformer 21 and a high value capacitor 22 (comparable with capacitor 20 in FIGS. 3 and 5). The autotransformer 21 has a tap 23 is suitably positioned between the terminal connected to capacitor 22 at the tap 24 connected to the first switching means 3. This autotransformer 21 may be formed by the one conventionally used for supplying a very high voltage to the cathode ray tube, as described for example in U.S. Pat. No. 3,452,244; such a transformer comprises a voltage step-up winding between taps 24 and 25, which latter is connected to a high voltage rectifier (not shown).

The waveform of the voltage at the various points in the autotransformer is shown in FIG. 7, in which waveform A shows the voltage at the terminals of capacitor 22, waveform B the voltage at tap 24 and waveform C the voltage at tap 23 of the autotransformer 21.

The voltage V c22 at the terminals of capacitor 22 varies slightly about a mean value V cm . It is increasing while diode 5 is conducting and decreasing during the conduction of the thyristor 4.

The voltage v 24 at tap 24 follows substantially the same curve as waveform E in FIG. 2, that is to say that during the retrace time interval from t 13 to t 5 to a positive pulse called the flyback pulse is produced and, during the time interval while the first switching means 3 is conducting, the voltage is zero. The mean valve of the voltage v 24 at tap 24 of the auto-transformer 21 is equal to the mean value V cm of the voltage at the terminals of capacitors 2 and 22.

Thus, there is obtained at tap 23 a waveform which is made up, during the retrace portion, of a positive pulse whose maximum amplitude is less than that of v 24 at tap 24 and, during the trace portion, of a substantially constant positive voltage, the level V of which is less than the mean value V cm of the voltage v c22 at the terminals of capacitor 22. By moving tap 23 towards terminals 24 the amplitude of the pulse during fly-back increases while voltage V falls and conversely by moving tap 23 towards capacitor 22 voltage V increases and the amplitude of the pulse drops.

In more exact terms, the voltage V at tap 23 is such that the means value of v 23 is equal to V cm . It has thus been shown that by choosing carefully the position of tape 23, a voltage V may be obtained during the trace portion of the scan, which may be of any value between V cm and zero.

This voltage V is thus obtained by periodically controlled rectification during the trace portion of the scan. For this purpose an electronic switch is used to periodically connect the tap 23 of trnasformer winding 21 to a load. This switch is made up of a power transistor 26 whose collector is connected to tap 23 and the emitter to a parallel combination formed by a high value filtering capacitor 27 and the load which it is desired to supply, which is represented by a resistor 28. The base of the transistor 26 receives a control voltage to block it during retrace and to unblock it during the whole or part of the trace period. A control voltage of this type may be obtained from a second winding 29 magnetically coupled to the inductance 7 of the deflection circuit and it may be transmitted to the base of transistor 26 by means of a coupling capacitor 30 and a resistor 31 connected between the base and the emitter of transistor 26.

It may easily be seen that the DC collector/emitter current in transistor 26 flows through the first diode 5 of the first switching means 3 via a resistor 28 and the part of the winding of auto-transformer 21 located between taps 23 and 24.

Experience has shown that a circuit as shown in FIG. 6 can supply 24 volts with a current of 2 amperes to the vertical deflection circuit of the same television set, the voltage at the terminals of capacitor 22 being from 50 to 60 volts.

It should be mentioned that, when the circuit which forms the load of the controlled rectifier 26, 27 does not draw enough current to sufficiently lengthen the circuit turn-off time T R , an additional resistor (not shown) may be connected between the emitter of transistor 26 and ground or in parallel to capacitor 22, which resistor will draw the additional current required.

SALORA 1F6C CHASSIS 1F Gating circuit for television SCR deflection system AND REGULATION / stabilization of horizontal deflection NETWORK CIRCUIT with Transductor reactor / Reverse thyristor energy recovery circuit.In a television deflection system

employing a first SCR for coupling a deflection winding across a source of energy during a trace interval of each deflection cycle and a second SCR for replenishing energy to the source of energy during a commutation interval of each deflection cycle, a gating circuit for triggering the first SCR. The gating circuit employs a voltage divider coupled in parallel with the second SCR which develops gating signals proportional to the voltage across the second SCR.

1. In a television deflection system in which a first switching means couples a deflection winding across a source of energy during a trace interval of each deflection cycle and a second switching means replenishes energy to said source of energy during a commutation interval of each deflection cycle, a gating circuit for said first switching means, comprising:

capacitive voltage divider means coupled in parallel with said second switching means for developing gating signals proportional to the voltage across said second switching means; and

means for coupling said voltage divider means to said first switching means to provide for conduction of said first switching means in response to said gating signals.

2. A gating circuit according to claim 1 wherein said voltage divider includes first and second capacitors coupled in series and providing said gating signals at the common terminal of said capacitors. 3. A gating circuit according to claim 2 wherein said first and second capacitors are proportional in value to provide for the desired magnitude of gating signals. 4. A gating circuit according to claim 3 wherein said means for coupling said voltage divider means to said first switching means includes an inductor. 5. A gating circuit according to claim 4 wherein said inductor and said first and second capacitors comprise a resonant circuit having a resonant frequency chosen to shape said gating signal to improve switching of said first switching means.

This invention relates to a gating circuit for controlling a switching device employed in a deflection circuit of a television receiver.

This invention relates to a gating circuit for controlling a switching device employed in a deflection circuit of a television receiver.

Various deflection system designs have been utilized in television receivers. One design employing two bidirectional conducting switches and utilizing SCR's (thyristors) as part of the switches is disclosed in U.S. Pat. No. 3,452,244. In this type deflection system, a first SCR is

employed for coupling a deflection winding across a source of energy during a trace interval of each deflection cycle, and a second SCR is employed for replenishing energy during a commutation interval of each deflection cycle. The first SCR is commonly provided with gating voltage by means of a separate winding or tap of an input reactor coupling a source of B+ to the second SCR.

Various regulator system designs have been utilized in conjunction with the afore described deflection system to provide for uniform high voltage production as well as uniform picture width with varying line voltage and kinescope beam current conditions.