The TELEFUNKEN CHASSIS 615A1 is a semi modular chassis type.

The basis of the TELEFUNKEN CHASSIS 615A1 is coming from TELEFUNKEN CHASSIS 714A From 1980 which you will see HERE !

Obviously the TELEFUNKEN CHASSIS 714A is higly different !

This type of chassis was fitted from 15 to 27 Inches screen formats and even in stereo versions !

When dismounted from the wooden cabinet it's a FLEXY monocarrier Chassis (Not a Flexy Girl Which is another thing !) ; since it has no metal bars soldered along his perimeter it's a very wobbling chassis.

This chassis was very reliable and durable but was suffering often from a high rate of dry joint.

It runs very cold.

TDA1940 - SYNCHRONIZATION

TDA1870 - FRAME DEFLECTION

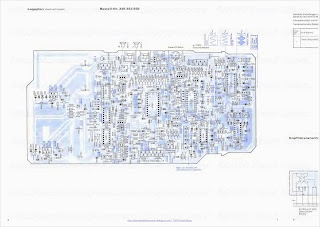

TELEFUNKEN PALCOLOR CHASSIS 615A Schaltnetzteil

(AT 349354097), IN GERMAN:

1. Schaltnetzteil,

insbesondere f·ur einen Fernsehempf·anger, mit einer Arbeitswicklung

(5), einem Schalttransistor (6), einer R·uckkopplungswicklung (7) und

einer Regelschaltung (ii) auf der Prim·arseite sowie mit Gleichrichtern

(15,16, 20) zur Erzeugung von Betriebsspannungen (U11U2#U3) auf der

Sekund·arseite eines Trenntransformators (1) gekenn zeichnet durch

folgende Merkmale: a) An eine Wicklung (19) ist ein Thyristor (24)

angeschlos sen, der f·ur die w·ahrend der siromf·uhrenden Phase der

Schalttransistoren (6) an der Wicklung (19) auftreten de Spannung in

Durchlassrichtung gepolt ist. b) An die Steuerelektrode des Thyristors

(24) ist eine der Betriebsspannungen (U2) in solcher H·ohe angelegt,

dass der Thyristor (24) im Normalbetrieb gesperrt bleibt und bei einem

unzul·assigen Anstieg der Betriebs spannung (U3) z·undet.

1. Schaltnetzteil,

insbesondere f·ur einen Fernsehempf·anger, mit einer Arbeitswicklung

(5), einem Schalttransistor (6), einer R·uckkopplungswicklung (7) und

einer Regelschaltung (ii) auf der Prim·arseite sowie mit Gleichrichtern

(15,16, 20) zur Erzeugung von Betriebsspannungen (U11U2#U3) auf der

Sekund·arseite eines Trenntransformators (1) gekenn zeichnet durch

folgende Merkmale: a) An eine Wicklung (19) ist ein Thyristor (24)

angeschlos sen, der f·ur die w·ahrend der siromf·uhrenden Phase der

Schalttransistoren (6) an der Wicklung (19) auftreten de Spannung in

Durchlassrichtung gepolt ist. b) An die Steuerelektrode des Thyristors

(24) ist eine der Betriebsspannungen (U2) in solcher H·ohe angelegt,

dass der Thyristor (24) im Normalbetrieb gesperrt bleibt und bei einem

unzul·assigen Anstieg der Betriebs spannung (U3) z·undet.

2. Netzteil nach Anspruch 1, dadurch gekennzeichnet, dass die Betriebsspannung (U3) ·uber einen Spannungsteiler (25,26) an die Steuerelektrode des Thyristors (24) angelegt ist.

3. Netzteil nach Anspruch 1, dadurch gekennzeichnet, dass die Wicklung (19) eine Sekund·arwicklung des Trenntransforma tors (1) ist.

Bei

Ger·aten der Nachrichtentechnik wie z.B. einem Fernsehempf·anger ist es

bekannt, die f·ur die einzelnen Stufen notwendigen Betriebsspannungen

mit einem Schaltnetzteil aus der Netzspannung zu erzeugen (Funkschau

1975, Heft 5, Seite 40-43). Ein Schaltnetzteil erm·oglicht die f·ur den

Anschluss ·ausserer Ger·ate und f·ur die Massnahmen zur Schutzisolierung

vorteilhafte galvanische Trennung der Empf·angerschaltung vom Netz. Da

ein Schaltnetzteil mit einer gegen·uber der Netzfrequenz hohen Frequenz

von ca. 30 kHz arbeitet, kann der zur galvanischen Trennung dienende

Trenntransformator gegen·uber einem Netztrafo f·ur 50 Hz wesentlich

kleiner und leichter ausgebildet sein. Durch mehrere Wicklungen oder

Wicklungsabgriffe und angeschlossene Gleichrichter k·onnen auf der

Sekund·arseite des Trenntransformators Betriebs~ spannungen

unterschiedlicher Gr·osse und Polarit·at erzeugt werden.

Bei

Ger·aten der Nachrichtentechnik wie z.B. einem Fernsehempf·anger ist es

bekannt, die f·ur die einzelnen Stufen notwendigen Betriebsspannungen

mit einem Schaltnetzteil aus der Netzspannung zu erzeugen (Funkschau

1975, Heft 5, Seite 40-43). Ein Schaltnetzteil erm·oglicht die f·ur den

Anschluss ·ausserer Ger·ate und f·ur die Massnahmen zur Schutzisolierung

vorteilhafte galvanische Trennung der Empf·angerschaltung vom Netz. Da

ein Schaltnetzteil mit einer gegen·uber der Netzfrequenz hohen Frequenz

von ca. 30 kHz arbeitet, kann der zur galvanischen Trennung dienende

Trenntransformator gegen·uber einem Netztrafo f·ur 50 Hz wesentlich

kleiner und leichter ausgebildet sein. Durch mehrere Wicklungen oder

Wicklungsabgriffe und angeschlossene Gleichrichter k·onnen auf der

Sekund·arseite des Trenntransformators Betriebs~ spannungen

unterschiedlicher Gr·osse und Polarit·at erzeugt werden.Ein solches Schaltnetzteil enth·alt eine Regelschaltung zur Stabilisierung der Amplitude der auf der Sekund·arseite erzeugten Betriebsspannungen. In dieser Regelschaltung wird eine durch Gleichrichtung der Impulsspannung am Trafo gewonnene Stellgr·osse erzeugt und mit einer Bezugsspannung verglichen. In Abh·angigkeit von der Abweichung wird der Schaltzeitpunkt des auf der Prim·arseite vorgesehenen elektronischen Schalters so gesteuert, dass die Amplitude der erzeugten Betriebsspannungen konstant bleibt.

Bei einem solchen Schaltnetzteil kann die genannte Regelschaltung z.B. durch ein fehlerhaftes Bauteil ausfallen. Die Regelung der Amplitude der erzeugten Betriebsspannungen ist dann unkontrolliert. Die Betriebsspannungen k·onnen dann auf den doppelten oder dreifachen Wert ansteigen. Dadurch besteht die Gefahr, dass das Schaltnetzteil oder die an die Betriebsspannungen angeschlossenen Verbraucher wie z.B. der Heizfaden der Bildr·ohre oder der Zeilenendstufentransistor zerst·ort werden. Der Anstieg der Betriebsspannungen kann dar·uberhinaus einen Anstieg der im Fernsehempf·anger erzeugten Hochspannung und dadurch eine R·ontgenstrahlung ausl·osen.

Es ist auch ein Schaltnetzteil bekannt (DE-OS 27 27 332), bei dem zum Schutz gegen einen zu starken Anstieg der erzeugten Betriebsspannungen aus der Impulsspannung an der Prim·arseite des Trafos eine Stellgr·osse gewonnen wird, die beim ·Uberschreiten eines Schwellwertes den R·uckkopplungsweg unwirksam steuert. Durch die Unterbrechung des R·uckkopplungsweges kann das Schaltnetzteil nicht mehr schwingen, so dass in erw·unschter Weise auch keine Betriebsspannungen mehr erzeugt werden. Diese Schaltung erfordert jedoch eine Vielzahl von Bauteilen und ist daher relativ teuer.

Der Erfindung liegt die Aufgabe zugrunde, eine sicher wirkende Schutzschaltung mit verringertem Schaltungsaufwand gegen

die oben

beschriebenen Gefahren zu schaffen.

die oben

beschriebenen Gefahren zu schaffen.Diese Aufgabe wird durch die im Anspruch 1 beschriebene Erfindung gel·ost. Vorteilhafte Weiterbildungen der Erfindung sind in den Unteranspr·uchen beschrieben.

Die Erfindung beruht auf folgender ·Uberlegung: Der Schalttransistor auf der Prim·arseite wird von der prim·arseitigen R·uckkopplungswicklung w·ahrend seiner stromleitenden Phase mit einem Basisstrom angesteuert. Wenn jetzt eine Sekund·arwicklung w·ahrend dieser stromleitenden Phase stark belastet, z.B. ·uber den Thyristor kurzgeschlossen wird, bricht auch die Spannung an der prim·arseitigen R·uckkopplungswicklung zusammen. Diese Wicklung kann dann f·ur den Schalttransistor nicht mehr einen f·ur den leitenden Betrieb ausreichenden Basis strom liefern. Das Schaltnetzteil schwingt dann nicht mehr, so dass die sekund·arseitigen Betriebsspannungen in erw·unschter Weise zusammenbrechen. Der schaltungstechni- sche Aufwand ist gering. Er besteht vorzugsweise aus einem Thyristor und zwei Widerst·anden.

Ein Ausf·uhrungsbeispiel der Erfindung wird anhand der Zeichnung erl·autert. Darin zeigen Figur 1 ein erfindungsgem·ass ausgebildetes Schaltnetzteil und Figur 2 Kurven zur Erl·auterung der Wirkungsweise. Dabei zeigen die kleinen Buchstaben, an welchen Punkten in Figur 1 die Spannungen gem·ass Figur 2 stehen.

Das Schaltnetzteil gem·ass Figur 1 enth·alt auf der Prim·arseite des Trenntransformators 1 den Netzgleichrichter 2, den Ladekondensator 3, den Strom-Messwiderstand 4, die Prim·arwicklung 5 den Schalttransistor 6, die zur Schwingungserzeugung dienende R·uckkopplungswicklung 7, den zur Steuerung des Schalttransistors 6 dienenden Thyristor 8, die Regelwicklung 9, den zur Erzeugung der Regelspannung dienenden Gleichrichter 10 sowie die zur Stabilisierung der Betriebsspannungen dienende Regelschaltung 11 mit dem Transistor 12 und der eine Referenzspannung lieferndenZenerdiode 13. Die Sekund·arwicklung 14 liefert ·uber den Gleichrichter 15 eine erste Betriebsspannung U1 von 150 V. Ein Abgriff der Wicklung 14 liefert ·uber den Gleichrichter 16 eine zweite Betriebsspannung U2 von 12 V f·ur einen Fernbedienungsempf·anger.

Eine weitere Sekund·arwicklung 19 liefert ·uber den Gleichrichter 20 eine dritte Betriebsspannung U3 von 12 V. Die Polung der Wicklungen 14,19 und der Gleichrichter 15,16,20 ist derart, dass die Gleichrichter 15,16,20 w·ahrend der Sperrphase des Schalttransistors 6 durch die sekund·arseitig auftretenden Impulsspannungen leitend gesteuert sind und die angeschlossenen Ladekondensatoren aufladen.

An das untere Ende der Wicklung 19 ist zus·atzlich der Thyristor 24 angeschlossen. An die Steuerelektrode b des Thyristors 24 ist die Betriebs spannung U2 ·uber den Spannungsteiler 25,26 angelegt.

Die Wirkungsweise der Schaltung wird anhand der Figur 2 erl·autert. Es sei angenommen, dass das Schaltnetzteil im Zeitpunkt tl in Betrieb genommen wird. Mit der Diode 21 wird aus der Netzspannung am Punkt d ein positiver Impuls erzeugt. Dieser gelangt ·uber den Kondensator 23 auf die Basis des Schalttransistors 6 und steuert diesen leitend. Dadurch beginnt das Schaltnetzteil zu schwingen, wobei die Schwingung durch die R·uckk

opplungswicklung 7

aufrechterhalten wird. Am Punkt a entsteht dann eine m·aanderf·ormige

Wechselspannung mit einer Frequenz von etwa 25-30 kHz.

opplungswicklung 7

aufrechterhalten wird. Am Punkt a entsteht dann eine m·aanderf·ormige

Wechselspannung mit einer Frequenz von etwa 25-30 kHz.Die daraufhin in den Sekund·arwicklungen 14,19 erzeugten Impulse erzeugen in der beschriebenen Weise die Betriebsspannungen U1,U2,U3. Der Spannungsteiler 25,26 ist so bemessen, dass der Thyristor 24 gesperrt bleibt, d.h. die Spannung am Punkt 6 jst kleiner als 0,7 V. Der Thyristor 24 hat dann keine Wirkung. Dir Amplitude der Spannungen Ui,U2,U3 wird ·uber die Regelschaltung 11 stabilisiert.

Es sei jetzt angenommen, dass durch einen Fehler in der Regelschaltung 11, z.B. durch Ausfall eines Bauteiles, die Regelung zur Stabilisierung der Betriebsspannungen U1,U2,U3 nicht mehr wirkt und diese Betriebsspannungen stark ansteigen. Dadurch steigt auch die Spannung am Punkt b an.

Im Zeitpunkt t2 erreicht diese Spannung den Wert von 0,7 V, so dass der Thyristor 24 z·undet. Der untere Teil der Wicklung 19 ist jetzt praktisch kurzgeschlossen. Das Netzteil ist dadurch sekund·arseitig so stark belastet, dass die R·uck kopplungswicklung 7 keinen ausreichenden Basisstrom zur Steuerung des Schalttransistors 6 in seine stromleitende Phase mehr liefert. Im Zeitpunkt t2 bricht die Schwingung des Schaltnetzteiles ab, so dass auch die Wechselspannung am Punkt a auf null abf·allt. Den Ladekondensatoren der Gleichrichter 15,16,20 wird kein Strom mehr zugef·uhrt, so dass die Betriebspannungen U1,U2,U3 nicht weiter ansteigen k·onnen, sondern entsprechend den wirksamen Entladezeitkonstanten abfallen. Das Schaltnetzteil w·urde auf diese Weise an sich beliebig lange ausgeschaltet bleiben.

Im Zeitpunkt t3 erscheint am Punkt b der n·achste aus der Netzspannung gewonnene Startimpuls, der den Schalttransistor 6 wieder leitend steuert, so dass die Wechselspannung am Punkt a wieder auftritt. Das Schaltnetzteil geht also in einen getakteten Betrieb ·uber, bei dem die ·ubertragene Leistung entsprechend dem Zeitverh·altnis zwischen Einschaltphase und Ausschaltphase der Spannung am Punkt a betr·achtlich verringert ist. Die Betriebsspannungen U11U2,U3 k·onnen nicht mehr unzul·assig hohe Werte annehmen.

CHASSIS 615A1 Simplified horizontal / line deflection circuit.

-----------------------------------------------------------------------------------------------

A horizontal deflection circuit makes a sawtooth

A horizontal deflection circuit makes a sawtoothcurrent flow through a deflection coil. The current

will have equal amounts of positive and negative

current. The horizontal switch transistor conducts

for the right hand side of the picture. The damper

diode conducts for the left side of the picture.

Current only flows through the fly back capacitor

during retrace time.

For time 1 the transistor is turned on. Current

ramps up in the yoke. The beam is moved from the

center of the picture to the right edge. Energy is

stored on the inductance of the yoke.

E=I2L/2

For time 2 the transistor is turned off. Energy

transfers from the yoke to the flyback capacitor. At

the end of time two all the energy from the yoke is

placed on the flyback capacitor. There is zero

current in the yoke and a large voltage on the

capacitor. The beam is quickly moved from the

right edge back to the middle of the picture.

During time 3 the energy on the capacitor flows

During time 3 the energy on the capacitor flowsback into the yoke. The voltage on the flyback

capacitor decreases while the current in the yoke

builds until there is no voltage on the capacitor. By

the end of time 3 the yoke current is at it's

maximum amount but in the negative direction.

The beam is quickly deflected form the center to the

left edge.

Time 4 represents the left hand half of the picture.

Yoke current is negative and ramping down. The

beam moves from the left to the center of the

picture.

The current that flows when the horizontal switch is

closed is approximately:

Ipk ≅ Vcc T / Ldy

Ipk = collector current

T = 1/2 trace time

Ldy = total inductance (yoke + lin coil + size coil)

note:The lin coil inductance varies with current.

______

Tr ≅ 3.14 √ L C

The current that flows during retrace is produced by

the C and L oscillation. The retrace time is 1/2 the

oscillation frequency of the L and C.

I2L /2 ≅ V2C /2 or I2L = V2C As stated earlier the energy in the yoke moves to the

flyback capacitor during time 2.

V= the amount of the flyback pulse that is above the

supply voltage.

D.C. annualizes is inductors are considered

D.C. annualizes is inductors are consideredshores, capacitors are open and generally

semiconductors are removed. The voltage at the

point “B+” is the supply voltage. The collector

voltage of Q1 is also at the supply voltage. The

voltage across C2 is equal to the supply voltage.

When we A.C. annualize this circuit we will find

that the collector of Q1 has a voltage that ranges

from slightly negative to 1000 volts positive. The

average voltage must remain the same as the D.C.

value.

In the A.C. annualizes of the circuit, the

inductance of the yoke (DY) and the inductance of

the flyback transformer are in parallel. The

inductance of T2 is much larger than that if the

DY. This results is a total system inductance of

about 10% to 20% less than that of the DY it’s

self.

The voltage across the Q1 is a half sinusoid pulse during the flyback or retrace period and close to zero at

all other times. It is not possible or safe to observe this point on an oscilloscope without a proper high

frequency high voltage probe. Normally use a 100:1 probe suitable for 2,000V peak. The probe must have

been high frequency calibrated recently.

HORIZONTAL SIZE / E/W AMPLITUDE - CORRECTION CIRCUIT:

There are several different methods of adjusting horizontal size.

SIZE COIL

SIZE COILAdd a variable coil to the yoke current path

causes the total inductance to vary with the coils

setting.

The yoke current is related to supply voltage,

trace time and total inductance. This method

has a limited range!

The horizontal section uses a PWM to set the

horizontal size. One DAC sets the horizontal

size and another DAC sets the pincushion and

trap.

The Raster Centering (D.C. centering) is

controlled by a DAC.

On small monitors the retrace time is fixed. On

large monitors or wide frequency range monitors

two different retrace times are available. The flyback time is set by the micro computer by selecting two

different flyback capacitors. At slow frequencies the longer retrace time is selected.

Different S corrector capacitor values are selected by the micro computer. At the highest frequency the

smallest capacitor is selected.

SPLIT DIODE MODULATOR

SPLIT DIODE MODULATORThis horizontal circuit consists of two parts. D1, C1, C2 and DY are the components as described above.

D2, C3, C4 and L1 are a second “dummy” horizontal section that does not cause deflection current. By the

D.C. analyzing this circuit the voltage across C2 + C4 must equal the supply voltage (B+). Deflection

current in the DY is related to the supply voltage minus the voltage across C4. For a maximum horizontal

size the control point must be held at ground. This causes the dummy section to not operate and the DY

section will get full supply voltage. If the control point is at 1/3 supply then the DY section will be

operating at 2/3 supply.

Note: The impedance of (D1,C1,C2 and DY) and (D2,C3,C4 and L1) makes a voltage divider. If the

control point is not connected then there is some natural voltage on C4. Most split diode monitors are built

to pull power from the dummy section through L2 to ground. A single power transistor shunts from the

control point to ground. It is true that power can be supplied from some other supply through L2 to rise the voltage on C4. For maximum range a bi-directional power amplifier can drive the control point.

control point to ground. It is true that power can be supplied from some other supply through L2 to rise the voltage on C4. For maximum range a bi-directional power amplifier can drive the control point.The most exciting feature if the split diode modulator is that the flyback pulse, as seen by the flyback

transformer, is the same size at all horizontal size settings.

HORIZONTAL SWITCH/DAMPER DIODE

On the right hand side of the screen, the H. switch transistor conducts current through the deflection yoke.

This current comes from the S correction capacitors, which have a charge equal to the effective supply

voltage. The damper diode allows current for the left hand side of the screen to flow back through the

deflection yoke to the S capacitors.

FLYBACK CAPACITOR

The flyback capacitor connects the hot side of the yoke to ground. This component determines the size and

length of the flyback pulse. ‘Tuning the flyback capacitor’ is done to match the timing of the flyback pulse

to the video blanking time of the video signal. The peak flyback voltage on the horizontal switch must be

set to less that 80% if the Vces specification. The two conditions of time and voltage can be set by three

variables (supply voltage, retrace capacitor and yoke inductance) .

S CAPACITOR

The S capacitors corrects outside versus center linearity in the horizontal scan. The voltage on the S cap

has a parabola plus the DC horizontal supply. Reducing the value of S cap increases this parabola thus

reducing the size of the outside characters and increasing the size of the center characters.

S Capacitor value: Too low: picture will be squashed towards edges.

Too high: picture will be stretched towards edges.

By simply putting a capacitor in series with each coil, the sawtooth waveform is

modified into a slightly sine-wave shape. This reduces the scanning speed near the

edges where the yoke is more sensitive. Generally the deflection angle of the electron

beam and the yoke current are closely related. The problem is the deflection angle

verses the distance of movement on the CRT screen does not have a linear effect.

DEFLECTION NPN TRANSISTOR BASE DRIVE CURRENT

The base drive resistor determines the amount of

base drive. If the transistor is over driven the Vsat

looks very good, but the current fall time is poor.

If the base current is too small the current fall time is very fast. The problem is that the transistor will have many volts across C-E when closed.

The best condition is found by placing the transistor in the heaviest load condition. Adjust the base resistor for the least power consumption then increase the base drive a small amount. This will slightly over drive the base.

The Telefunken PPHV Flyback Horizontal Output Transformer Technology:

The current Telefunken 415/

615 CTV chassis series like the here above

shown tv is conventional in most respects, with its self oscillating

chopper power supply which also provides mains isolation, TDA 3560 OR

TDA3562A single -chip decoder, class AB RGB output stages, TDA1670 field

timebase i.c. and BU208 line output transistor. The line output

transformer is something quite new however.

615 CTV chassis series like the here above

shown tv is conventional in most respects, with its self oscillating

chopper power supply which also provides mains isolation, TDA 3560 OR

TDA3562A single -chip decoder, class AB RGB output stages, TDA1670 field

timebase i.c. and BU208 line output transistor. The line output

transformer is something quite new however.Line output transformers are nowadays reliable components though a percentage of failures do occur. Tripler breakdown after some years' service is far more common, except in Japanese sets. The transformer is certainly one of the most expensive items in a TV receiver: the pulse windings and secondaries used to provide various supply lines add greatly to the manufacturing cost and increase the insulation problems. Telefunken decided to do something about this in designing the 415/615 chassis. The aims were to reduce the cost of the transformer, make it as small as possible, mountable without securing screws, and producible by automatic production methods whilst having a power handling capability, reliability and internal resistance equal to or better than conventional designs. To achieve these aims it was decided to use a half -wave e.h.t. rectifier arrangement. This in itself is not unique of course, but for CTV use the problem of a half -wave rectifier circuit is the high leakage inductance and internal capacitance in the transformer. The result is an e.h.t. system with a high internal resistance. It was decided therefore to use a transformer with just two windings, the primary and e.h.t. overwinding. The other supplies are derived from the chopper transformer, while a transistor to which the line flyback pulses are fed produces the feedback pulse for the flywheel sync system.

The latter is in the TDA1950 sync/line oscillator chip, which also produces the sandcastle pulse used by the TDA3560 or TDA3562A decoder i.c. for gating, blanking and clamping. This decision greatly simplifies the transformer of course, while collaboration with a specialist manufacturer or ferrite cores enabled the cross-sectional area of the core to be reduced by some 25 per cent. The result is a transformer which is extremely compact and light. The main design advance however is the use of what Telefunken call the "push-pull high-voltage concept". This uses two rectifier diodes, one at each end of the winding as shown in Fig. 1. The action of the circuit is shown in Fig. 2. D1 acts as a conventional peak rectifier when the positive going flyback pulse arrives at its anode, charging transformer George R. Wilding the e.h.t. reservoir capacitor C2 (tube capacitance). During this time D2 conducts, clamping the bottom end of the e.h.t. overwiding to chassis. At the end of the flyback pulse half cycle the bottom end of the winding swings positively and D2 cuts off. It conducts again when the voltage at its cathode (circuit oscillatory action) tries to swing negatively, thus charging the interwinding capacitance Cl. The next time the flyback pulse occurs, D1 sees an enhanced voltage at its anode, i.e. the sum of the flyback pulse and the charge on Cl. The circuit thus acts as a voltage multiplier, and the number of overwinding turns can be substantially reduced in comparison with a simple half -wave rectifier circuit. Even though it's on such a small former the primary winding has only two layers. These terminate in connec- tion pins which together with two snap-on springs hold the transformer securely to the board for soldering. The diodes and the e.h.t. connection are secured to the body of the overwinding and encapsulated in heat hardened epoxy resin. The focus supply is obtained via a bleed resistor in the tube's anode cap connector. Fig. 3 shows the feedback pulse generator stage.

The latter is in the TDA1950 sync/line oscillator chip, which also produces the sandcastle pulse used by the TDA3560 or TDA3562A decoder i.c. for gating, blanking and clamping. This decision greatly simplifies the transformer of course, while collaboration with a specialist manufacturer or ferrite cores enabled the cross-sectional area of the core to be reduced by some 25 per cent. The result is a transformer which is extremely compact and light. The main design advance however is the use of what Telefunken call the "push-pull high-voltage concept". This uses two rectifier diodes, one at each end of the winding as shown in Fig. 1. The action of the circuit is shown in Fig. 2. D1 acts as a conventional peak rectifier when the positive going flyback pulse arrives at its anode, charging transformer George R. Wilding the e.h.t. reservoir capacitor C2 (tube capacitance). During this time D2 conducts, clamping the bottom end of the e.h.t. overwiding to chassis. At the end of the flyback pulse half cycle the bottom end of the winding swings positively and D2 cuts off. It conducts again when the voltage at its cathode (circuit oscillatory action) tries to swing negatively, thus charging the interwinding capacitance Cl. The next time the flyback pulse occurs, D1 sees an enhanced voltage at its anode, i.e. the sum of the flyback pulse and the charge on Cl. The circuit thus acts as a voltage multiplier, and the number of overwinding turns can be substantially reduced in comparison with a simple half -wave rectifier circuit. Even though it's on such a small former the primary winding has only two layers. These terminate in connec- tion pins which together with two snap-on springs hold the transformer securely to the board for soldering. The diodes and the e.h.t. connection are secured to the body of the overwinding and encapsulated in heat hardened epoxy resin. The focus supply is obtained via a bleed resistor in the tube's anode cap connector. Fig. 3 shows the feedback pulse generator stage.Line end stage including transformer for a television receiver:

Der PPHV-Transformator", by Walter Goseberg, Funkshau 1/1981, pp. 70-71.

"Kaum zu fassen: 23.000 Volt zum Anfassen!-PPHV-Zeilentrafo der Zukunft. Aus Hannover."-Telefunken Heute, Aktuelle Information fur den Fachhandel.

A line end stage for a television receiver which comprises a transformer, a first high voltage rectifier and a second high voltage rectifier. The transformer has a primary winding coupled to the line sweep coils of the receiver, and a secondary winding. The secondary winding has one end coupled through the first high voltage rectifier to ground and through the second high voltage rectifier to the anode of the television receiver picture tube. The transformer comprises a core having a longitudinal axis. The primary winding is mounted on the core coaxial with the longitudinal axis and an insulating winding form surrounds the primary winding. The winding form is provided with spaced longitudinally-distributed radially-extending chambers and the secondary winding is located within these chambers. The thicknesses of the winding form between the bottoms of the chambers and the primary winding are greatest at the ends of the winding form and become progressively smaller toward the center of the form.

A line end stage for a television receiver which comprises a transformer, a first high voltage rectifier and a second high voltage rectifier. The transformer has a primary winding coupled to the line sweep coils of the receiver, and a secondary winding. The secondary winding has one end coupled through the first high voltage rectifier to ground and through the second high voltage rectifier to the anode of the television receiver picture tube. The transformer comprises a core having a longitudinal axis. The primary winding is mounted on the core coaxial with the longitudinal axis and an insulating winding form surrounds the primary winding. The winding form is provided with spaced longitudinally-distributed radially-extending chambers and the secondary winding is located within these chambers. The thicknesses of the winding form between the bottoms of the chambers and the primary winding are greatest at the ends of the winding form and become progressively smaller toward the center of the form.1. In a televison receiver having line sweep coils and a picture tube, a line end stage comprising

a transformer coupled to said line sweep coils including

a core having a longitudinal axis;

a single continuous untapped primary winding mounted on said core, said primary winding being coaxial with said longitudinal axis;

an insulating winding form surrounding said single primary winding, said winding form being coaxial with said longitudinal axis and being provided with spaced longitudinally-distributed radially-extending chambers; and

a single continuous untapped secondary winding located within the chambers of said winding form, the distances between the bottoms of the chambers within said winding form and said primary winding decreasing from the ends of said winding form toward the center thereof along said longitudinal axis;

a first high voltage rectifier having its anode connected to ground and its cathode connected to one end of said secondary winding; and

a second high voltage rectifier having its anode connected to the other end of said secondary winding and its cathode connected to the anode of said picture tube.

2. A line end stage as defined in claim 1 wherein the thickness of the insulation of said insulating winding form between said primary and secondary windings is a minimum along a line perpendicular to said longitudinal axis at the center of said core and increases toward the end of said core.

3. A line end stage as defined in claim 1 wherein the thickness of said winding form between the bottom of the chamber at the center of said winding form and said primary winding has a predetermined value, and the thicknesses of each of said chambers toward the ends of said winding form and said primary winding increases with respect to that at the center as a function of the distance from said center chamber.

4. A line end stage as defined in claim 1 wherein at least one of said chambers has parallel sides and the bottom thereof is perpendicular to said sides.

5. A line end stage as defined in claim 1 wherein the chambers at the ends of said winding form are empty, and said secondary winding is located within the chambers therebetween.

6. A line end stage as defined in claim 1 wherein the thicknesses of the secondary windings within said chambers are different, said thicknesses being selected to tune said secondary winding to a predetermined harmonic of the frequency of the return sweep oscillation of said television receiver.

7. A line end stage as defined in claim 1 wherein said primary winding extends in the direction of said longitudinal axis beyond said secondary winding.

8. A line end stage as defined in claim 1 wherein at least one of said chambers has parallel sides and the bottom thereof has a rounded fluted shape.

9. A line end stage as defined in claim 8 wherein the edge of said bottom adjacent one side of said chamber has a different radius of curvature than the edge adjacent the other side of said chamber.

10. A line end stage as defined in claim 9 wherein the chambers containing said secondary winding at the ends of the said winding form have said rounded fluted shape and wherein the edges of the bottoms of said chambers facing the ends of said winding form have a larger radius of curvature than the opposite edges of said chambers.

This invention relates to a line end stage for a television receiver and, in particular, to a transformer comprising a component of this stage. A line end stage for a television receiver includes, among other components, a transistor which functions as a switch, a high voltage rectifier, and a transformer having a primary winding and a high voltage secondary winding. The line end stage produces the high voltage required to energize the picture tube.

A conventional line end stage of this type is a relatively expensive and heavy part of the receiver, whih must withstand high voltages and currents on the order of 25,000 volts and two to three amperes. It performs several functions such as controlling the line sweep coils, and generating the high voltage for the picture tube, pulses for gating purposes and the direct operating voltages. Consequently, the stage must satisfy a number of different requirements.

More specifically, the line end stage should be as small as possible, light in weight and easy to manufacture. A low internal impedance is desirable and, despite the relatively high power involved, the stage should operate over long periods without malfunctioning.

More specifically, the line end stage should be as small as possible, light in weight and easy to manufacture. A low internal impedance is desirable and, despite the relatively high power involved, the stage should operate over long periods without malfunctioning. It is known that a low internal impedance can be attained by tuning the stray inductance of the high voltage winding and the effective capacitance to certain oddnumbered harmonics of the frequency of the retrace or return sweep oscillation of the line transformer. In this way, the pulse shape of the retrace pulse is broadened so as to reduce the internal impedance of the high voltage source, it being of particular advantage to tune to the ninth harmonic of the return sweep oscillation frequency. However, tuning to such a high frequency presents a number of technical problems because of the design of the line end stage, and because the effective inductances and capacitances must not exceed certain values. Maintaining these values and simultaneously meeting the other requirements is often difficult in practice.

It is an object of the present invention to provide a line end stage having a particularly simple design and which provides a fixed coupling between the primary and high voltage windings, the stray inductance of the high voltage winding being particularly low. This stage permits tuning to the desired harmonic of the frequency of the return sweep oscillation.

In accordance with the present invention, a line end stage for a television receiver is provided which comprises a transformer, a first high voltage rectifier and a second high voltage rectifier. The transformer has a primary winding coupled to the line sweep coils of the receiver, and a secondary winding. The secondary winding has a first end coupled through the first high voltage rectifier to ground and a second end coupled through the second high voltage rectifier to the anode of the television receiver picture tube.

In accordance with the present invention, a line end stage for a television receiver is provided which comprises a transformer, a first high voltage rectifier and a second high voltage rectifier. The transformer has a primary winding coupled to the line sweep coils of the receiver, and a secondary winding. The secondary winding has a first end coupled through the first high voltage rectifier to ground and a second end coupled through the second high voltage rectifier to the anode of the television receiver picture tube. The transformer comprises a core having a longitudinal axis. The primary winding is mounted on the core coaxial with the longitudinal axis, and an insulating winding form surrounds the primary winding. The winding form is provided with spaced, longitudinally-distributed, radially--extending chambers, the secondary winding being located within these chambers. The thickness of the winding form between the bottoms of the chambers and the primary winding is greatest at the ends of the winding form and become progressively smaller toward the center of the form.

The present invention offers a plurality of advantages with respect to the design, insulation and voltage distribution of the line transformer. In order to obtain a desired high voltage for the picture tube, a pulse voltage of a particular amplitude must be present across the high voltage winding, and with a given primary this determines the number of turns in the winding. In the present invention, the amplitude of the pulse voltage across the high voltage winding is the same as in prior art circuits in which the high voltage winding is directly grounded at one end. However, several advantages are obtained which are not realized with conventional circuits.

Since the first end of the high voltage winding is grounded through the first high voltage rectifier, it is maintained at a voltage having a direct component and an alternating component. An alternating voltage component is also present at the second end of the high voltage winding, this component having the same amplitude and being of opposite polarity from the alternating voltage component present at the first end of the winding. Accordingly, the alternating voltage component is zero at the center of the high voltage winding thereby producing an alternating voltage symmetry in the high voltage winding relative to the primary winding.

In prior art circuits having one end of the high voltage winding directly grounded, the alternating voltage has the required amplitude only at the ungrounded end of the winding. In contrast, in the present invention, the alternating voltages present at both ends of the coil are in phase opposition and at half the amplitude with respect to ground as compared to the alternating voltage at the ungrounded end of the conventional high voltage winding. The amplitude of the maximum alternating voltage is thus divided approximately in half compared to the maximum alternating voltage in the prior art circuit. This symmetry and reduction of voltage compared to the prior art circuit has several advantages.

The maximum amplitude of the alternating voltage is less than in the prior art circuit and therefore the thickness of the insulation between the high voltage winding and the primary winding can be reduced. This results in tighter coupling between the two windings, reduction in the stray inductance and simplifies tuning to the ninth harmonic.

The reduced amplitude of the alternating voltage across the high voltage winding is also beneficial because the capacitive currents flowing between the high voltage and primary windings are reduced in amplitude. In the prior art circuit, these capacitive currents are practically zero at the grounded end of the high voltage winding but increase toward the ungrounded end to a value corresponding to the amplitude of the alternating voltage at that end. In contrast, in the circuit according to the present invention, the amplitude of the capacitive current is zero at the center of the high voltage winding because the amplitude of the alternating voltage at this point is zero. The capacitive currents increase towards the ends of the high voltage winding to approximately equal and opposite values; however, these values are about half the maximum value of the capacitive current in the prior art circuit. Also, the integrated sum of the capacitive reactive currents flowing across the distributed winding capacitances is lower in the circuit according to the present invention than in the prior art circuit.

The fact that the amplitude of the alternating voltage at the center of the high voltage winding is zero can be utilized to advantage in the design of the winding form for the high voltage winding by making the insulating space at the center smaller than at the ends of the high voltage winding. According to one embodiment of the invention, the insulating space between the two windings is determined by the amplitude distribution of the effective alternating voltage across the high voltage winding.

The fact that the amplitude of the alternating voltage at the center of the high voltage winding is zero can be utilized to advantage in the design of the winding form for the high voltage winding by making the insulating space at the center smaller than at the ends of the high voltage winding. According to one embodiment of the invention, the insulating space between the two windings is determined by the amplitude distribution of the effective alternating voltage across the high voltage winding. In the present invention, the high voltage winding has about the same alternating voltage load at both ends, and the alternating voltages appearing at these two ends have the same shape and amplitude but are of opposite polarity. Accordingly, the interfering radiation emanating from the line transformer is reduced because the voltages at the ends of the high voltage winding partially cancel each other.

The primary and secondary sides of the transformer each contain only a single winding and are not provided with taps, thereby greatly simplifying the design of the transformer. In particular, this simple design permits fixed coupling and attainment of a low stray inductance for the high voltage winding which enhances tuning to a high harmonic of the frequency of the return sweep oscillation.

FIG. 1 is a schematic circuit diagram of the invention.

FIG. 2 shows voltage curves for explaining the operation of the circuit of FIG. 1.

FIG. 3 is an embodiment of the coil assembly of the transformer.

FIGS. 4 and 5 illustrate additional embodiments of the chambers of the winding form depicted in FIG. 3.

FIG. 1 is a schematic diagram of the line end stage of a television receiver which includes a switching transistor 2 having its base connected to an input terminal for switching by a square-wave input signal 1, a transformer 3 having a primary winding 4 and a high voltage secondary winding 5, two high voltage rectifiers 6 and 7, a smoothing capacitor 8, a picture tube 9, a coupling capacitor 10 which also serves as a tangential equalizer and line sweep coils 11. The anode of diode 6 is grounded and its cathode is connected to one end 12 of the secondary winding 5. The anode of diode 7 is connected to the other end 14 of secondary winding 5, its cathode being grounded for alternating voltages by capacitor 8 which is formed essentially by the capacitance of the anode coating of the picture tube 9. With these connections, the two ends 12 and 14 of the secondary winding 5 carry substantially the same load.

Referring to FIG. 2, the diode 6 prevents the return sweep voltage 13a at point 12 from becoming negative by clamping the negative peak of that voltage at ground potential. A direct voltage U 1 is generated at point 12 and also at point 14. Since the winding 5 is inductive, the return sweep voltage 13b at point 14 is of opposite polarity with respect to the voltage 13a at point 12. Thus, the alternating voltage at the center 15 of the winding is equal to zero and the distribution of the alternating voltage about the line 32 is symmetrical with respect to ground.

Referring to FIG. 2, the diode 6 prevents the return sweep voltage 13a at point 12 from becoming negative by clamping the negative peak of that voltage at ground potential. A direct voltage U 1 is generated at point 12 and also at point 14. Since the winding 5 is inductive, the return sweep voltage 13b at point 14 is of opposite polarity with respect to the voltage 13a at point 12. Thus, the alternating voltage at the center 15 of the winding is equal to zero and the distribution of the alternating voltage about the line 32 is symmetrical with respect to ground. The voltage present at point 14 is rectified by rectifier 7 so that the voltage U 2 at terminal 16 functions as the anode voltage for the picture tube 9. If the terminal 12 were grounded, approximately the same direct voltage U 2 would be produced at terminal 16 but the advantages of the present invention would not be obtained.

The amplitude of the alternating voltage component across winding 5 differs greatly from one end to the other. That is, the alternating voltage between winding 5 and ground is zero at the center of the winding and reaches maximum values of opposite polarities at the ends 12 and 14. This permits the insulation space between the high voltage winding 5 and primary winding 4 of transformer 3 to be a function of its position along the winding.

Referring to FIG. 3, the structure of transformer 3 is shown in which the primary winding 4 surrounds a core 17 having a longitudinal axis 30. An insulating winding form 18 having a plurality of chambers 20 surrounds winding 4. The high voltage winding 5 comprises partial windings 19 disposed in those chambers 20 designated by the letters B through L, chambers A and M not having windings placed therein.

All of the partial windings 19 lying within the chambers 20 are wound one after another without any interruption of the wire. The wire is fed through slots within the walls forming the chambers 20. That means that all of the partial windings 19 are series-connected without any interruption, and form together the winding 5 of FIG. 1.

The thickness d of the winding form 18 at the bottom of each of the respective chambers 20 is a minimum at the center of the form along radial axis 32 where the amplitude of the alternating voltage is substantially equal to zero, the thickness increasing symmetrically along a parabolic curve toward the two ends of the winding form 18. In an actual embodiment tested, the wall thickness d of chambers A-M had the following values:

| ______________________________________ |

| Chamber d in mm |

| ______________________________________ |

A 2.0 (empty) B 1.6 C 1.3 D 1.2 E 1.1 F 1.0 G 1.0 H 1.0 I 1.1 J 1.2 K 1.3 L 1.6 M 2.0 (empty) |

| ______________________________________ |

Chambers A and M are intentionally not provided with a winding 19. This has the advantage that the space between the first winding in chamber B and the sharp edge of end 21 of primary winding 4 is relatively large, thereby reducing the danger of arcing at the edge of the winding. Similarly, the distance between the winding in chamber L and the edge of end 22 of the primary winding 4 is relatively large to reduce the possibility that arcing will occur at this end of the transformer.

As shown in FIG. 3, the number of turns of the windings 19 in the individual chambers 20 are, in general, not the same. That is, the radial thicknesses of the windings in chambers F, G and H are equal but the thickness of the windings in the chambers on either side of chambers F and H decrease significantly and are at a minimum in chambers B and L, the stray inductance being controlled to permit tuning to a desired harmonic.

As shown in FIG. 3, the number of turns of the windings 19 in the individual chambers 20 are, in general, not the same. That is, the radial thicknesses of the windings in chambers F, G and H are equal but the thickness of the windings in the chambers on either side of chambers F and H decrease significantly and are at a minimum in chambers B and L, the stray inductance being controlled to permit tuning to a desired harmonic. If, for example, the winding is distributed so that there are more turns at the center of the winding form 18 where the distance between the high voltage winding 5 and the primary winding 4 is smaller than at the edges, the coupling is closer at the center thereby changing the stray inductance compared to that which would have been obtained with a uniform winding distribution.

It is desirable that the stray inductance of the winding 5 together with all effective capacitances be tuned to a frequency corresponding to the ninth harmonic of the frequency of the line fly back pulse in order to achieve a low value of internal resistance at terminal 16 of the high voltage source. The stray inductance of the winding 5 which is necessary for achieving this resonant frequency can be obtained by a proper distribution of the partial windings 19 within the chambers 20. In particular the stray inductance can be kept low because the distance between the partial windings 19 in the middle region of form 18, i.e. around chamber G can be made very small. This is possible as the value of the ac-voltage in this region corresponding to center 15 in FIG. 2 is zero.

FIG. 4 shows an embodiment of the winding form in which the edges along the bottom of the chamber 20 are rounded so as to have a fluted shape in order to reduce arcing, rounding the circumferential edges reducing the probability that arcing will take place. Moreover, the wire comprising the turns of the high voltage winding can more conveniently be placed in the chambers 20 during winding.

In FIG. 5, the radii or curvature at the two edges of the chambers 20 are different. This configuration is employed for the first and last chambers B and L having a winding 19 placed therein, the edge 23 having the larger radius of curvature being located at the end of the winding form. Thus, a chamber shaped as shown in FIG. 5 would be used for chamber L to reduce the chance of arcing between edge 22 and the coil placed in chamber L. The embodiment of FIG. 5 is preferably provided only for chambers B and L.

In FIG. 5, the radii or curvature at the two edges of the chambers 20 are different. This configuration is employed for the first and last chambers B and L having a winding 19 placed therein, the edge 23 having the larger radius of curvature being located at the end of the winding form. Thus, a chamber shaped as shown in FIG. 5 would be used for chamber L to reduce the chance of arcing between edge 22 and the coil placed in chamber L. The embodiment of FIG. 5 is preferably provided only for chambers B and L. It will be understood that the above description of the present invention is susceptible to various modifications, changes and adaptations, and the same are intended to be comprehended within the meaning and range of equivalents of the appended claims.

TELEFUNKEN PALCOLOR 6462J CHASSIS 615A1 PLL MICROCOMPUTER Frequency synthesizer tuning system for television receivers:TFK u3870M

" A method for tuning a television receiver having automatic frequency control to the carrier frequency of a selected broadcast channel with an associated channel number including generating a variable frequency signal by means of a local oscillator, generating a reference frequency signal by means of a reference oscillator, and generating a local oscillator correction signal for matching an intermediate frequency signal derived from said local oscillator signal and the carrier frequency signal with a predetermined nominal intermediate frequency signal, said method being characterized by the use of a microcomputer and comprising:

generating binary signals representing first and second digital tune words, said digital tune words representing a selected channel;

storing said first and second digital tune words in a first data memory in said microcomputer;

reading said first and second digital tune words from said first memory and generating a divided-down local oscillator frequency by the use of said first digital tune word and a divided-down reference oscillator frequency by the use of said second digital tune word;

comparing said divided-down local oscillator and reference frequencies and generating a control signal representative of the difference in frequency of said divided-down local oscillator and reference frequencies;

coupling said control signal to said local oscillator for causing it to be locked to the frequency of said received carrier signal;

mixing the local oscillator frequency signal and the carrier frequency signal to generate an intermediate frequency signal;

comparing said intermediate frequency signal with said predetermined nominal intermediate frequency signal and providing a tuning voltage to said microcomputer, said tuning voltage being indicative of the magnitude and direction of a tuning error between said intermediate frequency signal and said predetermined nominal intermediate frequency signal;

incrementally adjusting the reference oscillator frequency by means of a tuning signal provided to said reference oscillator by said microcomputer in response to said tuning voltage;

detecting when the incrementally changing, divided-down reference oscillator frequency causes the intermediate frequency signal to pass said predetermined nominal intermediate frequency signal; and

incrementally stepping the divided-down reference oscillator frequency back a predetermined number of steps following the passage of said predetermined nominal intermediate frequency signal by said intermediate frequency signal in tuning said television receiver to the selected channel.

"

A

television tuning system employs a frequency synthesizer system for

establishing the tuning of the receiver. A programmable frequency

divider counter is connected between the output of a reference

oscillator and a phase comparator to which the output of the local

oscillator in the tuner also is applied. The phase comparator output

provides a tuning voltage for controlling the tuning of the local

oscillator. A microprocessor is used to control the count of the

programmable frequency divider and initially to set a count

corresponding to the selected channel in a counter connected between the

output of the local oscillator and the phase comparator. The tuning

consists of three discrete time periods. First, a settling time to

allow channel change transients to settle; second, a short period of

forced search at a relatively rapid rate to insure proper tuning; and

third, a slower rate of step-by-step correction to accomodate for

station drift and the like during reception. This third time period is

initiated either by the passage of a fixed length of time following

the start of the forced search period or by sensing a preestablished

number of changes of state in the output of the frequency

discriminator during the forced/search period.

A

television tuning system employs a frequency synthesizer system for

establishing the tuning of the receiver. A programmable frequency

divider counter is connected between the output of a reference

oscillator and a phase comparator to which the output of the local

oscillator in the tuner also is applied. The phase comparator output

provides a tuning voltage for controlling the tuning of the local

oscillator. A microprocessor is used to control the count of the

programmable frequency divider and initially to set a count

corresponding to the selected channel in a counter connected between the

output of the local oscillator and the phase comparator. The tuning

consists of three discrete time periods. First, a settling time to

allow channel change transients to settle; second, a short period of

forced search at a relatively rapid rate to insure proper tuning; and

third, a slower rate of step-by-step correction to accomodate for

station drift and the like during reception. This third time period is

initiated either by the passage of a fixed length of time following

the start of the forced search period or by sensing a preestablished

number of changes of state in the output of the frequency

discriminator during the forced/search period.1. A tuning system for the tuner of a television receiver capable of receiving a composite television signal and including frequency discriminator (AFT) circuit means, said system including in combination:

a reference oscillator providing a reference signal at a predetermined frequency;

a local oscillator in the tuner providing a variable output frequency in response to the application of a control signal thereto;

a programmable frequency divider means having first and second inputs coupled respectively to the output of said reference oscillator and said local oscillator for producing signals on first and second outputs having frequencies which are a programmable fraction of the frequency of the signals applied to the inputs thereto;

phase comparator means having one input coupled with the first output of said programmable frequency divider means and having another input coupled with the second output of said programmable frequency divider means for developing a control signal and applying such control signal to said local oscillator for controlling the output frequency thereof;

counter circuit means coupled with said programmable frequency divider means for initially setting said divider means to a predetermined division ratio and operating to change the programmable fraction of division thereof in accordance with changes in the count in said counter circuit means;

control circuit means coupled with the output of said frequency discriminator means and further coupled with said counter circuit means for causing said counter circuit means to count at a first rate in a predetermined direction determined by the state of the output signal from said discriminator means in the absence of a predetermined signal output from said frequency discriminator means until a predetermined maximum count is attained, thereupon resetting said counter circuit means to a count which is a predetermined amount less than said maximum predetermined count and continuing to count at said first rate in the same predetermined direction from said new count to continuously change the programmable fraction of said frequency divider means in accordance with the state of operation of said counter circuit means, said control means operating in response to said predetermined signal output from the frequency discriminator means for terminating operation of said counter circuit means; and

further means for terminating operation of said counter circuit means at said first rate and causing operation thereof at a second slower rate.

2. The combination according to claim 1 wherein said further means includes timing means initiated into operation simultaneously with the setting of said divider means to a predetermined division ratio, and after a predetermined time interval said timing means producing an output signal applied to said counter circuit means to cause operation thereof to take place at said second slower rate. 3. The combination according to claim 1 wherein said counter circuit means includes a reversible digital counter coupled with said programmable frequency divider, means and said control circuit means causes said counter circuit means to count in said predetermined direction when the output of said frequency discriminator is of a first state and to count in the opposite direction when the output of said frequency discriminator is of second state; and said further means comprises means coupled with the output of said frequency discriminator and with said counter circuit means to take place at said second slower rate in response to a predetermined number of changes of state of frequency discriminator. 4. The combination according to claim 3 further including means responsive to the selection of a new channel in said television receiver for resetting said further means to an initial condition of operation. 5. The combination according to claim 4 wherein said further means comprises a search termination counter means operative to provide an output signal applied to said counter circuit means in response to a count thereby of a predetermined number of changes of state of said frequency discriminator to cause said counter circuit means to be operated at said second slower rate.

Both

of the above mentioned patents are directed to frequency synthesizer

tuning systems for use with television receivers to enable operation

of the receivers with minimal viewer fine tuning adjustments. By the

utilization of the frequency synthesizer tuning systems of these

patents, the fine tuning adjustment which is necessary with conventional

types of television receiver tuning systems has been substantially

eliminated. The system employed in the '953 patent permits utilization

of a frequency synthesizer tuning system which correctly tunes to a

desired television station or channel even if the transmitted signals

from that station are not precisely maintained at the proper

frequencies. The '535 patent is directed to a signal seek tuning system

adaptation of the frequency synthesizer tuning system of the '953

patent which still permits implementation of all of the desired

wide-band pull in range of the frequency synthesizer system of the '953

patent.

Both

of the above mentioned patents are directed to frequency synthesizer

tuning systems for use with television receivers to enable operation

of the receivers with minimal viewer fine tuning adjustments. By the

utilization of the frequency synthesizer tuning systems of these

patents, the fine tuning adjustment which is necessary with conventional

types of television receiver tuning systems has been substantially

eliminated. The system employed in the '953 patent permits utilization

of a frequency synthesizer tuning system which correctly tunes to a

desired television station or channel even if the transmitted signals

from that station are not precisely maintained at the proper

frequencies. The '535 patent is directed to a signal seek tuning system

adaptation of the frequency synthesizer tuning system of the '953

patent which still permits implementation of all of the desired

wide-band pull in range of the frequency synthesizer system of the '953

patent.The systems of the foregoing patents operate effectively to correct automatically for frequency offsets in a frequency synthesizer tuning system without affecting the operation of the conventional frequency synthesizer used in the system. The systems of these patents are in widespread use commercially and permit direct selection, with automatic fine tuning adjustment, of any desired VHF channel which the viewer wishes to observe. In addition, the signal seek adaptation disclosed in the '535 patent couples all of the advantages of the frequency synthesizer tuning system of the '953 patent with the desirability of providing bidirectional signal seek operation.

While the systems disclosed in the foregoing patents operate in a highly satisfactory manner to accomplish the desired results of accurate tuning without the necessity of fine tuning adjustments, the circuitry for accomplishing the desired results is somewhat complex. It is desirable to reduce the circuit complexity and the number of signal detectors for accomplishing these results without compromising the accuracy of operation of the system.

SUMMARY OF THE INVENTION

Accordingly, it is an object of this invention to provide an improved tuning system for a television receiver.

It is an additional object of this invention to provide an improved frequency synthesizer tuning system for a television receiver.

It is another object of this invention to provide an improved frequency synthesizer tuning system for a television receiver which includes a provision for adjusting the synthesizer loop for frequency offsets in the received signal with a minimum number of signal detectors.

It is a further object of this invention to tune the local RF oscillator of a television receiver to the correct frequency for a selected channel with a frequency synthesizer tuning system, and automatically to change the reference frequency of the synthesizer system, or adjust the count of a programmable divider that produces a signal that divides the frequency of the local oscillator of the tuner, if the AFT signal produced by the AFT frequency discriminator of the receiver is outside a predetermined range corresponding to correct tuning.

It is still another object of this invention to provide an improved frequency synthesizer tuning system for a television receiver which operates to adjust the synthesizer loop for frequency offsets in the received signal over a relatively wide pull in range in response to the output of the receiver frequency discriminator by changing the division ratio of a programmable frequency divider in the reference oscillator leg or local oscillator leg of the synthesizer loop at a first relatively high rate from an initial nominal value to a pre-established maximum in one direction, and then resetting the division ratio to a second nominal value once the maximum is reached and continuing to incrementally change the division ratio in the same direction from the second nominal value until a properly tuned condition is indicated by the output of the receiver AFT frequency discriminator, followed by control at a lower rate of operation to maintain tuning during transmitting station drifts.

In

accordance with a preferred embodiment of this invention, the

frequency synthesizer tuning system for a television receiver includes

a stable reference oscillator and a voltage controlled local

oscillator in the tuner. A programmable frequency divider is connected

between the output of the reference oscillator and one input to a

phase comparator, the other input of which is supplied by the output

of the local oscillator. The output of the phase comparator then

comprises a control signal which is supplied to the local oscillator

to control the frequency of its operation.

In

accordance with a preferred embodiment of this invention, the

frequency synthesizer tuning system for a television receiver includes

a stable reference oscillator and a voltage controlled local

oscillator in the tuner. A programmable frequency divider is connected

between the output of the reference oscillator and one input to a

phase comparator, the other input of which is supplied by the output

of the local oscillator. The output of the phase comparator then

comprises a control signal which is supplied to the local oscillator

to control the frequency of its operation.A counter circuit is connected to the programmable frequency divider for initially setting the divider to a predetermined division ratio upon selection of a desired channel by the viewer. The counter then operates to change the programmable fraction of the division ratio at a first relatively high rate in a direction controlled by the output from the receiver picture carrier discriminator in the absence of a predetermined signal output derived from the discriminator. A control means causes the counter circuit to count in this direction until it is determined that a station is tuned or a predetermined maximum count is attained if no station is correctly tuned, thereupon resetting the counter circuit to a count which is a predetermined amount less than the maximum predetermined count. Counting is continued in the same predetermined direction from the new lesser count to continuously change the programmable fraction of the frequency divider in accordance with the state of operation of the counter.

The high rate operation of the counter is terminated by the control means in response to a predetermined signal from the output of the discriminator, indicating that a station is correctly tuned, or after a fixed time-out interval; so that the system automatically adjusts for frequency offsets of the received signal which otherwise would cause the station to be mistuned if a conventional frequency synthesizer tuning system were used. After termination of the high rate operation of the counter, it is switched to a lower rate operation for maintaining tuning during transmitting station drifts.

BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a block diagram of a television receiver employing a preferred embodiment of the invention;

FIG. 2 is a detailed block diagram of a portion of the circuit of the preferred embodiment shown in FIG. 1;

FIG. 3 is a detailed circuit diagram of a portion of a circuit shown in FIG. 1;

FIG. 4 is a flow chart of the control sequence of operation of the circuit shown in FIG. 1 and 2; and

FIG. 5 shows a waveform and time/frequency chart, respectively, useful in explaining the operation of the circuit shown in FIGS. 1, 2 and 3.

DETAILED DESCRIPTION

Referring now to the drawings, the same reference numbers are used throughout the several figures to designate the same or similar components.

FIG. 1 is a block diagram of a television receiver, which may be a black and white or color television receiver. Mo

st

of the circuitry of this receiver is conventional, and for that

reason it has not been shown in FIG. 1. Added to the conventional

television receiver circuitry of FIG. 1, however, is a frequency

synthesizer tuning system, in accordance with a preferred embodiment

of the invention, which is capable of automatically changing the

reference frequency when a frequency offset exists in the received

signal for a particular channel.

st

of the circuitry of this receiver is conventional, and for that

reason it has not been shown in FIG. 1. Added to the conventional

television receiver circuitry of FIG. 1, however, is a frequency

synthesizer tuning system, in accordance with a preferred embodiment

of the invention, which is capable of automatically changing the

reference frequency when a frequency offset exists in the received

signal for a particular channel.Transmitted composite television signals, either received over the air or distributed by means of a master antenna TV distribution system, are received by an antenna 10 or on antenna input terminals to the receiver. As is well known, these composite signals include picture and sound carrier components and synchronizing signal components, with the composite signal applied to an RF and tuner stage 11 of the receiver. The stage 11 includes the conventional RF amplifiers and tuner sections of the receiver, including a VHF oscillator section and a UHF oscillator section. Preferably, the UHF and VHF oscillators are voltage controlled oscillators, the freuency of operation of which are varied in response to a tuning voltage applied to them to effect the desired tuning of the receiver.

The output of the RF and tuner stages 11 is applied to the remainder of the television receiver 14, which includes the IF amplifier stages for supplying conventional picture (video) and sound IF signals to the video and sound processing stages of the receiver 14. The circuitry of the receiver 14 may be of any conventional type used to separate, amplify and otherwise process the signals for application to a cathode ray tube 16 and to a loudspeaker 17 which reproduce the picture and sound components, respectively, of the received signal.

The

receiver 14 also includes a conventional AFT or automatic fine

tuning discriminator circuit and additionally may include a synch

separator circuit for producing an output in response to the presence

of vertical synchronizatin pulses, a picture carrier detection

circuit, and an automatic gain control (AGC) amplifier. Outputs

representative of these sensor components are shown as being coupled

over a group of lead 20 to sensory circuitry 22, which in turn

couples outputs representative of the operation of these various

sensor circuits to a microprocessor unit 23 for controlling the

operation of the microprocessor unit.

The

receiver 14 also includes a conventional AFT or automatic fine

tuning discriminator circuit and additionally may include a synch

separator circuit for producing an output in response to the presence

of vertical synchronizatin pulses, a picture carrier detection

circuit, and an automatic gain control (AGC) amplifier. Outputs

representative of these sensor components are shown as being coupled

over a group of lead 20 to sensory circuitry 22, which in turn

couples outputs representative of the operation of these various

sensor circuits to a microprocessor unit 23 for controlling the

operation of the microprocessor unit.The microprocessor unit 23 is utilized in the system of FIG. 1 for controlling the operation of a frequency synthesizer tuning system capable of automatic offset correction. When the viewer desires to select a new channel, he enters the desired channel number into a channel selection keyboard 25. There are a number of different keyboards which may be employed to accomplish this function, and the particular design is not important to this invention. The channel selector keyboard 25 also may include switches or keys for initiating a signal seek function in either the "up" or "down" direction.

Information represented by the selection of channel numbers on the keyboard 25 is supplied to the microprocessor unit 23 which provides output signals over a corresponding set of leads 27 to the tuners (local oscillators) 11 to effect the appropriate band switching control for the tuners 11 in accordance with the particular channel which has been selected. In addition, the keyboard 25, operating through the microprocessor unit 23, provides output signals which operate a channel number display 29 to provide an appropriate display of the selected channel number to the viewer.

The microprocessor M3870 unit 23 also processes the signals which are used to operate the channel number display 29 through a multiplexing circuit operation to decode the selected channel number into a parallel encoded signal. This signal is applied to corresponding inputs of the count-down counter or programmable frequency divider 31 to cause the division number of the divider 31 to relate to the divided down frequency of the tuner local oscillators connected to the input of the divider 31 through a prescaler divider circuit 32 to the frequency of the reference oscillator 34. Thus, the division number or division ratio of the local oscillator frequency obtained from the output of the programmable divider 31 is appropriately related to the frequency of the reference crystal oscillator 34.

The output of the oscillator 34 also is applied through a countdown circuit or programmable frequency divider 35. Conventional frequency synthesizer techniques are employed; and the microprocessor unit 23 automatically compensates, through appropriate code converter circuitry, for the non-uniform channel spacing of the television signals. It has been found most convenient to cause the programmable frequency divider 31 to divide by numbers corresponding directly to the oscillator frequency of the selected channel, for example, 101, 107, 113 . . . up to 931.

In accordance with the time division multiplex operation of the microprocessor 23, the count of the programmable frequency divider 35 initially is adjusted to a fixed count by the application of appropriate output signals from the microprocessor unit 23 to a point selected to be at or near the mid-point of the operating range of the programmable frequency divider 35. Thus, the output of the divider 35 is a stable reference frequency (because the input is from the reference crystal oscillator 34) which is used to establish initially and to maintain tuning of the receiver to the selected channel.

The output of the programmable divider 35 is applied to one of two inputs of a phase comparator circuit 37. The other input to the phase comparator circuit 37 is supplied from the selected one of the VHF or UHF oscillators in the tuner stages 11 through the programmable frequency divider 31. The phase comparator circuit 37 operates in a conventional manner to supply a DC tuning control signal through a phase locked loop filter circuit 39 and over a lead 40 to the oscillators in the tuner system 11 to change and maintain their operating frequency.

With the exception of the use of the microprocessor unit 23, the operation of the system which has been described thus far is that of a relatively conventional frequency synthesizer system incorporated into a television receiver. This system is similar to the system of the '953 patent. As in the system of that patent, the system shown in FIG. 1, when the transmitted station or station received on a master antenna distribution system provides the station or channel signals at the proper frequency, operates as a relatively conventional frequency synthesizer system. If, however, there is a frequency offset in the received signal to cause the carrier of the received signal to be displaced from the frequency which it should have to some other frequency, it is possible that the system would give the appearance of mistuning to the received station. The microprocessor 23, operating in conjunction with the sensory circuitry 22, is employed in conjunction with the countdown or programmable frequency divider circuit 35 to eliminate this disadvantage and still retain the advantages of frequency synthesizer tuning.

Reference now should be made to FIG. 2 which shows details of t

he

interface between the keyboard 25, the microprocessor unit 23, and

the circuitry used in the frequency synthesizer portions of the

system. A commercially available microprocessor which has been used

for the microprocessor 23, and which forms the basis for the