The PHILIPS CHASSIS K9 is an awesome and amazing example of PHILIPS ENGINEERING.

The PHILIPS CHASSIS K9 is an awesome and amazing example of PHILIPS ENGINEERING.It's the first PHILIPS CHASSIS completely based on semiconductors and further advanced with ASIC'S around all signal processing boards.

It's developed in 2 main sections borad panels:

- DEFLECTIONS LEFT SIDE (POWER SIGNALS PANEL)

- SIGNAL RIGHT SIDE (SMALL SIGNALS PANEL)

- MIDDLE BOTTOM POWER SUPPLY UNIT.

The chassis K9 is higly sophisticated and complex but it has an unique fashinating structure and design which expands his technology in a way of simplicity which is today, long time, lost and forgotten (forever).

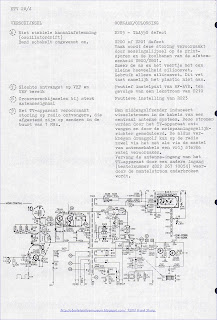

Control circuit for a switched-mode power supply, particularly for a television receiver: PHILIPS CHASSIS K9 SWITCH MODE POWER SUPPLY.

A switched-mode power supply provided with a control stage and a switching stage coupled by means of a transformer. The collector of an additional transistor is connected to the transformer. In this manner the ratio of the collector current to the base current of the switching transistor can assume a predetermined value, for example a constant value whatever the value of the mains voltage applied to the power supply.

1. A control circuit for a switched-mode power supply, said power supply comprising a non-regulated rectified DC voltage source, a driver transistor, a first transformer having primary and secondary windings, an end of said primary being coupled to the collector-emitter path of said driver transistor, a switching transistor having a base coupled to said secondary, a second transformer having a primary winding coupled in series with said switching transistor, and a plurality of secondary windings, said control circuit comprising a first additional transistor having a collector coupled to the remaining end of the primary winding of the first transformer not connected to the driver-transistor and an emitter coupled to the non-regulated direct voltage source.

2. A control circuit as claimed in claim 1, further comprising a constant voltage source coupled to the base of the additional transistor.

2. A control circuit as claimed in claim 1, further comprising a constant voltage source coupled to the base of the additional transistor.3. A control circuit as claimed in claim 1, further comprising a constant current source, and a resistor coupled between the emitter of the additional transistor and the constant current source.

4. A control circuit as claimed in claim 3, wherein the constant current source comprises a second additional transistor, the two additional transistors being of complementary conductivity and their emitters being connected with each other through said resistor, the collector of the second additional transistor being coupled to the non-regulated rectified direct voltage source and the collector of the first additional transistor being coupled to the end of the primary winding of the first transformer not connected to the driver transistor.

5. A control circuit as claimed in claim 4, further comprising a resistor coupled in series with the collector circuit of said second additional transistor and the non-regulated rectified direct voltage source.

6. A control circuit as claimed in claim 5, further comprising a zener diode coupled between the base of the second additional transistor and the non-regulated voltage source.

6. A control circuit as claimed in claim 5, further comprising a zener diode coupled between the base of the second additional transistor and the non-regulated voltage source.7. A control circuit as claimed in claim 6, further comprising a resistance bridge coupled to the base of the first additional transistor and arranged between the two electrodes of the zener diode.

8. A control circuit as claimed in claim 7, wherein the driver transistor and the switching transistor do not conduct simultaneously, and the voltage between the two electrodes of the zener diode as well as the values of the resistors arranged between the said electrodes and of the resistor arranged between the emitters of the two additional transistors are chosen so that the first additional transistor is in the saturated state at the lowest value of the non-regulated voltage while it operates in the linear state at a higher value of said non-regulated voltage.

This type of switched-mode power supply is used more and more because of the numerous advantages it presents as regards energy efficiency, reliability, compactness, etc. However, as for the majority of the other types of power supplies, its operation on mains supplies of different voltages imposes the use of either a transformer with taps or switch-over from full wave rectification at the highest mains voltage to a voltage doubler rectification for the lowest mains voltage.

It is known that the specific qualities of a switched-mode power supply depend for a large part on the switching speed of the switching transistor at the moment at which the latter passes periodically from the conductive state to the blocking state; this speed is at its maximum when the switching transistor presents, at the turn-off moment, a certain ratio between the collector current and the base current IC/IB: if this ratio is too low, the delay in the recombination of the charges stored in the base increases the switching time; if it is too high there is the risk that the transistor is brought out of saturation before it is blocked, which results in its substantially immediate destruction. For the known switched-mode power supplies it is not possible to maintain a suitable IC/IB ratio in the presence of large variations of the non-regulated rectified DC voltage which result from the connection to the nominal mains voltages of, for example, 110 or 220 V; actually, if the variations in IB are substantially proportional to the variations in the non-regulated voltage, the same does not happen for those of the IC whose amplitude is less.

It is known that the specific qualities of a switched-mode power supply depend for a large part on the switching speed of the switching transistor at the moment at which the latter passes periodically from the conductive state to the blocking state; this speed is at its maximum when the switching transistor presents, at the turn-off moment, a certain ratio between the collector current and the base current IC/IB: if this ratio is too low, the delay in the recombination of the charges stored in the base increases the switching time; if it is too high there is the risk that the transistor is brought out of saturation before it is blocked, which results in its substantially immediate destruction. For the known switched-mode power supplies it is not possible to maintain a suitable IC/IB ratio in the presence of large variations of the non-regulated rectified DC voltage which result from the connection to the nominal mains voltages of, for example, 110 or 220 V; actually, if the variations in IB are substantially proportional to the variations in the non-regulated voltage, the same does not happen for those of the IC whose amplitude is less.However, the importance of having a power supply which can operate without any switching on mains supplies of 110 or 220 V is evident: for the manufacturer it is cheaper to produce and the reliability is increased; while the user does not run the risk of incorrect manipulations, particularly when the power supply is destined for use in portable television sets.

One of the objects of the invention is to realize a control circuit which permits the switched-mode power supply to operate without switching in conditions which are substantially optimum and in the presence of mains voltage variations in the range of 90 to 250 Volts.

A further object of the invention is to ensure that said IC/IB ratio of the switching transistor has a predetermined and, more particularly a constant value at the turn-off moment whatever the value of the mains voltage applied to the power supply.

The control circuit according to the invention is characterized in that the end of the primary winding of the first transformer not connected to the driver transistor is connected to the collector of an additional transistor whose emitter is coupled with the non-regulated direct voltage source. Advantageously it is characterized in that the emitter of the additional transistor is connected to one end of a resistor, the other end of this resistor being connected to a constant current source, and that the constant current source is constituted by a second additional transistor, the two additional transistors being of complementary conductivity and their emitters being connected with each other through a resistor, whilst the collector of the second additional transistor is connected to one of the poles of the non-regulated rectified direct voltage source and the collector of the first additional transistor is connected to the end of the primary winding of the first transformer not connected to the driver transistor.

Whilst combining the action of a ballast transistor with that of a variable current generator, the circuit according to the invention thus maintains automatically a desired IC/IB ratio of the switching transistor whatever the value of the mains voltage applied to the power supply.

PHILIPS X26K206 TIZIANO CHASSIS K9 CIRCUIT ARRANGEMENT FOR GENERATING IN A PICTURE DISPLAY DEVICE A SAWTOOTH CURRENT OF LINE FREQUENCY HAVING AN AMPLITUDE VARYING AT FIELD FREQUENCY IN PHILIPS CHASSIS K9.

A circuit arrangement for generating by means of a modulator in a colour picture display device a sawtooth correction current of line frequency flowing through the line deflection coils and having an amplitude varying at field frequency for the purpose of obtaining a better colour superposition in the corners of the screen of the display tube, comprising means to add an additional correction current which flows in the same direction as the first mentioned current and which is proportional to the third power of both the line and the field deflection currents. Said means may be a saturable coil or a resonant circuit which is tuned to a frequency which lies between the like frequency and twice the value thereof. In the latter case the voltage present across the circuit may be used for correcting the North-South pincushion distortion. Also, the modulator is controlled by an amplifier comprising a linear and a voltage-dependent resistor which ensure that a

third-power component is added also to said field deflection current.

third-power component is added also to said field deflection current.1. A distortion correction circuit for line and field deflection coils of a display tube, said circuit comprising line and field deflection generator means coupled to said coils respestively for producing line and field deflection signals respectively; a modulator means for providing a line frequency first correction current having a field frequency varying amplitude to at least one of said coils; and means for supplying an additional correction current distinct from said deflection signals that is a thrid power function of at least one of said deflection signals and for applying it to said one deflection coil in the same direction as said first correction current.

2. A circuit as claimed in claim 1 wherein said supplying means comprises a non-linear inductor series coupled to said modulator and having an inductance that decreases with increasing current.

3. A circuit as claimed in claim 1 wherein said supplying means comprises a tuned circuit including an inductor and a capacitor parallel coupled thereto, said circuit being tuned to a frequency between the line frequency and twice the line frequency and being series coupled to said modulator.

4. A circuit as claimed in claim 3 wherein said inductor comprises a transformer primary, said transformer including a secondary; and further comprising means coupled to said secondary for correcting North-South pincushion distortion in said display tube.

5. A circuit as claimed in claim 1 wherein said modulator comprises diode switch means operating at the line frequency for coupling during the line scan time the field generator to a resonant circuit having a period twice the line flyback period, said resonant circuit including a capacitor and said line deflection coil; and further comprising a coil coupled in series between said line generator and said line coil.

6. A circuit as claimed in claim 5 further comprising a resistor series coupled to said capacitor.

7. A circuit as claimed in claim 5 further comprising a series circuit including in order a first capacitor, a pair of diodes that are non-conducting during the line flyback time, and a second capacitor, said series circuit being parallel coupled to said coil; and an inductance capacitance parallel resonant circuit coupled to the junction of the diodes, said circuit being resonant at a frequency between the line frequency and twice the line frequency.

8. A circuit as claimed in claim 1 further comprising amplifier means for applying said field signal to said modulator, said amplifier including a complementary pair of transistors adapted to receive a negative feedback network having an input coupled to the output electrodes of said transistors for receiving a zero average signal, said network comprising fixed and voltage dependent resistors coupled thereto.

9. A circuit as claimed in claim 1 further comprising a circuit coupled between said modulator and said field generator, said circuit comprising a fixed and a voltage dependent resistor parallel coupled thereto.

10. A circuit as claimed in claim 1 further comprising North-South pincushion correction means for adding a sinusoidal current of line frequency to said correction current.

11. A circuit as claimed 1 wherein said additional correction current is a third power function of both of said deflection signals.

U.S. Pat. No. 3,440,483 described a display device for colour television wherein for the purpose of correction on the screen of a display tube in the device use is made of a sawtooth correction current of line frequency having an amplitude varying at field frequency. From the beginning up to the end of the scan of a field period this correction current of line frequency is to decrease down to zero from a given value in a substantially linear manner, whereafter a substantially equal increase in the reverse current direction follows. This correction current is superimposed on the deflection current flowing in the line and/or field deflection coil, the peak-to-peak a

mplitude of the deflection current being substantially constant. Since the deflection coil is divided into two coil halves provided substantially symmetrically on either side of the neck of the display tube, it is possible to add the correction current in one coil half to the deflection current and to subtract it from the deflection current in the other coil half. The magnetic deflection field of one coil half will therefore be enlarged and that of the other coil half will be reduced to a substantially equal extent.

mplitude of the deflection current being substantially constant. Since the deflection coil is divided into two coil halves provided substantially symmetrically on either side of the neck of the display tube, it is possible to add the correction current in one coil half to the deflection current and to subtract it from the deflection current in the other coil half. The magnetic deflection field of one coil half will therefore be enlarged and that of the other coil half will be reduced to a substantially equal extent.As has been described in the said U.S. patent the so-called anisotropic astigmatism of a deflection coil causes a distortion which gives an electron beam having a circular or ellipse cross-section a tilted ellipse shape, which distortion is dependent on the extent of the deflection. In other words, this distortion occurs most seriously in the corners of the displayed picture and it results in colour superposition errors. The said patent application shows that it is possible to eliminate this distortion with the aid of an oppositely directed distortion caused by the above-mentioned correction current.

The said amplitude variation of field frequency of the sawtooth current of line frequency is established by means of a modulator controlled by the field deflection current generator. The said patent application describes inter alia an arrangement wherein this modulator is formed as a multiplier to which information regarding the line and field deflection currents is supplied. If the centre horizontal line on the screen of the display tube is referred to as x'Ox and the central vertical line is referred to as y'Oy, wherein O is the centre of the screen while, as is common practice in mathematics, x'Ox extends from left to right y'Oy extends from bottom to top, it can be assumed that the compensating deviation Δ x which is established by means of the modulator is in the first instance proportional to x and to y. In this case x and y are the coordinates of one point on the screen relative to the previously defined system of coordinates. In this manner the compensating deviation Δ x is indeed increased in the corners of the screen and is zero on the axes x'Ox and y'Oy.

However, the invention is based on the recognition of the fact that the previously described correction is not sufficient to completely eliminate the colour superposition errors in the corners of the screen of the display tube. In order to be able to eliminate this the circuit arrangement according to the invention is characterized in that it includes means to add an additional correction current to the sawtooth current in the vicinity of the beginning and the end of each scan period, which additional current flows in the same direction as the said correction current and which is proportional to the third power of the line deflection current and to the third power of the field deflection current.

The correction currents may be produced in different manners. To this end the circuit arrangement according to the invention is further characterized in that the means for producing the additional correction current during the line scan period are obtained by means of a coil which is series-arranged with the modulator and whose inductance decreases when the current flowing therethrough increases and that the means for producing the additional correction current during the line scan period are obtained by means of a parallel circuit which is series-arranged with the modulator and whose resonant frequency lies between the line frequency and twice the value thereof.

Furthermore the invention is based on the recognition of the fact that the voltage which is present under these circumstances across the said parallel circuit may alternatively be used for other purposes. To this end, the circuit arrangement according to the invention is characterized in that the coil in the parallel circuit constitutes the primary winding of a transformer and that the voltage produced across the secondary winding of the transformer controls a circuit for the correction of the North-South pincushion distortion on the screen of a picture display tube present in the picture display device.

A field deflection circuit in which the deflection coil is connected to a direct voltage source during the flyback period so as to reverse the polarity of the deflection current. For this purpose the deflection coil is connected through a switch controllable connected to the direct voltage source, which switch is controlled by the difference between a voltage proportional to the steep-edged sawtooth input signal and a voltage proportional to the deflection current. This difference is considerable during the flyback period and is utilized for switching on the controllable switch; it becomes zero as soon as the deflection current has reached its required value at which the switch is switched off again. It is thus achieved that the polarity reversal is always terminated when the required value is reached, even when the direct voltage fluctuates and also when the inductive load is changed.

A field deflection circuit in which the deflection coil is connected to a direct voltage source during the flyback period so as to reverse the polarity of the deflection current. For this purpose the deflection coil is connected through a switch controllable connected to the direct voltage source, which switch is controlled by the difference between a voltage proportional to the steep-edged sawtooth input signal and a voltage proportional to the deflection current. This difference is considerable during the flyback period and is utilized for switching on the controllable switch; it becomes zero as soon as the deflection current has reached its required value at which the switch is switched off again. It is thus achieved that the polarity reversal is always terminated when the required value is reached, even when the direct voltage fluctuates and also when the inductive load is changed. 1. A circuit for generating an output deflection current for a deflection coil from an input sawtooth deflection voltage signal having a polarity changes at the start of the flyback period which are short with respect to said flyback period; said circuit comprising an amplifier having an input adapted to receive said input signal, and an output means adapted to be coupled to said coil for providing said output current; means coupled to said amplifier for generating a control voltage that is the difference between a voltage that is proportional to said input signal and a voltage that is proportional to said output current; a direct voltage source; and means for rendering said output current independent of voltage and load variations comprising means for reversing the polarity of said deflection current at the start of said flyback period including a switch means coupled to said amplifier and said source and having a control input coupled to said means for generating for coupling said coil to said source at the start of said flyback period and separating said coil from said source upon said deflection current reaching a selected value required for the start of the scan period.

2. A circuit as claimed in claim 1, wherein said amplifier comprises a junction having a potential that differs from a threshold value during said flyback period, said switch being coupled to said junction and switching at about said threshold value; and further comprising feedback means for applying said voltage proportional to said deflection current to said amplifier input.

3. A circuit as claimed in claim 2 wherein said junction potential goes below said threshold value during said flyback period, said switch switching above said threshold value.

4. A circuit as claimed in claim 2 wherein said junction potential exceeds said threshold value during said flyback period, said switch switching below said threshold value.

5. A circuit as claimed in claim 2 wherein said amplifier comprises first and second final stage class B push pull transistors, each of said transistors having emitter and collector conduction electrodes, a conduction electrode of one of said transistors being coupled to a like conduction electrode of said other transistor, said first transistor being conductive during said start of said scan period; a pass direction coupled diode having a first end coupled to first transistor conduction electrode, and a second end adapted to receive a first terminal of a power supply; a capacitor having a first end coupled to said diode first end, and a second end coupled to said switch; and a resistor having a first end coupled to said capacitor second end, and a second end adapted to receive a second terminal of said power supply.

6. A circuit as claimed in claim 5 wherein said like conduction electrodes comprise said collector electrodes and said diode first end is coupled to said first transistor emitter.

7. A circuit as claimed in claim 5 wherein said like conduction electrodes comprise said emitter electrodes and said diode first end is coupled to said first transistor collector.

8. A circuit as claimed in claim 5 further comprising a second cut off direction coupled diode having a first end coupled to a conduction electrode of said first transistor, and a second end coupled to the remaining conduction electrode of said first transistor.

As compared with a vertical deflection circuit in which the deflection coil with an additionally arranged capacitor is constituted as a part of a resonance circuit, which circuit performs an unattenuated half oscillation during the flyback period whereby considerable voltage amplitudes at the output of the amplifier circuit occur, the advantage of such a deflection circuit is that the direct voltage to which the deflection coil must be connected is not so high, so that transistors having a slight collector breakdown voltage can be used. In a circuit arrangement of the kind described in the preamble and in U.S. Pat. No. 3,070,727 the flyback voltage depends on the height of the direct voltage, the inductance of the deflection coil and the maximum deflection current in accordance with the relation T = LI/U, in which T denotes the duration of the polarity reversal, I denotes the height of the deflection current (measured from peak to peak), L denotes the inductance of the deflection coil and U denotes the height of the direct voltage.

In a known circuit arrangement of this kind the input of the controllable (transistor) switch is connected to the output of the

amplifier through the series arrangement of a capacitor and a resistor. At the commencement of the flyback period the sawtooth voltage changes from its positive to its negative maximum value while a negative pulse becomes available through the RC member at the input of the transistor switch, which pulse causes this transistor to conduct and which connects the deflection coil to a negative direct voltage so that the current flowing through the coil is reversed in polarity. The duration of this polarity reversal depends on the time constant of the RC member before the input of the transistor switch. In case of fluctuations of the direct voltage to which the deflection coil is connected during the flyback period, the amplitude of the current reached by the deflection current during this polarity reversal of course also changes so that the scan period commences either at a too low or at a too high value of the vertical deflection current. Since in addition, as stated, the period of time during which the deflection coil must be connected to the direct voltage depends on the inductance of the deflection coil, the time constant of the RC member must be adapted to the inductance of the deflection coils.

amplifier through the series arrangement of a capacitor and a resistor. At the commencement of the flyback period the sawtooth voltage changes from its positive to its negative maximum value while a negative pulse becomes available through the RC member at the input of the transistor switch, which pulse causes this transistor to conduct and which connects the deflection coil to a negative direct voltage so that the current flowing through the coil is reversed in polarity. The duration of this polarity reversal depends on the time constant of the RC member before the input of the transistor switch. In case of fluctuations of the direct voltage to which the deflection coil is connected during the flyback period, the amplitude of the current reached by the deflection current during this polarity reversal of course also changes so that the scan period commences either at a too low or at a too high value of the vertical deflection current. Since in addition, as stated, the period of time during which the deflection coil must be connected to the direct voltage depends on the inductance of the deflection coil, the time constant of the RC member must be adapted to the inductance of the deflection coils.An object of the present invention is to obviate these drawbacks and to provide a circuit arrangement in which the deflection coil is connected to the direct voltage as long as is necessary for reaching the amplitude of the deflection current required for the commencement of the scan period and in which an adaptation is not necessary when the inductance of the deflection circuit changes, for example, by including a transformer for the North-South raster correction.

Starting from a vertical deflection circuit of the kind described in the preamble this object is achieved according to the invention in that the controllable switch is controlled by the difference between a voltage which is proportional to the sawtooth signal and a voltage which is proportional to the deflection current, said two voltages and/or the switch being dimensioned in such a manner that the deflection coil is separated from the direct voltage by means of the switch as soon as the current flowing through the deflection coil has reached the value required for the commencement of the scan period.

The invention is based on the regulation of the fact that the sawtooth signal at the input of the amplifier and the current flowing through the vertical deflec

tion coil have substantially the same variation throughout the scan period; during the flyback period the sawtooth signal is, however, reversed in polarity within a few microseconds, while the polarity reversal for the deflection current is considerably slower due to the limited direct voltage present at the deflection coil. These differences in the variation with time between the input signal and the deflection current may be utilized for the purpose of rendering the switch operative, which switch becomes inoperative again as soon as the deflection current has reached its value required for the commencement of the scan period, because then no difference exists any longer between the sawtooth input signal and the deflection current.

tion coil have substantially the same variation throughout the scan period; during the flyback period the sawtooth signal is, however, reversed in polarity within a few microseconds, while the polarity reversal for the deflection current is considerably slower due to the limited direct voltage present at the deflection coil. These differences in the variation with time between the input signal and the deflection current may be utilized for the purpose of rendering the switch operative, which switch becomes inoperative again as soon as the deflection current has reached its value required for the commencement of the scan period, because then no difference exists any longer between the sawtooth input signal and the deflection current.According to a further embodiment of the invention the voltage proportional to the deflection current is applied as a feedback voltage to the input of the amplifier and the controllable switch is connected to a point of the amplifier whose potential exceeds a threshold value only during the flyback period, which threshold value renders the controllable switch operative.

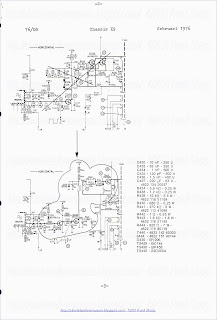

In order that the invention may be readily carried into effect, an embodiment thereof will now be described in detail by way of example with reference to the accompanying diagrammatic drawing. In this embodiment a class B push-pull amplifier is used which, as is known, has a lower dissipation then a class A amplifier for a determined deflection output. The amplifier is substantially symmetrical so that two corresponding parts are denoted by two corresponding reference numerals (for example, 12, 12').

In order that the invention may be readily carried into effect, an embodiment thereof will now be described in detail by way of example with reference to the accompanying diagrammatic drawing. In this embodiment a class B push-pull amplifier is used which, as is known, has a lower dissipation then a class A amplifier for a determined deflection output. The amplifier is substantially symmetrical so that two corresponding parts are denoted by two corresponding reference numerals (for example, 12, 12').The input signal 1 is applied through a capacitor 2 of 10 μF to the interconnected bases of the input transistors 3 and 3'. The collector of npn-transistor 3 is connected through a resistor 4 of 1.5 kOhms to the positive supply voltage terminal, while its emitter is connected through a resistor 5 of 6.8 kOhms to the negative supply voltage. Transistor 3' is of the pnp type and accordingly it has a polarity which is opposite to that of transistor 3; however, the resistors 4' in the collector lead and 5' in the emitter lead have the same values as resistors 4 and 5. The collector of the transistor 3(3') is connected to the base of a pnp- (npn-) transistor 6 (6') whose emitter is connected through a resistor 7 (7') of 470 Ohms to the positive (negative) supply voltage. The collectors of transistors 6 and 6' are connected together through a diode arranged in the pass direction. The collector voltages of transistors 6 and 6' are applied to the bases of transistors 8 and 8' which are of a conductivity type opposite to that of the transistors driving them. The collectors of transistors 8 and 8' are connected through resistors 9 and 9' to the bases of final transistors 10 and 10' which are again of a conductivity type which is opposite to that of the transistors driving them. The collectors of transistors 10 and 10' are connected together and the junction is connected to ground through the deflection coil 11 and a low-value resistor 12 of 2.2 Ohms. The final transistors are protected by diodes 15 and 15' from the voltage peaks occurring at the deflection coil when the current is reversed in polarity and when flashovers occur in the picture display tube, said diodes being connected in the blocking direction in parallel with the collector-emitter path of the final transistors. In case of a short circuit at the end of the final stage the driver current is limited by the resistors 9, 9'.

In case of a class B push-pull stage the output potential is normally highly dependent on the adjusted quiescent current which in turn is determined by the ambient temperature. In the present circuit arrangement this would give rise to the fact that the vertical position of the picture highly depends on the temperature. To avoid this, the bases of the final transistors 10 and 10' are connected through the series arrangement of diodes 13 and 13' arranged in the pass direction and resistors 14 and 14' to supply voltage terminal for their emitters. A resistor 16 of 47 kOhms arranged between the cathode of the diode 13 connected to the positive potential and the anode of the diode 13' connected to the negative potential ensures that the diodes 13 and 13' are always slightly biassed. As a result the base potential and the quiescent current of the final transistors 10 and 10' is determined by the bias voltage of these diodes when the input signal fails, hence when transistors 8 and 8' are cut off. Since this bias voltage is already very low and is even more reduced by the voltage drops at resistors 14 and 14', quiescent currents of a few μA can be adjusted. The distortions of the output signal to be expected at such a low quiescent current adjustment are eliminated in known manner (Austrian Pat. specification 245038) in that the bases of the final transistors are not connected to the emitters of the driver stages 8 and 8' but to their collectors so that the output resistance of the driver stages 8, 8' driving the final transistors 10, 10' is considerably larger than the input resistance of the final stages. The non-linearity of the input resistance therefore does not exert any influence on the course of the signal.

A voltage is derived from resistor 12 which is applied through resistors 17 and 17' to the emitters of input transistors 3 and 3'. The voltage 18 proportional to the deflection current derived from resistor 12 has the same phase and substantially also the same shape as the input signal 1 and therefore acts as a direct current feedback. The mean value of the deflection current and hence the position of the picture is determined in this circuit arrangement by the potential at the bases of transistors 3 and 3'. To adjust this potential a potentiometer connected to the supply voltage would be sufficient, while its wiper would be connected to the bases of the input transistors, but in this case the position of the picture would be greatly dependent on fluctuations in the supply voltage. Adjustment of the picture position substantially independent of supply voltage fluctuations is obtained when, as shown in the drawing, the base is connected to the wiper on a potentiometer 18' of 5 kOhms whose ends are connected to ground through resistors 19 and 19' of 22 kOhms and further resistors 20 and 20' of 330 Ohms, the junction of resistors 19, 20 and 19', 20' being connected through resistors 21 and 21', respectively, to the positive and negative potential, respectively. The amplifier and particularly the driver stages 8, 8' and the final stages 10, 10' are substantially insensitive to hum voltages so that the positive voltage of 24 volts and the negative voltage of -20 Volts need not be especially smooth. For the preliminary stages this smoothing may be effected in known manner by resistors 22 and 22' of 680 Ohms arranged in the supply lead which resistors together with capacitors 23 and 23' of 500 μF constitute a smoothing member.

It is achieved

by the direct current feedback that the deflection current is adjusted such that the voltage fed back on the emitters of the input transistors 3 and 3' corresponds but for a small difference to the voltage at the bases of transistor 3 and 3' (for this reason the deflection current can be varied by varying the value of resistor 12 in case of a given amplitude of the input signal). As a result the deflection current has the same variation with time as the input signal 1 at least during the scan period. At the beginning of the flyback period the input voltage changes within a few microseconds from its positive to its negative maximum value; the deflection current can, however, not be reversed in polarity at the same rate. As a result the base-emitter voltage of the input transistors 3 varies substantially stepwise after the beginning of the flyback period when the input signal has already reached its negative peak value while the deflection current has only very slightly varied. The bases of the input transistors 3, 3' become thus considerably more negative so that the lower transistor 3' and at the same time the transistors 6', 8', 10' conduct heavily while transistors, 3, 6, 8 and 10 are cut off. This voltage variation produces a negative voltage step, for example, at the interconnected emitters of driver transistor 8, 8' which emitters are connected to ground through a resistor 24 of 100 Ohms, said voltage step being applied to the input of a controllable switch 27 through a potential divider consisting of resistors 25 of 1 kOhm and 26 of 22 kOhms and having one end connected to the said emitters and the other end connected to the positive supply voltage, so that said switch then onducts. In the conducting state the switch 27 must conduct current in both directions; when using a transistors switch the collector-emitter path of the switching transistor may be connected for this purpose in parallel with a diode having an opposite pass direction and having such a polarity that it does not conduct during the scan period.

by the direct current feedback that the deflection current is adjusted such that the voltage fed back on the emitters of the input transistors 3 and 3' corresponds but for a small difference to the voltage at the bases of transistor 3 and 3' (for this reason the deflection current can be varied by varying the value of resistor 12 in case of a given amplitude of the input signal). As a result the deflection current has the same variation with time as the input signal 1 at least during the scan period. At the beginning of the flyback period the input voltage changes within a few microseconds from its positive to its negative maximum value; the deflection current can, however, not be reversed in polarity at the same rate. As a result the base-emitter voltage of the input transistors 3 varies substantially stepwise after the beginning of the flyback period when the input signal has already reached its negative peak value while the deflection current has only very slightly varied. The bases of the input transistors 3, 3' become thus considerably more negative so that the lower transistor 3' and at the same time the transistors 6', 8', 10' conduct heavily while transistors, 3, 6, 8 and 10 are cut off. This voltage variation produces a negative voltage step, for example, at the interconnected emitters of driver transistor 8, 8' which emitters are connected to ground through a resistor 24 of 100 Ohms, said voltage step being applied to the input of a controllable switch 27 through a potential divider consisting of resistors 25 of 1 kOhm and 26 of 22 kOhms and having one end connected to the said emitters and the other end connected to the positive supply voltage, so that said switch then onducts. In the conducting state the switch 27 must conduct current in both directions; when using a transistors switch the collector-emitter path of the switching transistor may be connected for this purpose in parallel with a diode having an opposite pass direction and having such a polarity that it does not conduct during the scan period.The current flowing through the deflection coil might alternatively be reversed in polarity when the deflection coil would be directly connected via the switch to the negative supply voltage. In case of a negative supply voltage of - 20 Volts, a deflection inductance of 30 mH and a deflection current of 1,2 A (peak-to-peak) a time of 1.8 ms would, however, be required for reversing the polarity of the deflection current; a flyback period of less than one ms is, however, desirable. This shorter flyback period could be obtained by increasing the negative and the positive supply voltage. Then, however, the dissipation of the final stage transistors 10, 10' would also be increased.

In the circuit arrangement shown in the drawing the duration

of the flyback period is reduced by means of a clamping circuit without increase of dissipation of the final stage transistors. For this purpose the emitter of transistor 10', unlike the emitter of transistor 10 is not directly connected to the associated voltage supply terminal but through a diode 28 conducting in the pass direction. In addition the emitter of transistor 10' is connected through a large capacitor 29 of 250 μF to the end of the transistor switch not connected to the negative supply voltage, which end is simultaneously connected through a resistor 30 of 220 Ohms to the positive supply voltage terminal. The clamping circuit operates as follows:

of the flyback period is reduced by means of a clamping circuit without increase of dissipation of the final stage transistors. For this purpose the emitter of transistor 10', unlike the emitter of transistor 10 is not directly connected to the associated voltage supply terminal but through a diode 28 conducting in the pass direction. In addition the emitter of transistor 10' is connected through a large capacitor 29 of 250 μF to the end of the transistor switch not connected to the negative supply voltage, which end is simultaneously connected through a resistor 30 of 220 Ohms to the positive supply voltage terminal. The clamping circuit operates as follows:During the scan period capacitor 29 is charged through resistor 30 and the diode 28, a voltage of + 24 Volts occurring at the end of capacitor 29 connected to the switch and a voltage of approximately - 20 Volts occurring at the other end, so that a voltage of approximately 44 Volts is present at the capacitor. As soon as the transistor switch 27 conducts as a result of the steep-edged voltage step of the input voltage 1 the electrode of capacitor 29 which was positive (+ 24 Volts) up till that instant is connected to the negative supply voltage; this potential step is transferred to the other electrode of the capacitor which was previously at - 20 Volts and subsequently at approximately - 60 Volts. Diode 28 is blocked at this voltage.

At the beginning of the flyback period a negative voltage peak is produced at the end of the deflection coil 11 connected to the amplifier output, and this as a result of the sudden cut-off of the final stage transistor 10 which was still conducting relatively strongly at the end of the scan period. The negative voltage peak is limited by diode 15' to a voltage which is slightly more negative than - 60 Volts, for example, -60.6 Volts. The deflection current flows via diode 15' in the same direction as it did previously through transistor 10, but due to the negative voltage at the end of the deflection coil connected to the amplifier output it decreases to the value of zero. Subsequently, the current is reversed in polarity and flows through the collector-emitter path of the npn transistor 10' whose base also carries a positive voltage during the first part of the flyback period. The voltage at the deflection coil is then only slightly less negative than the voltage on the left-hand electrode of capacitor 29 due to the small voltage drop on the collector-emitter path of transistor 10', so that the deflection current furthermore decreases at approximately the same rate as during the first half of the flyback period, because substantially the same voltage is present at the deflection coil. Simultaneously also the voltage at resistor 12 decreases and hence the difference between the base-emitter voltages of the input transistors 3 and 3'. Consequently the lower half of the class B push-pull amplifier becomes less conducting so that the emitter potential of transistors 8 and 8' becomes again less negative. In case of suitable dimensioning of the potential divider 25, 26 and of the threshold at which the transistor switch 27 is opened again it can be achieved that opening is effected just at the instant when the deflection current has reached its required value. The capacitor 29 is still further charged during the first part of the flyback period and the more the lower its capacitance is, and during the second part of the flyback period it is discharged to the voltage present at the commencement of the flyback period. The mean value of the potential on the left-hand electrode of this capacitor is thus still more negative than - 60 Volts during the flyback period and the more as the capacitance of the capacitor is lower so that the deflection current is reversed in polarity at an even faster rate. However, restrictions are imposed in this case due to the dielectric strength of the final stage transistors; consequently, when the dielectric strength of transistors 10, 10' is only slightly more than 60 Volts, a capacitor having a high capacitance (250 μF) is to be used, as in the embodiment.

This circuit arrangement is insensitive to fluctuations during operation. When, for example, the negative and/or the positive supply voltage increases, the flyback duration decreases; accordingly the emitter potential of the driver transistors 8 and 8' reaches the positive threshold value more quickly so that the switch is opened again and the polarity reversal is interrupted as soon as the deflection current has reached its required value.

PHILIPS X26K206 TIZIANO CHASSIS K9 NORD SOUTH (NORD/SUD) CORRECTION CIRCUIT ARRANGEMENT FOR CORRECTING THE DEFLECTION OF AT LEAST ONE ELECTRON BEAM IN A TELEVISION PICTURE TUBE BY MEANS OF A TRANSDUCTOR :

A circuit arrangement for raster correction in a television picture tube by means of a transductor whose power winding is connected in parallel with at least a portion of the line deflection coils, the line deflection genera

tor having a low internal impedance. In order to increase this impedance a mainly inductive impedance is connected in series with the generator. In a picture tube employing at least two electron beams the series impedance may include the convergence circuit. As a result the convergence in the corners of the picture screen is also improved. The linearity control circuit may likewise form part of the series impedance.

tor having a low internal impedance. In order to increase this impedance a mainly inductive impedance is connected in series with the generator. In a picture tube employing at least two electron beams the series impedance may include the convergence circuit. As a result the convergence in the corners of the picture screen is also improved. The linearity control circuit may likewise form part of the series impedance.1. A deflection circuit for a cathode ray tube comprising a transistor horizontal deflection generator; a horizontal deflection coil parallel coupled to said generator; means for pincushion correction of said tube comprising a saturable reactor having a control winding adapted to receive a vertical deflection signal and a power winding parallel coupled to at least a portion of said deflection coil; and means for increasing the effectiveness of said correction means comprising an impedance element external to said generator having a substantially inductive reactance series coupled between said generator and said coil. 2. A circuit as claimed in claim 1 wherein said generator comprises a transformer having a tap and said power winding has a first end coupled to said coil and a second end coupled to said tap. 3. A circuit as claimed in claim 1 wherein said impedance element comprises means for controlling the linearity of the beam deflection. 4. A deflection circuit for a cathode ray tube having at least two electron beams comprising a transistor horizontal deflection generator; a horizontal deflection coil parallel coupled to said generator; means for pincushion correction of said tube comprising a saturable reactor having a control winding adapted to receive a vertical deflection signal and a power winding parallel coupled to at least a portion of said deflection coil; means for increasing the effectiveness of said correction means comprising an Impedance element external to said generator having a substantially inductive reactance series coupled between said generator and said coil; and means for dynamically converging said beams comprising a convergence circuit coupled to said horizontal generator and to said transductor. 5. A circuit as claimed in claim 4 wherein said generator comprises a transformer having a tap and said power winding has a first end coupled to said coil and a second end coupled to said tap. 6. A circuit as claimed in claim 4 wherein said impedance element comprises means for controlling the linearity of the beam deflection.

A circuit arrangement for raster correction with the aid of a transductor is described, for example, in U.S. Pat. No. 3,444,422. In this patent the power winding of a transductor is connected in parallel with the horizontal deflection coils while the control winding receives a signal of field frequency so that the current of line frequency which flows through the deflection coils is modulated at the field

-frequency (East-West correction), whereas the vertical deflection current is modulated at the line frequency (North-South correction). However, in this known arrangement there is the difficulty that the transductor can exert little influence on the horizontal deflection current if the internal impedance of the deflection generator is low because the transductor then only constitutes an additional load on the generator. This is the case when the deflection generator includes a valve with feedback -- or a switch formed with one or more transistors. In order to be able to use a transductor arrangement also in such a case the circuit arrangement according to the invention is characterized in that a mainly inductive impedance is connected in series between the said parallel arrangement and the deflection generator.

-frequency (East-West correction), whereas the vertical deflection current is modulated at the line frequency (North-South correction). However, in this known arrangement there is the difficulty that the transductor can exert little influence on the horizontal deflection current if the internal impedance of the deflection generator is low because the transductor then only constitutes an additional load on the generator. This is the case when the deflection generator includes a valve with feedback -- or a switch formed with one or more transistors. In order to be able to use a transductor arrangement also in such a case the circuit arrangement according to the invention is characterized in that a mainly inductive impedance is connected in series between the said parallel arrangement and the deflection generator.Due to the step according to the invention the internal impedance of the deflection generator is increased and the different components of the circuit remain mainly inductive so that the deflection current is more or less linear when the voltage provided by the deflection generator during the line scan period is substantially constant. The series impedance may be, for example, a fixed coil. However, the invention is furthermore based on the recognition of the fact that the increase in the internal resistance of the horizontal deflection generator may not only be obtained by a constant impedance, but other arrangements envisaging other improvements of the deflection may be used for this purpose. In that case even special improvements may be obtained as will be apparent hereinafter and possible small non-linearities of the additionally used arrangements have no detrimental results.

It is true that in known convergence circuits in picture tubes employing a plurality of electron beams a satisfactory improvement is obtained for the central horizontal and vertical lines of a picture tube of the shadow mask type. However, it is found that convergence errors may subsist in the corners of the picture. Known circuit arrangements which correct these second-order errors are often complicated and expensive. In the circuit arrangement according to the invention a satisfactory compensation of such convergence errors is possible in a simple manner if the series impedance which is arranged between the horizontal deflection generator and the deflection coils includes the convergence circuit. In this manner the sum of the deflection current and of the current derived for the field correction and modulated by the transductor flows through the convergence circuit so that the desired additional convergence correction in the corners of the written raster is obtained.

In order that the invention may be readily carried into effect a few embodiments thereof will now be described in detail by way of example with reference to the accompanying diagrammatic drawings in which:

FIG. 1 shows a circuit arrangement in which the transductor is connected in parallel with the deflection coils, while in

FIG. 2 the transductor is only fed by part of the voltage applied to the deflection coils.

FIG. 1 shows two line-output transistors 1 and 2 which are arranged in series. The emitter of transistor 2 is connected to ground through a winding 3 while the collector of transistor 1 is connected through a winding 4 and a small series impedance 5, preferably a resistor, to the positive terminal of a supply source V b whose negative terminal is connected to ground.

Windings 3 and 4 are wound together with

an EHT-winding 6 on the same transformer core 7. The ends of windings 3 and 4 remote from each other are connected through the capacitor 10 for the S-correction to the deflection-unit consisting of two windings 8 and 9 arranged, for example, in parallel. The base of transistors 1 and 2 receive pulses of line frequency in a manner not shown in FIG. 1 so that these transistors are cut off during the flyback period. During the scan period, a substantially constant voltage is applied to the deflection unit. Consequently a more or less sawtooth-shaped current flows through windings 8 and 9. The bipartite power winding 11 of a transductor ensuring the raster correction is connected in parallel with this deflection unit 8, 9. The control winding 12 of said transductor, and a converting capacitor 13 in parallel therewith form part of the circuit for the vertical deflection through terminals 14 and 15. An adjustable coil 16 with which the raster correction can be adjusted exactly is connected in series with winding 12.

an EHT-winding 6 on the same transformer core 7. The ends of windings 3 and 4 remote from each other are connected through the capacitor 10 for the S-correction to the deflection-unit consisting of two windings 8 and 9 arranged, for example, in parallel. The base of transistors 1 and 2 receive pulses of line frequency in a manner not shown in FIG. 1 so that these transistors are cut off during the flyback period. During the scan period, a substantially constant voltage is applied to the deflection unit. Consequently a more or less sawtooth-shaped current flows through windings 8 and 9. The bipartite power winding 11 of a transductor ensuring the raster correction is connected in parallel with this deflection unit 8, 9. The control winding 12 of said transductor, and a converting capacitor 13 in parallel therewith form part of the circuit for the vertical deflection through terminals 14 and 15. An adjustable coil 16 with which the raster correction can be adjusted exactly is connected in series with winding 12.Windings 3 and 4 have the same number of turns so that pulses of the same amplitude and reversed polarity are produced at the emitter of transistor 2 and at the collector of transistor 1. As a result a disturbing radiation of these pulses is reduced. Furthermore, transistor types are chosen in this Example for transistors 1 and 2 whose collector-base diodes may function as efficiency diodes. All this has been described in U.S. Pat. No. 3,504,224.

According to the invention the convergence circuit 17 is arranged through a separation transformer 20 between the end of winding 3 remote from winding 4 and the horizontal deflection coils 8, 9. Furthermore, this current branch includes the linearity control circuit 21 which comprises the parallel arrangement of a resistor and a coil whose inductance is adjustable, for example, by means of premagnetization of the core of the coil. A current, which is the sum of the current for the deflection coils 8, 9 and of the current for the power winding 11 of the transductor, flows through the primary winding of transformer 20. This primary current is transformed to the secondary circuit of transformer 20 so that a current flows through convergence circuit 17.

In known arrangements the con

vergence current is only influenced by the deflection current itself. It has been found that in this case the convergence correction is not sufficient in the corners of the picture. At these areas, where the deflection in both directions is at a maximum, a greater intensity of the convergence current is required. This is especially the case in picture tubes having a great deflection angle and according to the invention this is achieved in that the current which is derived from the power winding 11 of the transductor for the raster correction is also applied to the convergence circuit. This current flows from the horizontal deflection generator constituted by windings 3 and 4 through the primary winding of transformer 20 to power winding 11 of the transductor. The transductor current is in fact at a minimum in the center of the picture and increases towards the edges and particularly towards the corners. Thus the convergence current varies in the desired manner. According to the invention the desired improvements of the convergence correction and simultaneously the likewise desired increase in the internal resistance of the horizontal deflection generator is consequently obtained without a considerable increase in the number of required circuit elements and without disturbing the normal operation of the circuit arrangement. Due to transformer 20 a terminal of convergence circuit 17 may be connected to ground so that the convergence can be adjusted safely. If necessary, a suitable impedance transformation may also be obtained with the aid of transformer 20.

vergence current is only influenced by the deflection current itself. It has been found that in this case the convergence correction is not sufficient in the corners of the picture. At these areas, where the deflection in both directions is at a maximum, a greater intensity of the convergence current is required. This is especially the case in picture tubes having a great deflection angle and according to the invention this is achieved in that the current which is derived from the power winding 11 of the transductor for the raster correction is also applied to the convergence circuit. This current flows from the horizontal deflection generator constituted by windings 3 and 4 through the primary winding of transformer 20 to power winding 11 of the transductor. The transductor current is in fact at a minimum in the center of the picture and increases towards the edges and particularly towards the corners. Thus the convergence current varies in the desired manner. According to the invention the desired improvements of the convergence correction and simultaneously the likewise desired increase in the internal resistance of the horizontal deflection generator is consequently obtained without a considerable increase in the number of required circuit elements and without disturbing the normal operation of the circuit arrangement. Due to transformer 20 a terminal of convergence circuit 17 may be connected to ground so that the convergence can be adjusted safely. If necessary, a suitable impedance transformation may also be obtained with the aid of transformer 20.The linearity control circuit 21 may alternatively be connected in series with the said branch which includes transformer 20. As a result the internal resistance of the horizontal deflection generator for the line frequency is further increased without the field correction and the convergence correction being disturbingly influenced.

FIG. 2 shows a modification of the circuit arrangement according to the invention in which the deflection current is not changed relative to that of FIG. 1. The end of power winding 11 of the transductor shown on the upper side of FIG. 1 is connected to ground in FIG. 2. In addition convergence circuit 17 is included between winding 3 and ground so that separation transformer 20 may be omitted. If as a first approximation the impedances 5 and 17 are assumed to be negligibly small relative to the other impedance of the circuit arrangement, power winding 11 may be considered to be connected to a tap on the deflection generator 3, 4. Consequently, only approximately half the voltage of the deflection generator is applied to transductor winding 11 which winding must

therefore be proportioned in such a manner that it can convey a current which is approximately twice as large as that of FIG. 1. This larger current also flows through convergence circuit 17 which, with the omission of separation transformer 20, is favorable for the convergence in the corners of the picture screen.

therefore be proportioned in such a manner that it can convey a current which is approximately twice as large as that of FIG. 1. This larger current also flows through convergence circuit 17 which, with the omission of separation transformer 20, is favorable for the convergence in the corners of the picture screen.In FIG. 2 the emitter of transistor 2 is connected to ground i.e., the said tap on the deflection generator. During the scan period the series arrangement of supply source V b and windings 3 and 4 FIG. 1 is substantially short-circuited by transistors 1 and 2. In order that these transistors in the circuit arrangement according to FIG. 2 operate under the same circumstances as those in FIG. 1, an additional winding 24 must be wound on core 7 between windings 4 and 6, winding 24 having the same number of turns as winding 3, and the collector of transistor 1 must be connected to the junction of windings 6 and 24.

The end of power winding 11 connected to ground in FIG. 2 may alternatively be connected for the desired adjustment of the corner convergence to a different tap on the transformer, that is to say, on winding 3 or 4.

Resistor 5 serves in known manner mainly as a safety resistor so that in case of an inadmissible load of the EHT, for example, as a result of flash-over in the picture tube, the supply voltage for transistors 1 and 2 is reduced so that overload of these transistors is avoided.

PHILIPS X26K206 TIZIANO CHASSIS K9 E/W CORRECTION Circuit arrangement in an image display apparatus for (horizontal) line deflection

Line deflection circuit in which the deflection coil is east-west modulated. In order to cancel an east-west dependent horizontal linearity defect the inductance value of the linearity correction coil is made independent of the field frequency, for example by means of a compensating current. In an embodiment this current is supplied by the shunt coil of the east-west modulator.

1. Circuit arrang

ement for use with a line deflection coil, said circuit comprising a generator means adapted to be coupled to said coil for producing a sawtooth line-deflection current through said line deflection coil, said deflection current having a field-frequency component current, a horizontal linearity correction coil adapted to be coupled in series with said deflection coil and including an inductor having a bias-magnetized core, and means for making the inductance value of the linearity correction coil substantially independent of the field frequency component current. 2. Circuit arrangement as claimed in claim 1, wherein said making means includes a current supply source means for producing a compensating line-frequency sawtooth current through a winding of the linearity correction coil, the amplitude of the compensating current having a field-frequency variation. 3. Circuit arrangement as claimed in claim 2, wherein the direction of curvature of the field-frequency envelope of the compensating current is opposite to the direction of curvature of the field-frequency component current of the line deflection current, whereby the magnetic fields produced in the core of the correction coil by the two currents have the same direction. 4. Circuit arrangement as claimed in claim 2, wherein the direction of curvature of the field-frequency envelope of the compensating current is the same as the direction of curvature of the field-frequency component current of the line deflection current, whereby the magnetic fields produced in the core of the correction coil by the two currents have opposite directions. 5. Circuit arrangement as claimed in claim 2, wherein said correction coil further comprises an additional winding disposed on the core, said additional winding being coupled to said supply source means to receive the compensating current. 6. Circuit arrangement as claimed in claim 5, further comprising modulator means for modulating the line deflection current with said field frequency component, said modulator including a compensation coil coupled in series with said additional winding. 7. Horizontal linearity correction coil comprising a core made of a magnetic material and bias-magnetized by at least one permanent magnet, and an additional winding disposed on the core. 8. Image display apparatus including a circuit arrangement as claimed in claim 1.

ement for use with a line deflection coil, said circuit comprising a generator means adapted to be coupled to said coil for producing a sawtooth line-deflection current through said line deflection coil, said deflection current having a field-frequency component current, a horizontal linearity correction coil adapted to be coupled in series with said deflection coil and including an inductor having a bias-magnetized core, and means for making the inductance value of the linearity correction coil substantially independent of the field frequency component current. 2. Circuit arrangement as claimed in claim 1, wherein said making means includes a current supply source means for producing a compensating line-frequency sawtooth current through a winding of the linearity correction coil, the amplitude of the compensating current having a field-frequency variation. 3. Circuit arrangement as claimed in claim 2, wherein the direction of curvature of the field-frequency envelope of the compensating current is opposite to the direction of curvature of the field-frequency component current of the line deflection current, whereby the magnetic fields produced in the core of the correction coil by the two currents have the same direction. 4. Circuit arrangement as claimed in claim 2, wherein the direction of curvature of the field-frequency envelope of the compensating current is the same as the direction of curvature of the field-frequency component current of the line deflection current, whereby the magnetic fields produced in the core of the correction coil by the two currents have opposite directions. 5. Circuit arrangement as claimed in claim 2, wherein said correction coil further comprises an additional winding disposed on the core, said additional winding being coupled to said supply source means to receive the compensating current. 6. Circuit arrangement as claimed in claim 5, further comprising modulator means for modulating the line deflection current with said field frequency component, said modulator including a compensation coil coupled in series with said additional winding. 7. Horizontal linearity correction coil comprising a core made of a magnetic material and bias-magnetized by at least one permanent magnet, and an additional winding disposed on the core. 8. Image display apparatus including a circuit arrangement as claimed in claim 1.  y correction coil the linearity error due to the ohmic resistance of the deflection circuit is corrected. The sign of the bias magnetisation is chosen so that it is cancelled by the deflection current at the beginning of the deflection interval, so that the inductance of the correction coil is a maximum, whereas the voltage drop across the deflection coil then is a minimum. This voltage drop is adjustable by adjustment of the starting inductance of the correction coil. During the deflection interval the core gradually becomes saturated so that the inductance of, and the voltage drop across, the correction coil decrease. Thus the linearity error can be cancelled exactly at the beginning of the interval, that is to say on the left on the screen of the image display tube, and with a certain approximation at other locations.

y correction coil the linearity error due to the ohmic resistance of the deflection circuit is corrected. The sign of the bias magnetisation is chosen so that it is cancelled by the deflection current at the beginning of the deflection interval, so that the inductance of the correction coil is a maximum, whereas the voltage drop across the deflection coil then is a minimum. This voltage drop is adjustable by adjustment of the starting inductance of the correction coil. During the deflection interval the core gradually becomes saturated so that the inductance of, and the voltage drop across, the correction coil decrease. Thus the linearity error can be cancelled exactly at the beginning of the interval, that is to say on the left on the screen of the image display tube, and with a certain approximation at other locations.  was found in practice that the said two corrections are not independent of one another, that is to say the adjustment of the east-west modulation affects horizontal linearity. As long as the modulation depth is not excessive, a satisfactory compromise can be found. However, in display tubes having a deflection angle of 110° and particularly in colour display tubes in which the deflection coils have a converging effect also, it is difficult to find such a compromise. A tube of this type is described in "Philips Research Reports," volume Feb. 14, 1959, pages 65 to 97; the distribution of the deflection field is such that throughout the display screen the landing points of the electron beams coincide without the need for a converging device. Owing to this field distribution, however, the pin-cushion-shaped distortion in the image displayed in the east-west direction is greater than in comparable display tubes of another type. Hence there must be east-west modulation of the line deflection current to a greater depth. It is true that under these conditions horizontal linearity can correctly be adjusted over a given horizontal strip after the east-west modulation has been adjusted correctly, i.e., for a rectangular image, but it is found that in other parts of the display screen a serious linearity error remains. When vertical straight lines are displayed as straight lines in the right-hand part of the screen, they are displayed as curved lines in the left-hand part.

was found in practice that the said two corrections are not independent of one another, that is to say the adjustment of the east-west modulation affects horizontal linearity. As long as the modulation depth is not excessive, a satisfactory compromise can be found. However, in display tubes having a deflection angle of 110° and particularly in colour display tubes in which the deflection coils have a converging effect also, it is difficult to find such a compromise. A tube of this type is described in "Philips Research Reports," volume Feb. 14, 1959, pages 65 to 97; the distribution of the deflection field is such that throughout the display screen the landing points of the electron beams coincide without the need for a converging device. Owing to this field distribution, however, the pin-cushion-shaped distortion in the image displayed in the east-west direction is greater than in comparable display tubes of another type. Hence there must be east-west modulation of the line deflection current to a greater depth. It is true that under these conditions horizontal linearity can correctly be adjusted over a given horizontal strip after the east-west modulation has been adjusted correctly, i.e., for a rectangular image, but it is found that in other parts of the display screen a serious linearity error remains. When vertical straight lines are displayed as straight lines in the right-hand part of the screen, they are displayed as curved lines in the left-hand part.  simplified circuit diagram of a line deflection circuit of an image display apparatus, not shown further. The circuit includes the series combination of a line deflection coil L y , a linearity correction coil L and a trace capacitor C t , which series combination is traversed by the line deflection current i y . The collector of an npn switching transistor T r and one end of a choke coil L 1 are connected to a junction point A of a diode D, a capacitor C r and the said series combination. The other end of the choke coil is connected to the positive terminal of a supply voltage source which supplies a substantially constant direct voltage V b and to the negative terminal of which the emitter of transistor Tr is connected. This negative terminal may be connected to earth. The other junction point B of elements D and C r and of the series combination of elements C t , L y and L is connected to one terminal of a modulation source M for east-west correction which has its other terminal connected to earth. Diode D has the pass direction shown in the FIG.

simplified circuit diagram of a line deflection circuit of an image display apparatus, not shown further. The circuit includes the series combination of a line deflection coil L y , a linearity correction coil L and a trace capacitor C t , which series combination is traversed by the line deflection current i y . The collector of an npn switching transistor T r and one end of a choke coil L 1 are connected to a junction point A of a diode D, a capacitor C r and the said series combination. The other end of the choke coil is connected to the positive terminal of a supply voltage source which supplies a substantially constant direct voltage V b and to the negative terminal of which the emitter of transistor Tr is connected. This negative terminal may be connected to earth. The other junction point B of elements D and C r and of the series combination of elements C t , L y and L is connected to one terminal of a modulation source M for east-west correction which has its other terminal connected to earth. Diode D has the pass direction shown in the FIG.  ottom left-hand part of FIG. 3 flows through the coil, the field strength H varies proportionally about the value H 0 , for the mean value of the current is zero. Because the curve of L is not linear, the variation L(t) of L, which is shown in the top right-hand part, is not a linear function of time. The resulting curve may be regarded as composed of a linear component and a substantially parabolic component which is to be taken into account when choosing the capacitance of capacitor C t .

ottom left-hand part of FIG. 3 flows through the coil, the field strength H varies proportionally about the value H 0 , for the mean value of the current is zero. Because the curve of L is not linear, the variation L(t) of L, which is shown in the top right-hand part, is not a linear function of time. The resulting curve may be regarded as composed of a linear component and a substantially parabolic component which is to be taken into account when choosing the capacitance of capacitor C t .  . The amplitude of current i 2 and the turns number of winding L 2 can be chosen so that current i y flows through inductances the total value of which is not dependent upon the field frequency. The curve L(t) of FIG. 3 remains substantially unchanged. Consequently the undesirable field-frequency modulation is removed without variation of the bias magnetization, which would have been varied if current i 2 were a field-frequency current. Obviously the same result can be achieved by a choice such of the direction of current i 2 and of the winding sense of winding L 2 that the two field strengths are subtracted one from the other, whilst the curvature of the envelope of current i 2 has the same direction as that of the envelope of current i y .