The CHASSIS D16 from PHILIPS is his most sophisticated and complex type.

It employs the DIGIVISION ITT DIGIT2000 Technology even when PHILIPS has developed his own 100HZ digital technology.

This is a great example of the Extreme flexibilty of the research & development of PHILIPS which was basically completely free to develop and design chassis technology without marketing obligations or any type of blocking circumstances in any field or aspect design.

The CHASSIS PHILIPS D16 Is a semi modular type and it has additional horizontal board for further device like audio processing and I/O selection / expansion including a D2B Bus connection feature.

The CHASSIS PHILIPS D16 Is a semi modular type and it has additional horizontal board for further device like audio processing and I/O selection / expansion including a D2B Bus connection feature.Here described the functions featured:

D2B Bus :Domestic Digital Bus (D2B) SMARTwireX: D2B is an optical data bus system that was developed to connect audio, video, computer, and telephone components in a single ring structure within a vehicle. SMARTwireX defines a physical layer supporting the D2B networks running up to 25 Mb/sec and featuring automotive compatibility. It is an electrical physical solution for automotive networks.

The present invention D2B Bus :Domestic Digital Bus (D2B) SMARTwireX relates to a communication protocol for use in communication among AV (audio-video) equipments, communication among computers and communication among AV equipments and computers, for example.

It is customary that the AV system is formed of a plurality of AV equipments, such as a TV (television receiver), an MDP (multi-media player), a VTR (video tape recorder), an AV center (switcher) or the like.

In the AV system, a plurality of AV equipments, such as TV, MDP, VTR and AV center, are connected together by means of video signal lines, audio signal lines and control signal lines (control buses). A variety of control signals and data (e.g., packets of predetermined formats) are supplied to the AV equipments via the control buses, whereby the respective AV equipments are operated in a ganged fashion.

In the AV system, a plurality of AV equipments, such as TV, MDP, VTR and AV center, are connected together by means of video signal lines, audio signal lines and control signal lines (control buses). A variety of control signals and data (e.g., packets of predetermined formats) are supplied to the AV equipments via the control buses, whereby the respective AV equipments are operated in a ganged fashion.Specifically, according to the AV system, when a play button of the VTR is operated, a packet is output to the TV and the AV center from the VTR, whereby the TV and the AV center are powered. Further, the AV center is switched such that the VTR and the TV are connected together, and image and sound reproduced by the VTR are output from the VTR.

The packets are communicated in the following procedure:

(T1) Routing information transmission

(T2) Command (CMD) transmission

(T3) Request (REQ) transmission

(T4) Get answer (GET-ANS) transmission.fwdarw.answer (ANS) reception

(T5) End (END) transmission

Initially, an AV equipment which transmits a packet first is set to "master apparatus" and an AV equipment which receives such packet is set to "slave apparatus". Routing information is transmitted from the master apparatus to the slave apparatus (T1). At that time, the slave apparatus is locked so that it is inhibited from receiving a packet transmitted from other AV equipment.

Then, a command (CMD) which turns on the power supply is transmitted from the master apparatus to the slave apparatus (T2). A request (REQ) which solicits the processing of the command is further transmitted from the master apparatus to the slave apparatus (T3).

Then, in order to obtain an answer (ANS) for REQ, the get answer (GET-ANS) is transmitted from the master apparatus to the slave apparatus (T4). The GET-ANS is repeatedly transmitted until the answer ANS is obtained from the slave apparatus. When the answer (ANS) is obtained from the slave apparatus, an end (END) representing the end of the processing is transmitted (T5). At that time, the slave apparatus which is set in the locked state is set in the unlock state. Therefore, the slave apparatus is set in a state that it can again receive a packet transmitted from the AV equipment.

As described above, the packet exchange procedure in the conventional AV system is cumbersome.

Since the GET-ANS is repeatedly transmitted until the answer ANS is obtained from the slave apparatus, the traffic on the control bus is increased. Furthermore, it is frequently observed that other AV equipments cannot use the control bus. There is then the problem that the overall processing speed of the system is lowered.

Since the GET-ANS is repeatedly transmitted until the answer ANS is obtained from the slave apparatus, the traffic on the control bus is increased. Furthermore, it is frequently observed that other AV equipments cannot use the control bus. There is then the problem that the overall processing speed of the system is lowered.When a packet is transmitted from the master apparatus to the slave apparatus, for example, the CMD transmission and the REQ transmission, the communication mode of the master apparatus is set in the master communication mode, and the communication mode of the slave apparatus is set in the slave reception mode. If on the other hand a packet is expected to be transmitted from the slave apparatus to the master apparatus, such as when the master apparatus does not receive the answer (ANS) from the slave apparatus, and therefore issues the GET-ANS, the communication mode of the master apparatus is set in the master reception mode and the communication mode of the slave apparatus is set in the slave transmission mode.

As described above, there are four communication modes such as the master transmission mode, the master reception mode, the slave transmission mode and the slave reception mode. Therefore, each AV equipment must exchange a packet by switching the four modes and a communication efficiency is low.

Further, each AV equipment needs four buffers including a master transmission buffer for latching a packet transmitted in the master transmission mode, a master reception buffer for latching a packet received in the master reception mode, a slave transmission buffer for latching a packet transmitted in the slave transmission mode and a slave reception buffer for latching a packet received in the slave reception mode. There is then the problem that the apparatus becomes large in size and expensive.

Furthermore, since the reception side cannot recognize a transmission error, there is then the problem that an error recovery processing required when a transmission error occurs becomes complex.

In addition, date of 3 frames must be transmitted at minimum in order to transmit pure data, e.g., OSD data. There is then the problem that a lot of time must be prepared and that the processing becomes complex.

SUMMARY OF THE INVENTION

In view of the aforesaid aspect, an object of the present invention is to provide a communication protocol for communicating data in which a communication can be efficiently made by a simple procedure.

According to a first aspect of the present invention, there is provided a communication protocol for communicating data by a serial format which is comprised of a command packet informing an operation command, a status request packet informing a status request of some apparatus, a data request packet informing a data request to some apparatus, a datum packet informing data, an answer packet informing answer datum for previous request, an automatic status sending packet informing a status of an apparatus, and a simulcast packet informing simulcast datum for a plurality of apparatus.

According to a second aspect of the present invention, there is provided a communication system for communicating data which is comprised of a command packet communicating member for communicating a command packet, a status request packet communicating member for communicating a status request packet. a data request packet communicating member for communicating a data request packet, a datum packet communicating member for communicating a datum packet, an answer packet communicating member for communicating an answer packet, an automatic status sending packet communicating member for communicating an automatic status sending packet, and a simulcast packet communicating member for communicating a simulcast packet.

In accordance with a third aspect of the present invention, there is provided a communication system for communicating data which is comprised of a master apparatus which comprises a command packet communicating member for communicating a command packet, a status request communicating member for communicating a status request packet, a data request packet communicating member for communicating a data request packet, a datum packet communicating member for communicating a datum packet, an answer packet communicating member for communicating an answer packet, an automatic status packet communicating member for communicating an automatic status sending packet, and a simulcast packet communicating member for communicating a simulcast packet, and a slave apparatus which comprises a command packet communicating member for communicating a command packet, a status request packet communicating member for communicating a status request packet, a data request packet communicating member for communicating a data request packet, a datum packet communicating member for communicating a datum packet, an answer packet communicating member for communicating an answer packet, an automatic status sending packet communicating member for communicating an automatic status sending packet, and a simulcast packet communicating member for communicating a simulcast packet.

In accordance with a third aspect of the present invention, there is provided a communication system for communicating data which is comprised of a master apparatus which comprises a command packet communicating member for communicating a command packet, a status request communicating member for communicating a status request packet, a data request packet communicating member for communicating a data request packet, a datum packet communicating member for communicating a datum packet, an answer packet communicating member for communicating an answer packet, an automatic status packet communicating member for communicating an automatic status sending packet, and a simulcast packet communicating member for communicating a simulcast packet, and a slave apparatus which comprises a command packet communicating member for communicating a command packet, a status request packet communicating member for communicating a status request packet, a data request packet communicating member for communicating a data request packet, a datum packet communicating member for communicating a datum packet, an answer packet communicating member for communicating an answer packet, an automatic status sending packet communicating member for communicating an automatic status sending packet, and a simulcast packet communicating member for communicating a simulcast packet.The D16 Has even PIP functions but this section is SIEMENS Chipset based.

Description:This invention relates generally to digital television receivers and, particularly, to digital television receivers arranged for economical interfacing with a plurality of auxiliary devices.

With the proliferation of low cost microprocessors and microprocessor controlled devices, television (TV) receivers are being designed to utilize digitized signals and controls. There are many advantages associated with digital TV receivers, including uniformity of product, precise control of signal parameters and operating conditions, elimination of mechanical switches and a potential for reliability that has been heretofore unknown. Digital television receivers include a high speed communication bus for interconnecting a central control unit microprocessor (CCU) with various TV function modules for processing a TV signal. These modules include a deflection processing unit (DPU), a video processing unit (VPU), an automatic phase control (APC), a video codec unit (VCU), an audio analog to digital converter (ADC) and an audio processing unit (APU). The CCU has associated with it a non-volatile memory, a hardware-generated clock signal source and a suitable interface circuit for enabling the CCU to control processing of the TV signal throughout the various TV function modules. The received TV signal is in analog form and suitable analog to digital (A/D) converters and digital to analog (D/A) converters are provided for converting the digital and analog signals for signal processing and for reconverting them after processing for driving a cathode ray tube (CRT) and suitable speakers. The CCU microprocessor is heavily burdened because of the high speed timing required to control the various TV function modules.

To further complicate matters, modern TV receivers are increasingly being used with auxiliary devices for other than simple processing of TV signals. For example, the video cassette recorder (VCR) has enabled so-called "time-shifting" of program material by recording TV signals for later, more convenient viewing. The VCR is also extensively used with prerecorded material and with programs produced by users having access to a video camera. Other auxiliary devices providing features such as "Space Phone" whereby the user is enabled to make and receive telephone calls through his TV receiver, are desirable options. Additionally, a source selector auxiliary device enables a host of different signal sources, such as cable, over-the-air antenna, video disk, video games, etc. to be connected for use with the signal processing circuitry of the TV. In addition, all of these many auxiliary devices are preferably controllable from a remote position. A great deal of flexibility is available since each of the above auxiliary devices includes a microprocessor for internally controlling functioning of the device.

To further complicate matters, modern TV receivers are increasingly being used with auxiliary devices for other than simple processing of TV signals. For example, the video cassette recorder (VCR) has enabled so-called "time-shifting" of program material by recording TV signals for later, more convenient viewing. The VCR is also extensively used with prerecorded material and with programs produced by users having access to a video camera. Other auxiliary devices providing features such as "Space Phone" whereby the user is enabled to make and receive telephone calls through his TV receiver, are desirable options. Additionally, a source selector auxiliary device enables a host of different signal sources, such as cable, over-the-air antenna, video disk, video games, etc. to be connected for use with the signal processing circuitry of the TV. In addition, all of these many auxiliary devices are preferably controllable from a remote position. A great deal of flexibility is available since each of the above auxiliary devices includes a microprocessor for internally controlling functioning of the device. In the digital TV system described, the CCU microprocessor and the microprocessors in the auxiliary devices may be conventionally arranged to communicate over the main communication bus. Such a system would entail a specialized microprocessor with a hardware-generated clock signal in each auxiliary device in order to communicate at the high speeds used on the main communication bus. A specialized microprocessor, that is, one that is hardware configured, is significantly more expensive than an off-the-shelf microprocessor. Also, the auxiliary devices may not be required, or even desired, by all users and their low volume production cost becomes very important. It would therefore be desirable to provide a digital TV in which such auxiliary devices utilized off-the-shelf microprocessors for their control.

A digital TV system includes a CCU that is interconnected by a three-wire, high speed bus to a plurality of TV signal function modules for controlling operation thereof by means of a high speed hardware generated clock signal. A software generated clock signal in the CCU is supplied on a low speed two-wire auxiliary device bus which is connected to microprocessors in a plurality of auxiliary devices for performing functions ancillary to TV signal processing. The microprocessor in each auxiliary device is an off-the-shelf type that does not require any special hardware because the timing on the auxiliary device bus is sufficiently slow to enable software monitoring of the line and data transfer.

As mentioned, the three-wire IM bus 21 is a high speed bidirectional bus in which CCU 20 functions as the master and all of the interconnected TV signal processing function modules are slaves that communicate with the CCU in accordance with the protocol established for the system. CCU 20 is also indicated as including a software generated clock which supplies a two-wire auxiliary device bus 50. Two-wire bus 50 includes a clock lead 51 and a data lead 52 coupled to a plurality of auxiliary devices. A VCR 54, including an off-the-shelf microprocessor 55, is coupled to bus 50. A Source Selector 56, including an off-the-shelf microprocessor 57, is also coupled to bus 50. Source Selector 56 has access to four RF inputs, two baseband video and audio inputs and one separate baseband audio input. It will be appreciated that Source Selector 56 may have a greater or lesser number of signal sources to which it has access. Source Selector 56 outputs are coupled to VCR 54 and also to tuner 10 and supply, under control of CCU 20 and keyboard 44, the signal from the signal source selected by keyboard 44 or IR transmitter 46 for use with the digital TV. Auxiliary device bus 50 is also coupled to a Space Phone 58 which includes an off-the-shelf microprocessor 59 and a modem 60 that is connectable to a conventional telephone terminal.

As mentioned, the three-wire IM bus 21 is a high speed bidirectional bus in which CCU 20 functions as the master and all of the interconnected TV signal processing function modules are slaves that communicate with the CCU in accordance with the protocol established for the system. CCU 20 is also indicated as including a software generated clock which supplies a two-wire auxiliary device bus 50. Two-wire bus 50 includes a clock lead 51 and a data lead 52 coupled to a plurality of auxiliary devices. A VCR 54, including an off-the-shelf microprocessor 55, is coupled to bus 50. A Source Selector 56, including an off-the-shelf microprocessor 57, is also coupled to bus 50. Source Selector 56 has access to four RF inputs, two baseband video and audio inputs and one separate baseband audio input. It will be appreciated that Source Selector 56 may have a greater or lesser number of signal sources to which it has access. Source Selector 56 outputs are coupled to VCR 54 and also to tuner 10 and supply, under control of CCU 20 and keyboard 44, the signal from the signal source selected by keyboard 44 or IR transmitter 46 for use with the digital TV. Auxiliary device bus 50 is also coupled to a Space Phone 58 which includes an off-the-shelf microprocessor 59 and a modem 60 that is connectable to a conventional telephone terminal. Two-wire auxiliary device bus 50 is a relatively low speed bus and there is no need for separate hardware generated clock signals to be developed by the auxiliary device microprocessors. As mentioned above, this feature involves a significant savings in the cost and complexity of the auxiliary devices.

The protocol used on the two-wire auxiliary device bus consists of a 16 bit sequence, the first eight bits of which are used for bus address commands for the auxiliary devices. Each auxiliary device may respond to 16 addresses which allows the CCU to write into or read from various storage registers in the devices which are used for control or data storage. Thus, with this low cost system, as many as 16 auxiliary devices may be connected to the auxiliary device bus. The second eight bits of the 16 bit sequence contain data which is either transferred from the CCU to the auxiliary device addressed, or transferred from the auxiliary device to the CCU, based upon the bus address used. Thus, the various bus addresses to which a given auxiliary device will respond determine whether the auxiliary device will receive data from the CCU or send data to the CCU. The clock line timing, generated by software in CCU 20, is slow enough to permit software monitoring of the line and data reception by simple auxiliary device microprocessors that are not equipped with an external interrupt feature. The timing on the auxiliary device bus is made sufficiently fast to avoid too many instruction steps or the need for special registers in CCU 20. In the system described, data is clocked every 82.5 microseconds, thus permitting a 16 bit word to be clocked in 1.32 milliseconds. A pause of 277.5 microseconds between the first 8 bits and the second 8 bits permits the slave auxiliary device to process the bus address data contained in the first 8 bits. This timing fits into the 2 millisecond timing block structure used for the CCU in controlling the DIGIT 2000 digital TV. Two-2 millisecond timing blocks have been established in the CCU, which has a 20 millisecond timing loop divided into ten-2 millisecond timing blocks. Thus, two control words may be sent to an auxiliary device every 20 milliseconds, or a request by the CCU to receive data and the actual receipt of that data may take place in that time period.

Referring to the drawing, a digital TV includes a tuner 10 coupled to an IF/Detector 12 which has a pair of outputs 13 and 14 supplying video and audio signals, respectively. Control signals for tuner 10 are supplied through an interface circuit 16 from a CCU microprocessor 20 which functions as a single master control unit for the system. Microprocessor 20 is interconnected by means of a bidirectional three-wire IM (Intermetal) bus 21 to a DPU 22, a VPU 26, an APC 30, a TTX (teletext processor) 38, an APU 36, an ADC 32 and a non-volatile memory 24. A serial control line 29 interconnects a hardware generated clock 28, VPU 26 and VCU 34. VPU 26 and VCU 34 are also interconnected by a seven wire cable and TTX 38 is interconnected with a DRAM 42. DRAM 42 is a dynamic RAM in which TTX information is stored for display. VCU 34 is supplied with video signal and supplies a digitized 7 bit grey coded video signal to VPU 24 for processing and RGB color signals to a Video Drive 40 which, in turn, supplies a cathode ray tube (not shown). A keyboard 44 is coupled to CCU 20 and includes an IR detector that is responsive to coded IR signals supplied from an IR transmitter (IRX) 46. A resident microprocessor in keyboard 44 decodes the received IR signals and generated control commands and supplies appropriate outputs to CCU 20. The diagram, as described, is substantially identical to that for a "DIGIT" 2000 VLSI Digital TV System developed by ITT Intermetal and published in Edition 1984/85 Order No. 6250-11-2E

- JPEG (Joint Photographic Expert Group) for still pictures coding

- H.261 at p times 64 kbit/s was proposed by the CCITT (Consultative Committee on International Telephony and Telegraphy) for teleconferencing

- MPEG-1 (Motion Picture Expert Group) up to 1,5 Mbit/s was proposed for full motion compression on digital storage media

- MPEG-2 was proposed for digital TV compression, the bandwith depends on the chosen level and profile [33].

2. Features of the CCU 2030, CCU 2050 and CCU 2070

With the proliferation of low cost microprocessors and microprocessor controlled devices, television (TV) receivers are being designed to utilize digitized signals and controls. There are many advantages associated with digital TV receivers, including uniformity of product, precise control of signal parameters and operating conditions, elimination of mechanical switches and a potential for reliability that has been heretofore unknown. Digital television receivers include a high speed communication bus for interconnecting a central control unit microprocessor (CCU) with various TV function modules for processing a TV signal. These modules include a deflection processing unit (DPU), a video processing unit (VPU), an automatic phase control (APC), a video codec unit (VCU), an audio analog to digital converter (ADC) and an audio processing unit (APU). The CCU has associated with it a non-volatile memory, a hardware-generated clock signal source and a suitable interface circuit for enabling the CCU to control processing of the TV signal throughout the various TV function modules. The received TV signal is in analog form and suitable analog to digital (A/D) converters and digital to analog (D/A) converters are provided for converting the digital and analog signals for signal processing and for reconverting them after processing for driving a cathode ray tube (CRT) and suitable speakers. The CCU microprocessor is heavily burdened because of the high speed timing required to control the various TV function modules.

Central

Control Units All three types, differing only in their ROM and RAM

capacity, are the unprogrammed versions and are programmed during

production according to the customer's specifications. For programming,

an emulator board is available. The programmed versions have the type

designations CCU2031, CCU 2032 and so on. Combined with peripheral

hardware, CCU 2030, CCU 2050 and CCU 2070 offer the following features:

infrared remote control ~ front-panel control with up to 32 commands —

tuning by frequency synthesis (PLL) and band switching non-volatile

program storage LED display for channel indication, max. 4 digits,

directly driven storage of alignment information during production

generation and recognition of various signals control of the digital

signal processors for video, audio, teletext and deflection via a serial

bus (IM bus) The CCUs are produced in N-channel HMOS technology, are

housed in a 40-pin Dil plastic package, and contain on one chip the

following functions (Fig. 4): 8049 8-bit

microcomputer

remote-control decoder Ports P2 and P3 for connecting a maximum of 32

keys and 4-digit seven-segment LED channel indication PLL tuner circuit

for VHF and UHF IM bus interface for inputting and outputting control

signals and for inputting alignment instructions crystal-controlled

clock oscillator which also serves as reference for the PLL circuit

mains flip-flop and reset circuit This specification is restricted to

the hardware aspects of the CCU 20.0 Central Control Unit. Many

functions are defined in detail by the microcomputer’s ROM code and are

thus described in the program specifications of the individual

applications. For understanding the operation of the CCU, the following

texts are useful: IM bus specification (section 11.) and the manual of

the 48-series microprocessor family (see sections 12. and 13.).

3. Functional Description

The

CCU 20.0 Central Control Unit provides an efficient interface between

user and TV set. Their programmability enables different set makers to

design receivers according to their own specs. The CCU has the main

functions: — processing of user’s settings — control of the digital

signal processors for video, audio, Teletext and deflection By means of

the MDA 2062 non-volatile memory (EE-PROM) which has a capacity of 128 x

8 bits, the CCU controls storage and output of factory alignment values

that have been programmed during production of the TV set.

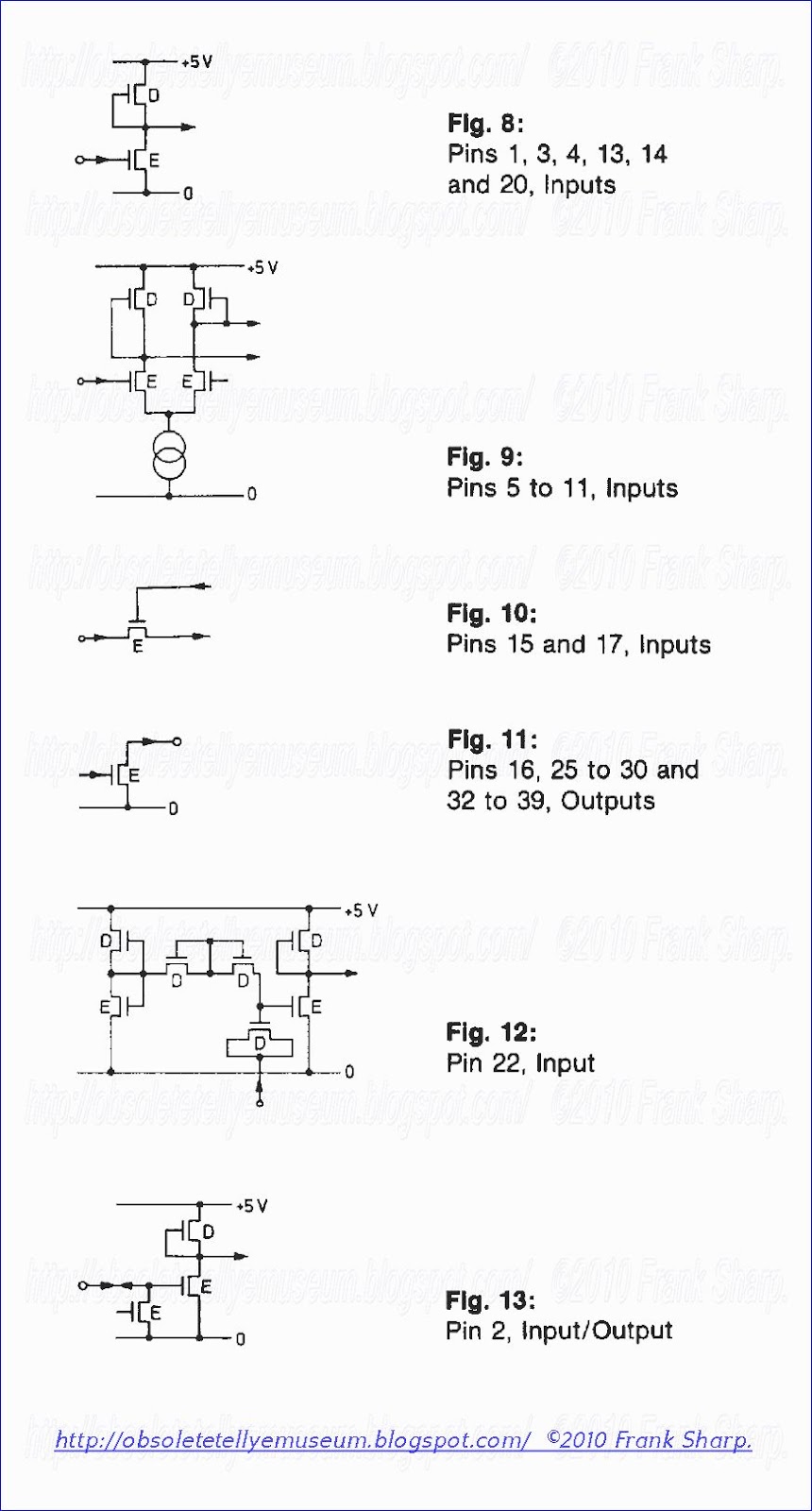

10. Description of the Connections and Signals

Pin

1 — XTAL: Oscillator Crystal The internal configuration of this

in/output is shown in Fig. 8. For normal use, a 4 MHz crystal is

connected to this oscillator pin and to GND. The input is self-biasing

to ap- prox. 3.5 V, input DC resistance is approx. 350 kQ. The output

signal is the 4 MHz clock signal of the CCU. It may be fed to other

circuits, but maximum load configurations have to be observed as loading

affects oscillation start-up after power-on of the ST.BY supply (see

section 8.).

Pin 2 — S: Single-Step Input

The internal configuration of this input is shown in Fig. 9. Via this input, the CCU can be put into the single-step mode (see section 12.2.2.). The inactive low level is 0 to +5 V and the required, active high level is +12 V. The input contains a pull-down device (about 30 pA to GND) which allows to leave the input unconnected for normal operation.

Pin 3 - Osc Out: fos./4096 Output

‘The

internal configuration of this output is shown in Fig. 10. This output

provides the memory clock signal for the MDA 2062 EEPROM (1 kHz). The

drive capability of pin 3 is one TTL gate. The frequency is selected by a

mask option (see section 14.).

Pin 4 — Reset: Reset Input The internal configuration of this input is shown in Fig. 11. An active low level at this pin provides normalization for uC and peripheral circuits. An inactive high level is fed to the uC and peripheral circuits depending on the state of the mains flip-flop and the setting of the reset options (cf. sec- tions 4.6. and 14.). The input circuit is of a Schmitt trigger configuration and provides some noise immunity. In critical applications, however, an additional ceramic capacitor, connected between this pin and GND, may be necessary to increase noise immunity.

Pin 5 — Mains: Mains Switch Input/Output The internal configuration of this in/output is shown in Fig. 12.

Pin 5 represents the output of the mains flip-flop with a resistive pull-up. The output is active low (mains on). By shorting this pin to GND momentarily, the mains flip-flop is set to the active, low state via the input circuitry of this pin. The resistive pull-up provides drive for a PNP transistor connected emitter to ST.BY, base via a resistor to pin 5, and collector to the mains relay. A detailed functional de- scription of the mains flip-flop and reset circuit is given in section 4.6.

Pin 6 — EA: Test Enable Input The internal configuration of this input is shown in Fig. 9. Pin 6 is a test input providing external access to the uC (cf. sections 5. and 12.2.4.). For normal operation, an inactive low level is required at this pin (GND). Pin 7 to 9 — Data, Ident, Clock: IM Bus Connections The internal configurations of these pins are shown in Figs. 12 and 13. By means of these pins, the CCU links with peri- pheral devices. The IM bus is described in detail in section 11. Please note that the resistive pull-ups for all open-drain outputs connected to the IM bus are situated within the CCU.

Pins 10 and 11 — Up and Down: Tuning Voltage Outputs The internal configuration of these pins is shown in Fig. 13. Active high levels on these outputs indicate whether the tuner frequency should be increased (Up) or reduced (Down) and represent the output signals of the phase- locked loop circuit of the CCU (cf. section 4.4.). The out- puts contain resistive pull-ups.

Pin 12 — IR: Remote-Control Input The internal configuration of this pin is shown in Fig. 14. Via an external coupling capacitor of 10 nF, the remote-control signal, amplified by the TBA 2800 preamplifier IC, is fed to the remote-control decoder contained in the CCU (cf. sec- tion 4.2.). The input is self-biasing to approx. 1.4 V, and the input DC resistance is approx. 150 kQ. For highest input sensitivity, this pin must not be loaded resistively.

Pin 13 — LO: Local Oscillator Input The internal configuration of this input is shown in Fig. 14. Via an external coupling capacitor of at least 1 nF, the tuner oscillator frequency (signal), divided by 64 by a prescaler device, is fed to the PLL circuit contained in the CCU, thereby providing feedback from the tuner oscillator (cf. section 4.4.). The input is self-biasing to approx. 1.7 V, and the input DC resistance is approx. 200 kQ. For highest in- put sensitivity, this pin must not be loaded resistively.

Pin 14 to 19, 21 and 22 — Port P3, Bits 0 to 7 The internal configuration of these outputs or test in/out- puts is shown in Fig. 15. During normal use, these open- drain outputs provide multiplexed drive for LED display and keyboard (cf. section 4.3.). The voltage handling capability is limited to Vpp. During test operations (EA at or above 5 V, cf. section 5.), these pins give access to the nC bus port DBp to DB7 which also connects to peripheral circuits as PLL, IM bus interface, remote-control decoder etc. Drive capability of the bus port via P3 is very limited (external CMOS bidirectional buffers required).

Pin 20 — GND: Ground, 0 This pin must be connected to the negative of the supply. It may also be designated Vsgg. Please note that current on this pin is total Vpp and ST.BY supply current plus currents flowing into outputs (Port P3) and may amount to more than 300 mA.

Pins 23 to 26 and 36 to 39 — Port P2, Bits 0 to 7

The internal configuration of these in/outputs or test out- puts is shown in Fig. 16. Direct data transfer with the uC can be executed via this port (cf. sections 12.2.12. and 4.3.). The outputs drive one TTL gate. Open-drain outputs with a 5 V rating may be specified on each single pin of this port as an option (cf. section 14.). During test operations (EA at or above 5 V, cf. section 5.), P24, to P27 give access to the C output signals RD, WR, ALE and PSEN which al- so connect to peripheral circuits as PLL, IM bus interface, remote-control! decoder etc. Drive capability of the uC con- trol signals via connections P2, to P27 is very limited (exter- nal CMOS buffers required). Pin 27 — ST.BY: Standby Supply Voltage This pin must be connected to the positive of the 5 V standby supply. it powers the crystal oscillator, the mains flip-flop and reset circuits, the remote-control decoder and a specific portion of the 1.C-resident RAM. From standby operation, an infrared signal may activate the mains flip-flop and thus awake the system to full operation.

Pins 28 to 35 — Port P1, Bits 0 to 7

The internal configuration of these in/outputs is shown in Fig. 17. Direct data transfer with the 4C can be executed via this port (cf. section 12.2.12.). The outputs are open- drain with a 12 V rating. Pin 40 —- Vpp: Supply Voltage This pin must be connected to the positive of the 5 V supply.

11. Description of the IM Bus

The

INTERMETALL Bus (IM Bus for short) has been designed to control the

DIGIT 2000 ICs by the CCU Central Control Unit. Via this bus the CCU can

write data to the ICs or read data from them. This means the CCU acts

as a master whereas all controlled ICs are slaves. The IM Bus consists

of three lines for the signals Ident (ID), Clock (CL) and Data (D). The

clock frequency range is 50 Hz to 170 kHz. Ident and clock are

unidirectional from the CCU to the slave ICs, Data is bidirectional. Bi

directionality is achieved by using open-drain outputs with

On-resistances of 150 Q maximum. The 2.5 kQ. pull-up resistor common to

all outputs is incorporated in the CCU. The timing of a complete IM Bus

transaction is shown in Fig. 18 and Table 1.

In the non-operative state the signals of all three bus lines are High. To start a transaction the CCU sets the ID signal to Low level, indicating an address transmission, and sets the CL signal to Low level as well to switch the first bit on the Data line.

Thereafter

eight address bits are transmitted beginning with the LSB. Data

takeover in the slave ICs occurs at the High levels of the clock signal.

At the end of the address byte the ID signal goes High, initiating the

address comparison in the slave circuits. In the addressed slave the IM

bus interface switches over to Data read or write, because these

functions are correlated to the address. Also controlled by the address

the CCU now transmits eight or sixteen clock pulses, and accordingly one

or two bytes of data are written into the addressed IC or read out from

it, beginning with the LSB. The Low clock level after the last clock

pulse switches the Data line to High level. After this the completion of

the bus transaction is signalled by a short Low-state pulse of the ID

signal. This initiates the storing of the transferred data. It is

permissible to interrupt a bus transaction for up to 10 ms. For future

software compatibility, the CCU must write a zero into all bits not used

at present. When reading undefined or unused bits, the CCU must adopt

“don’t care” behaviour.

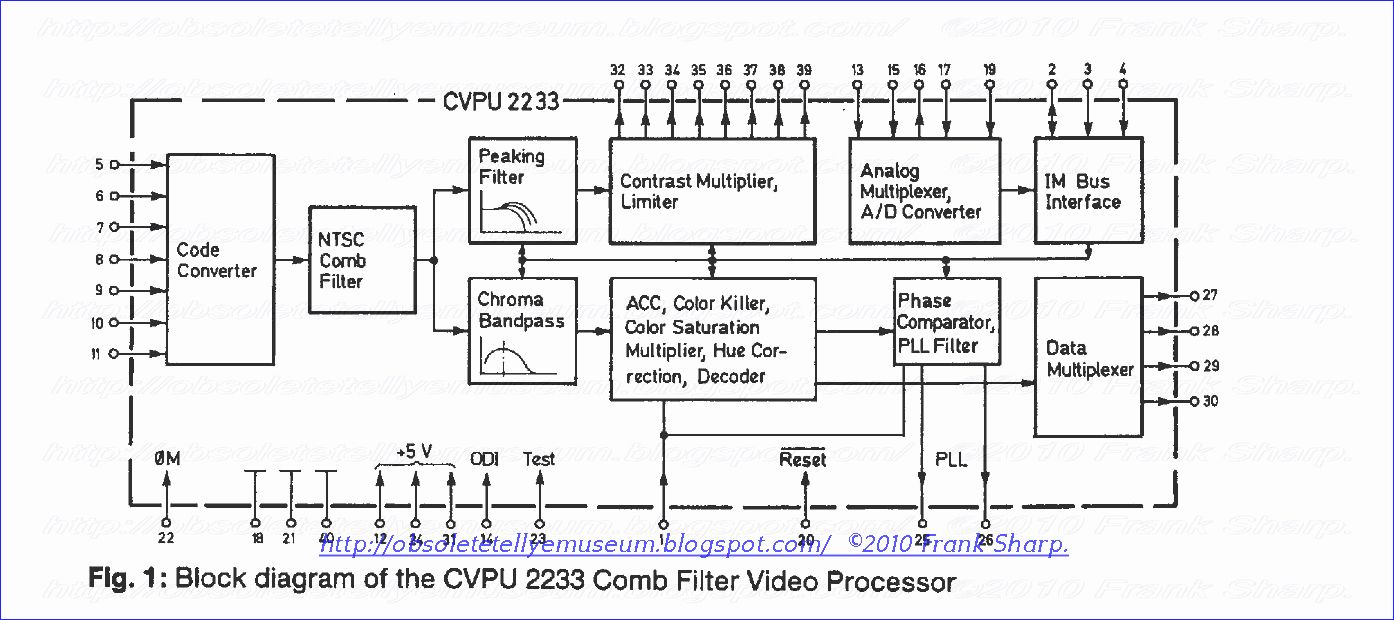

VCU 2134 Video Codec

High-speed

coder/decoder IC for analog - to-digital and digital-to- analog

conversion of the video signal in digital TV receivers based on the

DIGIT 2000 concept and having double-scan horizontal deflection. The VCU

2134 is a VLSI circuit in Cl technology, housed in a 40-pin Dil plastic

package. One single silicon chip combines the following functions and

circuit details (see Fig. 1):

— two input video amplifiers

— one A/D converter for the composite video signal

— the noise inverter

— one D/A converter for the luminance signal

— two D/A converters for the color difference signals

~ one RGB matrix for converting the color difference signals and the luminance signal into RGB signals

— three RGB output amplifiers

— programmable auxiliary circuits for blanking, brightness

adjustment and picture tube alignment

~ additional clamped

RGB inputs for text and other analog RGB signals

— programmable beam current limiting

1. Functional Description

The

VCU 2134 Video Codec Unit is intended for converting the analog

composite video signal from the video demodulator into a digital

signal. The latter is further processed digitally in the CVPU 2235 Video

Processor, in the PSP 2210 Progressive Scan Processor, and in the DPU

2554 Deflection Processor. After processing in the CVPU and the PSP

(color demodulation, comb filtering, line storage for double scanning

etc.), the PSP’s output signals (luminance and color difference) are

reconverted into analog signals in the VCU 2134. From these analog

signals are de- rived the RGB signals by means of the RGB matrix, and,

af- ter amplification in the internal RGB amplifiers, the RGB signals

drive the RGB output amplifiers of the color TV re- ceiver. In addition,

the VCU 2134 carries out the following functions:

— brightness adjustment

— automatic CRT spot-cutoff contro! (black level)

- white balance control and beam current limiting

Further,

the VCU 2134 offers direct inputs for text or other analog RGB signals

including adjustment of brightness and contrast for these signals. The

RGB matrix and RGB amplifier circuits integrated in the VCU 2134 are

analog. The CRT spot-cutoff control is carried out via the RGB

amplifiers’ bias, and the white balance control is accomplished by

varying the gain of these amplifiers. The VCU 2134 is clocked both by a

14 to 20.5 MHz clock signal and a 28 to 41 MHz clock signal supplied by

the MCU 2632 Clock Generator IC.

1.1. The A/D Converter with Input Amplifiers and Bit Enlargement The video signal is input to the VCU 2134 via pin 37 which is intended for normal TV video signal and for VCR or SCART video signal respectively. The video amplifier whose action is required, is activated by the CCU 2030, CCU 2050 or CCU 2070, via the IM bus by software (see Fig. 9). Video Amp | has the low gain (2 V video amplitude required), and Video Amp Il has the high gain (1 V video amplitude required). The amplification of both video amplifiers is doubled during the undelayed horizontal blanking pulse (at pin 36) in order to obtain a higher digital resolution of the color synchronization signal (burst). The A/D converter is of the flash type, a circuit of 2" comparators connected in parallel. This means that the number of comparators must be doubled if one additional bit is needed. Thus it is important to have as few bits as possible. For a slowly varying video signal, 8 bits are required. In order to achieve an 8-bit picture resolution

using a 7-bit converter, a trick is used: during every other line the reference voltage of the A/D converter is changed by an

amount corresponding to one half of the least significant bit. In this procedure, a grey value located between two 7-bit steps is converted to the next lower value during one line and to the next higher value during the next line. The two grey values on the screen are averaged by the viewer’s eye, thus producing the impression of grey values with 8-bit resolution. The A/D converter’s sampling frequency is 14 to 20.5 MHz, the clock being supplied by the MCU 2632 Clock Generator IC which is common to all circuits for the digital TV system. The converter’s resolution is 1/2 LSB of 8 bits. Its output signal is Gray-coded to eliminate spikes and glitches resulting from different comparator speeds or from the coder itself. The output is fed to the CVPU 2235 and to the DPU 2554 in parallel form.

1.2. The Noise Inverter

The

digitized composite video signal passes the noise inverter circuit

before it is put out to the CVPU and to the DPU 2554. The noise inverter

serves for suppressing bright spots on the screen which can be

generated by noise pulses, p. ex. produced by ignition sparks of cars

etc. The function of the noise inverter can be seen in Fig. 2.

The maximum white level corresponds with step 126 of the A/D converter’s output signal (that means a voltage of 7 V at pin 37 in the case Video Amp | being selected). If, due to an unwanted pulse on the composite video signal, the voltage reaches 7.5 V (what means step 127 in digital) or more, the signal level is reduced by such an amount, that a medium grey is obtained on the screen (about 40 IRE). The noise inverter circuit can be switched off by software (address 16 in the CVPU, see there). The luminance D/A converter is designed as an R-2R ladder network. It is clocked with the 28.6 MHz clock signal applied to pin 23. The cutoff frequency of the luminance signal is determined by the clock frequency.

1.3. The Luminance D/A Converter (Y)

After

having been processed in the CVPU 2235 (color demodulation, comb

filtering, etc.) and in the PSP 2210, the different parts of the

digitized video signal are fed back to the VCU 2134 for further

processing to drive the RGB out- put amplifiers. The luminance signal

(Y) is routed to the Y D/A converter in the VCU 2134 in the form of a

parallel 8- bit signal with a resolution of 1/2 LSB of 9 bits. This bit

range provides a sufficient signal range for contrast as well as

positive and negative overshoot caused by the peaking filter (see Data

Sheet CVPU).

1.4. The D/A Converters for the Color Difference Signals

R-Y

and B-Y In order to save input and output pins at the VCU 2134, CVPU

and PSP as well as connection lines, the two digital color difference

signals R-Y and B-Y are transferred in time muitiplex operation. This is

possible because these signals’ bandwidth is only 2 MHz and the clock

is a 28 to 41 MHz signal. The two 8-bit D/A converters R-Y and B-Y are

also built as R-2R ladder networks. They are clocked with % clock fre-

quency, but the clock for the multiplex data transfer is 28 to 41 MHz.

Four times 4 bits are transferred sequentially, giving a total of 16

bits. A sync signal coordinates the multi- plex operations in the VCU

2134, CVPU and PSP. Thus, only four lines are needed for 16 bits.

Fig. 4 shows the timing diagram of the data transfer described. To switch the CO input the VCU 2134 from chroma signal reception to sync signal reception, the information to do this is given by the PSP to pins 10 to 17 of the VCU in the shape of “zero luminance” during horizontal blanking time. To avoid mistakes, a limiter in the PSP ensures that no zero luminance is put out at other times.

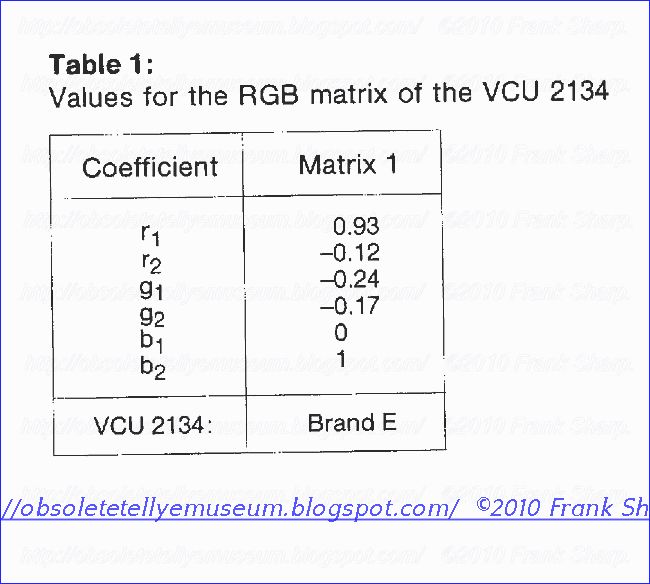

1.5. The RGB

Matrix

and the RGB Output Amplifiers In the RGB matrix, the signals Y, R-Y and

B-Y are dematrixed, the reduction coefficients of 0.88 and 0.49 being

tak- en into account. In addition, the matrix is supplied with a signal

produced by an 8-bit D/A converter for setting the brightness of the

picture. The brightness adjustment range corresponds to ‘2 of the

luminance signal range. It can be covered in 255 steps. The brightness

is set by commands fed from the CCU 2030, CCU 2050 or CCU 2070 Central

Control Unit to the CVPU via the IM bus. There is available one matrix,

called matrix 1, based on the formula: R = 1, + (RY) + 2° (BY) + Y G =

g,- (RY) + go: (BY) + Y B = b, - (R-Y) + bp - (BY) + Y

The three RGB

output amplifiers are impedance converters having a low output

impedance, an output voltage swing of 6 V (p-p), thereof 3 V for the

video part and 3 V for bright- ness and dark signal. The output current

is 4 mA.

Fig. 5 shows the recommended video output stage configuration. For the purpose of white-balance control, the amplification factor of each output amplifier can be varied stepwise in 127 steps (7 bits) by a factor of 1 to 2. Further, the CRT spot-cutoff control is accomplished via these amplifiers’ bi- as by adding the output signal of an 8-bit D/A converter to the intelligence signal. The amplitude of the output signal corresponds to one half of the luminance range. The eight bits make it possible to adjust the dark voltage in 0.5% steps. By means of this circuit, the factory-set values for the dark currents can be maintained and aging of the picture tube compensated.

1.6. The Beam Current and Peak Beam Current Limiter The principle of this circuitry may be explained by means of

Fig. 6. Both facilities are carried out via pin 38 of the VCU 2134. For beam current limiting and peak beam current limiting, contrast and brightness are reduced by reducing the reference voltages for the D/A converters Y, R-Y and B-Y. At a voltage of more than +4 V at pin 38, contrast and brightness are not affected. In the range of +4 Vto +3V, the contrast is continuously reduced. At +3 V, the original contrast is reduced to a programmable level, which is set by the bits of address 16 of the CVPU as shown in Table 2. A further decrease of the voltage merely reduces brightness, the contrast remains unchanged. At 2.5 V, the brightness is reduced to zero. At voltages lower than 2 V, the output goes to ultra black. This is provided for security purposes. The beam current limiting is sensed at the ground end of the EHT circuit, where the average value of the beam cur- rent produces a certain voltage

drop across a resistor inserted between EHT circuit and ground. The peak beam current limiting can be provided additionally to avoid “blooming” of white spots or letters on the screen. For this, a fast peak current limitation is needed which is sensed by three sensing transistors inserted between the RGB amplifiers and the cathodes of the picture tube. One of these three transistors is shown in Fig. 6. The sum of the picture tube’s three cathode currents produces a voltage drop across resistor R1. If this voltage exceeds that generated by the divider R2, R3 plus the base emitter voltage of T2, this transistor will be turned on and the voltage at pin 38 of the VCU 2134 sharply reduced. Time constants for both beam current limiting and peak beam current limiting can be set by the capacitors C1 and C2.

1.7. The Blanking

Circuit

The blanking circuit coordinates blanking during vertical and

horizontal flyback. During the latter, the VCU 2134's output amplifiers

are switched to “ultra black”. Such switching is different during

vertical flyback, however, be- cause at this time the measurements for

picture tube alignment are carried out. During vertical flyback, only

the cathode to be measured is switched to “black” during measuring time,

the other two are at ultra black so that only the dark current of one

cathode is measured at the same time. For measuring the leakage current,

all three cathodes are switched to ultra black. The sequence described

is controlled by three code bits contained in a train of 72 bits which

is transferred from the CVPU through PSP to the VCU 2134 during each

vertical blanking interval. This transfer starts with the vertical

blanking pulse. During the transfer all three cathodes of the picture

tube are biased to ultra black. In the same manner, the white-balance

control is done. The blanking circuit is controlled by two pulse

combinations supplied by the DPU 2554 Deflection Processor (“sandcastle

pulses”).

Pin 34 of the VCU 2134 receives the combined vertical blanking and delayed horizontal blanking pulse from pin 22 of the DPU (Fig. 7b), and pin 36 of the VCU gets the combined undelayed horizontal blanking and color key pulse from pin 19 of the DPU (Fig. 7a). The two outputs of the DPU are tristate controlled, supplying the output levels max. 0.4 V (low), min. 4.0 V (high), or high impedance, whereby the signal level in the high-impedance mode is determined by the VCU's input configuration, a voltage divider of 3.6 kQ and 4.7 kQ between the +5 V supply and ground, to 2.8 V. The VCU’s input amplifier has two thresholds of 2.0 V and 3.4 V for detecting the three levels of the combined pulses. In this way, two times two pulses are transferred via only two lines.

1.8. The Circuitry for Picture Tube Alignment

During

vertical flyback, a number of measurements are taken and data is

exchanged between the VCU 2134, the CVPU via PSP and the CCU. This

measurements deal with picture tube alignment, as white level and dark

current adjustment, and with the photo current supplied by a photo

resistor which serves for adapting the contrast of the picture to the

light in the room where the TV set is operated (the latter feature only

in connection with the CVPU 2235, see Fig. 5). The circuitry for

transferring the picture tube alignment data, the sensed beam currents

and the photo current is clocked in compliance with the PSP 2210 by the

vertical blanking pulse and the color key pulse.

To carry out the measurements, a quadruple cycle is provided (see Table 3). The timing of the data transfer during the vertical flyback is shown in Fig. 8, and Fig. 9 shows the data sequence during that data transfer.

A) Video signal during vertical flyback, lines No. 1 to 22.

B) Vertical blanking pulse supplied by pin 22 of the DPU 2554 to pin 34 of the VCU 2134 (tgp), duration is 13 lines and delay with respect to the start of line 4 is tyg = 23 us. With this pulse starts the 72-bit data transfer described in section 1.7., and with the end of pulse starts the picture tube’s cathode current measurement.

C) Internal control pulse for CRT current measurement, generated simultaneously in VCU 2134 and CVPU. The cathode under test is set to black by code bits.

D) Internal control pulse generated in VCU 2134 (pulse B + pulse C). During this pulse the cathodes of the CRT are at ultra black, the D/A converters for chroma and brightness are set to zero output, and Teletext fast blanking is off.

E) Control pulse generated in CVPU and VCU 2134 for CRT spot-cutoff current sensing. During this time, the measured output is set to black level. E’) Control pulse generated in VCU 2134. During this pulse, the output of the Y D/A converter delivers the white- current measuring level. This is achieved by switchi ng off the clock for the D/A converter.

F) Control pulse generated in VPU and VCU for white cur- rent sensing. During this time, the measured output is set to white current measuring level. F’) Control pulse generated in VCU 2134 which sets the Y D/A converter to zero output by setting its reference voltage to zero.

G) Window pulse for 72-bit data transfer from CVPU to VCU as described in section 1.7., duration 4 lines, generated in VCU 2134. The end of this pulse starts the clock hold-off time for the Y D/A converter (diagram E’).

H) Signal at the CO/Msync output of the PSP supplied to the CO/Msync input of the VCU 2134 (pin 21). Normally, via this connection are transferred chroma data and the sync signal. With the begin of the vertical blanking, chroma data transfer is interrupted to enable the trans- fer of 72 clock pulses for 72-bit data transfer.

1) Window pulse for 72-bit data transfer, generated in CVPU, duration 6 lines. The end of this pulse enables Y and chroma data output from CVPU to VCU.

J) Signals at the LO to L7 outputs of the PSP supplied to the LO to L7 inputs (pins 10 to 17) of the VCU 2134. With the begin of vertical blanking, luma data transfer is interrupted and the luminance output of the CVPU supplies white-current measuring level during lines 19 and 20 (see diagram F).

Fig. 9:

Data sequence during the transfer of test results from the CVPU to the VCU 2134. Nine Bytes are transferred, in each case the MSB first. These 9 Bytes, 8 bits each, coincide with the 72 pulses of 4.4 MHz that are transferred during vertical flyback from pin 8 of the PSP to pin 21 of the VCU 2134 (see Fig. 8). ! and m: beam current limiter range k: noise inverter on/off n: video input amplifier switching bit n=0 means Video Amp | selected (input amplitude 2 V) n= 1 means Video Amp II selected (input amplitude 1 V) : clamping mode: S=0 means clamping by color key pulse at pin 36 S=1 means clamping by additional pulse (Fig. 10) R, G, B: code bits p= 1: no doubled gain in the input amplifier during horizon- tal blanking (see section 1.1.) q=1: no changing of the A/D converter’s reference voltage during every other line (see section 1.1.)

1.9. The Analog RGB Inputs

The

three additional analog RGB inputs are provided for inputting text or

other analog RGB signals. They are connected to fast voltage-to-current

converters whose output current can be altered in 64 steps (6 bits) for

contrast set- ting between 100 % and 30 %. The three inputs are clamped

to a DC black level which corresponds to the level of 31 steps in the

luminance channel, by means of either the color key pulse or an

additional pulse provided by a modified fast switching input. The mode

is selected by the shift register (Fig. 9). So, the same brightness

level is achieved for normal and for external RGB signals. The output

currents of the converters are then fed to the three RGB output

amplifiers. Switchover to the external video signal is also fast.

The present invention relates to a set of three or more integrated circuits for digital video signal processing in color-television receivers as is set forth in the preamble of claim 1. An IC set of this kind is described in a publication by INTERMETALL entitled "Eine neue Dimension-VLSI-Digital-TV-System", Freiburg im Breisgau, September 1981, on pages 6 to 11 (see also the corresponding English edition entitled "A new dimension-VLSI Digital TV System", also dated September 1981).

The first integrated circuit, designated in the above-mentioned publications by "MAA 2200" and called "Video Processor Unit" (VPU), includes an analog-to-digital converter followed by a first serial-data-bus interface circuit which, in turn, is followed by a first multiplexer. During the vertical blanking interval, the analog-to-digital converter is fed, via a second multiplexer, with measured data corresponding to the cathode currents of the picture tube flowing at "black" (="dark current") and "white" ("white level") in each of the three electron guns, and with the signal of an ambient-light detector. The processed digital chrominance signals are applied to the first multiplexer.

The second integrated circuit, designated by "MAA 2000" and called "central control unit" (CCU) in the above publications, contains a microprocessor, an electrically reprogrammable memory, and a second serial-data-bus interface circuit. The memory holds alignment data and nominal dark-current/white-level data entered by the manufacturer of the color-television receiver. From these data and the measured data, the microprocessor derives video-signal-independent operating data for the picture tube.

The third integrated circuit, designated by "MAA 2100" and called "video-codec unit" (VCU) in the above publications, includes a demultiplexer, an analog RGB matrix, and three analog amplifiers each designed to drive one of the electron guns via an external video output stage. After digital-to-analog conversion, the dark current of the picture tube is adjusted via the operating point of the respective analog amplifier, and the white level of the picture tube is adjusted by adjusting the gain of the respective analog amplifier. The demultiplexer is connected to the first multiplexer of the first integrated circuit via a chroma bus.

As to the prior art concerning such digital color-television receiver systems, reference is also made to the journal "Elektronik", Aug. 14, 1981 (No. 16), pages 27 to 35, and the journal "Electronics", Aug. 11, 1981, pages 97 to 103.

During the further development of the prior art system following the above-mentioned publication dates, the developers were faced with the problem of how to accomplish the dark-current/white-level control of the picture tube within the existing system, particularly with respect to measured-data acquisition and transfer and to the transfer of the operating data to the picture tube.

Another requirement imposed during the further development of the prior art system was that the leakage currents of the electron guns of the picture tube be measured and processed within the existing system. The solution of these problems is to take into account the requirement that the number of external terminals of the individual integrated circuits be kept to a minimum.

The object of the invention as claimed is to solve the problems pointed out. The essential principles of the solution, which directly give the advantages of the invention, are, on the one hand, the division of the measurement to four successive vertical blanking intervals and, on the other hand, the utilization of one wire of the chroma bus at the beginning of the next vertical blanking interval as well as the measurement of the ambient light by means of the light detector and the measurement of the leakage currents during a single vertical blanking interval.

The invention will now be explained in more detail with reference to the accompanying drawing, which is a block diagram of one embodiment of the IC set in accordance with the invention. It shows the first, second, and third integrated circuits ic1, ic2, and ic3, which are drawn as rectangles bordered by heavy lines. The first integrated circuit ic1 includes the analog-to-digital converter ad, which converts the measured dark-current, white-level, ambient-light, and leakage-current data into digital signals, which are fed to the first bus interface circuit if1. The latter is connected via the line db to the first multiplexer mx1, which interleaves data from the first bus interface circuit if1 with digital chrominance signals cs produced in the first integrated circuit ic1, and places the interleaved signals on the chroma bus cb. The generation of the digital chrominance signals cs is outside the scope of the present invention and is disclosed in the references cited above.

The first integrated circuit ic1 further includes the second multiplexer mx2, which consists of the three electronic switches s1, s2, s3, and represents a subcircuit which is essential for the invention. The input of the first switch s1 is grounded through the first resistor r1, and connected to the collectors of the external transistors tr, tg, tb, each of which is associated with one of the electron guns. Via the base-emitter paths of these transistors, the cathodes of the three electron guns are driven by the video output stages ve. The final letters r, g, and b in the reference characters tr, tg, and tb and in the reference characters explained later indicate the assignment to the electron gun for RED (r), GREEN (g), and BLUE (b), respectively. The output of the first switch s1 is connected to the input of the analog-to-digital converter ad.

The input of the second switch s2 is connected to the light detector ls, which has its other terminal connected to a fixed voltage u and combines with the grounded resistor r3 to form a voltage divider. The input of the second switch s2 is thus connected to the tap of this voltage divider, while the output of this switch, too, is coupled to the input of the analog-to-digital converter ad.

The input of the third switch s3 is connected to the input of the first switch s1 via the second resistor r2, while the output of the third switch s3 is grounded. The value of the resistor r1 is about one order of magnitude greater than that of the resistor r2.

For the whole duration of the picture shown on the screen of the picture tube b, and throughout the vertical sweep, the first switch s1 and the third switch s3 are closed, and the second switch s2 is open. During the vertical retrace interval, for the white-level measurement, the switches s1, s3 are closed, and the switch s2 is open; for the dark-current measurement and the leakage-current measurement, the switch s1 is closed, and the switches s2, s3 are open, and for the light-detector-current measurement, the switches s2, s3 are closed, and the switch s1 is open.

The measurements of the dark current and the white level of each electron gun and the measurements of the light-detector current and the leakage currents are made in four successive vertical blanking intervals. One end of the respective cathode is connected to a voltage us for blacker-than-black, and the other end is connected to a voltage ud for black and then to a voltage uw for white, in accordance with the following table:

| ______________________________________ |

| Measurement in the first at about the Vertical half of the end of the blanking vertical vertical interval blanking blanking Cathode No. interval interval red green blue |

| ______________________________________ |

1 Leakage cur- Light-detect- us us us rents of the or current cathodes 2 Dark current White level ud/uw us us red red 3 Dark current White level us ud/uw us green green 4 Dark current White level us us ud/uw blue blue |

| ______________________________________ |

The voltage ud for black is, as usual, a voltage which just causes no brightness on the screen of the picture tube b, i.e., a voltage just below the dark threshold of the picture tube. The voltage us for blacker-than-block is then a cathode voltage lying further in the black direction than the voltage for black. The voltage for white is the voltage for the screen brightness to be measured; the brightness of the screen is generally below the maximum permissible value.

Thus, two measurements are made during each vertical blanking interval, namely one in the first half, preferably at one-third of the pulse duration of the vertical blanking interval, and the other at about the end of the first half. During the four successive vertical blanking intervals, the first measurement determines the leakage currents of the cathodes and the dark currents for red, green, and blue. The second measurements determine the light-detector current and the white levels for red, green, and blue. During the measurement of the cathode leakage currents and the light-detector current, all three cathodes are at the voltage us. During the measurements of the dark current and the white level of the respective cathode, the latter is connected to the respective dark-current cathode voltage ud and white-level cathode voltage uw, respectively, while the cathodes of the two other electron guns, which are not being measured, are at the voltage us.

The second integrated circuit circuit ic2 contains the microprocessor mp, the electrically reprogrammable memory ps, and the second bus interface circuit if2, which is associated with the serial data bus sb in this integrated circuit and also connects the microprocessor mp and the memory ps with one another and with itself. The memory ps holds alignment data and nominal dark-current/white-value data of the picture tube used, which were entered by the manufacturer. From this alignment and nominal data and from the measured data obtained via the second multiplexer mx2 and the analog-to-digital converter ad of the first integrated circuit ic1, the microprocessor mp derives video-signal-independent operating data for the picture tube.

The derivation of these operating data is also outside the scope of the invention; it should only be mentioned that with respect to the operating data of the picture tube, the microprocessor performs a control function in accordance with a predetermined control characteristic.

The third integrated circuit ic3 includes the demultiplexer dx, which is connected to the first multiplexer mx1 of the first integrated circuit ic1 via the chroma bus cb and separates the chrominance signals cs and the operating data of the picture tube from the interleaved signals transferred over the chroma bus. While the transfer of measured data from the analog-to-digital converter ad to the microprocessor mp of the second integrated circuit ic2 takes place via the two interface circuits if1, if2 and the data bus sb at an appropriate instant, the video-signal-independent operating data for the picture tube b, which are derived by the microprocessor mp, are transferred from the second integrated circuit ic2 via the two interface circuits if1, if2 and the line db to the first multiplexer mx1 at an appropriate instant, and from the first multiplexer mx1 over a wire of the chroma bus cb into the shift register sr of the third integrated circuit ic3 shortly after the beginning of the next vertical blanking interval. To accomplish this, the first interface circuit if1 also includes a shift register from which the operating data are read serially.

During this data transfer into the shift register sr, the cathodes of the picture tube b are preferably at the voltage us in order that this data transfer does not become visible on the screen.

The appropriate instant for the transfer of measured data to the microprocessor mp is determined by the latter itself, i.e., depending on the program being executed in the microprocessor, and on the time needed therefor, the measured data are called for from the interface circuits not at the time of measurement but at a selectable instant within the working program of the microprocessor mp. If the measurement currently being performed should not yet be finished at the instant at which the measured data are called for, in a preferred embodiment of the invention, the stored data of the previous measurement will be transferred to the microprocessor mp.

As mentioned previously, the operating data for the picture tube b are transferred into the shift register sr at the beginning of a vertical blanking interval. The parallel outputs of this shift register are combined in groups each assigned to one operating value, and each group has one of the digital-to-analog converters dh, ddr, ddg, ddb, dwr, dwg, dwb associated with it. In the figure, the division of the shift register into groups is indicated by broken lines. The shift register sr performs a serial-to-parallel conversion in the usual manner, and the operating data are entered by the demultiplexer dx into the shift register in serial form and are then available at the parallel outputs of the shift register.

The digital-to-analog converter dh provides the analog brightness control signal, which is applied to the RGB matrix m in the integrated circuit ic3. Also applied to the RGB matrix m are the analog color-difference signals r-y, b-y and the luminance signal y. The formation of these signals is outside the scope of the invention and is known per se from the publications cited at the beginning.

The three analog-to-digital converters ddr, ddg, ddb provide the dark-current-adjusting signals for the three cathodes, which are currents and are applied to the inverting inputs--of the analog amplifiers vr, vg, vb. Also connected to these inputs is a resistor network which is adjustable in steps in response to the digital white-level-adjusting signals at the respective group outputs of the shift register sr. The resistors serve as digital-to-analog converters dwr, dwg, dwb and establish the connection between the inverting inputs--and the outputs of the analog amplifiers vr, vg, vb.

In an arrangement according to the invention which has proved good in practice, each of the three dark-current-adjusting signals is a seven-digit signal, and each of the three white-level-adjusting signals and the brightness control signal are five-digit signals. The voltages us and ud/uw of the three cathodes are assigned a three-digit identification signal in accordance with the above table, which signal is also fed into the shift register sr in the implemented circuit. Finally, a three-digit contrast control signal is provided in the implemented circuit for the Teletext mode of the color-television receiver. These nine data blocks are transferred in the implemented circuit from the demultiplexer dx to the shift register sr in the following order, with the least significant bit transmitted first, and with the specified number of blanks: identification signal, white-level signal blue, three blanks, white-level signal green, three blanks, white-level signal red, one blank, dark-current signal blue, one blank, dark-current signal green, one blank, dark-current signal red, contrast signal Teletext, and brightness control signal. These are seven eight-digit data blocks which are assigned to 56 pulses of a 4.4-MHz clock frequency, which is the frequency of the shift clock signal of the shift register sr.

It should be noted that the data sequence just described does not correspond to the order of the groups of the shift register sr in the figure. The order in the figure was chosen only for the sake of clarity.

The outputs of the three analog amplifiers vr, vg, vb are coupled to the inputs of the video output stage ve, whose outputs, as explained previously, are connected to the bases of the transistors pr, tg, td, so that the cathodes of the picture tube b are driven via the base-emitter paths of these transistors.

In another preferred embodiment of the invention, the measurement performed during a vertical blanking interval is not enabled until the data of the previous measurement has been transferred into the microprocessor mp. In this manner, no measurement will be left out.

It is also possible to omit the digital-to-analog converter dh if the analog RGB matrix m is replaced with a digital one.

One advantage of the invention is that the use of the chroma bus for the transfer of operating data facilitates the implementation of the third integrated circuit ic3 using bipolar technology, because an additional bus interface circuit, which could be used there, would occupy too much chip area.

VCU 2136

The VCU 2136 and VPU 2204 represent further developments of the VCU 2133 and VPU 2203 that are suitable for S-VHS. This application note describes the modifications that were necessitated for these ICs by the S-VHS. lt should be read as an addendum to data sheets VCU 2133/5E and VPU 2203/1E. Some improvements have been made in the luminance filters to get better frequency response and therefore better picture quality. See the part "New filters” in VPU 2204. With S-VHS the luma and chroma information is transmitted in parallel channels. The luma and chroma data are converted by the VCU 2136 A/D converter and are transmitted in the time multiplex via the digital bus. It is important that a corresponding demultiplex takes place in the PVPU and that the SPU 2223 is able to separate the chroma information from the multiplexed data. Furthermore, the DTI 2223 is able to compensate group delay difference between the luma and chroma data.

Fig. 1 illustrates the timing

of the data: the analog signals at the inputs V1 at pin 35 and V2 at pin 37 of the VCU 2136 are taken over in time multiplex and an A/D conversion is performed. As the timing diagram (fig. 1) shows, the data 1 (luma in S-VHS operation) are taken over with the rising edge and the data 2 with the falling edge of the clock signal. The data rate is doubled in comparison to the VCU 2133 (Double Data Stream DDS).

Changes from the VCU 2133 to the VCU 2136: With the help of two control bits, three possible VCU operation modes "Composite Video”, "VHS” and "S-VHS” can be set. First, these two bits are entered into register 16 of the VPU 2204 by the CCU. During the vertical blanking interval this information is passed on from the VPU to the VCU inside the 72 bit data stream. Composite Video, VHS and S-VHS operation mode of the VCU only differ in the setting of the input operation multipliers 1 and 2 (see fig. 2). The function of the input multiplexer remains unchanged. The following constellations are possible. Refer to the VPU 2203/1E data sheet, table 3: "Data transfer between Address no. 16, high byte, bit 6=1, Address no. 16, high byte, bit 5=0 "S-VHS mode” Pin 35: Analog Luma, 2.0V max. 1 V input is also possible if high byte bit 5 = 1 in address 16 Pin 37: Analog Chroma, 0.3V max. for burst. Address no. 16, high byte, bit 6=0, Address no. 16, high byte, bit 5=0: "Composite Video” mode Amplification during color

burst key x 2 Pin 35: Analog Composite Video, 2.0V max. Pin 37: Analog Composite Video, 2.0V max. only the data on pin 35 is processed in this mode.

Address no. 16, high byte, bit 6=0 Address no. 16, high byte, bit 5=1: "VHS" mode. Amplification during color burst key x 2 Pin 35: Analog Composite Video, 1.0V max. Pin 37: Analog Composite Video, 1.0V max. Only the data on pin 37 is processed in this mode. Note: The VCU 2136 does not contain the noise inverter that was incorporated in the VCU 2133 any longer. Address no. 16, high byte bit 6 is the former bit "noise inverter”. Changes from the VPU 2203 to the VPU 2204: - on the input side, a demultiplexer was inserted to separate the luma and chroma data in the double data stream and to distribute them into the luma and chroma channels of the VPU (see fig. 3). — the colour trap was conceived to be switched off for the S-VHS operation mode. — Two additional control bits were introduced (refer to the VPU 2203/1E data sheet table 3: "Data transfer between ...”), that is: Address no. 15, low byte, bit 2 "S-VHS on” (see fig. 2): bit 2=0: S-VHS off VPU works on the V1 data only. Luma and chroma data are

separated with the help of chroma trap and chroma filter. bit 2=1: S-VHS on demultiplex of the sequential luma and chroma data, no chroma x 2 during color burst. Address no. 15., low byte, bit 1 (see fig. 3): bit 1=0: chroma trap on. bit 1=1: chroma trap off. New filters in the VPU 2204 To improve frequency response and picture quality some changes in the luminance- and peaking filter part of the VPU have been made. The old filter characteristics are still available. New features are: the S-VHS characteristics without chroma trap the “enhanced” Munakami filter without ringing the “broad” version. For SECAM the broader chroma trap can be switched off to the same chroma trap as for PAL.

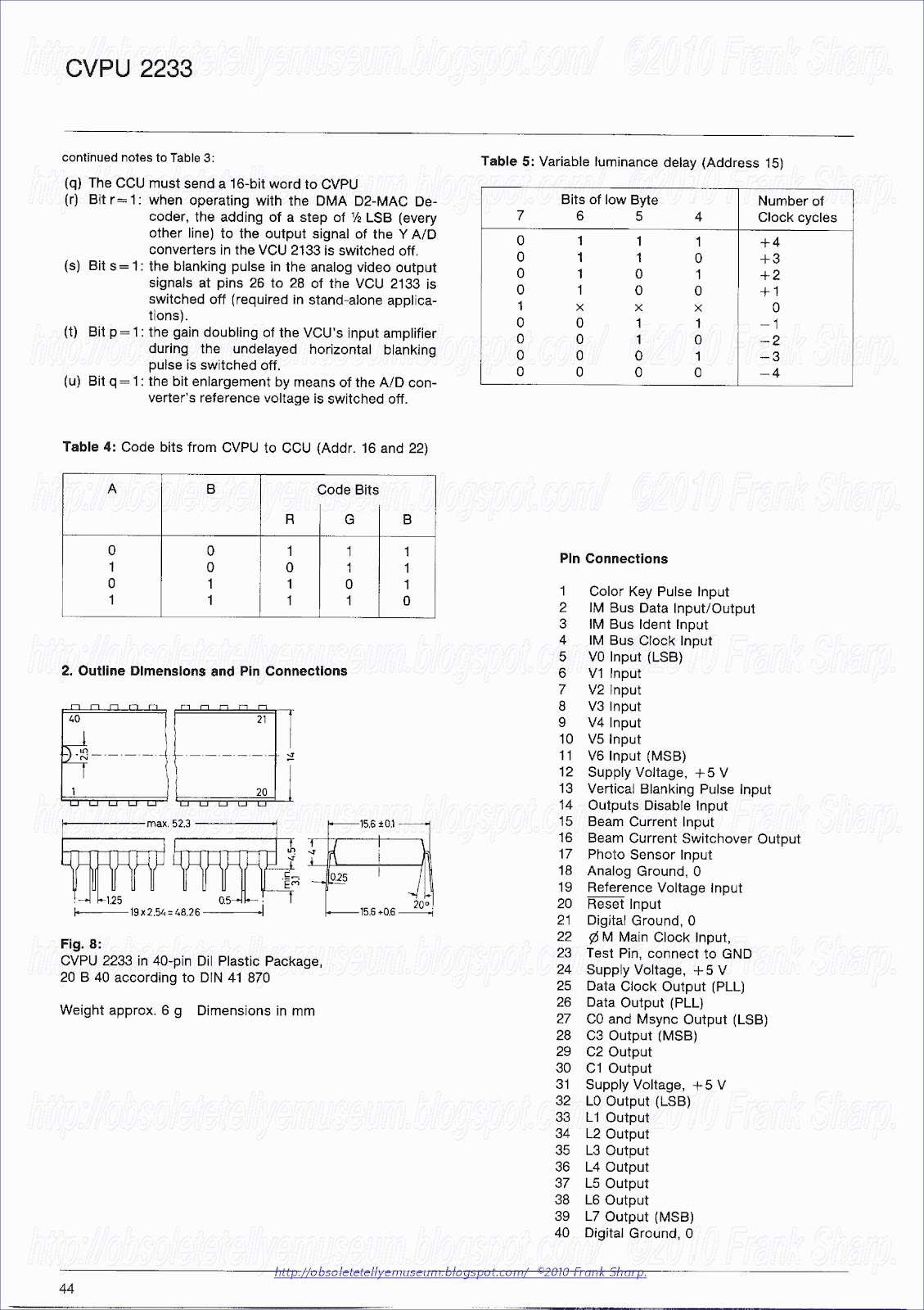

DPU 2553, DPU 2554, DPU 2555 Deflection Processors.

During the past few years, digital circuit technology has come into se in television receivers, including color television receivers, for processing the received signal and for generating the deflection signal required to control the movement of the electron beam. During the research for and the development and implementation of these digital circuit systems, the course traced ou by conventional analog signal processing was followed, and the known individual problems were solved by means of digital rather than analog circuits.

By contrast, the present invention is predicated on the realization that, against the background of digital signal processing in television receivers, the constraints resulting from conventional analog technology, particularly with respect to predetermined signal waveforms, can be eliminated, thus making it possible to cope with difficult problems better than with conventional analog and/or digital technology. One of those difficult problems is still the geometric distortions introducted by the nonspherical curvature of the tube screen during reproduction. To eliminate these distortions, a considerable amount of circuitry is required both with conventional analog technology and more recent digital technology; an example is the great number of pincushion-correcting circuits.The fundamental idea of the invention as claimed is to abandon the rigid dependence on the commonly used sawtooth signal for ohorizontal deflection and vertical deflection, which both have a very short retrace period in comparison with the trace period, and to make the individual pixels of the video signal visible on the screen when the two deflection signals have moved the electron beam to the point intended on the transmitter side.

In the present invention, therefore, the deflection signals are no longer generated by a sawtooth generator of long-known analog or more recent digital design, but a deflection processor is provided which generates horizontal and vertical deflection signals with freely selectable waveforms.

The video signal, after being digitized by means of a clock signal, is written into a random-access memory and is read ou in such a way that the individual pixels occupy the intended positions on the screen. The memory has a suitable controller associated therewith, of course. The digital signals read out of the memory must be applied to a compensating stage for correcting picture tube errors before they drive the picture tube via digital-to-analog converters.

Deflection Processors

1.

Introduction These programmable VLSI circuits in N-channel MOS

technology carry out the deflection functions in digital color TV