Was featuring the PHILIPS 20AX CRT TUBE FAMILY. (A56-510X)

This version was featuring first time A frequency synthesized tuning system based around PHILIPS TRD chipset. (SAB2024 SAB2022 SAB1016 SAB2015 SAB3012)

SAB2015 Station search + RAM

SAB2022 TV AFT (AUTOMATIC FINE TUNING)

SAB2024 TV PLL TUNING

SAB1016 TV CHARACTER FADE IN (OSD)

SAB 3012 US/IF/REC 2X64 CODES REMOTE RECEIVER.

The present invention relates to a television set which includes a picture display device, an alpha numerical character generating circuit connected to the said device, a control device and means for checking analogue data relating to the operation of the set, such as volume, brightness and color. The system commonly used on television receivers for tuning into the required channels is the so-called FREQUENCY SYNTHESIZER system. This system, made possible by the advent of integrated circuits, offers a number of advantages over other known systems, such as the conventional potentiometer type MECHANICAL MEMORY systems and the more recent so-called VOLTAGE SYNTHESIZER systems. The frequency synthesizer system is fully electronic enabling any channel to be called up directly by the user who formulates the channel number on a keyboard or other control device. The system usually consists of a quartz-controlled reference oscillator, a phase lock loop, a programmable divider and a computer which supplies the number to be sent to the programmable divider in response to the number of the channel set by the user. Thanks to the phase lock loop, for each channel number set by the user, the frequency of the local oscillator on the set is kept so stable and accurate that the set is tuned with great precision to the corresponding channel signal.

For further details concerning frequency synthesizer tuning systems, refer to the article entitled "A Frequency Synthesizer for Television Receivers" by E. G. Breeze, published in the November, 1974 issue of the "Transactions BTR" Magazine, or "Digital Television Tuner Uses MOS LSI and Non Volatile Memory" by L. Penner, published in the April 1, 1976 issue of "Electronics".

Channel selection is controlled by a frequency synthesizer a sweep of available channels is made by a channel selecting arrangement and this sweep is arranged to be stopped when a signal is received. When the sweeping is stopped a fine tuning arrangement takes control to respond to the frequency of the received signal and to compensate for any drift of that signal.

According to this invention there is provided a receiver comprising frequency synthesizer controlled channel selection means which includes a fine tuning arrangement; means for initiating a sweep of available channels by the channel selection means; means for stopping the sweep on reception of a signal and means, operable on cessation of sweeping and responsive to the frequency of the signal, and arranged to control the fine tuning arrangement to compensate for frequency drift of the signal.

The receiver may be in the form of a television receiver.

The means operable a cessation of sweeping may comprise level detector means arranged to receive a signal whose level is representative of the frequency of the received signal and to provide an output signal when a predetermined frequency drift is detected.

In a preferred form two level comparators are provided each arranged to receive the frequency representative signal and a respective reference level and to provide an output respectively representative of an upward and downward frequency drift exceeding predetermined limits.

The signal whose level is representative of the frequency of the received signal may be provided by automatic frequency control (A.F.C.) means conveniently in the form of an A.F.C. discriminator.

The means operable or cessation of sweeping may be arranged to control the fine tuning arrangement via a signal path which includes means for blocking said signal path until the said signal is received.

The means for blocking may be in the form of gate means connected to the said signal path and arranged to receive a second input a signal indicative of the receipt of the said signal.

The means for initiating a sweep may comprise an operator control coupled to control input means of the channel selection means, and the means for stopping sweeping is operative to isolate the operator control from the said control input means.

The operator may be coupled to the channel selection means via gating means operative to open an operation of the operator control and the means for stopping sweeping may provide a signal operative to block the gating means or receipt of the said signal.

The means for stopping sweeping may include means for detecting the reception of the said signal which in a preferred form of television receiver comprises a sync comparator operative to compare video signals with line flyback signals and to provide an output signal whose level is indicitive of the reception of the said signal.

The frequency synthesizer system lends itself well to a number of different modes of television channel tuning;

direct selection by formulating the required channel number as described above television channels are numbered: for example, in the European C.C.I.R. standard, V.H.F. band channels are numbered from 2 to 12 and U.H.F. band channels from 21 to 69; in the American Standard, VHF channels are numbered from 2 to 13 and UHF from 14 to 83).

memory selection: each of a certain set of keys corresponds to a preselected and memorised channel;

automatic scanning of all the channels of a given standard, or of all the channels contained in the memory or continuous scanning of all the frequency bands involved.

The first application enables immediate, direct selection of any one of the channels in the relative standard (60 in Europe, 82 in America).

the second enables faster detection of one of a limited number of preferred channels.

The third is a fast, simple way of finding out which standard channels can be received, which channels have been memorised and whether other broadcasting stations exist on non-standard frequencies such as the private broadcasting stations in Italy (there are currently over a hundred operating).

Line synch Switched Mode Power Supply with Line deflection output Transistor Drive Circuit:

A stabilized supply voltage circuit for a picture display device comprising a chopper wherein the switching signal has the line frequency and is duration-modulated. The coil of the chopper constitutes the primary winding of a transformer a secondary winding of which drives the line output transistor so that the switching transistor of the chopper also functions as a driver for the line output stage. The oscillator generating the switching signal may be the line oscillator. In a special embodiment the driver and line output transistor conduct simultaneously and in order to limit the base current of the line output transistor a coil shunted by a diode is incorporated in the drive line of the line output transistor. Other secondary windings of the transformer drive diodes which conduct simultaneously with the efficiency diode of the chopper so as to generate further stabilized supply voltages.

Description:

Such a circuit arrangement is known from German "Auslegeschrift" 1.293.304. wherein a circuit arrangement is described which has for its object to convert an input direct voltage which is generated between two terminals into a different direct voltage. The circuit emp

loys a switch connected to the first terminal of the input voltage and periodically opens and closes so that the input voltage is converted into a pulsatory voltage. This pulsatory voltage is then applied to a coil. A diode is arranged between the junction of the switch and the coil and the second terminal of the input voltage whilst a load and a charge capacitor in parallel thereto are arranged between the other end of the coil and the second terminal of the input voltage. The assembly operates in accordance with the known efficiency principle i.e., the current supplied to the load flows alternately through the switch and through the diode. The function of the switch is performed by a switching transistor which is driven by a periodical pulsatory voltage which saturates this transistor for a given part of the period. Such a configuration is known under different names in the

literature; it will be referred to herein as a "chopper." A known advantage thereof, is that the switching transistor must be able to stand a high voltage or provide a great current but it need not dissipate a great power. The output voltage of the chopper is compared with a constant reference voltage. If the output voltage attempts to vary because the input voltage and/or the load varies, a voltage causing a duration modulation of the pulses is produced at the output of the comparison arrangement. As a result the quantity of the energy stored in the coil varies and the output voltage is maintained constant. In the German "Auslegeschrift" referred to it is therefore an object to provide a stabilized supply

voltage device.

In the circuit arrangement according to the mentioned German "Auslegeschrift" the frequency of the load variations or a harmonic thereof is chosen as the frequency for the switching voltage. Particularly when the load fed by the chopper is the line deflection circuit of a picture display device, wherein thus the impedance of the load varies in the rhythm of the line frequency, the frequency of the switching voltage is equal to or is a multiple of the line frequency.

In the circuit arrangement according to the mentioned German "Auslegeschrift" the frequency of the load variations or a harmonic thereof is chosen as the frequency for the switching voltage. Particularly when the load fed by the chopper is the line deflection circuit of a picture display device, wherein thus the impedance of the load varies in the rhythm of the line frequency, the frequency of the switching voltage is equal to or is a multiple of the line frequency.It is to be noted that the chopper need not necessarily be formed as that in the mentioned German "Auslegeschrift." In fact, it is known from literature that the efficiency diode and the coil may be exchanged. It is alternatively possible for the coil to be provided at the first terminal of the input voltage whilst the switching transistor is arranged between the other end and the second terminal of the input voltage. The efficiency diode is then provided between the junction of said end and the switching transistor and the load. It may be recognized that for all these modifications a voltage is present across the connections of the coil which voltage has the same frequency and the same shape as the pulsatory switching voltage. The control voltage of a line deflection circuit is a pulsatory voltage which causes the line output transistor to be saturates and cut off alter

nately. The invention is based on the recognition that the voltage present across the connections of the coil is suitable to function as such a control voltage and that the coil constitutes the primary of a transformer. To this end the circuit arrangement according to the invention is characterized in that a secondary winding of the transformer drives the switching element which applies a line deflection current to line deflection coils and by which the voltage for the final anode of a picture display tube which forms part of the picture display device is generated, and that the ratio between the period during which the switching transistor is saturated and the entire period, i.e., the switching transistor duty cycle is between 0.3 and 0.7 during normal operation.

nately. The invention is based on the recognition that the voltage present across the connections of the coil is suitable to function as such a control voltage and that the coil constitutes the primary of a transformer. To this end the circuit arrangement according to the invention is characterized in that a secondary winding of the transformer drives the switching element which applies a line deflection current to line deflection coils and by which the voltage for the final anode of a picture display tube which forms part of the picture display device is generated, and that the ratio between the period during which the switching transistor is saturated and the entire period, i.e., the switching transistor duty cycle is between 0.3 and 0.7 during normal operation.The invention is also based on the recognition that the duration modulation which is necessary to stabilize the supply voltage with the switching transistor does not exert influence on the driving of the line output transistor. This resides in the fact that in case of a longer or shorter cut-off period of the line output transistor the current flowing through the line deflection coils thereof is not influenced because of the efficiency diode current and transistor current are taken over or, in case of a special kind of transistor, the collector-emitter current is taken over by the base collector current and conversely. However, in that case the above-mentioned ratios of 0.3 : 0.7 should be taken into account since otherwise this take-over principle is jeopardized.

As will be further explained the use of the switching transistor as a driver for the line output transistor in an embodiment to be especially described hereinafter has the further advantage that the line output transistor automatically becomes non-conductive when this switching transistor is short circuited so that the deflection and the EHT for the display tube drop out and thus avoid damage thereof.

Due to the step according to the invention the switching transistor in the stabilized supply functions as a driver for the line deflection circuit. The circuit arrangement according to the invention may in addition be equipped with a very efficient safety circuit so that the reliability is considerably enhanced, which is described in the U.S. Pat. No. 3,629,686. The invention is

furthermore based on the recognition of the fact that the pulsatory voltage present across the connections of the coil is furthermore used and to this end the circuit arrangement according to the invention is characterized in that secondary windings of the transformer drive diodes which conduct simultaneously with the efficiency diode so as to generate further stabilized direct voltages, one end of said diodes being connected to ground.

In order that the invention may be readily carried into effect, a few embodiments thereof will now be described in detail by way of example with reference to the accompanying diagrammatic drawings in which:

FIG. 1 shows a principle circuit diagram wherein the chopper and the line deflection circuit are further shown but other circuits are not further shown.

FIGS. 2a, 2b and 2c show the variation as a function of time of two currents and of a voltage occurring in the circuit arrangement according to FIG. 1.

FIGS. 3a 3b, 3c and 3d show other embodiments of the chopper.

FIGS. 4a and 4b show modifications of part of the circuit arrangement of FIG. 1.

In FIG. 1 the reference numeral 1 denotes a rectifier circuit which converts the mains voltage supplied thereto into a non-stabilized direct voltage. The collector of a switching transistor 2 is connected to one of the two terminals between which this direct voltage is obtained, said transistor being of the npn-type in this embodiment and the base of which receives a pulsatory voltage which originates through a control stage 4 from a modulator 5 and causes transistor 2 to be saturated and cut off alternately. The voltage waveform 3 is produced at the emitter of transistor 2. In order to maintain the output voltage of the circuit arrangement constant, the duration of the pulses provided is varied in modulator 5. A pulse oscillator 6 supplies the pulsatory voltage to modulator 5 and is synchronized by a signal of line frequency which originates from the line oscillator 6' present in the picture display device. This line oscillator 6' is in turn directly synchronized in known manner by pulses 7' of line frequency which are present in the device and originate for example from a received television signal if the picture display device is a television receiver. Pulse oscillator 6 thus generates a pulsatory voltage the repetition frequency of which is the line frequency.

In FIG. 1 the reference numeral 1 denotes a rectifier circuit which converts the mains voltage supplied thereto into a non-stabilized direct voltage. The collector of a switching transistor 2 is connected to one of the two terminals between which this direct voltage is obtained, said transistor being of the npn-type in this embodiment and the base of which receives a pulsatory voltage which originates through a control stage 4 from a modulator 5 and causes transistor 2 to be saturated and cut off alternately. The voltage waveform 3 is produced at the emitter of transistor 2. In order to maintain the output voltage of the circuit arrangement constant, the duration of the pulses provided is varied in modulator 5. A pulse oscillator 6 supplies the pulsatory voltage to modulator 5 and is synchronized by a signal of line frequency which originates from the line oscillator 6' present in the picture display device. This line oscillator 6' is in turn directly synchronized in known manner by pulses 7' of line frequency which are present in the device and originate for example from a received television signal if the picture display device is a television receiver. Pulse oscillator 6 thus generates a pulsatory voltage the repetition frequency of which is the line frequency.The emitter of switching transistor 2 is connected at one end to the cathode of an efficiency diode 7 whose other end is connected to the second input voltage terminal and at the other end to primary winding 8 of a transformer 9. Pulsatory voltage 3 which is produced at the cathode of efficiency diode 7 is clamped against the potential of said second terminal during the intervals when this diode conducts. During the other intervals the pulsatory voltage 3 assumes the value V i . A charge capacitor 10 and a load 11 are arranged between the other end of winding 8 and the second input voltage terminal. The elements 2,7,8,10 and 11 constitute a so-called chopper producing a direct voltage across charge capacitor 10, provided that capacitor 10 has a sufficiently great value for the line frequency and the current applied to load 11 flowing alternately through switching transistor 2 or through efficiency diode 7. The output voltage V o which is the direct voltage produced across charge capacitor 10 is applied to a comparison circuit 12 which compares the voltage V o with a reference voltage. Comparison circuit 12 generates a direct voltage which is applied to modulator 5 so that the duration of the effective period δ T of switching transistor 2 relative to the period T of pulses 3 varies as a function of the variations of output voltage V 0 . In fact, it is readily evident that output voltage V o is proportional to the ratio δ :

V o = V i . δ

Load 11 of the chopper consists in the consumption of parts of the picture display device which are fed by output voltage V 0 . In a practical embodiment of the circuit arrangement according to FIG. 1 wherein the mains alternating voltage has a nominal effective value of 220 V and the rectified voltage V i is approximately 270 V, output voltage V o for δ = 0.5 is approximately 135 V. This makes it also possible, for example, to feed a line deflection circuit as is shown in FIG. 1 wherein load 11 then represents different parts which are fed by the chopper. Since voltage V o is maintained constant due to pulse duration modulation, the supply voltage of this line deflection circuit remains constant with the favorable result that the line amplitude(= the width of the picture displayed on the screen of the picture display tube) likewise remains constant as well as the EHT required for the final anode of the picture display tube in the same circuit arrangement independent of the variations in the mains voltage and the load on the EHT generator (= variations in brightness).

However, variations in the line amplitude and the EHT may occur as a result of an insufficiently small internal impedance of the EHT generator. Compensation means are known for this purpose. A possibility within the scope of the present invention is to use comparison circuit 12 for this purpose. In fact, if the beam current passes through an element having a substantially quadratic characteristic, for example, a voltage-dependent resistor, then a variation for voltage V o may be obtained through comparison circuit 12 which variation is proportional to the root of the variation in the EHT which is a known condition for the line amplitude to remain constant.

However, variations in the line amplitude and the EHT may occur as a result of an insufficiently small internal impedance of the EHT generator. Compensation means are known for this purpose. A possibility within the scope of the present invention is to use comparison circuit 12 for this purpose. In fact, if the beam current passes through an element having a substantially quadratic characteristic, for example, a voltage-dependent resistor, then a variation for voltage V o may be obtained through comparison circuit 12 which variation is proportional to the root of the variation in the EHT which is a known condition for the line amplitude to remain constant.In addition this facilitates smoothing of voltage V o since the repetition frequency of pulsatory voltage 3 is many times higher than that of the mains and a comparatively small value may be sufficient for charge capacitor 10. If charge capacitor 10 has a sufficiently high value for the line frequency, voltage V o is indeed a direct voltage so that a voltage having the same form as pulsatory voltage 3 is produced across the terminals of primary winding 8. Thus voltages which have the same shape as pulsatory voltage 3 but have a greater or smaller amplitude are produced across secondary windings 13, 14 of transformer 9 (FIG. 1 shows only 2 secondary windings but there may be more). The invention is based on the recognition that one end of each secondary winding is connected to earth while the other end thereof drives a diode, the winding sense of each winding and the direction of conductance of each diode being chosen to be such that these diodes conduct during the same period as does efficiency diode 7. After smoothing, stabilized supply voltages, for example, at terminal 15 are generated in this manner at the amplitudes and polarities required for the circuit arrangements present in the picture display device. In FIG. 1 the voltage generated at terminal 15 is, for example, positive relative to earth. It is to be noted that the load currents of the supply voltages obtained in this manner cause a reduction of the switching power which is economized by efficiency diode 7. The sum of all diode currents including that of diode 7 is in fact equal to the current which would flow through diode 7 if no secondary winding were wound on transformer 9 and if no simultaneous diode were used. This reduction may be considered an additional advantage of the circuit arrangement according to the invention, for a diode suitable for smaller powers may then be used. However, it will be evident that the overall secondary load must not exceed the primary load since otherwise there is the risk of efficiency diode 7 being blocked so that stabilization of the secondary supply voltages would be out of the question.

It is to be noted that a parabola voltage of line frequency as shown at 28 is produced across the charge capacitor 10 if this capacitor is given a smaller capacitance so that consequently the so-called S-correction is established.

In FIG. 1 charge capacitors are arranged between terminals 15 etc. and earth so as to ensure that the voltages on these points are stabilized direct voltages. If in addition the mean value of the voltage on one of these terminals has been made equal to the effective value of the alternating voltage which is required for heating the filament of the picture display tube present in the picture display device, this voltage is suitable for this heating. This is a further advantage of the invention since the cheap generation of a stabilized filament voltage for the picture display tube has always been a difficult problem in transistorized arrangements.

A further advantage of the picture display device according to the invention is that transformer 9 can function as a separation transformer so that the different secondary windings can be separated from the mains and their lower ends can be connected to ground of the picture display device. The latter step makes it possible to connect a different apparatus such as, for example, a magnetic recording and/or playback apparatus to the picture display device without earth connection problems occurring.

In FIG. 1 the reference numeral 14 denotes a secondary winding of transformer 9 which in accordance with the previously mentioned recognition of the invention can drive line output transistor 16 of the line deflection circuit 17. Line deflection circuit 17 which is shown in a simplified form in FIG. 1 includes inter alia line deflection coils 18 and an EHT transformer 19 a secondary winding 20 of which serves for generating the EHT required for the acceleration anode of the picture display tube. Line deflection circuit 17 is fed by the output voltage V o of the chopper which voltage is stabilized due to the pulse duration modulation with all previously mentioned advantages. Line deflection circuit 17 corresponds, for example, to similar arrangements which have been described in U.S. Pat. No. 3,504,224 issued Mar. 31, 1970 to J.J. Reichgelt et al., U.S. patent application Ser. No. 737,009 filed June 14, 1968 by W. H. Hetterscheid and U.S. application Ser. No. 26,497 filed April 8, 1970 by W. Hetterscheid et al. It will be evident that differently formed lined deflection circuits are alternatively possible.

It will now be shown that secondary winding 14 can indeed drive a line deflection circuit so that switching transistor 2 can function as a driver for the line deflection. FIGS. 2a and b show the variation as a function of time of the current i C which flows in the collector of transistor 16 and of the drive voltage v 14 across the terminals of secondary winding 14. During the flyback period (0, t 1 ) transistor 16 must be fully cut off because a high voltage peak is then produced at its collector; voltage v 14 must then be absolutely negative. During the scan period (t 1 , t 4 ) a sawtooth current i C flows through the collector electrode of transistor 16 which current is first negative and then changes its direction. As the circuit arrangement is not free from loss, the instant t 3 when current i C becomes zero lies, as is known, before the middle of the scan period. At the end t 4 of the scan period transistor 16 must be switched off again. However, since transistor 16 is saturated during the scan period and since this transistor must be suitable for high voltages and great powers so that its collector layer is thick, this transistor has a very great excess of charge carriers in both its base and collector layers. The removal of these charge carriers takes a period t s which is not negligible whereafter the transistor is indeed switched off. Thus the fraction δ T of the line period T at which v 14 is positive must end at the latest at the instant (t 4 - t s ) located after the commencement (t = 0) of the previous flyback.

The time δ T may be initiated at any instant t 2 which is located between the end t 1 of the flyback period and the instant t 3 when collector current i C reverses its direction. It is true that emitter current flows through transistor 16 at the instant t 2 , but collector current i C is not influenced thereby, at least not when the supply voltage (= V o ) for line deflection circuit 17 is high enough. All this has been described in the U.S. Pat. No. 3,504,224. The same applies to line deflection circuits wherein the collector base diode does not function as an efficiency diode as is the case in the described circuit 17, but wherein an efficiency diode is arranged between collector and emitter of the line output transistor. In such a case the negative part of the current i C of FIG. 2a represents the current flowing through the said efficiency diode.

After the instant t 3 voltage v 14 must be positive. In other words, the minimum duration of the period T when voltage v 14 must be positive is (t 4 - t s ) - t 3 whilst the maximum duration thereof is (t 4 - t s ) - t 1 . In a television system employing 625 lines per raster the line period t 4 is approximately 64 μus and the flyback period is approximately 12 μus. Without losses in the circuit arrangement instant t 3 would be located approximately 26 μus after the instant t 1 , and with losses a reasonable value is 22 μus which is 34 μus after the commencement of the period. If for safety's sake it is assumed that t s lasts approximately 10 μus, the extreme values of δ T are approximately 20 and 42 μus and consequently the values for δ are approximately 0.31 and 0.66 at a mean value which is equal to approximately 0.49. It was previously stated that a mean value of δ = 0.5 was suitable. Line deflection circuit 17 can therefore indeed be used in combination with the chopper in the manner described, and the relative variation of δ may be (0.66 - 0.31) : 0.49 = 71.5 percent. This is more than necessary to obviate the variations in the mains voltage or in the various loads and to establish the East-West modulation and ripple compensation to be described hereinafter. In fact, if it is assumed that the mains voltage varies between -15 and +10 percent of the nominal value of 220 V, while the 50 Hz ripple voltage which is superimposed on the input voltage V i has a peak-to-peak value of 40 V and V i is nominally 270 V, then the lowest occurring V i is:

0.85 × 270 V - 20 V = 210 V and the highest occurring V i is

1.1 × 270 V + 20 V = 320 V. For an output voltage V o of 135 V the ratio must thus vary between

δ = 135 : 210 = 0.64 and δ = 135 : 320 = 0.42.

A considerable problem presenting itself is that of the simultaneous or non-simultaneous drive of line output transistor 16 with switching transistor 2, it being understood that in case of simultaneous drive both transistors are simultaneously bottomed, that is during the period δ T. This depends on the winding sense of secondary winding 14 relative to that of primary winding 8. In FIG. 1 it has been assumed that the drive takes place simultaneously so that the voltage present across winding 14 has the shape shown in FIG. 2b. This voltage assumes the value n(V i - V o ) in the period δ T and the value -nVo in the period (1 - δ )T, wherein n is the ratio of the number of turns on windings 14 and 8 and wherein V o is maintained constant at nominal mains voltage V o = δ V inom . However, if as a result of an increase or a decrease of the mains voltage V i increases or decreases proportionally therewith, i.e., V i = V i nom + Δ V, the positive portion of V 14 becomes equal to n(V i nom - V o +Δ V) = n [(1 -δ)V i nom +ΔV] = n(0.5 V inom +ΔV) if δ = 0.5 for V i = V i nom. Relatively, this is a variation which is twice as great. For example, if V i nom = 270 V and V o = 135 V, a variation in the mains voltage of from -15 to +10 percent causes a variation of V i of from -40.5 V to +27 V which ranges from -30 to +20 percent of 135 V which is present across winding 8 during the period δ T. The result is that transistor 16 can always be bottomed over a large range of variation. If the signal of FIG. 2b would be applied through a resistor to the base of transistor 16, the base current thereof would have to undergo the same variation while the transistor would already be saturated in case of too low a voltage. In this case it is assumed that transformer 9 is ideal (without loss) and that coil 21 has a small inductance as is explained in the U.S. patent application Ser. No. 737,009 above mentioned. It is therefore found to be desirable to limit the base current of transistor 16.

This may be effected by providing a coil 22 having a large value inductance, approximately 100 μH, between winding 14 and the small coil 21. The variation of said base current i b is shown in FIG. 2c but not to the same scale as the collector current of FIG. 2a. During the conducting interval δ T current i b varies as a linear function of time having a final value of wherein L represents the inductance of coil 22. This not only provides the advantage that this final value is not immediately reached, but it can be shown that variation of this final value as a function of the mains voltage has been reduced, for there applies at nominal mains voltage that: If the mains voltage V i = V i nom +Δ V, then ##SPC1## because V i nom = 2 V o . Thus this variation is equal to that of the mains voltage and is not twice as great.

During switching off, t 2 , of transistor 16 coil 22 must exert no influence and coil 21 must exert influence which is achieved by arranging a diode 23 parallel to coil 22. Furthermore the control circuit of transistor 16 in this example comprises the two diodes 24 and 25 as described in U.S. application Ser. No. 26,497 above referred to, wherein one of these diodes, diode 25 in FIG. 1, must be shunted by a resistor.

During switching off, t 2 , of transistor 16 coil 22 must exert no influence and coil 21 must exert influence which is achieved by arranging a diode 23 parallel to coil 22. Furthermore the control circuit of transistor 16 in this example comprises the two diodes 24 and 25 as described in U.S. application Ser. No. 26,497 above referred to, wherein one of these diodes, diode 25 in FIG. 1, must be shunted by a resistor.The control circuit of transistor 16 may alternatively be formed as is shown in FIG. 4. In fact, it is known that coil 21 may be replaced by the parallel arrangement of a diode 21' and a resistor 21" by which the inverse current can be limited. To separate the path of the inverse current from that of the forward current the parallel arrangement of a the diode 29' and a resistor 29" must then be present. This leads to the circuit arrangement shown in the upper part of FIG. 4. This circuit arrangement may now be simplified if it is noted that diodes 25 and 21' on the one hand and diodes 23 and 29' on the other hand are series-arranged. The result is shown in the lower part of FIG. 4 which, as compared with the circuit arrangement of FIG. 1, employs one coil less and an additional resistor.

FIG. 3 shows possible modifications of the chopper. FIG. 3a shown in a simplified form the circuit arrangement according to FIG. 1 wherein the pulsatory voltage present across the connections of windings 8 has a peak-to-peak amplitude of V i - V o = 0.5 V i for δ = 0.5, As has been stated, the provision of coil 22 gives a relative variation for the base current of transistor 16 which is equal to that of the mains voltage. In the cases according to FIG. 3b, 3c and 3d the peak-to-peak amplitude of the voltage across winding 8 is equal to V i so that the provision of coil 22 results in a relative variation which is equal to half that of the mains voltage which is still more favorable than in the first case.

Transistors of the npn type are used in FIG. 3. If transistors of the pnp type are used, the relevant efficiency diodes must of course be reversed.

In this connection it is to be noted that it is possible to obtain an output voltage V o with the aid of the modifications according to FIGS. 3b, c and d, which voltage is higher than input voltage V i . These modifications may be used in countries such as, for example, the United of America or France where the nominal mains voltage is 117 or 110 V without having to modify the rest of the circuit arrangement.

The above-mentioned remark regarding the sum of the diode currents only applies, however, for the modifications shown in FIGS. 3a and d.

If line output transistor 16 is not simultaneously driven with switching transistor 2, efficiency diodes 7 conducts simultaneously with transistor 16 i.e., during the period which is denoted by δ T in FIGS. 1 and 2b. During that period the output voltage V o of the chopper is stabilized so that the base current of transistor 16 is stabilized without further difficulty. However, a considerable drawback occurs. In FIG. 1 the reference numeral 26 denotes a safety circuit the purpose of which is to safeguard switching transistor 2 when the current supplied to load 11 and/or line deflection circuit 17 becomes to high, which happens because the chopper stops. After a given period output voltage V o is built up again, but gradually which means that the ratio δ is initially small in the order of 0.1. All this is described in U.S. patent No. 3,629,686. The same phenomenon occurs when the display device is switched on. Since δ = 0.1 corresponds to approximately 6 μs when T = 64 μs, efficiency diode 7 conducts in that case for 64 - 6 = 58 μus so that transistor 16 is already switched on at the end of the scan or at a slightly greater ratio δ during the flyback. This would cause an inadmissibly high dissipation. For this reason the simultaneous drive is therefore to be preferred.

The line deflection circuit itself is also safeguarded: in fact, if something goes wrong in the supply, the driver voltage of the line deflection circuit drops out because the switching voltage across the terminals of primary winding 8 is no longer present so that the deflection stops. This particularly happens when switching transistor 2 starts to constitute a short-circuit between emitter and collector with the result that the supply voltage V o for the line deflection circuit in the case of FIG. 1 becomes higher, namely equal to V i . However, the line output transformer is now cut off and is therefore also safe as well as the picture display tube and other parts of the display device which are fed by terminal 15 or the like. However, this only applies to the circuit arrangement according to FIG. 1 or 3a.

Pulse oscillator 6 applies pulses of line frequency to modulator 5. It may be advantageous to have two line frequency generators as already described, to wit pulse oscillator 6 and line oscillator 6' which is present in the picture display device and which is directly synchronized in known manner by line synchronizing pulses 7'. In fact, in this case line oscillator 6' applies a signal of great amplitude and free from interference to pulse oscillator 6. However, it is alternatively possible to combine pulse oscillator 6 and line oscillator 6' in one single oscillator 6" (see FIG. 1) which results in an economy of components. It will be evident that line oscillator 6' and oscillator 6" may alternatively be synchronized indirectly, for example, by means of a phase discriminator. It is to be noted neither pulse oscillator 6, line oscillator 6' and oscillator 6" nor modulator 5 can be fed by the supply described since output voltage V o is still not present when the mains voltage is switched on. Said circuit arrangements must therefore be fed directly from the input terminals. If as described above these circuit arrangements are to be separated from the mains, a small separation transformer can be used whose primary winding is connected between the mains voltage terminals and whose secondary winding is connected to ground at one end and controls a rectifier at the other end.

Pulse oscillator 6 applies pulses of line frequency to modulator 5. It may be advantageous to have two line frequency generators as already described, to wit pulse oscillator 6 and line oscillator 6' which is present in the picture display device and which is directly synchronized in known manner by line synchronizing pulses 7'. In fact, in this case line oscillator 6' applies a signal of great amplitude and free from interference to pulse oscillator 6. However, it is alternatively possible to combine pulse oscillator 6 and line oscillator 6' in one single oscillator 6" (see FIG. 1) which results in an economy of components. It will be evident that line oscillator 6' and oscillator 6" may alternatively be synchronized indirectly, for example, by means of a phase discriminator. It is to be noted neither pulse oscillator 6, line oscillator 6' and oscillator 6" nor modulator 5 can be fed by the supply described since output voltage V o is still not present when the mains voltage is switched on. Said circuit arrangements must therefore be fed directly from the input terminals. If as described above these circuit arrangements are to be separated from the mains, a small separation transformer can be used whose primary winding is connected between the mains voltage terminals and whose secondary winding is connected to ground at one end and controls a rectifier at the other end. Capacitor 27 is arranged parallel to efficiency diode 7 so as to reduce the dissipation in switching transistor 2. In fact, if transistor 2 is switched off by the pulsatory control voltage, its collector current decreases and its collector-emitter voltage increases simultaneously so that the dissipated power is not negligible before the collector current has becomes zero. If efficiency diode 7 is shunted by capacitor 27 the increase of the collector-emitter voltage is delayed i.e., this voltage does not assume high values until the collector current has already been reduced. It is true that in that case the dissipation in transistor 2 slightly increases when it is switched on by the pulsatory control voltage but on the other hand since the current flowing through diode 7 has decreased due to the presence of the secondary windings, its inverse current is also reduced when transistor 2 is switched on and hence its dissipation has become smaller.

Capacitor 27 is arranged parallel to efficiency diode 7 so as to reduce the dissipation in switching transistor 2. In fact, if transistor 2 is switched off by the pulsatory control voltage, its collector current decreases and its collector-emitter voltage increases simultaneously so that the dissipated power is not negligible before the collector current has becomes zero. If efficiency diode 7 is shunted by capacitor 27 the increase of the collector-emitter voltage is delayed i.e., this voltage does not assume high values until the collector current has already been reduced. It is true that in that case the dissipation in transistor 2 slightly increases when it is switched on by the pulsatory control voltage but on the other hand since the current flowing through diode 7 has decreased due to the presence of the secondary windings, its inverse current is also reduced when transistor 2 is switched on and hence its dissipation has become smaller.In addition it is advantageous to delay these switching-on and switching-off periods to a slight extent because the switching pulses then contain fewer Fourier components of high frequency which may cause interferences in the picture display device and which may give rise to visible interferences on the screen of the display tube. These interferences occupy a fixed position on the displayed image because the switching frequency is the line frequency which is less disturbing to the viewer. In a practical circuit wherein the line frequency is 15,625 Hz and wherein switching transistor 2 is an experimental type suitable for a maximum of 350 V collector-emitter voltage or 1 A collector current and wherein efficiency diode 7 is of the Philips type BA 148 the capacitance of capacitor 27 is approximately 680 pF whilst the load is 70 W on the primary and 20 W on the secondary side of transformer 9. The collector dissipation upon switching off is 0.3 W (2.5 times smaller than without capacitor 27) and 0.7 W upon switching on.

As is known the so-called pincushion distortion is produced in the picture display tubes having a substantially flat screen and large deflection angles which are currently used. This distortion is especially a problem in color television wherein a raster correction cannot be brought about by magnetic means. The correction of the so-called East-West pincushion distortion i.e., in the horizontal direction on the screen of the picture display tube can be established in an elegant manner with the aid of the circuit arrangement according to the invention. In fact, if the voltage generated by comparison circuit 12 and being applied to modulator 5 for duration-modulating pulsatory voltage 3 is modulated by a parabola voltage 28 of field frequency, pulsatory voltage 3 is also modulated thereby. If the power consumption of the line deflection circuit forms part of the load on the output voltage of the chopper, the signal applied to the line deflection coils is likewise modulated in the same manner. Conditions therefore are that the parabola voltage 28 of field frequency has a polarity such that the envelope of the sawtooth current of line frequency flowing through the line deflection coils has a maximum in the middle of the scan of the field period and that charge capacitor 10 has not too small an impedance for the field frequency. On the other hand the other supply voltages which are generated by the circuit arrangement according to the invention and which might be hampered by this component of field frequency must be smoothed satisfactorily.

A practical embodiment of the described example with the reference numerals given provides an output for the supply of approximately 85 percent at a total load of 90 W, the internal resistance for direct current loads being 1.5 ohms and for pulsatory currents being approximately 10 ohms. In case of a variation of ± 10 percent of the mains voltage, output voltage V o is stable within 0.4 V. Under the nominal circumstances the collector dissipation of switching transistor 2 is approximately 2.5 W.

Since the internal resistance of the supply is so small, it can be used advantageously, for example, at terminal 15 for supplying a class-B audio amplifier which forms part of the display device. Such an amplifier has the known advantages that its dissipation is directly proportional to the amplitude of the sound to be reproduced and that its output is higher than that of a class-A amplifier. On the other hand a class-A amplifier consumes a substantially constant power so that the internal resistance of the supply voltage source is of little importance. However, if this source is highly resistive, the supply voltage is modulated in the case of a class-B amplifier by the audio information when the sound intensity is great which may detrimentally influence other parts of the display device. This drawback is prevented by means of the supply according to the invention.

The 50 Hz ripple voltage which is superimposed on the rectified input voltage V i is compensated by comparison circuit 12 and modulator 5 since this ripple voltage may be considered to be a variation of input voltage V i . A further compensation is obtained by applying a portion of this ripple voltage with suitable polarity to comparison circuit 12. It is then sufficient to have a lower value for the smoothing capacitor which forms part of rectifier circuit 1 (see FIG. 3). The parabola voltage 28 of field frequency originating from the field time base is applied to the same circuit 12 so as to correct the East-West pincushion distortion.

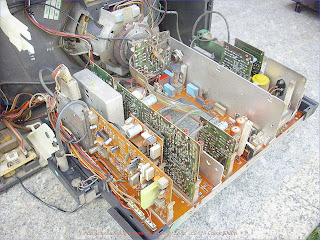

F UNIT Luminance and chromince unit TDA2560 TDA2527.

H UNIT HORIZONTAL OSC TDA2590

G UNIT RGB AMPL MATRIX TDA2530

E UNIT SOUND UNIT TDA1039

I UNIT FRAME TDA1270

M UNIT SUPPLY CONTROL TDA2640.

A UNIT MAINS RECT.

Control circuit for a switched-mode power supply, particularly for a television receiver: VOXSON T5647CD CHASSIS CT4 20AX SWITCH MODE POWER SUPPLY.

The Control UNIT is developed around the PHILIPS TDA2640.

"Television Switched-Mode Power Supply Using the TDA2640", Mullard Technical Communications, L. M. White, pp. 258-279, Jul. 1975.

A switched-mode power supply provided with a control stage and a switching stage coupled by means of a transformer. The collector of an additional transistor is connected to the transformer. In this manner the ratio of the collector current to the base current of the switching transistor can assume a predetermined value, for example a constant value whatever the value of the mains voltage applied to the power supply.

1. A control circuit for a switched-mode power supply, said power supply comprising a non-regulated rectified DC voltage source, a driver transistor, a first transformer having primary and secondary windings, an end of said primary being coupled to the collector-emitter path of said driver transistor, a switching transistor having a base coupled to said secondary, a second transformer having a primary winding coupled in series with said switching transistor, and a plurality of secondary windings, said control circuit comprising a first additional transistor having a collector coupled to the remaining end of the primary winding of the first transformer not connected to the driver-transistor and an emitter coupled to the non-regulated direct voltage source.

2. A control circuit as claimed in claim 1, further comprising a constant voltage source coupled to the base of the additional transistor.

3. A control circuit as claimed in claim 1, further comprising a constant current source, and a resistor coupled between the emitter of the additional transistor and the constant current source.

4. A control circuit as claimed in claim 3, wherein the constant current source comprises a second additional transistor, the two additional transistors being of complementary conductivity and their emitters being connected with each other through said resistor, the collector of the second additional transistor being coupled to the non-regulated rectified direct voltage source and the collector of the first additional transistor being coupled to the end of the primary winding of the first transformer not connected to the driver transistor.

5. A control circuit as claimed in claim 4, further comprising a resistor coupled in series with the collector circuit of said second additional transistor and the non-regulated rectified direct voltage source.

6. A control circuit as claimed in claim 5, further comprising a zener diode coupled between the base of the second additional transistor and the non-regulated voltage source.

7. A control circuit as claimed in cl

aim 6, further comprising a resistance bridge coupled to the base of the first additional transistor and arranged between the two electrodes of the zener diode.

aim 6, further comprising a resistance bridge coupled to the base of the first additional transistor and arranged between the two electrodes of the zener diode.8. A control circuit as claimed in claim 7, wherein the driver transistor and the switching transistor do not conduct simultaneously, and the voltage between the two electrodes of the zener diode as well as the values of the resistors arranged between the said electrodes and of the resistor arranged between the emitters of the two additional transistors are chosen so that the first additional transistor is in the saturated state at the lowest value of the non-regulated voltage while it operates in the linear state at a higher value of said non-regulated voltage.

This type of switched-mode power supply is used more and more because of the numerous advantages it presents as regards energy efficiency, reliability, compactness, etc. However, as for the majority of the other types of power supplies, its operation on mains supplies of different voltages imposes the use of either a transformer with taps or switch-over from full wave rectification at the highest mains voltage to a voltage doubler rectification for the lowest mains voltage.

It is known that the specific qualities of a switched-mode power supply depend for a large part on the switching speed of the switching transistor at the moment at which the latter passes periodically from the conductive state to the blocking state; this speed is at its maximum when the switching transistor presents, at the turn-off moment, a certain ratio between the collector current and the base current IC/IB: if this ratio is too low, the delay in the recombination of the charges stored in the base increases the switching time; if it is too high there is the risk that the transistor is brought out of saturation before it is blocked, which results in its substantially immediate destruction. For the known switched-mode power supplies it is not possible to maintain a suitable IC/IB ratio in the presence of large variations of the non-regulated rectified DC voltage which result from the connection to the nominal mains voltages of, for example, 110 or 220 V; actually, if the variations in IB are substantially proportional to the variations in the non-regulated voltage, the same does not happen for those of the IC whose amplitude is less.

However, the importance of having a power supply which can operate without any switching on mains supplies of 110 or 220 V is evident: for the manufacturer it is cheaper to produce and the reliability is increased; while the user does not run the risk of incorrect manipulations, particularly when the power supply is destined for use in portable television sets.

One of the objects of the invention is to realize a control circuit which permits the switched-mode power supply to operate without switching in conditions which are substantially optimum and in the presence of mains voltage variations in the range of 90 to 250 Volts.

A further object of the invention is to ensure that said IC/IB ratio of the switching transistor has a predetermined and, more particularly a constant value at the turn-off moment whatever the value of the mains voltage applied to the power supply.

The control circuit according to the inv

ention is characterized in that the end of the primary winding of the first transformer not connected to the driver transistor is connected to the collector of an additional transistor whose emitter is coupled with the non-regulated direct voltage source. Advantageously it is characterized in that the emitter of the additional transistor is connected to one end of a resistor, the other end of this resistor being connected to a constant current source, and that the constant current source is constituted by a second additional transistor, the two additional transistors being of complementary conductivity and their emitters being connected with each other through a resistor, whilst the collector of the second additional transistor is connected to one of the poles of the non-regulated rectified direct voltage source and the collector of the first additional transistor is connected to the end of the primary winding of the first transformer not connected to the driver transistor.

ention is characterized in that the end of the primary winding of the first transformer not connected to the driver transistor is connected to the collector of an additional transistor whose emitter is coupled with the non-regulated direct voltage source. Advantageously it is characterized in that the emitter of the additional transistor is connected to one end of a resistor, the other end of this resistor being connected to a constant current source, and that the constant current source is constituted by a second additional transistor, the two additional transistors being of complementary conductivity and their emitters being connected with each other through a resistor, whilst the collector of the second additional transistor is connected to one of the poles of the non-regulated rectified direct voltage source and the collector of the first additional transistor is connected to the end of the primary winding of the first transformer not connected to the driver transistor.Whilst combining the action of a ballast transistor with that of a variable current generator, the circuit according to the invention thus maintains automatically a desired IC/IB ratio of the switching transistor whatever the value of the mains voltage applied to the power supply.

TDA2590 horizontal oscillator combination

GENERAL DESCRIPTION

— The TDA2590 is a monolithic integrated circuit designed

as a horizontal oscillator combination for TV receivers and monitors.

It is constructed using the Fairchild Planar* process.

LINE OSCILLATOR USING THE THRESHOLD SWITCHING PRINCIPLE

PHASE COMPARISON BETWEEN SYNC PULSE AND OSCILLATOR VOLTAGE (d>1)

PHASE COMPARISON BETWEEN LINE FLYBACK PULSE AND OSCILLATOR VOLTAGE

(<62) Y

SWITCH FOR CHANGING THE FILTER CHARACTERISTIC AND THE GATE CIRCUIT

{WHEN USED FOR VCR)

COINCIDENCE DETECTOR (¢3)

SYNC SEPARATOR

NOISE SEPARATOR

VERTICAL SYNC SEPARATOR AND OUTPUT STAGE

COLOR BURST KEYING AND LINE FLYBACK BLANKING PULSE GENERATOR

PHASE SHIFTER FOR THE OUTPUT PULSE

OUTPUT PULSE DURATION SWITCHING

OUTPUT STAGE FOR DIRECT DRIVE OF THYRISTOR DEFLECTION CIRCUITS

SYNC GATING PULSE GENERATOR

LOW SUPPLY VOLTAGE PROTECTION.

VOXSON T5647CD CHASSIS CT4 20AX Television set which displays analog data relevant to the operation of the television set on its video display:

(SAB2024 SAB2022 SAB1016 SAB2015 SAB3012)

SAB2015 Station search + RAM

SAB2022 TV AFT (AUTOMATIC FINE TUNING)

SAB2024 TV PLL TUNING

SAB1016 TV CHARACTER FADE IN (OSD)

SAB 3012 US/IF/REC 2X64 CODES REMOTE RECEIVER.

The present invention relates to a television set which includes a picture display device, an alpha numerical character generating circuit connected to said device, a control device, means for determining analogue data relating to the operation of the set, such as volume, brightness and color, and means for displaying on said display device a combination of alpha numerical characters, supplied by said character generating device, indicating the values of said analogue data.

A control keyboard has six keys "V+", "V-", "L+", "L-", "C+" and "C-". The output of the keyboard is connected to a processing unit which is connected via a digital to analogue converter and switch to an alpha numerical character generator which is connected to a picture display device. When one of the six keys is pressed a combination of signals proportional to the analogue signal level of volume, brightness and color (V, L, C) is displayed on the picture display device. If one of the + keys is pressed, the corresponding analogue level is increased by 1/64 of maximum value, while a similar decrease is obtained by pressing one of the - keys.

1. A television set, comprising:

a picture display device for displaying a video picture;

character generator means for generating signals representative of alphabetical, numerical and/or abstract characters;

said picture display device receiving said signals and displaying the alphabetical, numerical and/or abstract characters represented thereby; and

control means for determining the value of analog data, other than the tuning frequency of said television set, relating to the operation of said television set, and for causing said character generator means to generate signals representative of alphabetical, numerical and/or abstract characters which indicate said value of said analog data.

An integrated circuit for a programmable television receiver comprises a memory for storing a plurality of programs, a digital clock and a character generating circuit for generating character signals for displaying the programs in the memory and/or time of the digital clock on the screen of a television receiver. The integrated circuit uses dynamic circuits to reduce the number of elements required, and CMOS transistors to attain a lower power dissipation. 2. A television set, comprising:

a picture display device for displaying a video picture;

character generator means for generating signals representative of alphabetical, numerical and/or abstract characters;

said picture display device receiving said signals and displaying the alphabetical, numerical and/or abstract characters represented thereby; and

control means for determining the value of analog data relating to the operation of said television set and for causing said character generator means to generate signals representative of alphabetical, numerical and/or abstract characters which indicate said value of said analog data, said control means also causing said character generator means to generate signals representative of alphabetical, numerical and/or abstract characters indicative of which of said data the user of said television set has last selected to adjust.

3. A television set, comprising:

a picture display device for displaying a video picture;

1. An integrated circuit for use in a programmable television receiver comprising:

an oscillator to which a quartz crystal is to be externally coupled;

a digital clock coupled to said oscillator;

a memory for storing a plurality of programs each including time data and associated channel data and having a plurality of recirculating dynamic shift registers each adapted to store one program;

a character generating circuit coupled to said memory and adapted to generate character signals to permit the content of said memory to be displayed on the screen of a cathode ray tube of a television receiver;

circuit means coupled to the output of said oscillator to generate shift pulses for driving said recirculating dynamic shift registers in said memory;

time comparision means coupled to the outputs of said memory and said digital clock for comparing the time data in said memory and the time of said digital clock;

means to readout said channel data from said memory; and

means responsive to said time comparing means and said readout means to form a program execution output based on said channel data when a coincidence occurs between the time data in said memory and the time of said digital clock.

2. An integrated circuit according to claim 1, in which said character generating circuit comprises:

an input for receiving horizontal timing pulses which synchronize with horizontal synchronizing pulses of the television receiver, have a frequency higher than that of the horizontal synchronizing pulse and provide a unit length in displaying characters in the horizontal direction of the cathode ray tube;

a horizontal component pulse generating circuit responsive to the horizontal timing pulses for generating horizontal component pulses which provide horizontal components of each character and have a horizontal one-digit display period, and clock pulses having the horizontal one-digit display period;

a horizontal display digit designation pulse generating circuit connected to said horizontal component pulse generating circuit to generate horizontal display digit designation pulses in response to the clock pulses;

a vertical component pulse generating circuit for generating vertical component pulses which provide vertical components of each character in response to the horizontal synchronizng pulse in the television receiver;

a multiplexer connected to said memory and said horizontal display digit designation pulse generating circuit to deliver hour data, minute data and channel data in the binary form from said memory in a predetermined sequence in response to said horizontal display digit designation pulses;

segment decoders for decoding the outputs of said multiplexer and generating segment outputs; and

output circuit means for generating character signals during each horizontal one-digit display period in response to the outputs of said segment decoders, said horizontal components pulses and said vertical component pulses.

3. An integrated circuit according to claim 2, in which said multiplexer includes a plurality of series-connected circuits each having a plurality of first MOS transistors of first channel type connected between each bit output of said multiplexer and a first potential point, the gate of one MOS transistor in each series circuit being connected to receive a binary signal having the same weight of each data and the gates of the remaining MOS transistors in each series circuit being connected to receive display digit designation pulses from said display digit designation pulse generating circuit; and a second MOS transistor of second channel type connected between the bit output and a second potential point, the gate of said second MOS transistor being connected to receive one clock pulse from said digit designation pulse generating circuit. 4. An integrated circuit according to claim 2, in which said segment decoders each include a plurality of first MOS transistors of first channel type connected between a decoder output and a first potential point, the gates of said first MOS transistors being connected to receive respective outputs of said multiplexer, and said output circuit means includes a second MOS transistor of the first channel type connected between a circuit point and each output of those segment decoders corresponding to the same horizontal component of the character and having a gate connected to receive from said vertical component pulse generating circuit a vertical component pulse associated with the horizontal component, a third MOS transistor of a second channel type connected between said circuit point and a second potential point and having a gate connected to receive one clock pulse from said display digit designation pulse generating circuit, a CMOS clocked inverter connected to said circuit point and adapted to be driven by clock pulses from said display digit designation pulse generating circuit which are different in phase from the clock pulse applied to the gate of said third transistor, and logic circuit means for gating the output of said clocked inverter in response to the corresponding horizontal component pulse. 5. An integrated circuit according to claim 1, in which said memory and digital clock are connected to a first power source line and said character generating circuit is connected to a second power source line.

A programmable TV receiver capable of preliminarily setting the time and channel number of a desired television program has recently been developed. In this case, the television receiver is automatically switched ON and OFF when a programmed time comes. Most of such programmable TV receivers use a mechanically operated clock and memory and have the drawbacks that only a lesser number of programs can be memorized. The use of the electronic memory and digital electronic clock leads to a prominent increase in the number of storable programs and also provides an accurate counting of time. The use of electronic devices permits a stored content (time and channel number) to be displayed on the screen of CRT of a TV set. When such electronic memory and electronic digital clock are realized by discrete elements, a programming device is made bulkier, incurring a high cost. In order to attain miniaturization of the device at low cost the adoption of integrated circuit is considered. However, problem arises from the standpoint of a restricted chip size when all the circuits necessary for a programmable device is integrated into an integrated circuit.

In an electronic programmable device it is necessary to prevent the content of the memory and of the digital clock from being erased when an AC power source is turned OFF. In order to prevent such a situation, switching must be effected from the power source to a dry cell. In this case, the power consumption of the programmable device must be restricted.

It is accordingly the object of this invention to provide a CMOS integrated circuit which has a low power dissipation and incorporates a memory, digital clock, character generating circuit, etc., necessary for a programmable television receiver in a chip of practical size.

According to this invention there is provided an integrated circuit for use in a programmable television receiver comprising an oscillator to which a quartz crystal is to be externally coupled; a digital clock coupled to said oscillator; a memory adapted to store a plurality of programs each including a time data and a channel data and having a plurality of recirculating dynamic shift registers each for storing one program; a character generating circuit coupled to said memory and adapted to generate character signals to permit the content of said memory to be displayed on the screen of a cathode ray tube of a television receiver; circuit means coupled to the output of said oscillator to generate shift pulses for driving said recirculating dynamic shift registers in said memory; time comparison means coupled to the outputs of said memory and said digital clock for comparing the time data in said memory and the time of said digital clock; and means responsive to said time comparing means to form a program execution output when a coincidence occurs between the time data in said memory and the time of said digital clock.

This invention can be more fully understood from the following detailed description when taken in conjunction with the accompanying drawings, in which:

character generator means for generating signals representative of alphabetical, numerical and/or abstract characters;

said picture display device receiving said signals and displaying the alphabetical, numerical, and/or abstract characters represented thereby; and

control means for determining the value of analog data relating to the operation of said television set and for causing said character generator means to generate signals representative of alphabetical, numerical and/or abstract characters which indicate said value of said analog data, said alphabetical, numerical and/or abstract characters consisting of a number of characters proportional to the value of said analog data.

4. A television set, comprising:

a picture display device for displaying a video picture;

character generator means for generating signals representative of alphabetical, numerical and/or abstract characters;

said picture display device receiving said signals and displaying the alphabetical, numerical and/or abstract characters represented thereby; and

control means for determining the value of analog data relating to the operation of said television set and for causing said character generator means to generate signals representative of alphabetical, numerical and/or abstract characters which indicate said value of said analog data, at least one of said alphabetical, numerical andl/or abstract characters indicating the type of data concerned.

5. A television set as claimed in claim 2, wherein said visual indication of which of said data the user has last selected to adjust includes a given additional character alongside said data the user has selected to adjust. 6. A television set as claimed in claim 2, wherein said visual indication of which of said data the user has last selected to adjust includes a given color for the data the user has selected to adjust. 7. A television set as claimed in claim 1, wherein said control means includes a push-button panel for generating digital electronic signals, in response to actuation thereof by the user of said television set, which instructs said control means to change the value of said analog data, said control means also causing said character generator means to generate signals representative of alphabetical, numerical and/or abstract characters which indicate the value of said adjusted analog data and also indicate that said analog data has been adjusted. 8. A television set as claimed in claim 7, wherein said control means generates digital electronic signals indicative of said adjusted value of said analog data, said control means further including a digital to analog converter for converting said digital signal into an analog signal, and a signal switch controlled by said control means for applying said analog signal to that portion of said television circuit which will cause the value of said analog data to assume said adjusted value. 9. A television set as claimed in any one of claims 1-6, additionally comprising a memory for memorizing values of said analog data. 10. A television set as claimed in claim 9, wherein the television set includes a tuning arrangement, capable of memory selection in which each of a series of keys is associated with a preselected and memorised television channel, and a memory circuit capable of memorising, for each of the said channels, number signals representing the preselected values of the said analog data. 11. A television set as claimed in any one of claims 1-6, additionally comprising means for producing an alarm when the said combination of alphabetical, numerical and/or abstract characters coincides with one or more preset combinations.

The present invention relates to a television set which includes a picture display device, an alpha numerical character generating circuit connected to the said device, a control device and means for checking analogue data relating to the operation of the set, such as volume, brightness and color. The system commonly used on television receivers for tuning into the required channels is the so-called FREQUENCY SYNTHESIZER system. This system, made possible by the advent of integrated circuits, offers a number of advantages over other known systems, such as the conventional potentiometer type MECHANICAL MEMORY systems and the more recent so-called VOLTAGE SYNTHESIZER systems. The frequency synthesizer system is fully electronic enabling any channel to be called up directly by the user who formulates the channel number on a keyboard or other control device. The system usually consists of a quartz-controlled reference oscillator, a phase lock loop, a programmable divider and a computer which supplies the number to be sent to the programmable divider in response to the number of the channel set by the user. Thanks to the phase lock loop, for each channel number set by the user, the frequency of the local oscillator on the set is kept so stable and accurate that the set is tuned with great precision to the corresponding channel signal. For further details concerning frequency synthesizer tuning systems, refer to the article entitled "A Frequency Synthesizer for Television Receivers" by E. G. Breeze, published in the November, 1974 issue of the "Transactions BTR" Magazine, or "Digital Television Tuner Uses MOS LSI and Non Volatile Memory" by L. Penner, published in the April 1, 1976 issue of "Electronics".

The frequency synthesizer system lends itself well to a number of different modes of television chanel tuning;

direct selection by formulating the required channel number as described above television channels are numbered: for example, in the European C.C.I.R. standard, V.H.F. band channels are numbered from 2 to 12 and U.H.F. band channels from 21 to 69; in the American Standard, VHF channels are numbered from 2 to 13 and UHF from 14 to 83).

memory selection: each of a certain set of keys corresponds to a preselected and memorised channel;

automatic scanning of all the channels of a given standard, or of all the channels contained in the memory or continuous scanning of all the frequency bands involved.

The first application enables immediate, direct selection of any one of the channels in the relative standard (60 in Europe, 82 in America).

the second enables faster detection of one of a limited number of preferred channels.

The third is a fast, simple way of finding out which standard channels can be received, which channels have been memorised and whether other broadcasting stations exist on non-standard frequencies such as the private broadcasting stations in Italy (there are currently over a hundred operating).

Examples of frequency synthesizer systems with this wide range of selection modes are described in West German Patent Applications No. 26 45 833 and 26 52 185 and, in particular, Italian Patent Application No. 69.950-A/77 filed on Dec. 30, 1977 by the present applicant. All these modes, which are particularly useful in areas where a number of broadcasting stations can be received, require highly complex control equipment which many users may find difficulty in operating. This is even more so if, besides emitter selection and standard receiver adjustment controls (volume, brightness, colour, etc.), provision is also made for additional accessory functions such as a digital clock which requires additional setting controls. Provision of a character generator capable of displaying alpha numerical data on the television screen could prove beneficial in connection with this problem. The aim of the present invention is to provide a television receiver enabling the many functions described above to be effected simple and inexpensively with as little operating difficulty as possible on the part of the user.

BRIEF SUMMARY OF THE INVENTION

According to the present invention there is provided a television set including a picture display device, an alpha numerical character generating circuit connected to said device, a control device and means for determing analogue data relating to the operation of the set wherein means are provided for displaying on the picture device a combination of alpha numerical character, supplied by said character generating circuit, indicating the values of said analogue data.

BRIEF DESCRIPTION OF THE DRAWING

The invention will now be described by way of example only and with reference to the accompanying drawings, in which:

FIG. 1 shows the block diagram of part of a television receiver according to the present invention;

FIGS. 2, 3 and 4 show block diagrams of elementary logic functions performed by the circuits on the device according to the present invention;

FIGS. 5 and 6 show a number of FIG. 1 circuits in greater detail.

FIG. 7 shows the block diagram of an improved version of the FIG. 1 circuit-only the differing features are shown.

DETAILED DESCRIPTION OF THE INVENTION

Referring now to FIG. 1,

indicates a receiving aerial connected to varicap-diode tuner 2 at the output of which a signal converted to intermediate frequency IF is available. The tuner is the known type and consists essentially of a selective amplifier stage, a mixer circuit and local oscillator circuit.