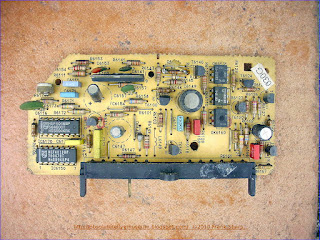

Control Unit

This C

ontrol unit employs two microcomputers the Slave Processor IC 810 and the Master Processor IC 860 Due to this circuit design the power consumed on standby mode is reduced to approx. 8 Wh.

ontrol unit employs two microcomputers the Slave Processor IC 810 and the Master Processor IC 860 Due to this circuit design the power consumed on standby mode is reduced to approx. 8 Wh. Intelligent Pre - amplifier (Slave Processor) (IC 310)

This stage is made up oi the microprocessor IC 810, the infrared receiver IC 1201, as well as the standby evaluation.

The operating voltage +H (SV) is stabilized by the fixed voltage control IC 620 and applied to the control unit via plug R6. The bi phase-code modulated infrared signals are processed by lC 1201 and led to pin 16 of the microprocessor at 5Vpp. The IC 810 contains an internal program which is used only for decoding the infrared signals and for sampling the temporary contact. If a 10 bit word is "correctly" identified, the IC 810 announces this by a HIGH-LOW level change on pin 15. The main computer reacts by producing an interrupt pulse. The program sequence being presently carried out by the main computer is now completed. Then the computer sends ten pulses to the request input, pin 2 of IC 810. With these pulses, the IC 810 feeds out the 10 bit word from pin 15. The quartz O 854 produces the 10 MHz clock frequency between pins 27 and 26 (measurable at pin 26; 5Vpp) for both processors. It the receiver is switched to standby the IC 310 produces a LOW level on pin 8 and the mains stage is switched oil via

T 6130-, T 6124 and OK 6131. When switching the receiver on with the mains switch, pin 18 of the microprocessor is connected to a HIGH level for a t on period by the temporary contact. The capacitor C 866 remains charged up for a period and the computer evaluates the level. After the reset pulse via 0 806, R 806 and T 808 on pin 20, lC 810, pin 28, IC 860, the computer samples pin 18, IC 810. it this is at LOW, the microprocessor identifies that the receiver has been switched on with the mains plug.

Control Unit (Master Processor) (IC 860)

The control computer in this circuit, the microprocessor IC 860, obtains its program from the EPROM IC 850. The microprocessor is used tor driving the display, scanning the keyboard, switching over the EURO-AV socket, the IF, the colour module, the Teletext decoder, as well as controlling the data traffic between the modules and the data memory IC 360.

The microprocessor feeds out pulses from pins 34-36 at a rhythm of 2 msec. When a button is depressed, these pulses are applied to the input pins 31-33. From this the computer identifies the button which has been depressed.

The display drive is carried out in time multiplex mode from the output ports 48-50 of the microprocessor. The transistors T 802, T 804 and T 806 produce the anode voltage for the LEDs at a 2 msec rate. The data for the digits are present on the pins 16-21. On reception of the enable signal (PBO, pin 37)the information for the display LEDs is fed out from pins 19,21 (PC bus) in serial into the shift register of the LED driver (IC 830) and is then fed out in parallel.

The data transfer with the modules and the memory is also carried out on the PC bus. The PC bus is a bidirectional two-lead bus consisting of the SDA (System Data) and SCL (System Clock) leads. Both leads are connected via the pull-up resistors R 834, R 836 to +H.

Service Mode Program

In this fault finding program the microprocessor in the operating; control unit calls up the individual modules which are connected to the PC bus and indicates them in the form of a code number on the displays if no acknowledgement occurs the module or peripheral unit is defective (eg. connection is interrupted, no operating voltage). With a receiver which is defective due to a breakdown of the lCs driven by the l=c bus very fast fault location can be carried out by calling up the following fault finding program:

1. Switch off the receiver with the mains switch.

2. when the receiver is switched on with the mains switch, depress and hold the search button " —>~ ' on the operating control unit. Three points appear in the display.

After approx. 5 seconds a code, eg. ‘E02’ will be indicated in the display if a fault is found.

The defective plug-in modulator peripheral unit can be established from the fault table; ‘E02’ is the IF memory. Additional faults which are possible, can be indicated by depressing the '+' button on the operating control unit.

if no additional faults are indicated. the display shows ‘P1’.

3. if no fault is found in the PC bus communication the display shows three points when the receiver is switched on, and after 5 seconds ‘P1 '.

Indication

‘E 01' —> NVM (digital store; SDA 3526, IC 360; chassis) no ack

‘E 02' ——> NVM 1 (IF memory; SDA 3526) no ack ‘E 03' —> NVM 2 (tuner memory; SDA 2586, 24 C 16 no ack ‘E 04" -> DDC (Feature Box; SDA 9064) no ack ‘E 05' —> DMSD (Feature Box; SAA 9051) no ack ‘E 06’ --> DSD (Feature Box; SAA 9056) no ack ‘E 07‘ --> PLL (tuner; SDA 3202) no ack ‘E 08" --> stereo sound (IF; TDA 6611) no ack ‘E 09' --> MSG (Feature Box; SDA 9099) no ack ‘E 10' --> MOIF (Feature Box; SDA 9093) no ack ‘E 1 1' -> DA converter (encoder; TDA 8442, IC 940) no ack ‘E 12‘ --> VT Mll (Feature Box; SDA 9090) no ack ‘E 14' --> VTP (VT decoder; SDA 9241) v no ack

Emergency Data Base .

This receiver is titted with a non-volatile memory (IC 360) in which all important parameters, such as, eg. colour decoder dam or picture geometry, are stored.

in case of a fault or altered data of this lC it is possible to load a complete program with average values from the EPROM of the operating control unit into the Feature Box. When carrying out services this provides a means of establishing a possible fault in the Feature Box.

Emergency Data Base Storage

Depress and hold the Fine Tuning button and switch the receiver on with the mains button. By this action the average values of the colour decoder data and picture geometry are read from the operating control into the Feature Box. Select the Service Mode Program, set the bar to field ‘Basic Values‘ and store with the "OK" button.

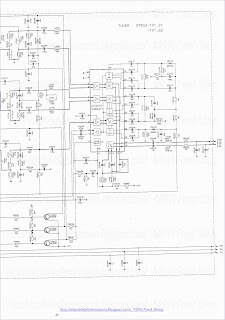

The principle functions carried out by the circuit are to chop the DC voltage at a frequency of 62.5 kHz, to transform and rectify so that the load relationship is correctly maintained on the secondaries.

The principle functions carried out by the circuit are to chop the DC voltage at a frequency of 62.5 kHz, to transform and rectify so that the load relationship is correctly maintained on the secondaries. The inductance (L) is connected to the DC voltage source (U_) via a switch (8) activated by a control circuit, so that during the conduction phase of the switch a linear rising current in the inductance causes a magnetic field to build up and for energy to be stored. The rectifying diode (D) is cutoff and decouples the secondary load from the input circuit ,/titer the switch is open, the EMF becomes effective, the diode conducts and connects the load and the charging capacitor to the inductance.

The expanded basic circuit as used In the television sets

in this expanded circuit a transformer takes over the function of the coil; the switch is replaced by a transistor. The energy source for the secondary is during the switch off l phase of the transistor via the diode (D). This switch—mode power supply with line-frequency synchronization assures a very high stable factor due to variation of the duty cycle.

stable largely independent of the mains voltage and load. The necessary information is obtained from the transformer winding 11/13 and is supplied via R 548, D 647, R 6158 and R 6157 to pin 3 of IC 6100. in parallel to this circuit, the operating voltage +A is automatically readjusted (via the opto coupler OK 6160 due to the mains isolation). This reference voltage is applied to the operational amplifier IC 6166 via R 613, Ft 612, R 611 , and to the opto coupler via R 6127. By means of the control R 611, the +A voltage is set to 161 V or 155 V, respectively (minimum brightness and contrast). At the logic block pin 2, IC 6100, double the line frequency is provided for pulse start-up. The oscillator of IC 6170 operates on 125 kHz (times the line frequency); its frequency and phase are controlled. On pin 14, the IC 6170 is synchronized with the line frequency via T 61 10, OK 6110 and T 6120. The time constant for the control of the VCO is determined by C 6171. R 6171 (pin 9 and pin 13). Due to this fact a

connection is established between the mains supply and the line deflection. In IC 6150 the frequency is divided and applied to pin 1 where it is available for the logic block via R 6152, C 6111. This 62.5 kHz frequency can be measured on pin 2 of IC 6100 using a frequency counter. In order to reduce the start-up current the operating voltage (+NE) for IC 6150 and IC 6170 is released by the transistors T 6100 and T 6105 not before U_' (pin 1, IC 6100) reaches the switching threshold of the T 6100 base voltage.

Overload cut-out clrcuit

ii the power from the mains supply circuit exceeds the permissible level the voltage dropped on the test resistor R 627 increases and tums on the transistor T 6140. Pin 5 of IC 6100 is thus connected to chassis level and the mains supply unit switches off.

The limiting of the control, as well as the overload identification is obtained from the so—called ‘collector current simulation" of the switching transistor T 634 on pin 4 of TDA 4601 in combination with R 638 and C 6151.

Due to the mains isolation, a data transfer from the secondary to the primary side is only possible via opto couplers.

Stand-by mode

On stand-by mode the blocking—oscillator converter mains stage is completely switched off by the stand-by function of IC 6100 DA 4601 (pin 5; < 2.1 V). The base of transistor T 6130 is taken to HIGH. Consequently, all secondary voltages are absent.

Due to this circuit concept the power consumption on stand-by mode is reduced to about 8 Wh.

To allow the operating control unit to be in operation a separate mains supply is used to generate the +5V voltage (+H). it supplies the operating voltage for both processors IC 860 and IC 810.

1C 810 (pin 8) drives the blocking-oscillator converter mains stage via the stand-by lead and evaluates the data of the IR preamplifier (IC 1201). Communication between the master processor IC 860 and IC 810 is accomplished via the lead ‘IR Data‘ and ”lr Clock" (pin 39, 11).

Power supply Description based on TDA4601d (SIEMENS)

Semiconductor

circuit for supplying power to electrical equipment, comprising a

transformer having a primary winding connected, via a parallel

connection of a collector-emitter path of a transistor with a first

capacitor, to both outputs of a rectifier circuit supplied, in turn, by a

line a-c voltage; said transistor having a base controlled via a second

capacitor by an output of a control circuit acted upon, in turn by the

rectified a-c line voltage as actual value and by a reference voltage;

said transformer having a first secondary winding to which the

electrical equipment to be supplied is connected; said transformer

having a second secondary winding with one terminal thereof connected to

the emitter of said transistor and the other terminal thereof connected

to an anode of a first diode leading to said control circuit; said

transformer having a third secondary winding with one terminal thereof

connected, on the one hand, via a series connection of a third capacitor

with a first resistance, to the other terminal of said third secondary

winding and connected, on the other hand, to the emitter of said

transistor, the collector of which is connected to said primary winding;

a point between said third capacitor and said first resistance being

connected to the cathode of a second diode; said control circuit having

nine terminals including a first terminal delivering a reference voltage

and connected, via a voltage divider formed of a third and fourth

series-connected resistances, to the anode of said second diode; a

second terminal of said control circuit serving for zero-crossing

identification being connected via a fifth resistance to said cathode of

said second diode; a third terminal of said control-circuit serving as

actual value input being directly connected to a divider point of said

voltage divider forming said connection of said first terminal of said

control circuit to said anode of said second diode; a fourth terminal of

said control circuit delivering a sawtooth voltage being connected via a

sixth resistance to a terminal of said primary winding of said

transformer facing away from said transistor; a fifth terminal of said

control circuit serving as a protective input being connected, via a

seventh resistance to the cathode of said first diode and, through the

intermediary of said seventh resistance and an eighth resistance, to the

cathode of a third diode having an anode connected to an input of said

rectifier circuit; a sixth terminal of said control circuit carrying

said reference potential and being connected via a fourth capacitor to

said fourth terminal of said control circuit and via a fifth capacitor

to the anode of said second diode; a seventh terminal

of said control circuit establishing a potential for pulses controlling

said transistor being connected directly and an eighth terminal of said

control circuit effecting pulse control of the base of said transistor

being connected through the intermediary of a ninth resistance to said

first capacitor leading to the base of said transistor; and a ninth

terminal of said control circuit serving as a power supply input of said

control circuit being connected both to the cathode of said first diode

as well as via the intermediary of a sixth capacitor to a terminal of

said second secondary winding as well as to a terminal of said third

secondary winding.

Semiconductor

circuit for supplying power to electrical equipment, comprising a

transformer having a primary winding connected, via a parallel

connection of a collector-emitter path of a transistor with a first

capacitor, to both outputs of a rectifier circuit supplied, in turn, by a

line a-c voltage; said transistor having a base controlled via a second

capacitor by an output of a control circuit acted upon, in turn by the

rectified a-c line voltage as actual value and by a reference voltage;

said transformer having a first secondary winding to which the

electrical equipment to be supplied is connected; said transformer

having a second secondary winding with one terminal thereof connected to

the emitter of said transistor and the other terminal thereof connected

to an anode of a first diode leading to said control circuit; said

transformer having a third secondary winding with one terminal thereof

connected, on the one hand, via a series connection of a third capacitor

with a first resistance, to the other terminal of said third secondary

winding and connected, on the other hand, to the emitter of said

transistor, the collector of which is connected to said primary winding;

a point between said third capacitor and said first resistance being

connected to the cathode of a second diode; said control circuit having

nine terminals including a first terminal delivering a reference voltage

and connected, via a voltage divider formed of a third and fourth

series-connected resistances, to the anode of said second diode; a

second terminal of said control circuit serving for zero-crossing

identification being connected via a fifth resistance to said cathode of

said second diode; a third terminal of said control-circuit serving as

actual value input being directly connected to a divider point of said

voltage divider forming said connection of said first terminal of said

control circuit to said anode of said second diode; a fourth terminal of

said control circuit delivering a sawtooth voltage being connected via a

sixth resistance to a terminal of said primary winding of said

transformer facing away from said transistor; a fifth terminal of said

control circuit serving as a protective input being connected, via a

seventh resistance to the cathode of said first diode and, through the

intermediary of said seventh resistance and an eighth resistance, to the

cathode of a third diode having an anode connected to an input of said

rectifier circuit; a sixth terminal of said control circuit carrying

said reference potential and being connected via a fourth capacitor to

said fourth terminal of said control circuit and via a fifth capacitor

to the anode of said second diode; a seventh terminal

of said control circuit establishing a potential for pulses controlling

said transistor being connected directly and an eighth terminal of said

control circuit effecting pulse control of the base of said transistor

being connected through the intermediary of a ninth resistance to said

first capacitor leading to the base of said transistor; and a ninth

terminal of said control circuit serving as a power supply input of said

control circuit being connected both to the cathode of said first diode

as well as via the intermediary of a sixth capacitor to a terminal of

said second secondary winding as well as to a terminal of said third

secondary winding.Description:

Such a blocking oscillator switching

power supply is described in the German periodical, "Funkschau" (1975)

No. 5, pages 40 to 44. It is well known that the purpose of such a

circuit is to supply electronic equipment, for example, a television

set, with stabilized and controlled supply voltages. Essential for such

switching power supply is a power switching transistor i.e. a bipolar

transistor with high switching speed and high reverse voltage. This

transistor therefore constitutes an important component of the control

element of the control circuit. Furthermore, a high operating frequency

and a transformer intended for a high operating frequency are provided,

because generally, a thorough separation of the equipment to be supplied

from the supply naturally is desired. Such switching power supplies may

be constructed either for synchronized or externally controlled

operation or for non-synchronized or free-running operation. A blocking

converter is understood to be a switching power supply in which power is

delivered to the equipment to be supplied only if the switching

transistor establishing the connection between the primary coil of the

transformer and the rectified a-c voltage is cut off. The power

delivered by the line rectifier to the primary coil of the transformer

while the switching transistor is open, is interim-stored in the

transformer and then delivered to the consumer on the secondary side of

the transformer with the switching transistor cut off.

Such a blocking oscillator switching

power supply is described in the German periodical, "Funkschau" (1975)

No. 5, pages 40 to 44. It is well known that the purpose of such a

circuit is to supply electronic equipment, for example, a television

set, with stabilized and controlled supply voltages. Essential for such

switching power supply is a power switching transistor i.e. a bipolar

transistor with high switching speed and high reverse voltage. This

transistor therefore constitutes an important component of the control

element of the control circuit. Furthermore, a high operating frequency

and a transformer intended for a high operating frequency are provided,

because generally, a thorough separation of the equipment to be supplied

from the supply naturally is desired. Such switching power supplies may

be constructed either for synchronized or externally controlled

operation or for non-synchronized or free-running operation. A blocking

converter is understood to be a switching power supply in which power is

delivered to the equipment to be supplied only if the switching

transistor establishing the connection between the primary coil of the

transformer and the rectified a-c voltage is cut off. The power

delivered by the line rectifier to the primary coil of the transformer

while the switching transistor is open, is interim-stored in the

transformer and then delivered to the consumer on the secondary side of

the transformer with the switching transistor cut off. In the blocking converter described in the aforementioned reference in the literature, "Funkschau" (1975), No. 5, Pages 40 to 44, the power switching transistor is connected in the manner defined in the introduction to this application. In addition, a so-called starting circuit is provided. Because several diodes are generally provided in the overall circuit of a blocking oscillator according to the definition provided in the introduction hereto, it is necessary, in order not to damage these diodes, that due to the collector peak current in the case of a short circuit, no excessive stress of these diodes and possibly existing further sensitive circuit parts can occur.

Considering

the operation of a blocking oscillator, this means that, in the event of

a short circuit, the number of collector current pulses per unit time

must be reduced. For this purpose, a control and regulating circuit is provided.

Simultaneously, a starting circuit must bring the blocking converter

back to normal operation when the equipment is switched on, and after

disturbances, for example, in the event of a short circuit. The starting

circuit shown in the literature reference "Funkschau" on Page 42

thereof, differs to some extent already from the conventional d-c

starting circuits. It is commonly known for all heretofore known

blocking oscillator circuits, however, that a thyristor or an equivalent

circuit replacing the thyristor is essential for the operation of the

control circuit.

Considering

the operation of a blocking oscillator, this means that, in the event of

a short circuit, the number of collector current pulses per unit time

must be reduced. For this purpose, a control and regulating circuit is provided.

Simultaneously, a starting circuit must bring the blocking converter

back to normal operation when the equipment is switched on, and after

disturbances, for example, in the event of a short circuit. The starting

circuit shown in the literature reference "Funkschau" on Page 42

thereof, differs to some extent already from the conventional d-c

starting circuits. It is commonly known for all heretofore known

blocking oscillator circuits, however, that a thyristor or an equivalent

circuit replacing the thyristor is essential for the operation of the

control circuit. It is accordingly an object of the invention to provide another starting circuit. It is a further object of the invention to provide a possible circuit for the control circuit which is particularly well suited for this purpose. It is yet another object of the invention to provide such a power supply which is assured of operation over the entire range of line voltages from 90 to 270 V a-c, while the secondary voltages and secondary load variations between no-load and short circuit are largely constant.

With the foregoing and other objects in view, there is

provided, in accordance with the invention, a blocking oscillator-type

switching power supply for supplying power to electrical equipment

wherein a primary winding of a transformer, in series with an

emitter-collector path of a first bipolar transistor, is connected to a

d-c voltage obtained by rectification of a line a-c voltage fed-in via

two external supply terminals, a secondary winding of the transformer

being connectible to the electrical equipment for supplying power

thereto, the first bipolar transistor having a base controlled by the

output of a control circuit acted upon, in turn, by the rectified a-c

line voltage as actual value and by a set-point transmitter, and

including a starting circuit for further control of the base of the

first bipolar transistor, including a first diode in the starting

circuit having an anode directly connected to one of the supply

terminals supplied by the a-c line voltage and a cathode connected via a

resistor to an input serving to supply power to the control circuit,

the input being directly connected to a cathode of a second diode, the

second diode having an anode connected to one terminal of another

secondary winding of the transformer, the other secondary winding having

another terminal connected to the emitter of the first bipolar

transmitter.

With the foregoing and other objects in view, there is

provided, in accordance with the invention, a blocking oscillator-type

switching power supply for supplying power to electrical equipment

wherein a primary winding of a transformer, in series with an

emitter-collector path of a first bipolar transistor, is connected to a

d-c voltage obtained by rectification of a line a-c voltage fed-in via

two external supply terminals, a secondary winding of the transformer

being connectible to the electrical equipment for supplying power

thereto, the first bipolar transistor having a base controlled by the

output of a control circuit acted upon, in turn, by the rectified a-c

line voltage as actual value and by a set-point transmitter, and

including a starting circuit for further control of the base of the

first bipolar transistor, including a first diode in the starting

circuit having an anode directly connected to one of the supply

terminals supplied by the a-c line voltage and a cathode connected via a

resistor to an input serving to supply power to the control circuit,

the input being directly connected to a cathode of a second diode, the

second diode having an anode connected to one terminal of another

secondary winding of the transformer, the other secondary winding having

another terminal connected to the emitter of the first bipolar

transmitter.  In

accordance with another feature of the invention, there is provided a

second bipolar transistor having the same conduction type as that of the

first bipolar transistor and connected in the starting circuit with the

base thereof connected to a cathode of a semiconductor diode, the

semiconductor diode having an anode connected to the emitter of the

first bipolar transistor, the second bipolar transistor having a

collector connected via a resistor to a cathode of the first diode in

the starting circuit, and having an emitter connected to the input

serving to supply power to the control circuit and also connected to the

cathode of the second diode which is connected to the other secondary

winding of the transformer.

In

accordance with another feature of the invention, there is provided a

second bipolar transistor having the same conduction type as that of the

first bipolar transistor and connected in the starting circuit with the

base thereof connected to a cathode of a semiconductor diode, the

semiconductor diode having an anode connected to the emitter of the

first bipolar transistor, the second bipolar transistor having a

collector connected via a resistor to a cathode of the first diode in

the starting circuit, and having an emitter connected to the input

serving to supply power to the control circuit and also connected to the

cathode of the second diode which is connected to the other secondary

winding of the transformer. In accordance with a further feature of the invention, the base of the second bipolar transistor is connected to a resistor and via the latter to one pole of a first capacitor, the anode of the first diode being connected to the other pole of the first capacitor.

In accordance with an added feature of the invention, the input serving to supply power to the control circuit is connected via a second capacitor to an output of a line rectifier, the output of the line rectifier being directly connected to the emitter of the first bipolar transistor.

In accordance with an additional feature of the invention, the other secondary winding is connected at one end to the emitter of the first bipolar transistor and to a pole of a third capacitor, the third capacitor having another pole connected, on the one hand, via a resistor, to the other end of the other secondary winding and, on the other hand, to a cathode of a third diode, the third diode having an anode connected via a potentiometer to an actual value input of the control circuit and, via a fourth capacitor, to the emitter of the first bipolar transistor.

In accordance with yet another feature of the invention, the control circuit has a control output connected via a fifth capacitor to the base of the first bipolar transistor for conducting to the latter control pulses generated in the control circuit.

In accordance with a concomitant feature of the invention, there is provided a sixth capacitor shunting the emitter-collector path of the first transistor.

Other features which are considered as characteristic for the invention are set forth in the appended claim.

Although

the invention is illustrated and described herein as embodied in a

blocking oscillator type switching power supply, it is nevertheless not

intended to be limited to the details shown, since various modifications

and structural changes may be made therein without departing from the

spirit of the invention and within the scope and range of equivalents of

the claims.

Although

the invention is illustrated and described herein as embodied in a

blocking oscillator type switching power supply, it is nevertheless not

intended to be limited to the details shown, since various modifications

and structural changes may be made therein without departing from the

spirit of the invention and within the scope and range of equivalents of

the claims. 100HZ DIGITAL TELEVISION PICTURE SCAN TECHNOLOGY OVERVIEW

Various principles were discussed for the 50/100 Hz conversion. The semi -image repetition was seen as a good compromise in terms of performance and effort, since no adaptation to movement sequences was required. The semi -picture (20 ms) received by the transmitter was stored in a semi -screen memory and then displayed twice on the screen with a half -screen duration of 10 ms. In order to be able to manufacture a large surface -flicker device as quickly as possible, the use of customer -specific circuits was dispensed with. Therefore, digital CCD memory (317 kbit) had to be used as memory circuits, since these required a significantly lower control expenditure for the storage control built up with standard logic circuits (74f ..., 74ls ..., 74HCT ...) .

This digital CCD memory (SAA 9001 from Valvo) had a serial structure. When used in a standard conversion, this meant to double the semi -screen that two semi -image memory were required. One was described with the current transmitter half picture, while the other, which contained the previous half picture, was read twice from and its content was shown on the screen. This disadvantage of the serial storage structure of the digital CCD storage, which required the storage capacity in large surface flicker exemption, was accepted to keep time to market for the basic 100 Hz television.

Inserting the CTI circuit after the D/A conversion made it possible to drastically reduce the sampling rate for the two color difference signals. Since the color remote-long-standing components (Y50),-(R-Y) 50 and-(B-Y) 50 were digitized, PAL/Secam operation was possible. There was deliberately dispensed with NTSC reproduction, since this would have required an elaborate storage control switchover (60 half-picture/s).

In an arrangement for converting an original picture signal representing

a sequence of frames, each of which is composed of two interlaced

fields, into a converted picture signal which has a double field

frequency with respect to the original picture signal, is for doubling

the field frequency, for the purpose of noise reduction, motion

compensation and line flicker reduction, a memory arrangement (1, 2)

provided for doubling the field frequency, which memory arrangement

precedes a motion compensation arrangement (5) whose output signal is

applied to a noise reduction arrangement (6), and a line flicker

reduction arrangement (7) is provided which receives the output signals

from the noise reduction arrangement (6) and the motion compensation

arrangement (5), while the converted picture signal is obtained from the

output signal of the noise reduction arrangement (6), the line flicker

reduction arrangement (7) or the motion compensation arrangement (5),

dependent on the position with respect to time of a field to be

generated of the converted picture signal. ( U.S. Philips Corporation)

In an arrangement for converting an original picture signal representing

a sequence of frames, each of which is composed of two interlaced

fields, into a converted picture signal which has a double field

frequency with respect to the original picture signal, is for doubling

the field frequency, for the purpose of noise reduction, motion

compensation and line flicker reduction, a memory arrangement (1, 2)

provided for doubling the field frequency, which memory arrangement

precedes a motion compensation arrangement (5) whose output signal is

applied to a noise reduction arrangement (6), and a line flicker

reduction arrangement (7) is provided which receives the output signals

from the noise reduction arrangement (6) and the motion compensation

arrangement (5), while the converted picture signal is obtained from the

output signal of the noise reduction arrangement (6), the line flicker

reduction arrangement (7) or the motion compensation arrangement (5),

dependent on the position with respect to time of a field to be

generated of the converted picture signal. ( U.S. Philips Corporation)

1. A system for converting an original picture signal representing a sequence of frames, each of which is composed of two interlaced fields, into a converted picture signal which has a double field frequency with respect to the original picture signal, comprising: a memory for doubling each field of the original picture signal, a motion compensation circuit receiving an output signal from the memory, a noise reduction circuit receiving an output signal from the motion compensation circuit, a line flicker reduction circuit receiving output signals from the noise reduction circuit and the motion compensation circuit and a multiplexer for generating a converted picture signal that is obtained from the output signals of the noise reduction circuit, the line flicker reduction circuit or the motion compensation circuit, dependent on position with respect to time of each field to be generated of the converted picture signal with respect to the original picture signal.

2. The system as claimed in claim 1, wherein said memory comprises a first field memory, the original picture signal being written into the first field memory and read from the first field memory at a double field frequency, each field being consecutively read twice, and wherein said system comprises a second field memory into which each field read for the second time from the first field memory is written after said each field read for the second time has passed through the noise reduction circuit.

3. The system as claimed in claim 2, wherein the first

and second field memories precede a line memory which buffers a picture

line of one of the output signals of the first and second field

memories.

3. The system as claimed in claim 2, wherein the first

and second field memories precede a line memory which buffers a picture

line of one of the output signals of the first and second field

memories. 4. The system as claimed in claim 1, wherein the line flicker reduction circuit comprises a median filter receiving three input signals each having an amplitude values, one of the input signals having an amplitude value between the other two amplitude values, the median filter supplying as an output signal the one input signal.

5. The system as claimed in claim 3, wherein the motion compensation circuit receives the output signals of the first and second field memories and the line memory, and in that the motion compensation circuit determines a motion vector from two consecutive fields of the original picture signal read from the field memories, said motion vector indicating motion between the two fields for a group of pixels of these fields.

6. The system as claimed in claim 2, wherein the line flicker reduction circuit is a median filter receiving three input signals each having an amplitude values, one of the input signals having an amplitude value between the other two amplitude values, the median filter supplying as an output signal the one input signal.

7. The system as claimed in claim 3, wherein the line flicker reduction circuit is a median filter receiving three input signals each having an amplitude values, one of the input signals having an amplitude value between the other two amplitude values, the median filter supplying as an output signal the one input signal.

8. The system as claimed in claim 5, wherein the multiplexer generates a sequence of four fields of the converted picture signal corresponding to two fields of a frame of the original picture signal, a first field of the sequence being obtained from the output signal of the noise reduction circuit, a second and a third field of the sequence being obtained from the output signal of the line flicker reduction circuit, and a fourth field of the sequence being obtained from the output signal of the motion compensation circuit.

9. A system for converting an original picture signal representing a sequence of frames, each of which is composed of two interlaced fields, into a converted picture signal which has a double field frequency with respect to the original picture signal, comprising: a memory for doubling each field of the original picture signal,a motion compensation circuit receiving an output signal from the memory, a noise reduction circuit receiving an output signal from the motion compensation circuit, a line flicker reduction circuit receiving output signals from the noise reduction circuit and the motion compensation circuit and a multiplexer for generating a converted picture signal that is obtained from the output signals of the noise reduction circuit, the line flicker reduction circuit or the motion compensation circuit, dependent on position with respect to time of each field to be generated of the converted picture signal with respect to the original picture signal,

wherein the multiplexer generates a sequence of four fields

of the converted picture signal corresponding to two fields of a frame

of the original picture signal, a first field of the sequence being

obtained from the output signal of the noise reduction circuit, a second

and a third field of the sequence being obtained from the output signal

of the line flicker reduction circuit, and a fourth field of the

sequence being obtained from the output signal of the motion

compensation circuit.

wherein the multiplexer generates a sequence of four fields

of the converted picture signal corresponding to two fields of a frame

of the original picture signal, a first field of the sequence being

obtained from the output signal of the noise reduction circuit, a second

and a third field of the sequence being obtained from the output signal

of the line flicker reduction circuit, and a fourth field of the

sequence being obtained from the output signal of the motion

compensation circuit.10. The system as claimed in claim 9, wherein in generating the first field of the sequence, the multiplexer obtains a value of each pixel of a line position x in a picture line y by addition of a value, multiplied by a factor k, of a pixel of a line position x-vx in a line y+1 of a last field of the original picture signal transmitted before a corresponding frame of the original picture signal,

and a value, multiplied by a factor 1-k, of a pixel of the line position x of the picture line y of a first field of the corresponding frame of the original picture signal, the value vx being a motion vector supplied by the motion compensation circuit and the value k determining a measure of noise reduction.

11. The system as cla

imed in claim 9, wherein in

generating the second field of the sequence, the multiplexer obtains a

value of each pixel of a line position x in a picture line y by median

filtering from a value of a pixel of a line position x+(vx.1/2) in a line y+1 of a first field of a corresponding frame of the original picture signal,

imed in claim 9, wherein in

generating the second field of the sequence, the multiplexer obtains a

value of each pixel of a line position x in a picture line y by median

filtering from a value of a pixel of a line position x+(vx.1/2) in a line y+1 of a first field of a corresponding frame of the original picture signal, a value of a pixel of the line position x+(vx.1/2) in a line y+1 of the first field of the corresponding frame of the original picture signal, and a value of a sum of

a value, multiplied by a factor k, of a pixel of the line position x+(vx.1/2) in the line y-1 of the first field of the corresponding frame of the original picture signal

and a value, multiplied by a factor 1-k, of a pixel of a line position x-(vx.1/2) in the line y of a second field of the corresponding frame of the original picture signal,

the value vx being a motion vector supplied by the motion compensation circuit and the value k indicating a measure of noise reduction.

12. The system as claimed in claim 9, wherein in generating the third field of the sequence, the multiplexer obtains a value of each pixel of a line position x in a picture line y by median filtering from a value of a pixel of a line position x+vx in the line y of a first field of the corresponding frame of the original picture signal,

a value of a pixel of the line position x in a line y-1 of a second

field of the corresponding frame of the original picture signal,

a value of a pixel of the line position x in a line y-1 of a second

field of the corresponding frame of the original picture signal, and a value of a sum of

a value, multiplied by a factor k, of pixel of the line position x+vx in the line y of the first field of the corresponding frame

and a value, multiplied by a factor 1-k, of a pixel of the line position x in a line y+1 of the second field of the corresponding frame of the original picture signal,

the value vx being a motion vector supplied by the motion compensation circuit and the value k determining a measure of noise reduction.

13. The system as claimed in claim 9, wherein in generating the fourth field of the sequence, the multiplexer obtains a value of each pixel of a line position x in a picture line y from a value of a pixel of a line position x+(vx.1/2) of the line y of a second field of a corresponding frame of the original picture signal, the value vx being a motion vector supplied by the motion compensation circuit.

ND OF THE INVENTION

ND OF THE INVENTIONThe invention relates to an arrangement for converting an original picture signal representing a sequence of frames, each of which is composed of two interlaced fields, into a converted picture signal which has a double field frequency with respect to the original picture signal.

When converting a picture signal into such a converted picture signal which, with respect to the original picture signal, has a double field frequency, there is the problem that every second field of the converted picture signal must be newly generated, because no corresponding field of the original picture signal is available with respect to time and also with respect to the picture information.

In simple arrangements for doubling the field frequency, every field is doubled. A moving object in the fields of the converted picture signal is imaged twice in the same position before it jumps to the next position in the two subsequent fields. Since the human eye cannot follow these jumps, it is incident on the average speed of motion and observes a moving object from field to field at different positions. This leads to a double structure and motion blurr.

In other arrangements for field

doubling of a picture signal a motion compensation is therefore provided

by means of which the motion between two fields of the original picture

signal is determined so that the motion can be taken into account in

fields of the converted picture signal to be generated therebetween as a

function of time and a corresponding interpolation can be performed.

However, such arrangements have the further problem that possibly

present noise is also to be reduced and that the line flicker, which

still occurs in spite of the doubling of the field frequency in picture

signals generated by way of interlaced scanning, is to be reduced. In

the state of the art arrangements are only known in which a motion

compensation is combined either with a noise reduction or with a line

flicker reduction.

In other arrangements for field

doubling of a picture signal a motion compensation is therefore provided

by means of which the motion between two fields of the original picture

signal is determined so that the motion can be taken into account in

fields of the converted picture signal to be generated therebetween as a

function of time and a corresponding interpolation can be performed.

However, such arrangements have the further problem that possibly

present noise is also to be reduced and that the line flicker, which

still occurs in spite of the doubling of the field frequency in picture

signals generated by way of interlaced scanning, is to be reduced. In

the state of the art arrangements are only known in which a motion

compensation is combined either with a noise reduction or with a line

flicker reduction.SUMMARY OF THE INVENTION

It is an object of the invention to provide an arrangement in which the motion of the picture contents during generation of the compensated fields is taken into account when converting the picture signal into a converted picture signal at the double field frequency, and which moreover allows a noise reduction of the picture signal and a line flicker reduction.

According to the invention this object is solved in that for doubling the field frequency a memory arrangement is provided which precedes an arrangement for motion compensation whose output signal is applied to an arrangement for noise reduction, in that an arrangement for line flicker reduction is provided which receives the output signals from the noise reduction arrangement and the motion compensation arrangement and in that the converted picture signal is obtained from the output signal of the noise reduction arrangement, the line flicker reduction arrangement or the motion compensation arrangement, dependent on the position with respect to time of a field to be generated of the converted picture signal.

The actual the field frequency doubling is obtained by means of a memory arrangement. Consequently, the fields of the original picture signal are repeated at the double frequency so that a double field frequency is realised. However, this signal still has the above-mentioned errors.

An arrangement for motion compensation is therefore provided, which arrangement determines motions in the original picture signal and, with reference to the known motions, allows a compensation of this motion in the new fields to be generated of the compensated signal.

The arrangement for motion compensation precedes an arrangement for noise reduction which combines the data of two consecutive fields for the purpose of noise reduction.

Furthermore, an arrangement for line flicker reduction is provided which receives the output signals from the motion compensation arrangement and the output signals from the noise reduction arrangement.

The output signal of the arrangement, i.e. the converted picture signal of the double field frequency, is obtained from the output signal of one of said three arrangements in dependence upon the position with respect to time of a field to be generated of the converted picture signal. This alternation between the output signals of the arrangements is advantageous because different errors occur, dependent on the position with respect to time of the fields of the converted picture signal.

In some fields a motion compensation is

required because these fields occur with respect to time between two

fields of the original picture signal. This is not required for those

fields which coincide with pictures of the original picture signal. The

line flicker reduction is in its turn only required for those fields

which as a consequence of the interlaced scanning method do not have the

correct vertical position as compared with the fields of the original

picture signal from which they are generated.

In some fields a motion compensation is

required because these fields occur with respect to time between two

fields of the original picture signal. This is not required for those

fields which coincide with pictures of the original picture signal. The

line flicker reduction is in its turn only required for those fields

which as a consequence of the interlaced scanning method do not have the

correct vertical position as compared with the fields of the original

picture signal from which they are generated. The arrangement according to the invention thus offers a combination of motion compensation with line flicker reduction and noise reduction.

An embodiment of the arrangement is characterized in that the original picture signal is written into a first field memory from which it is read at the double frequency, each field being consecutively read twice, and in that a second field memory is provided into which each field read for the second time from the first field memory is written after it has passed through the noise reduction arrangement.

The first field memory is thus used for doubling the field frequency. Each field written into this memory is read twice consecutively. A second field memory already operates at this double field frequency at the input side, because each field, which was read from the first field memory for the second time and has passed through the noise reduction arrangement, is written into this second field memory. After this noise-reduced field has been written into the memory, it is available at the output of the second field memory.

Consequently, two fields of the original picture signal, however, with a doubled field frequency are available at the outputs of the two field memories for the motion compensation arrangement. One of these fields is already noise-reduced, which simplifies the determination of motion by the motion compensation arrangement.

A further embodiment of the invention is

characterized in that the two field memories precede a line memory which

buffers a picture line of one of the output signals of the two fields.

For one of the fields information of two consecutive picture lines is

thus time-parallel available, which is advantageous for the subsequent

line flicker reduction.

A further embodiment of the invention is

characterized in that the two field memories precede a line memory which

buffers a picture line of one of the output signals of the two fields.

For one of the fields information of two consecutive picture lines is

thus time-parallel available, which is advantageous for the subsequent

line flicker reduction. In a further embodiment of the invention the arrangement for line flicker reduction may advantageously be a median filter whose output supplies that input signal which has the middle amplitude value of the input signals.

In accordance with a further embodiment of the invention the arrangement for motion compensation receives the output signals of the two field memories and the line memory, which motion compensation arrangement determines a motion vector from the two consecutive fields of the original picture signal read from the field memories, which motion vector indicates the motion between the two fields for a group of pixels of these fields.

This motion vector may be used for motion compensation in those fields of the converted field signal which occur with respect to time between two fields of the original picture signal.

A further embodiment of the invention is characterized in that the arrangement generates a sequence of four fields (A1100,B1-100,B1*100,B1+100) of the converted picture signal corresponding to two fields of a frame of the original picture signal, the first field (A1100) of the sequence being obtained from the output signal of the noise reduction arrangement, the second and third fields (B1-100,B1*100) of the sequence being obtained from the output signal of the line flicker reduction arrangement and the fourth field (B1+100) of the sequence being obtained from the motion compensation arrangement.

As a consequence of the doubled field frequency of the converted picture signal, four fields of the converted picture signal must be generated in a time range in which two fields of the original picture signal are present. These two fields of the original picture signal and the four fields of the corresponding sequence of the converted picture signal will hereinafter be referred to as corresponding fields and corresponding sequence, respectively.

The first field of the sequence is obtained from the output signal of the noise reduction arrangement. This is possible because this first field of the sequence has the right position with respect to time and location as compared with the first corresponding field of the original picture signal and because only a noise reduction is to be performed.

The second and third fields of the sequence are obtained from the output signal of the line flicker reduction arrangement, because the two fields of the original picture signal must be utilized for these two fields, at

least

one of which does not have the correct position with respect to time and

neither has the correct vertical position due to the interlaced

scanning method used.

least

one of which does not have the correct position with respect to time and

neither has the correct vertical position due to the interlaced

scanning method used. The signal for the fourth field of the sequence is obtained from the motion compensation arrangement, because this signal can only be obtained from the second corresponding field of the original picture signal due to use of motion compensation.

The further sub-claims state how the arrangement advantageously generates the four fields for the sequence of converted picture signals from the corresponding two fields of the original picture signal.

These and other aspects of the invention will be apparent from and elucidated with reference to the embodiments described hereinafter.

BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 shows a block diagram of the arrangement according to the invention for converting an original picture signal into a converted picture signal of the double field frequency,

FIG. 2 shows a Table of the fields written into and read from the memory arrangement according to FIG. 1,

FIG. 3 shows a diagram in accordance with which the arrangement of FIG. 1 generates the first field of a sequence of the converted picture signal,

FIG. 4 is a representation, corresponding to FIG. 3, of the second field of the sequence,

FIG. 5 is a representation, corresponding to FIG. 3, of the third field of the sequence, and

FIG. 6 is a representation, corresponding to FIG. 3, of the fourth field of the sequence.

DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS OF THE INVENTION

FIG. 1 shows a block diagram of the arrangement according to the invention, which arrangement allows the field frequency of an original picture signal to be doubled and thus generates a converted picture signal, which gen

erated picture signal is noise-reduced, and which performs, if

necessary, a motion compensation and a line flicker reduction for the

fields.

erated picture signal is noise-reduced, and which performs, if

necessary, a motion compensation and a line flicker reduction for the

fields. The arrangement of FIG. 1 is divided into two blocks, the first block processing the received luminance signal component Y50 of the original picture signal and the second block processing the received chrominance signal component C50 of the original picture signal. In the embodiment shown in FIG. 1 the chrominance signal is doubled only with respect to its frequency. The special procedures of noise reduction and line flicker reduction are performed only for the luminance signal in the embodiment shown in FIG. 1. However, it is alternatively possible to take these measures both for the luminance signal and for the chrominance signal.

In the arrangement shown in FIG. 1 the luminance signal component Y50 of the original picture signal is applied to a first field memory 1 by means of which the field frequency of this signal is doubled. Each field of the original picture signal written into the field memory 1 is subsequently read twice. This reading process is performed at the double frequency. A simple doubling of the field frequency is thus already performed. However, the output signal of this field memory is only suitable for display if motion disturbances and line flicker are accepted. Furthermore, a second field memory 2 is provided whose input receives field signals to be described hereinafter, which signals already have the double field frequency. The signals of two consecutive fields of the original picture signal are parallel available at the outputs of the two field memories 1 and 2, which fields have already been doubled in field frequency.

The two field memories 1 and 2

are followed by a multiplexer 3 allowing one of the output signals of

the field memories 1 and 2 to be alternatively applied to a line memory

4. The output signals of the two field memories 1 and 2 are applied to a

motion compensation arrangement 5 via the multiplexer 3. The

arrangement 5 thus receives the signals of the two field memories 1 and 2

and hence two consecutive fields of the original picture signal whose

field frequencies have already been doubled. By using the line memory 4,

the values of two pixels of the same line position of consecutive

picture lines are simultaneously available for one of the two field

signals.

The two field memories 1 and 2

are followed by a multiplexer 3 allowing one of the output signals of

the field memories 1 and 2 to be alternatively applied to a line memory

4. The output signals of the two field memories 1 and 2 are applied to a

motion compensation arrangement 5 via the multiplexer 3. The

arrangement 5 thus receives the signals of the two field memories 1 and 2

and hence two consecutive fields of the original picture signal whose

field frequencies have already been doubled. By using the line memory 4,

the values of two pixels of the same line position of consecutive

picture lines are simultaneously available for one of the two field

signals. The motion compensation arrangement 5 determines, from the two fields apply thereto, a motion which is present in the picture contents between these two fields. Advantageously, a motion vector indicating the motion between the two fields for a group of pixels is obtained from this determined motion for a group of pixels. The motion compensation arrangement 5 can determine this motion both in the horizontal direction and in the vertical direction, i.e. in the line direction as well as in the direction perpendicular to the lines. However, the motion may exclusively be determined in the line direction, which is much easier to realise in the circuit construction and also yields good results.

The arrangement shown in FIG. 1 also includes a noise reduction arrangement 6. This arrangement 6 may operate in known manner in which it combines the signals of pixels of the same location in consecutive fields. These signals are applied from the arrangement 5 to the arrangement 6. Since the arrangement 5 has already determined the corresponding motion vector, the noise reduction in the arrangement 6 can already be performed with motion-compensated signals.

The output signal of the noise reduction arrangement 6 is applied to the input of the second field memory 2, to an input of a line flicker reduction arrangement 7 and to a first input of a multiplexer 8. A signal which is already noise-reduced is thus written into the field memory 2 at the input side, which signal corresponds to that field which is read from the first field memory 1 for the second time already.

The line flicker reduction arrangement 7 which may be, for example a median filter and which selects, from the signals applied thereto, the signal with the middle instantaneous amplitude value, not only receives the output signal from the arrangement 6 but also the output signal from the motion compensation arrangement 5, because this outp

ut signal also

contains the motion-compensated output signal of the line memory 4. This

is necessary because a vertical interpolation must be performed for the

line flicker reduction and consequently the pixels corresponding to the

signals of two lines should be available, i.e. pixels of the same

location in their line.

ut signal also

contains the motion-compensated output signal of the line memory 4. This

is necessary because a vertical interpolation must be performed for the

line flicker reduction and consequently the pixels corresponding to the

signals of two lines should be available, i.e. pixels of the same

location in their line. The line flicker reduction arrangement 7 not only receives these signals of two successive picture lines of a field from the arrangement 6 but also the signal of another field. In a manner to be described hereinafter a median filtering of these signals is performed, which leads to a line flicker reduction.

The output signal of the line flicker reduction arrangement 7 is applied to a second input of the multiplexer 8. A third input of the multiplexer 8 receives the output signal from the noise reduction arrangement 5.

At the output, the multiplexer 8 supplies the luminance signal Y100 which represents the converted picture signal and which has a doubled field frequency as compared with the input signal Y50. In a manner to be described hereinafter, the multiplexer 8 is switched between its three inputs dependent on the field to be generated.

FIG. 1 further shows a circuit block 9 in which the field frequency of the chrominance signal component C50 of the original picture sign

al is doubled. This can be effected in the

same way as for the luminance signal but alternatively, the field

frequency may be doubled only. At the output, the unit 9 supplies the

chrominance signal component of the converted picture signal.

al is doubled. This can be effected in the

same way as for the luminance signal but alternatively, the field

frequency may be doubled only. At the output, the unit 9 supplies the

chrominance signal component of the converted picture signal. FIG. 2 shows a Table indicating diagrammatically which fields are written into or read from the field memories 1 and 2 shown in FIG. 1.

Two consecutive fields of the original picture signal are denoted by A1, B1 and A2, B2, etc. in an unchanged form. Two fields having the same cipher form part of a frame. The two fields are generated in accordance with the interlaced scanning method.

As is shown in the Table of FIG. 2, for example two fields A1 and B1 of a frame of the original picture signal are written into the field memory 1 of FIG. 1, which field memory is denoted by FM1 in FIG. 2. Each of these two fields is subsequently read twice from the

field memory 1, which reading is effected at the double frequency so that the field frequency of these pictures is already doubled.

If a field is read from the first

field memory 1 for the second time, this signal reaches the input of the

field memory 2 denoted by FM2 in the Table of FIG. 2, after it has

passed through the arrangement 5 and the arrangement 6 of FIG. 1. At the

next reading step of the field memories 1 and 2, two fields whose field

frequencies have already been doubled are available at their outputs.

As one of the fields, viz. the field written into the field memory 2 has

already passed through the noise reduction arrangement, this field is

already noise-reduced which is denoted by NR in the Table of FIG. 2.

If a field is read from the first

field memory 1 for the second time, this signal reaches the input of the

field memory 2 denoted by FM2 in the Table of FIG. 2, after it has

passed through the arrangement 5 and the arrangement 6 of FIG. 1. At the

next reading step of the field memories 1 and 2, two fields whose field

frequencies have already been doubled are available at their outputs.

As one of the fields, viz. the field written into the field memory 2 has

already passed through the noise reduction arrangement, this field is

already noise-reduced which is denoted by NR in the Table of FIG. 2. The result is that two fields from the original picture signal having an already doubled field frequency are available at the outputs of the field memories 1 and 2 in FIG. 1.

It will now be explained with reference to FIGS. 3 to 6 how the four fields A1100,B1-100,B1*100 and B1+100 of the output signal Y100 as shown in the Table of FIG. 2, which are the signals of the multiplexer 8 as shown in FIG. 1, are obtained. These four fields are hereinafter assumed to be associated with a sequence. A frame of the original picture signal or two fields of this signal, viz. the fields A1 and B1 correspond to this sequence. The four fields of the sequence will hereinafter be assumed to correspond to these two fields of the original picture signal.

FIG. 3 shows diagrammatically, above a broken line, two fields B0NR and A1 of the original picture signal read from the two field memories 1 and 2 of FIG. 1. Below the broken line, a field A1100 is shown which represents the first field of a sequence of the converted picture signal. This signal of the field A1100 is to be generated by the arrangement of FIG. 1.

To this end the output signal of the first field memory 1 is used, from which field memory the field A1 of the original picture signal (at the doubled field frequency) is read. The field B0 of the original picture signal was already previously written i

n a noise-reduced form into the

field memory 2. At the output, this signal is now available as signal B0NR at the output of the second field memory simultaneously with the signal A1. The first field A1100

of the sequence is obtained from these two output signals of the field

memories 1 and 2 in accordance with the diagrammatic representation in

FIG. 3.

n a noise-reduced form into the

field memory 2. At the output, this signal is now available as signal B0NR at the output of the second field memory simultaneously with the signal A1. The first field A1100

of the sequence is obtained from these two output signals of the field

memories 1 and 2 in accordance with the diagrammatic representation in

FIG. 3. This field A1100 to be generated has the correct position vertically and with respect to time as compared with the field A1 of the original picture signal. Therefore, only a noise reduction should be carried out, and a line flicker reduction in particular is not necessary.

The output signals of the field memories 1 and 2 are utilized for the noise reduction, while it is advantageous to submit the field read from the field memory 2 and not having the correct position with respect to time as compared with the field A1100 to be generated to a motion compensation of its picture contents. The motion vector determined by the motion compensation arrangement 5 in accordance with FIG. 1 is utilized for this purpose. This motion vector is denoted by vx in FIG. 3.

For a pixel marked in picture line 3 of the field A1100 in FIG. 3, th100, as read from the field memory 1, is utilized. Moreover, the pixel of the field B0NR as read from the second field memory and offset by the motion vector vx

is used. This pixel is taken from line 4. A noise-reduced signal is

obtained from these two pixels of the two fields. A factor k is provided

for this purpose, indicating the degree of noise reduction. The pixel

from the field A1 is multiplied by a factor 1-k and the pixel from the

field B0NR is multiplied by a factor k. These two multiplied values are added and constitute the value of the marked pixel of the field A1100.

For a pixel marked in picture line 3 of the field A1100 in FIG. 3, th100, as read from the field memory 1, is utilized. Moreover, the pixel of the field B0NR as read from the second field memory and offset by the motion vector vx

is used. This pixel is taken from line 4. A noise-reduced signal is

obtained from these two pixels of the two fields. A factor k is provided

for this purpose, indicating the degree of noise reduction. The pixel

from the field A1 is multiplied by a factor 1-k and the pixel from the

field B0NR is multiplied by a factor k. These two multiplied values are added and constitute the value of the marked pixel of the field A1100. e pixel of the same line position and the same line number of the field A1

If k is chosen to be small, only a small or no noise reduction is to be performed and this pixel is essentially obtained from the corresponding pixel of the field A1. With a larger factor k, the value of the pixel is increasingly being taken from the field B0NR.

The generated field A1100 thus corresponds to the field A1 of the original picture signal, but for the performed noise reduction. It is written into the second field memory 2 of FIG. 1 and is available as A1NR for subsequent fields to be generated.

During the generation of the first field A1100 the multiplexer 8 is switched to its first input in accordance with FIG. 1, because the output signals for the noise reduction are used as output signals in accordance with the diagrammatic representation in FIG. 3 and hence as signals for the field A1100.

FIG. 4 is a representation, corresponding to FIG. 3, for obtaining the second field B1-100 of the sequence.

As compared with the two fields of the original picture signal, this second field of the sequence neither has a vertically correct position nor a correct position as regards time. Therefore, a motion compensation and a line flicker reduction are performed.

At the instant of generating this second field, the field B1 of the original picture signal is read from the first field memory and the field A1 of the original picture signal is read in a noise-reduced form from the second field memory.

In the representation in FIG. 4 a pixel of the picture line 2 is marked for the field B1-100. The value of this pixel is generated from three values by means of median filtering, which values are obtained from the fields A1NR and B1.

The

first of these values is obtained from the picture line 3 for that

pixel which, after being offset by half the motion vector (vx.1/2) has the same position as the pixel to be generated in the field B1-100. The second input signal of the median filter is obtained from the pixel of the same line position of line 1 of the field A1NR.

The value of this pixel is also multiplied by a factor k. Moreover,

that pixel of the picture line 2 of the field B1 which, after use of

half the negative motion vector (-vx.1/2) has the same picture line position as the pixel to be generated of the field B1-100

is multiplied by a factor 1-k. These two values are added and the sum

constitutes the third input signal for the median filtering. Due to the

median filtering, the input signal having the middle instantaneous

amplitude value is selected from these three input signals. This signal

is constituted by the value of the marked pixel of the second field B1-100 of the sequence.

The

first of these values is obtained from the picture line 3 for that

pixel which, after being offset by half the motion vector (vx.1/2) has the same position as the pixel to be generated in the field B1-100. The second input signal of the median filter is obtained from the pixel of the same line position of line 1 of the field A1NR.

The value of this pixel is also multiplied by a factor k. Moreover,

that pixel of the picture line 2 of the field B1 which, after use of

half the negative motion vector (-vx.1/2) has the same picture line position as the pixel to be generated of the field B1-100

is multiplied by a factor 1-k. These two values are added and the sum

constitutes the third input signal for the median filtering. Due to the

median filtering, the input signal having the middle instantaneous

amplitude value is selected from these three input signals. This signal

is constituted by the value of the marked pixel of the second field B1-100 of the sequence. As already shown in the representation according to FIG. 4, a motion compensation for all signals is required for this field. Moreover, a line flicker reduction is to be performed. Consequently, the multiplexer 8 is switched to its second input for generating the value of the field B1-100 in accordance with the representation in FIG. 1, which input receives the output signal from the line flicker reduction arrangement 7.

FIG. 5 is a representation corresponding to FIGS. 3 and 4, but in the representation according to FIG. 5 the third field B1*100 of the sequence is to be generated.

The two corresponding fields A1 and B1 of the original picture signal are used again for generating this field. The field B1 is read from the field memory 1 of FIG. 1. The field A1, which is already noise-reduced, is read from the field memory 2 of FIG. 1.

A median filtering is performed again, because the output field B1 has the incorrect vertical position. The output field A1NR additionally has the incorrect position with respect to time so that also a motion compensation has to be performed for this field.

A

median filtering of three input signals is carried out for generating

one of the pixels marked in FIG. 5, of the picture line 3 of the field

B1*100.

A

median filtering of three input signals is carried out for generating

one of the pixels marked in FIG. 5, of the picture line 3 of the field

B1*100. The first of these input signals represents the value of the pixel of the picture line 2 of the field B1, which has the same picture line position in its picture line as the pixel to be generated in its picture line. Moreover, from the field A1, as read from the second field memory, that pixel is used which after correction by the motion vector vx has the same line position as the pixel to be generated. This motion-compensated pixel represents the second input signal of the median filter. The third input signal is formed by the sum of the value of the same line position of the pixel of the picture line 4 of the field B1, multiplied by a factor 1-k, and the value of the second input signal of the median filter, multiplied by a factor k. This sum represents the third input signal of the median filter and is simultaneously written as input signal into the second field memory from which it can be read again for fields to be subsequently generated.

The multiplexer 8 of the block diagram in FIG. 1 is switched to its second input for generating the third field B1*100 of the sequence, because a line flicker reduction as well as a motion compensation have to be performed.

In FIG. 6, corresponding to the representations in FIGS. 3 to 5, the values of the fourth field B1+100 of the sequence are to be obtained.

Since the field B1 used for this purpose (in a noise-reduced form) of the original picture signal has the correct vertical position,+100, a line flicker reduction is not necessary in this case. The field B1NR has, however, the incorrect position with respect to time so that a motion compensation is necessary.

i.e. the same position as the field B1

Consequently, for a pixel as marked by way of example in FIG. 6 in picture line 2 in a given position, that pixel of the field B1NR as read from the field memory 2 is used which has the same line position as the pixel to be generated in its picture line after correction by half the motion vector (vx.1/2).