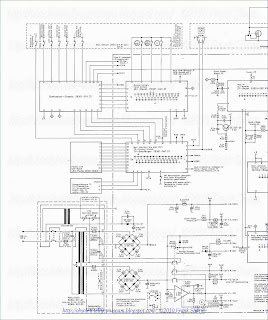

The GRUNDIG SUPER COLOR Einschub W8272 IT CHASSIS 29301-114.63 is a Semi modular chassis.

GRUNDIG SUPER COLOR Einschub W8272 IT CHASSIS 29301-114.63 First GRUNDIG with isolated Chassis from Mains, this because of isolations requirements for featuring external connectivity with VCR and audio devices.

This CHASSIS don't shares much with previous models. Line deflection stages and signal stages and other parts are differently designed and developed even if they're a classic Technology type design or that era employing Thyristor devices.

It introduces the " Stations Computer " as named GRUNDIG Synthesizer tuning system, which is a HIGLY sophisticated circuitry dedicated only to feature Frequency Synthesizer Tuning with OSD Diplaying channels.

This is realized on a separated chassis fitted on the bottom of the cabinet (see Photo)

On the same chassis is fitted the Tuner which is a special in this case type.

The circuit is based on a SIEMENS ASICs the SM574 and S047 and other circuits.

All these are NOT Ucontroller or Microprocessor based but special ICs designed for the scope.

Furthermore it eliminates the "battery backup" this because the tuning channels are stored to EAROM Memory type which was power needless.

Furthermore it has even a Time Clock feature even this with OSD on screen display clock which can be called via remote control TELEPILOT 160E.

This is realized with a special ASIC from texas Instruments.

The chassis like other GRUNDIG type has the diagnose socket to obtain quick fault search diagnose process during service.

GRUNDIG SUPER COLOR Einschub W8272 IT CHASSIS 29301-114.63 Frequency synthesizer tuning system for television receivers:(SM574 -

GRUNDIG Stations Computer Theory:

A television tuning system employs a frequency synthesizer system for establishing the tuning of the receiver. A programmable frequency divider, controlled by a reversible counter, is connected between the output of a reference oscillator and a phase comparator to which the output of the local oscillator in the tuner also is applied. The phase comparator output provides a tuning voltage for controlling the tuning of the local oscillator. A logic circuit is coupled to sense predetermined relationships of signals from a picture carrier detector, a sound carrier detector, an AFT signal, and the presence of vertical synchronization signal components for changing the count in the reversible binary counter to adjust the programmable frequency divider to compensate for channel frequency offsets which may occur in excess of the pull-in range of the AFT circuit.

As improvements continually have been made in television receivers, the number of adjustments which must be made by the viewer have been substantially reduced. One adjustment, however, which still remains in most receivers is a fine tuning adjustment. Such an adjustment is required even with receivers having automatic fine tuning (AFT or AFC) systems in them. With respect to the VHF channels, the fine tuning adjustment generally is made only when the receiver is first put into operation and then infrequently afterwards as components of the receiver age. For UHF channels, however, a fine tuning adjustment generally is required each time the UHF station is tuned in by the viewer. This is annoying and it is desirable to eliminate the need to such a fine tuning adjustment.

Copending application Ser. No. 537,692, filed Dec. 31, 1974, now U.S. Pat. No. 3,949,158, issued Apr. 6, 1976, is directed to a wide band AFT system which utilizes digital logic circuitry to extend the automatic control range of an AFT system by as much as ±2 megahertz. Such a system substantially minimizes, and in many cases eliminates, the need for fine tuning adjustments of television receivers which are rough-tuned by conventional detent-type turret tuners and the like.

It is desirable to employ channel selection systems in television receivers which permit direct selection of channels without the necessity of tuning through unused or unwanted channels to arrive at the desired channel. Many techniques have been suggested for accomplishing this. Most such direct select tuning systems employ a push button keyboard of the type commonly found in hand-held calculators or push button telephones to select the channel numbers. Decoding logic then is employed to change the keyboard information for selecting the channel into a form which effects the desired tuning of the receiver.

It is desirable to employ channel selection systems in television receivers which permit direct selection of channels without the necessity of tuning through unused or unwanted channels to arrive at the desired channel. Many techniques have been suggested for accomplishing this. Most such direct select tuning systems employ a push button keyboard of the type commonly found in hand-held calculators or push button telephones to select the channel numbers. Decoding logic then is employed to change the keyboard information for selecting the channel into a form which effects the desired tuning of the receiver.

An ideal system for converting keyboarded direct select channel information into a usable control signal for tuning the receiver is a frequency synthesizer tuning system. Generally, this is accomplished by employing a programmable frequency divider between the output of the local oscillator or tuning oscillator of the receiver and one input to a phase comparator. The other input to the phase comparator is obtained from the output of a reference oscillator; and the output of the phase comparator comprises a tuning voltage which is used to control the frequency of the local oscillator. The division ratio of the programmable frequency divider is selected directly by the channel selection keyboard. Theoretically, this type of system is ideal for eliminating the need for fine tuning adjustments of a television receiver, so long as the reference oscillator is a highly stable oscillator. But even with a highly stable reference oscillator, frequency synthesizer systems fail to maintain proper tuning of television receivers in all cases, primarily because the signals from transmitting stations are not precisely maintained at the proper frequencies.

Thus, even with frequency synthesizer systems, it is necessary to employ an AFT or AFC circuit to take care of minor mistuning variations. For the most part, a conventional AFT system having a ±1 mHz pull-in range will be sufficient for a frequency synthesizer tuning system. In master antenna TV distribution systems, however, the UHF channels, and in some instances the UHF channels, are translated to an unused VHF channel. Such distribution systems are widely used, primarily in large cities, and particularly in hotel and motel installations. When inexpensive equipment is used for the translation, the resultant carrier may be mistuned a significant amount from the proper frequency. The amount of mistuning can easily be in excess of ±1 megahertz, the normal pull-in range of a good AFT or AFC system. It can even exceed ±2 megahertz. In the case where a conventional frequency synthesizer tuning system is used, a frequency off-set of this magnitude in a master antenna distribution system, or in any other case, will result in the mistuning of the received station; and the customer has no way of adjusting the RF oscillator for the mistuning.

Thus, even with frequency synthesizer systems, it is necessary to employ an AFT or AFC circuit to take care of minor mistuning variations. For the most part, a conventional AFT system having a ±1 mHz pull-in range will be sufficient for a frequency synthesizer tuning system. In master antenna TV distribution systems, however, the UHF channels, and in some instances the UHF channels, are translated to an unused VHF channel. Such distribution systems are widely used, primarily in large cities, and particularly in hotel and motel installations. When inexpensive equipment is used for the translation, the resultant carrier may be mistuned a significant amount from the proper frequency. The amount of mistuning can easily be in excess of ±1 megahertz, the normal pull-in range of a good AFT or AFC system. It can even exceed ±2 megahertz. In the case where a conventional frequency synthesizer tuning system is used, a frequency off-set of this magnitude in a master antenna distribution system, or in any other case, will result in the mistuning of the received station; and the customer has no way of adjusting the RF oscillator for the mistuning. It is desirable to automatically correct for frequency offsets in a frequency synthesizer tuning system without affecting the operation of the conventional frequency synthesizer in the tuning system. If this can be accomplished, the obvious advantages of frequency synthesizers in a television tuning system can be realized without the attendant disadvantages which otherwise exist when there is a frequency offset in the signal of the station to which the receiver is being tuned, whether such offset is created by a master antenna TV distribution or results from some other cause.

Accordingly, it is an object of this invention to provide an improved tuning system for a television receiver.

It is an additional object of this invention to provide an improved frequency synthesizer tuning system for a television receiver.

It is another object of this invention to provide an improved frequency synthesizer tuning system for a television receiver which includes a provision for adjusting the synthesizer loop for frequency offsets in the received signal.

It is a further object of this invention to tune the local RF oscillator of a television receiver to the correct frequency with a frequency synthesizer tuning system, and to automatically change the reference frequency if the AFT signal produced by the AFT discriminator of the receiver is outside a predetermined window.

In accordance with a preferred embodiment of this invention, a frequency synthesizer tuning system for a television receiver includes a stable reference oscillator and a voltage controlled local oscillator in the tuner. A programmable frequency divider is connected between the output of the reference oscillator and one input to a phase comparator, the other input of which is supplied with the output of the local oscillator. The output of the phase comparator then comprises a control signal which is supplied to the local oscillator to control the frequency of its operation.

Selection of a desired channel by the viewer causes a predetermined division ratio to be established in the programmable frequency divider each time a channel is selected. In addition, however, a control circuit coupled to the output of the AFT circuit changes the division ratio of the programmable frequency divider whenever predetermined signal conditions exist in the AFT signal. This, then, permits the system to adjust for frequency offsets of the received signal which otherwise would cause the station to be mistuned, if a conventional frequency synthesizer tuning system were used.

As described in the above-mentioned copending application, one adjustment which still generally must be made in most television receivers is a fine tuning adjustment. The system disclosed in the above copending application is directed to a frequency synthesizer tuning system having a wide pull-in range and operating to automatically correct for frequency offsets without affecting the operation of the conventional frequency synthesizer in the tuning system used. Such a system represents a substantial improvement over systems of the prior art which either required a manual fine tuning adjustment or which merely used a conventional frequency synthesizer system without a frequency offset correction provision. The system disclosed in this copending application eliminated the need for the manual fine tuning adjustment for receivers used in strong signal areas or responding to strong transmitted signals with no interference. In addition, the automatic offset correction prevented the receiver from being erroneously mistuned when there was an offset in the transmitted carrier frequency.

While such a system appears to completely solve the problem of fine tuning adjustments in a television receiver, there are situations which arise in which the frequency synthesizer system with automatic offset frequency correction does not necessarily give the most desirable picture. This is particularly true when the television receiver is in a fringe area for the station to which it is tuned. For fringe area reception, it often is desirable to intentionally mistune the television receiver to minimize noise or interference. If this were to be done, however, in a system having the automatic offset frequency correction disclosed in the above copending application, the automatic offset correction operation of the system would tune the receiver back to the nominal "correct" tuning point. But such a tuning point for weak signals may not be what the viewer wants.

Therefore, it is desirable to include a manual fine tuning adjustment capability in a frequency synthesizer tuner having a provision for automatic correction of frequency offsets. This then would result in maximum flexibility of the tuning system under all conditions of operation of the receiver. In addition, it is desirable to provide a manual fine tuning adjustment of a frequency synthesizer television receiver which is also capable of having an automatic signal seek mode, while preventing undesirable interfering interaction of the manual fine tuning and the signal seek circuitry of the receiver.

Accordingly, it is an object of this invention to provide an improved tuning system for a television receiver.

It is an additional object of this invention to provide an improved frequency synthesizer tuning system for a television receiver.

It is another object of this invention to provide an improved frequency synthesizer tuning system for a television receiver which includes a provision for adjusting the synthesizer loop for frequency offsets of the received signal, and, in addition, has a provision for permitting manual fine tuning adjustments of the frequency synthesizer loop.

It is a further object of this invention to provide a frequency synthesizer tuning system for a television receiver with a manual fine tuning adjustment.

In accordance with a preferred embodiment of this invention, a frequency synthesizer tuning system for the tuner of a television receiver includes a voltage controlled local oscillator in the tuner and a stable reference oscillator. A first programmable frequency divider is connected between the output of the reference oscillator and one input to a phase comparator. A second programmable frequency divider is connected between the output of the local oscillator and the other input to the phase comparator. The output of the phase comparator then comprises a control signal which is supplied to the local oscillator to control the frequency of its operation. A channel selection means is coupled with the second programmable frequency divider to establish the programmable division ratio or programmable fraction of that divider.

In accordance with a preferred embodiment of this invention, a frequency synthesizer tuning system for the tuner of a television receiver includes a voltage controlled local oscillator in the tuner and a stable reference oscillator. A first programmable frequency divider is connected between the output of the reference oscillator and one input to a phase comparator. A second programmable frequency divider is connected between the output of the local oscillator and the other input to the phase comparator. The output of the phase comparator then comprises a control signal which is supplied to the local oscillator to control the frequency of its operation. A channel selection means is coupled with the second programmable frequency divider to establish the programmable division ratio or programmable fraction of that divider. A manual fine tuning means is connected with the first programmable frequency divider to control the division ratio of the first frequency divider to establish a programmable fraction of division as desired by the operator of the manual fine tuning control means. Each time a new channel is selected by the operator of the receiver, the first programmable frequency divider is reset to a preestablished nominal division ratio.

NOTE: GRUNDIG was providing service manuals papers fitting they in the set, see photo.

This CHASSIS was mounted even in these following models:

GRUNDIG SUPER COLOR 8442

GRUNDIG SUPER COLOR 8642

GRUNDIG SUPER COLOR 8242

GRUNDIG SUPER COLOR W 8242

GRUNDIG SUPER COLOR 8942

GRUNDIG SUPER COLOR 8142

GRUNDIG SUPER COLOR Einschub W8272 IT CHASSIS 29301-114.63 LINE DEFLECTION THYRISTOR TECHNOLOGY VIEW (Thyristor Horizontal Output Circuits).

Brief Basics: LINE Scan output stages operate on the same basic principle whether

the active device used is a valve, transistor or thyristor. As a

starting point, let's remind ourselves of this principle, which was

first developed by Blumlein in 1932. The idea in its simplest form is

shown in Fig. 1. The scan coils, together with a parallel tuning

capacitor, are connected in series with a switch across the h.t. supply.

When the switch is closed - (a) - current flows through the coils,

building up linearly as required to deflect the beam from the centre to

the right-hand side of the screen. At this point the switch is opened.

The coils and the capacitor then form a resonant circuit. The magnetic

fields generated around the coils during the preceeding forward scan as

current flowed through them when the switch was closed now collapse,

charging the capacitor - (b). As a result of the resonant action the

capacitor next discharges, driving current through the coils in the

opposite direction - (c). Once more magnetic fields are generated around

the coils. This resonant action lasts for one half -cycle of

oscillation, during which the beam is rapidly deflected from the right-

hand side to the centre and then to the left-hand side of the screen.

The flyback is thus complete. If the switch is now closed again further

oscillation is prevented and, as the magnetic fields around the coils

collapse, a decaying current flows through them in the direction shown

at (d). This decaying current flow deflects the beam from the left-hand

side of the screen back towards the centre: the period during which this

occurs is often referred to as the energy recovery part of the scanning

cycle. When the current has decayed to zero we are back at the

situation shown at (a): the current through the coils reverses, driving

the beam to the right-hand side of the screen. This is a very efficient

System, since most of the energy drawn from the supply is subsequently

returned to it. There is negligible resistance in the circuit, so there

is very little power loss.

Brief Basics: LINE Scan output stages operate on the same basic principle whether

the active device used is a valve, transistor or thyristor. As a

starting point, let's remind ourselves of this principle, which was

first developed by Blumlein in 1932. The idea in its simplest form is

shown in Fig. 1. The scan coils, together with a parallel tuning

capacitor, are connected in series with a switch across the h.t. supply.

When the switch is closed - (a) - current flows through the coils,

building up linearly as required to deflect the beam from the centre to

the right-hand side of the screen. At this point the switch is opened.

The coils and the capacitor then form a resonant circuit. The magnetic

fields generated around the coils during the preceeding forward scan as

current flowed through them when the switch was closed now collapse,

charging the capacitor - (b). As a result of the resonant action the

capacitor next discharges, driving current through the coils in the

opposite direction - (c). Once more magnetic fields are generated around

the coils. This resonant action lasts for one half -cycle of

oscillation, during which the beam is rapidly deflected from the right-

hand side to the centre and then to the left-hand side of the screen.

The flyback is thus complete. If the switch is now closed again further

oscillation is prevented and, as the magnetic fields around the coils

collapse, a decaying current flows through them in the direction shown

at (d). This decaying current flow deflects the beam from the left-hand

side of the screen back towards the centre: the period during which this

occurs is often referred to as the energy recovery part of the scanning

cycle. When the current has decayed to zero we are back at the

situation shown at (a): the current through the coils reverses, driving

the beam to the right-hand side of the screen. This is a very efficient

System, since most of the energy drawn from the supply is subsequently

returned to it. There is negligible resistance in the circuit, so there

is very little power loss. ok

at the power supply requirements can be simplified (a line output

transistor must be operated in conjunction with a stabilised power

supply: this is not necessary in the thyristor circuit since regulation

can be built in). In the nature of things however there must be

disadvantages as well - and there are! First, a thyristor will not act

as a bidirectional switch.

ok

at the power supply requirements can be simplified (a line output

transistor must be operated in conjunction with a stabilised power

supply: this is not necessary in the thyristor circuit since regulation

can be built in). In the nature of things however there must be

disadvantages as well - and there are! First, a thyristor will not act

as a bidirectional switch.  A

more practical arrangement is shown in Fig. 4. A secondary winding L3

is added to Ll to provide the trigger pulse for TH2: L4, C4 and R I

provide the pulse shaping required. The tuning capacitor Ct is

rearranged as a T network: this is done to reduce the voltage across the

individual capacitors and enable smaller values to be used, all in the

interests of economy. And finally a transformer is coupled to the

circuit by C5 to make use of the flyback pulse for e.h.t. generation and

to provide other supplies. In many recent chassis THUD 1 and TH2/D2 are

encapsu- lated together, in pairs. In practical circuits L1 and L2

generally consist of a single transformer - often a transductor is used,

for convenience rather than for the transductor characteristics. This

makes practical circuits look at first glance rather different to the

basic form shown in Figs. 3 and 4. A further winding is often added to

the transformer to provide a supply for other parts of the receiver,

making the circuit look even more confusing. In addition e.h.t.

regulation, pincushion distortion correction and beam limiting circuitry

is required, and protection circuits may be incorporated.

A

more practical arrangement is shown in Fig. 4. A secondary winding L3

is added to Ll to provide the trigger pulse for TH2: L4, C4 and R I

provide the pulse shaping required. The tuning capacitor Ct is

rearranged as a T network: this is done to reduce the voltage across the

individual capacitors and enable smaller values to be used, all in the

interests of economy. And finally a transformer is coupled to the

circuit by C5 to make use of the flyback pulse for e.h.t. generation and

to provide other supplies. In many recent chassis THUD 1 and TH2/D2 are

encapsu- lated together, in pairs. In practical circuits L1 and L2

generally consist of a single transformer - often a transductor is used,

for convenience rather than for the transductor characteristics. This

makes practical circuits look at first glance rather different to the

basic form shown in Figs. 3 and 4. A further winding is often added to

the transformer to provide a supply for other parts of the receiver,

making the circuit look even more confusing. In addition e.h.t.

regulation, pincushion distortion correction and beam limiting circuitry

is required, and protection circuits may be incorporated. transformer's primary winding. By feeding a field frequency waveform to

the control winding on this transductor the line scanning is modulated

at field frequency. There is a simple but effective safety circuit in

this Grundig line output stage. If the voltage at tag c on the line

output transformer rises above 68V zener diode Di514 conducts,

triggering thyristor Ty511 into conduction with the result that the

cut-out operates. C517 is returned to chassis via a damped coil (L517)

so that the voltage transient when the efficiency diode cuts off is

attenuated. Likewise L512/C512/R512 are added to suppress the voltage

transient when the flyback thyristor Ty511 cuts off. The balancing coil

L516 is included to remove unwanted voltage spikes produced by the

thyristors.

transformer's primary winding. By feeding a field frequency waveform to

the control winding on this transductor the line scanning is modulated

at field frequency. There is a simple but effective safety circuit in

this Grundig line output stage. If the voltage at tag c on the line

output transformer rises above 68V zener diode Di514 conducts,

triggering thyristor Ty511 into conduction with the result that the

cut-out operates. C517 is returned to chassis via a damped coil (L517)

so that the voltage transient when the efficiency diode cuts off is

attenuated. Likewise L512/C512/R512 are added to suppress the voltage

transient when the flyback thyristor Ty511 cuts off. The balancing coil

L516 is included to remove unwanted voltage spikes produced by the

thyristors.  LARGELY

due to advances in colour c.r.t. scan coil design, the thyristor line

output stage has become obsolete laready in the 1981's.

LARGELY

due to advances in colour c.r.t. scan coil design, the thyristor line

output stage has become obsolete laready in the 1981's. s type used polyester capacitors, and it's no surprise that they were

inclined to give up. When replacing the tuning capacitors in a

thyristor line output stage it's essential to use polypropylene types -a

good range of axial components with values ranging from 0.001µF to

047µF is available from RS Components, enabling even non-standard values

to be made up from an appropriate combination. Using polypropylene

capacitors in place of polyester ones will not only ensure capacitor

reliability but will also lower the stress on other components by

reducing the circuit losses (and hence power consumption).

s type used polyester capacitors, and it's no surprise that they were

inclined to give up. When replacing the tuning capacitors in a

thyristor line output stage it's essential to use polypropylene types -a

good range of axial components with values ranging from 0.001µF to

047µF is available from RS Components, enabling even non-standard values

to be made up from an appropriate combination. Using polypropylene

capacitors in place of polyester ones will not only ensure capacitor

reliability but will also lower the stress on other components by

reducing the circuit losses (and hence power consumption). e

right of the tuning capacitance acts in exactly the same manner as a

transis- tor line output stage, with the scan thyristor Th2 replacing

the transistor. The thyristor is switched on about half way through the

forward scan, the efficiency diode D2 provid- ing the initial part of

the line scan (left-hand side of the screen). The scan coils and line

output transformer (used to generate the e.h.t. plus various other

supply lines and pulse waveforms as required) are a.c. coupled, via the

scan -correction capacitor C5 and C6 respectively. The problem with a

thyristor is that it can be turned on at its gate but not off. To switch

a thyristor off, the current flowing through it must be reduced below a

value known as the hold -on current. This is the main function of the

components on the left-hand side - the line generator, the flyback

thyristor with its parallel diode and the commutat- ing coil. During the

forward scan, the tuning capacitors are charged from the h.t. line via

the input and commutat- ing coils. The line generator produces a pulse

to trigger the flyback thyristor Th1- this occurs just before the actual

flyback. When Thl1 switches on, the junction of the input coil and the

commutating coil is momentarily con- nected to chassis. The tuning

capacitance and the com- mutating coil then resonate, producing a pulse

which draws current via the scan thyristor. Since this current flow is

in the opposite direction to the scan current flow, the two cancel and

the current flowing via the scan thyris- tor falls below the hold -on

current. Th2 is thus switched off, and the scan coils resonate with the

tuning capaci- tance to provide the flyback action. So much for the

basic action. A secondary winding coupled to the input coil produces a

pulse to switch the scan thyristor on, in conjunction with the

shaping/delay network Ll, C4, R1. The tuning capacitors are usually

arranged in the T formation shown to reduce the values required and the

voltages developed across them. In practical circuits the input

and commutating coils are usually combined in a single unit which for

obvious reasons is generally known as the combi coil. The main point not

so far mentioned is stabilisation. There are two approaches to this. In

earlier circuits a transductor was included in parallel with the

e

right of the tuning capacitance acts in exactly the same manner as a

transis- tor line output stage, with the scan thyristor Th2 replacing

the transistor. The thyristor is switched on about half way through the

forward scan, the efficiency diode D2 provid- ing the initial part of

the line scan (left-hand side of the screen). The scan coils and line

output transformer (used to generate the e.h.t. plus various other

supply lines and pulse waveforms as required) are a.c. coupled, via the

scan -correction capacitor C5 and C6 respectively. The problem with a

thyristor is that it can be turned on at its gate but not off. To switch

a thyristor off, the current flowing through it must be reduced below a

value known as the hold -on current. This is the main function of the

components on the left-hand side - the line generator, the flyback

thyristor with its parallel diode and the commutat- ing coil. During the

forward scan, the tuning capacitors are charged from the h.t. line via

the input and commutat- ing coils. The line generator produces a pulse

to trigger the flyback thyristor Th1- this occurs just before the actual

flyback. When Thl1 switches on, the junction of the input coil and the

commutating coil is momentarily con- nected to chassis. The tuning

capacitance and the com- mutating coil then resonate, producing a pulse

which draws current via the scan thyristor. Since this current flow is

in the opposite direction to the scan current flow, the two cancel and

the current flowing via the scan thyris- tor falls below the hold -on

current. Th2 is thus switched off, and the scan coils resonate with the

tuning capaci- tance to provide the flyback action. So much for the

basic action. A secondary winding coupled to the input coil produces a

pulse to switch the scan thyristor on, in conjunction with the

shaping/delay network Ll, C4, R1. The tuning capacitors are usually

arranged in the T formation shown to reduce the values required and the

voltages developed across them. In practical circuits the input

and commutating coils are usually combined in a single unit which for

obvious reasons is generally known as the combi coil. The main point not

so far mentioned is stabilisation. There are two approaches to this. In

earlier circuits a transductor was included in parallel with the  input

coil to vary the impe- dance in series with the tuning capacitance.

This was driven by a transistor which was in turn controlled by feedback

from the line output transformer. A more efficient technique is used in

later circuits, with a current dumping thyristor in series with the

input coil. Practical Circuit As a typical example of the earlier type

of circuit, Fig. 2 shows the thyristor line output stage used in the

Grundig 5010/5011/6010/6011 series. Td1 is the regulating transductor

which is driven by Tr506. Ty511 is the flyback thyristor (commutating

thyristor might be a better name), Ty518 the scan thyristor, Di518 the

efficiency diode and C516/7/8 the tuning capacitance. The scan coils are

cou- pled via C537, while C532 provides coupling between the primary

winding of the line output transformer and chas- sis. A transductor

(Td2) is used for EW raster correction. The combi coil also feeds 1.t.

rectifiers from its secondary windings.

input

coil to vary the impe- dance in series with the tuning capacitance.

This was driven by a transistor which was in turn controlled by feedback

from the line output transformer. A more efficient technique is used in

later circuits, with a current dumping thyristor in series with the

input coil. Practical Circuit As a typical example of the earlier type

of circuit, Fig. 2 shows the thyristor line output stage used in the

Grundig 5010/5011/6010/6011 series. Td1 is the regulating transductor

which is driven by Tr506. Ty511 is the flyback thyristor (commutating

thyristor might be a better name), Ty518 the scan thyristor, Di518 the

efficiency diode and C516/7/8 the tuning capacitance. The scan coils are

cou- pled via C537, while C532 provides coupling between the primary

winding of the line output transformer and chas- sis. A transductor

(Td2) is used for EW raster correction. The combi coil also feeds 1.t.

rectifiers from its secondary windings.  Component Problems: The only problem with this type of circuit is the large amount of energy that shuttles back and forth at line frequency.

This places a heavy stress on certain components. Circuit losses

produce quite high temperatures, which are concentrated at certain

points, in particular the combi coil. This leads to deterioration of the

soldered joints around the coil, a common cause of failure. This can

have a cumulative effect, a high -resistance joint increasing the local

heating until the joint becomes well and truly dry -a classic symptom

with some Grundig sets. The wound components themselves can be a source

of trouble, due to losses - particularly the combi coil and the

regulating transductor. Later chassis are less prone to this sort of

thing, partly because of the use of later generation, higher efficiency

yokes but mainly due to more generous and better design of the wound

components. The ideal dielectric for use in the tuning capacitors is

polypropylene (either metalised or film). It's a truly won- derful

dielectric - very stable, with very small losses, and capable of

operation at high frequencies and elevated temperatures. It's also

nowadays reasonably inexpensive. Unfortunately many earlier chassis of

this type used polyester capacitors, and it's no surprise that they were

inclined to give up. When replacing the tuning capacitors in a

thyristor line output stage it's essential to use poly- propylene types

-a good range of axial components with values ranging from 0.001µF to

047µF is available from RS Components, enabling even non-standard values

to be made up from an appropriate combination. Using polypropylene

capacitors in place of polyester ones will not only ensure capacitor

reliability but will

Component Problems: The only problem with this type of circuit is the large amount of energy that shuttles back and forth at line frequency.

This places a heavy stress on certain components. Circuit losses

produce quite high temperatures, which are concentrated at certain

points, in particular the combi coil. This leads to deterioration of the

soldered joints around the coil, a common cause of failure. This can

have a cumulative effect, a high -resistance joint increasing the local

heating until the joint becomes well and truly dry -a classic symptom

with some Grundig sets. The wound components themselves can be a source

of trouble, due to losses - particularly the combi coil and the

regulating transductor. Later chassis are less prone to this sort of

thing, partly because of the use of later generation, higher efficiency

yokes but mainly due to more generous and better design of the wound

components. The ideal dielectric for use in the tuning capacitors is

polypropylene (either metalised or film). It's a truly won- derful

dielectric - very stable, with very small losses, and capable of

operation at high frequencies and elevated temperatures. It's also

nowadays reasonably inexpensive. Unfortunately many earlier chassis of

this type used polyester capacitors, and it's no surprise that they were

inclined to give up. When replacing the tuning capacitors in a

thyristor line output stage it's essential to use poly- propylene types

-a good range of axial components with values ranging from 0.001µF to

047µF is available from RS Components, enabling even non-standard values

to be made up from an appropriate combination. Using polypropylene

capacitors in place of polyester ones will not only ensure capacitor

reliability but will  also

lower the stress on other components by reducing the circuit losses

(and hence power consumption). The thyristors are also liable to fail,

as are their parallel diodes. Earlier devices were less reliable than

their successors. Since all thyristor line output stages operate in the

same way and under similar conditions, the use of later types of

thyristors and diodes in earlier circuits is a matter of mechanical

rather than electrical con- siderations. One important point should be

noted: the scan thyristor is a faster device and often has a higher

voltage rating than the flyback thyristor. The simplest course is to

keep in stock some of the later scan thyristors that incorporate an

efficiency diode - suitable types are the RCA S3900SF and the Telefunken

TD3-800H. The Telefunken device is in a TO66 package (and can be

obtained quite cheaply) while the RCA type is in a TO220 package. Either

type can be used in the scan or flyback positions and can also be used

as a replacement for the regulating thyristor used in later designs

instead of a transductor. Whenever replacing a thyristor in the line

output stage it's good practice to replace the parallel diode at the

same time. Using one of the above recom- mended devices will do this

automatically, since the thyristor and its parallel diode share the same

encapsulation - always remember to remove the old diode when this is a

separate device however, as some can exhibit high -voltage

leakage/breakdown which is not evident from a quite check with the Avo.

Apart from the wound components (including the line output transformer),

the thyristors and their parallel diodes and the tuning capacitors

several other com- ponents are prone to failure. These include the

tripler, scan/flyback rectifier diodes used to provide various supply

lines, surge limiting resistors, the scan coil coup- ling/scan

correction capacitor (replace with a metalised polypropylene type) and

regulator components such as the thyristor in later types and the

transductor driver transistor in earlier circuits.

also

lower the stress on other components by reducing the circuit losses

(and hence power consumption). The thyristors are also liable to fail,

as are their parallel diodes. Earlier devices were less reliable than

their successors. Since all thyristor line output stages operate in the

same way and under similar conditions, the use of later types of

thyristors and diodes in earlier circuits is a matter of mechanical

rather than electrical con- siderations. One important point should be

noted: the scan thyristor is a faster device and often has a higher

voltage rating than the flyback thyristor. The simplest course is to

keep in stock some of the later scan thyristors that incorporate an

efficiency diode - suitable types are the RCA S3900SF and the Telefunken

TD3-800H. The Telefunken device is in a TO66 package (and can be

obtained quite cheaply) while the RCA type is in a TO220 package. Either

type can be used in the scan or flyback positions and can also be used

as a replacement for the regulating thyristor used in later designs

instead of a transductor. Whenever replacing a thyristor in the line

output stage it's good practice to replace the parallel diode at the

same time. Using one of the above recom- mended devices will do this

automatically, since the thyristor and its parallel diode share the same

encapsulation - always remember to remove the old diode when this is a

separate device however, as some can exhibit high -voltage

leakage/breakdown which is not evident from a quite check with the Avo.

Apart from the wound components (including the line output transformer),

the thyristors and their parallel diodes and the tuning capacitors

several other com- ponents are prone to failure. These include the

tripler, scan/flyback rectifier diodes used to provide various supply

lines, surge limiting resistors, the scan coil coup- ling/scan

correction capacitor (replace with a metalised polypropylene type) and

regulator components such as the thyristor in later types and the

transductor driver transistor in earlier circuits.  There

are two basic fault conditions: when the excess current trip is

activated and the set goes dead, or no e.h.t. with the trip not

activated. The first condition is usually due to a line timebase fault,

the most common being a short-circuit flyback thyristor or its parallel

diode. A straightforward resistance check will sort this out. If this is

not the case, short-circuit the scan thyristor by soldering a wire link

between its anode and cathode. This will prevent any drive to the scan

coils and the line output transformer. If the tripping stops, the fault

could be due to the tripler, the line output transformer, a rectifier

diode fed from a winding on the latter or a short in a circuit supplied

by a scan rectifier diode. If the trip continues to operate and the

flyback thyristor/diode is not the culprit, the most likely causes are

incorrect drive to this thyristor - if possible check with a scope

against the waveform given in the manual - or a rectifier diode fed from

the combi coil. As an example of the latter, Fig. 3 shows the

arrangement used in the Finlux Peacock: the electronic trip will operate

if either D503 or D504 goes short-circuit, a fairly common fault on

these sets. The diodes can also go open-circuit/high resistance to give

the no sound with field collapse symp- tom, but that's another story (

referring to the diodes as D603/4 ). When the set is dead, h.t. is

present and the trip is not activated, suspect the following: the scan

thyristor, the efficiency diode, the line output transformer, the scan -

correction capacitor, or lack of drive to the scan thyristor. Dry

-joints can be the cause of any of these basic fault conditions,

depending on the actual circuit and where the dry -joint has occurred.

There

are two basic fault conditions: when the excess current trip is

activated and the set goes dead, or no e.h.t. with the trip not

activated. The first condition is usually due to a line timebase fault,

the most common being a short-circuit flyback thyristor or its parallel

diode. A straightforward resistance check will sort this out. If this is

not the case, short-circuit the scan thyristor by soldering a wire link

between its anode and cathode. This will prevent any drive to the scan

coils and the line output transformer. If the tripping stops, the fault

could be due to the tripler, the line output transformer, a rectifier

diode fed from a winding on the latter or a short in a circuit supplied

by a scan rectifier diode. If the trip continues to operate and the

flyback thyristor/diode is not the culprit, the most likely causes are

incorrect drive to this thyristor - if possible check with a scope

against the waveform given in the manual - or a rectifier diode fed from

the combi coil. As an example of the latter, Fig. 3 shows the

arrangement used in the Finlux Peacock: the electronic trip will operate

if either D503 or D504 goes short-circuit, a fairly common fault on

these sets. The diodes can also go open-circuit/high resistance to give

the no sound with field collapse symp- tom, but that's another story (

referring to the diodes as D603/4 ). When the set is dead, h.t. is

present and the trip is not activated, suspect the following: the scan

thyristor, the efficiency diode, the line output transformer, the scan -

correction capacitor, or lack of drive to the scan thyristor. Dry

-joints can be the cause of any of these basic fault conditions,

depending on the actual circuit and where the dry -joint has occurred.  The usual symptom is fuzzy verticals and a sawtooth effect on

diagonals. The trip may operate, possibly after period of operation.

These components set up the transductor's operating bias. Linearity

problems are usually caused by the regulator circuit, which can also be

responsible for line "hunting". In the event of lack of width in the

earlier type of circuit, check for dry -joints in the regulator circuit

and suspect the control transistor. Foldover on the left-hand side of

the screen can be caused by an open -circuit flyback diode. Foldover at

the centre of the screen with greatly reduced width is the symptom when

the efficiency diode goes open -circuit - the trip may or may not

operate. Unusual interference patterns on the screen, best viewed with

the contrast control turned to minimum and the brightness control

advanced until a distinctly visible but not over bright white raster is

obtained, can be due to the tripler if there's curved patterning on the

extreme left- hand side of the screen, the regulator clamp diode (Di505

in Fig. 2) if there's curved interference just to the left of centre, or

the flyback thyristor drive circuit if there's a single vertical line

of patterning about four fifths of the way to the right of the screen.

The usual symptom is fuzzy verticals and a sawtooth effect on

diagonals. The trip may operate, possibly after period of operation.

These components set up the transductor's operating bias. Linearity

problems are usually caused by the regulator circuit, which can also be

responsible for line "hunting". In the event of lack of width in the

earlier type of circuit, check for dry -joints in the regulator circuit

and suspect the control transistor. Foldover on the left-hand side of

the screen can be caused by an open -circuit flyback diode. Foldover at

the centre of the screen with greatly reduced width is the symptom when

the efficiency diode goes open -circuit - the trip may or may not

operate. Unusual interference patterns on the screen, best viewed with

the contrast control turned to minimum and the brightness control

advanced until a distinctly visible but not over bright white raster is

obtained, can be due to the tripler if there's curved patterning on the

extreme left- hand side of the screen, the regulator clamp diode (Di505

in Fig. 2) if there's curved interference just to the left of centre, or

the flyback thyristor drive circuit if there's a single vertical line

of patterning about four fifths of the way to the right of the screen.The aim of this article has been to provide a general guide to servicing rather than to list faults common to particular models. Much useful information on individual

chassis with thyristor line output stages has appeared in previous issues of Obsolete Technology Tellye !- refer to the following as required: Search with the tag Thyristors at the bottom of the post to select all posts with this argument on various fabricants.

LINE DEFLECTION TRANSFORMER 29201-007.01 OR BV9279-066.01 and

THYRISTORS

- SIEMENS BST CC0 146 RUG (RCA ITR17053) RETURN THYRISTOR (Ruecklauf)

- SIEMENS BST CD 543 H1G (RCA ITR17052) TRACE THYRISTOR (Hinlauf)

- RCA 17127 REGULATION PHASE THYRISTOR (regelung)

INTEGRAL THYRISTOR-RECTIFIER DEVICEA semiconductor switching device comprising a silicon controlled rectifier (SCR) and a diode rectifier integrally connected in parallel with the SCR in a single semiconductor body. The device is of the NPNP or PNPN type, having gate, cathode, and anode electrodes. A portion of each intermediate N and P region makes ohmic contact to the respective anode or cathode electrode of the SCR. In addition, each intermediate region includes a highly conductive edge portion. These portions are spaced from the adjacent external regions by relatively low conductive portions, and limit the conduction of the diode rectifier to the periphery of the device. A profile of gold recombination centers further electrically isolates the central SCR portion from the peripheral diode portion.

That

class of thyristors known as controlled rectifiers are semiconductor

switches having four semiconducting regions of alternate conductivity

and which employ anode, cathode, and gate electrodes. These devices are

usually fabricated from silicon. In its normal state, the silicon

controlled rectifier (SCR) is non-conductive until an appropriate

voltage or current pulse is applied to the gate electrode, at which

point current flows from the anode to the cathode and delivers power to a

load circuit. If the SCR is reverse biased, it is non-conductive, and

cannot be turned on by a gating signal. Once conduction starts, the gate

loses control and current flows from the anode to the cathode until it

drops below a certain value (called the holding current), at which point

the SCR turns off and the gate electrode regains control. The SCR is

thus a solid state device capable of performing the circuit function of a

thyratron tube in many electronic applications. In some of these

applications, such as in automobile ignition systems and horizontal

deflection circuits in television receivers, it is necessary to connect a

separate rectifier diode in parallel with the SCR. See, for example, W.

Dietz, U. S. Pat. Nos. 3,452,244 and 3,449,623. In these applications,

the anode of the rectifier diode is connected to the cathode of the SCR,

and the cathode of the rectifier is connected to the SCR anode. Thus,

the rectifier diode will be forward biased and current will flow through

it when the SCR is reverse biased; i.e., when the SCR cathode is

positive with respect to its anode. For reasons of economy and ease of

handling, it would be preferable if the circuit function of the SCR and

the associated diode rectifier could be combined in a single device, so

that instead of requiring two devices and five electrical connections,

one device and three electrical connections are all that would be

necessary. In fact, because of the semiconductor profile employed, many

SCR's of the shorted emitter variety inherently function as a diode

rectifier when reverse biased. However, the diode rectifier function of

such devices is not isolated from the controlled rectifier portion, thus

preventing a rapid transition from one function to the other.

Therefore, it would be desirable to physically and electrically isolate

the diode rectifier portion from that portion of the device which

functions as an SCR.

That

class of thyristors known as controlled rectifiers are semiconductor

switches having four semiconducting regions of alternate conductivity

and which employ anode, cathode, and gate electrodes. These devices are

usually fabricated from silicon. In its normal state, the silicon

controlled rectifier (SCR) is non-conductive until an appropriate

voltage or current pulse is applied to the gate electrode, at which

point current flows from the anode to the cathode and delivers power to a

load circuit. If the SCR is reverse biased, it is non-conductive, and

cannot be turned on by a gating signal. Once conduction starts, the gate

loses control and current flows from the anode to the cathode until it

drops below a certain value (called the holding current), at which point

the SCR turns off and the gate electrode regains control. The SCR is

thus a solid state device capable of performing the circuit function of a

thyratron tube in many electronic applications. In some of these

applications, such as in automobile ignition systems and horizontal

deflection circuits in television receivers, it is necessary to connect a

separate rectifier diode in parallel with the SCR. See, for example, W.

Dietz, U. S. Pat. Nos. 3,452,244 and 3,449,623. In these applications,

the anode of the rectifier diode is connected to the cathode of the SCR,

and the cathode of the rectifier is connected to the SCR anode. Thus,

the rectifier diode will be forward biased and current will flow through

it when the SCR is reverse biased; i.e., when the SCR cathode is

positive with respect to its anode. For reasons of economy and ease of

handling, it would be preferable if the circuit function of the SCR and

the associated diode rectifier could be combined in a single device, so

that instead of requiring two devices and five electrical connections,

one device and three electrical connections are all that would be

necessary. In fact, because of the semiconductor profile employed, many

SCR's of the shorted emitter variety inherently function as a diode

rectifier when reverse biased. However, the diode rectifier function of

such devices is not isolated from the controlled rectifier portion, thus

preventing a rapid transition from one function to the other.

Therefore, it would be desirable to physically and electrically isolate

the diode rectifier portion from that portion of the device which

functions as an SCR.GRUNDIG SUPER COLOR Einschub W8272 IT CHASSIS 29301-114.63 Horizontal deflection circuit Thyristor horizontal output circuits:

(Thyristor Horizontalsteuerung)

Description:

1. A horizontal deflection circuit for generating the deflection current in the deflection coil of a television picture tube wherein a first switch controls the horizontal sweep, and wherein a second switch in a so-called commutation circuit with a commutating inductor and a commutating capacitor opens the first switch and, in addition, controls the energy transfer from a dc voltage source to an input inductor, characterized in that the input inductor (Le) and the commutating inductor (Lk) are combined in a unit designed as a transformer (U) which is proportioned so that the open-circuit inductance of the transformer is essentially equal to the value of the input inductor (Le), while the short-circuit inductance of the transformer (U) is essentially equal to the value of the commutating inductor (Lk), and that the second switch (S2) is connected in series with the dc voltage source (UB) and a first winding (U1) of the transformer (U). 2. A horizontal deflection circuit according to claim 1, characterized in that the transformer (U) operates as an isolation transformer between the supply (UB) and the subcircuits connected to a second winding. 3. A horizontal deflection circuit according to claim 1, characterized in that the second switch (S

2)

is connected between ground and that terminal of the first winding (U1)

of the transformer (U) not connected to the supply potential (+UB). 4. A

horizontal deflection circuit according to claim 1, characterized in

that a capacitor (CE) is connected across the series combination of the

first winding (U1) of the transformer and the second switch (S2). 5. A

horizontal deflection circuit according to claim 1, characterized in

that the second winding (U2) of the transformer (U) is connected in

series with a first switch (S1), the commutating capacitor (Ck), and a

third, bipolar switch (S3) controllable as a function of the value of a

controlled variable developed in the deflection circuit. 6. A horizontal

deflection circuit according to claim 5, characterized in that the

third switch (S3) is connected between ground and the second winding

(U2) of the transformer. 7. A horizontal deflection circuit according to

claim 2, characterized in that the isolation transformer carries a

third winding via which power is supplied to the audio output stage of

the television set. 8. A horizontal deflection circuit according to

claims 2, characterized in that the voltage serving to control the first

switch (S1) is derived from a third winding of the transformer.

2)

is connected between ground and that terminal of the first winding (U1)

of the transformer (U) not connected to the supply potential (+UB). 4. A

horizontal deflection circuit according to claim 1, characterized in

that a capacitor (CE) is connected across the series combination of the

first winding (U1) of the transformer and the second switch (S2). 5. A

horizontal deflection circuit according to claim 1, characterized in

that the second winding (U2) of the transformer (U) is connected in

series with a first switch (S1), the commutating capacitor (Ck), and a

third, bipolar switch (S3) controllable as a function of the value of a

controlled variable developed in the deflection circuit. 6. A horizontal

deflection circuit according to claim 5, characterized in that the

third switch (S3) is connected between ground and the second winding

(U2) of the transformer. 7. A horizontal deflection circuit according to

claim 2, characterized in that the isolation transformer carries a

third winding via which power is supplied to the audio output stage of

the television set. 8. A horizontal deflection circuit according to

claims 2, characterized in that the voltage serving to control the first

switch (S1) is derived from a third winding of the transformer. German Auslegeschrift (DT-AS) No. 1,537,308 discloses a horizontal deflection circuit in which, for generating a periodic sawtooth current within the respective deflection coil of the picture tube, in a first branch circuit, the deflection coil is connected to a sufficiently large capacitor serving as a current source via a first controlled, bilaterally conductive switch which is formed by a controlled rectifier and a diode connected in inverse parallel. The control electrode of the rectifier is connected to a drive pulse source which renders the switch conductive during part of the sawtooth trace period. In that arrangement, the sawtooth retrace, i.e. the current reversal, also referred to as "commutation", is initiated by a second controlled switch.

The first controlled switch also forms part of a second branch circuit where it is connected in series with a second current source and a reactance capable of oscillating. When the first switch is closed, the reactance, consisting essentially of a coil and a capacitor, receives energy from the second current source during a fixed time interval. This energy which is taken from the second current source corresponds to the circuit losses caused during the previous deflection cycle.

As can be seen, such a circuit needs two different, separate inductive elements, it being known that inductive elements are expensive to manufacture and always have a certain volume determined by the electrical properties required.

The object of the invention is to reduce the amount of inductive elements required.

The invention is characterized in that the input inductor and the commutating inductor are comb

ined

in a unit designed as a transformer which is proportioned so that the

open-circuit inductance of the transformer is essentially equal to the

value of the input inductor, while the short-circuit inductance of the

transformer is essentially equal to the value of the commutating

inductor, and that the second switch is connected in series with the dc

voltage source and a first winding of the transformer.

ined

in a unit designed as a transformer which is proportioned so that the

open-circuit inductance of the transformer is essentially equal to the

value of the input inductor, while the short-circuit inductance of the

transformer is essentially equal to the value of the commutating

inductor, and that the second switch is connected in series with the dc

voltage source and a first winding of the transformer. This solution has an added advantage in that, in mass production, both the open-circuit and the short-circuit inductance are reproducible with reliability.

According to another feature of the invention, the electrical isolation between the windings of the transformer is such that the transformer operates as an isolation transformer between the supply and the subcircuits connected to a second winding or to additional windings of the transformer. In this manner, the transformer additionally provides reliable mains isolation.

According to a further feature of the invention, the second switch is connected between ground and that terminal of the first winding of the transformer not connected to the supply potential. This simplifies the control of the switch.

According to a further feature of the invention, to regulate the energy supply, the second winding of the transformer is connected in series with the first switch, the commutating capacitor, and a third, bipolar switch controllable as a function of the value of a controlled variable developed in the deflection circuit.

The advantage gained by this measure lies in the fact that the control takes place on the side separated from the mains, so no separate isolation device is required for the gating of the third switch. Further details and advantages will be apparent from the following description of the accompanying drawings and from the claims. In the drawings,

FIG. 1 is a basic circuit diagram of the arrangement disclosed in German Auslegeschrift (DT-AS) No. 1,537,308;

FIG. 2 shows a first embodiment of the horizontal deflection circuit according to the invention, and

FIG. 3 shows a development of the horizontal deflection circuit according to the invention.

FIG. 1 shows the essential circuit elements of the horizontal deflection circuit known from the German Auslegeschrift (DT-AS) No. 1,537,308 referred to by way of introduction.

Connected in series with a dc voltage source UB is an input inductor Le and a bipolar, controlled switch S2. In the following, this switch will be referred to as the "second switch"; it is usually called the "commutating switch" to indicate its function.

In known circuits, the second switch S2 consists of a controlled rectifier and a diode connected in inverse parallel.

The second switch S2 also forms part of a second circuit which contains, in addition, a commutating inductor Lk, a commutating capacitor Ck, and a first switch S1. The first switch S1, controlling the horizontal sweep, is constructed in the same manner as the above-described second switch S2, consisting of a controlled rectifier and a diode in inverse parallel. Connected in parallel with this first switch is a deflection-coil arrangement AS with a capacitor CA as well as a high voltage generating arrangement (not shown). In FIGS. 1, 2, and 3, this arrangement is only indicated by an arrow a

nd

by the reference characters Hsp. The operation of this known horizontal

deflection circuit need not be explained here in detail since it is

described not only in the German Auslegeschrift referred to by way of

introduction, but also in many other publications.

nd

by the reference characters Hsp. The operation of this known horizontal

deflection circuit need not be explained here in detail since it is

described not only in the German Auslegeschrift referred to by way of

introduction, but also in many other publications. FIGS. 2 and 3 show the horizontal deflection circuit modified in accordance with the present invention. Like circuit elements are designated by the same reference characters as in FIG. 1.

FIG. 2 shows the basic principle of the invention. The two inductors Le and Lk of FIG. 1 have been replaced by a transformer U. To be able to serve as a substitute for the two inductors Le and Lk, the transformer must be proportioned in a special manner. Regardless of the turns ratio, the open-circuit inductance of the transformer is chosen to be essentially equal to the value of the input inductor Le, and the short-circuit inductance of the transformer is essentially equal to the value of the commutating inductor Lk.

To permit the second switch S2 to be utilized for the connection of the dc voltage source UB, it is included in the circuit of that winding U1 of the transformer connected to the dc voltage UB.

In principle, it is of no consequence for the operation of the switch S2 whether it is inserted on that side of the winding U1 connected to the positive operating potential +UB or on the side connected to ground. In practice, however, the solution shown in FIGS. 2 and 3 will be chosen since the gating of the controlled rectifier is less problematic in this case.

In compliance with pertinent safety regulations, the transformer U may be designed as an isolation transformer and can thus provide mains separation, which is necessary for various reasons. It is known from German Offenlegungschrift (DT-OS) No. 2,233,249 to provide dc isolation by designing the commutating inductor as a transformer, but this measure is not suited to attaining the object of the present invention.

If the energy to be taken from the dc voltage source is to be controlled as a function of the energy needed in the horizontal deflection circuit and in following subcircuits, the embodiment of the horizontal deflection circuit of FIG. 3 may be used.

The circuit including the winding U2 of the transformer U contains a third controlled switch S3, which, too, is inserted on the grounded side of the winding U2 for the reasons mentioned above. This third switch S3, just as the second switch S2, is operated at the frequency of a horizontal oscillator HO, but a control circuit RS whose input l is fed with a controlled variable is inserted between the oscillator and the switch S3. Depending on this controlled variable, the controlled rectifier of the third switch S3 can be caused to turn on earlier. A suitable controlled variable containing information on the energy consumption is, for example, the flyback pulse capable of being taken from the high voltage generating circuit (not shown). Details of the operation of this kind of energy control are described in applicant's German Offenlegungsschrift (DT-OS) No. b 2,253,386 and do not form part of the present invention.

With mains isolation, the additional, third switch S3 shown here has the advantage of being on the side isolated from the mains and eliminates the need for an isolation device in the control lead of the controlled rectifier.

As an isolation transformer, the transformer U may also carry additional windings U3 and U4 if power is to be supplied to the audio output stage, for example; in addition, the first switch S1 may be gated via such an additional winding.

The points marked at the windings U1 and U2 indicate the phase relationship between the respective voltages. Connected in parallel with the winding U1 and the second switch S2 is a capacitor CE which completes the circuit for the horizontal-frequency alternating current; this serves in particular to bypass the dc voltage source or the electrolytic capacitors contained therein.

If required, a well-known tuning coil may be inserted, e.g. in series with the second winding U2, without changing the basic operation of the horizontal deflection circuit according to the invention.

GRUNDIG SUPER COLOR Einschub W8272 IT CHASSIS 29301-114.63 Electron beam deflection circuit including thyristors Further Discussion and deepening of knowledge, Thyristor horizontal output circuits:

1.

An electron beam deflection circuit for a cathode ray tube with

electromagnetic deflection by means of a sawtooth current waveform

having a trace portion and a retrace portion, said circuit comprising: a

deflection winding; a first source of electrical energy formed by a

first capacitor; first controllable switching means comprising a

parallel combination of a first thyristor and a first diode connected

together to conduct in opposite directions, for connecting said winding

to said first source during said trace portion, while said first

switching means is turned on; a second source of electrical energy

including a first inductive energy storage means coupled to a voltage

supply; reactive circuit means including a combination of inductive and

capacitive reactances for storing the energy supplied by said second

source; second controllable switching means, substantially similar to

said first one, for completing a circuit including said reactive circuit

means and said first switching means, when turned on before the end of

said trace portion, so as to pass through said first switching means an

oscillatory current in opposite direction to that which passes through

said first thyristor from said first source and to turn said first

thyristor off after these two currents cancel out, the oscillatory

current flowing thereafter through said first diode for an interval

termed the circuit turn-off time, which has to be greater than the

turn-off time of said first thyristor; wherein the improvement

comprises: means for drawing, during at least a part of said trace

portion, a substantial amount of additional current through said first

switching means, in the direction of conduction of said first diode,

whereby to perceptibly shift the waveform of the current flowing through

said first switching means towards the negative values by an amount

equal to that of said substantial additional current and to lengthen, in

proportion thereto, said circuit turn-off time, without altering the

values of the reactances in the reactive circuit which intervene in the

determination of both the circuit turn-off and retrace portion time

intervals.

1.

An electron beam deflection circuit for a cathode ray tube with

electromagnetic deflection by means of a sawtooth current waveform

having a trace portion and a retrace portion, said circuit comprising: a

deflection winding; a first source of electrical energy formed by a

first capacitor; first controllable switching means comprising a

parallel combination of a first thyristor and a first diode connected

together to conduct in opposite directions, for connecting said winding

to said first source during said trace portion, while said first

switching means is turned on; a second source of electrical energy

including a first inductive energy storage means coupled to a voltage

supply; reactive circuit means including a combination of inductive and

capacitive reactances for storing the energy supplied by said second

source; second controllable switching means, substantially similar to

said first one, for completing a circuit including said reactive circuit

means and said first switching means, when turned on before the end of

said trace portion, so as to pass through said first switching means an

oscillatory current in opposite direction to that which passes through

said first thyristor from said first source and to turn said first

thyristor off after these two currents cancel out, the oscillatory

current flowing thereafter through said first diode for an interval

termed the circuit turn-off time, which has to be greater than the

turn-off time of said first thyristor; wherein the improvement

comprises: means for drawing, during at least a part of said trace

portion, a substantial amount of additional current through said first

switching means, in the direction of conduction of said first diode,

whereby to perceptibly shift the waveform of the current flowing through

said first switching means towards the negative values by an amount

equal to that of said substantial additional current and to lengthen, in

proportion thereto, said circuit turn-off time, without altering the

values of the reactances in the reactive circuit which intervene in the

determination of both the circuit turn-off and retrace portion time

intervals.

2. A deflection circuit as claimed in claim 1, wherein said amount of additional current is greater than or equal to 5 per cent of the peak-to-peak value of the current flowing through the deflection winding.

3. A deflection circuit as claimed in claim 1, wherein said means for drawing a substantial amount of additional current through said first switching means comprises a resistor connected in parallel to said first capacitor.

4. A deflection circuit as claimed in claim 1, wherein said means for drawing an additional current is formed by connecting said first and second energy sources in series so that the current charging said reactive circuit means forms the said additional current.

5. A deflection circuit as claimed in claim 1, further including a series combination of an autotransformer winding and a second high-value capacitor, said combination being connected in parallel to said first switching means, wherein said autotransformer comprises an intermediate tap located between its terminals respectively connected to said first switching means and to said second capacitor, said tap delivering, during said trace portion, a suitable DC supply voltage lower than the voltage across said second capacitor; and wherein said means for drawing a substantial amount of additional current comprises a load to be fed by said supply voltage and having one terminal connected to ground; and further controllable switching means controlled to conduct during at least part of said trace portion and to remain cut off during said retrace portion, said further switching means being connected between said tap and the other terminal of said load.

The

present invention constitutes an improvement in the circuit described

in U.S. Pat. No. 3,449,623 filed on Sept. 6, 1966, this circuit being

described in greater detail below with reference to FIGS. 1 and 2 of the

accompanying drawings. A deflection circuit of this type comprises a

first thyristor switch which allows the conenction of the horizontal

deflection winding to a constant voltage source during the time interval

used for the transmisstion of the picture signal and for applying this

signal to the grid of the cathode ray tube (this interval will be termed

the "trace portion" of the scan), and a second thyristor switch which

provides the forced commutation of the first one by applying to it a

reverse current of equal amplitude to that which passes through it from

the said voltage source and thus to initiate the retrace during the

horizontal blanking interval.

The

present invention constitutes an improvement in the circuit described

in U.S. Pat. No. 3,449,623 filed on Sept. 6, 1966, this circuit being

described in greater detail below with reference to FIGS. 1 and 2 of the

accompanying drawings. A deflection circuit of this type comprises a

first thyristor switch which allows the conenction of the horizontal

deflection winding to a constant voltage source during the time interval

used for the transmisstion of the picture signal and for applying this

signal to the grid of the cathode ray tube (this interval will be termed

the "trace portion" of the scan), and a second thyristor switch which

provides the forced commutation of the first one by applying to it a

reverse current of equal amplitude to that which passes through it from

the said voltage source and thus to initiate the retrace during the